16通道,1 MSPS,12位ADC,定序

器28引线TSSOP

数据表

特征

快速吞吐速率:1 MSPS额定欲诉 DD 在最高吞吐量2.7 V

快速吞吐速率:1 MSPS额定欲诉 DD 在最高吞吐量2.7 V

快速吞吐速率:1 MSPS额定欲诉 DD 在最高吞吐量2.7 V

至5.25 V低功耗

5.4毫瓦最大在870 kSPS时采用3 V电源

12.5毫瓦最大在1 MSPS,5 V电源

16(单端)与定序器宽输入带宽的输入

69.5分贝SNR在50kHz输入频率

灵活的功耗/串行时钟速度管理无流水线延迟

高速串行接口,SPI / QSPI™/ MICROWIRE™/

DSP兼容

全关断模式:0.5μA最大28引脚TSSOP和32引脚LFCSP

封装

AD7490

功能框图

AD7490

VDD

T / H

12位逐次逼近

ADC

输入多路复用

器

REFIN

VIN0

VIN15

SEQUENCER

控制

逻辑

AGND

图1。

SCLK

DOUT

DIN CS

VDRIVE

1

0

0

-

1

9

6

2

0

概述

的AD7490是一个12位的高速,低功耗,16通道,逐次逼近ADC。将部件从一个

单一的操作

2.7 V至5.25 V电源供电,最高吞吐量可达1 MSPS。该器件包含一个低噪声,

宽带宽采样和保持放大器,可以在1 MHz以上的处理输入频率。

频率,因为这也被用来作为主时钟,以控制转化。

的AD7490是在32引脚LFCSP和28引脚TSSOP封装。

转换过程和数据采集过程通过CS和串行时钟信号,使该器件能够容易地与微处

理器或DSP接口控制。在CS的下降沿对输入信号进行采样,并转换同时在此处

启动。有该器件无流水线延迟。

该AD7490采用先进的设计技术,可在高吞吐速率下实现极低的功耗。为了获

得最大的吞吐速率,AD7490功耗仅为1.8 mA的3个V电源,并与5个V电源2.5

毫安。

通过在控制寄存器中的相关位,对于其模拟输入范围可以被选择为一个0 V

至REF 在

至REF 在

输入或0 V至2×REF 在 输入,可采用标准二进制或二进制补码输出编码。的AD7

输入或0 V至2×REF 在 输入,可采用标准二进制或二进制补码输出编码。的AD7

输入或0 V至2×REF 在 输入,可采用标准二进制或二进制补码输出编码。的AD7

490设有一个通道序列16个单端模拟输入,以允许信道的预先编程选择要被顺

序转换。转换时间由SCLK确定

产品聚焦

1。 该AD7490提供高达1 MSPS的吞吐率。在

1。 该AD7490提供高达1 MSPS的吞吐率。在

采用3个V电源的最大吞吐量,所述AD7490功耗仅为5.4功率毫瓦。

2。 信道的序列可以被选择,通过该

2。 信道的序列可以被选择,通过该

AD7490周期和转换。

3。 的AD7490采用2.7 V至5.25 V电源供电。

3。 的AD7490采用2.7 V至5.25 V电源供电。

在V 驾驶 功能允许串行接口直接连接到3 V或5个V处理器系统独立于V的 DD。

在V 驾驶 功能允许串行接口直接连接到3 V或5个V处理器系统独立于V的 DD。

在V 驾驶 功能允许串行接口直接连接到3 V或5个V处理器系统独立于V的 DD。

在V 驾驶 功能允许串行接口直接连接到3 V或5个V处理器系统独立于V的 DD。

4。 转换速率由串行时钟确定,

4。 转换速率由串行时钟确定,

允许所述转换时间到通过串行时钟速度增加而降低。该器件还提供各种关

断模式,可在较低吞吐量最大化电源效率。功耗为0.5μA,最大,完全关断

时。

5。 该器件具有一个标准的逐次逼近

5。 该器件具有一个标准的逐次逼近

ADC,通过CS输入和一次性转换控制采样时间的精确控制。

牧师d

ADI公司提供的信息被认为是准确可靠的。但是,没有责任承担ADI公司供其使用,也不对可能导致其使用第三方专利或

其他权利的任何侵犯。规格如有变更,恕不另行通知。没有获发牌照以暗示或以其他方式在ADI公司的任何专利或专利

的权利。商标和注册商标均为其各自所有者的财产。

文档反馈

其中技术的方式,邮政信箱9106,马萨诸塞州诺伍德02062-9106,USA电话:781.329.4700©2002-2

012 ADI公司,保留所有权利。

技术支援

www.analog.com

�

AD7490

目录

数据表

特征 ................................................. ............................................. 1

影子寄存器................................................ ......................... 14

功能框图............................................... ............... 1

概述................................................ ......................... 1

操作理论............................................... ....................... 16

电路信息................................................ .................... 16

产品亮点................................................ ........................... 1

转换器操作................................................ .................. 16

修订记录 ................................................ ............................... 2

ADC传递函数............................................... .............. 17

规格................................................. .................................... 3

典型连接图............................................... .... 18

时序规范................................................ .................. 5

工作模式............................................... .................... 19

绝对最大额定值 ............................................... ............. 6

串行接口................................................ ............................ 22

ESD注意事项................................................ .................................. 6

引脚配置和功能描述........................... 7

典型性能特性............................................. 8

功耗与吞吐率............................................. .......... 23

微处理器接口................................................ 24 .......

应用提示................................................ ....................... 25

术语................................................. ................................... 10

外形尺寸................................................ ....................... 26

的内部寄存器结构............................................... ............. 12

订购指南................................................ .......................... 27

控制寄存器................................................ .......................... 12

修订记录

12分之12-REV。C到牧师d

图4和表4的变化........................................... .................. 7

更新的外形尺寸(改变CP-32-2 CP-32-7)..... 26

更改订购指南.............................................. ............. 27

6月9日-REV。B到版本C

更改为我 DD 自动待机模式参数,表1 ............... 4

更改为我 DD 自动待机模式参数,表1 ............... 4

更改为我 DD 自动待机模式参数,表1 ............... 4

5月8日-REV。A到版本B

更新后的格式................................................ ..................通用更改表1 ..............

............. ................................................. 3

图12和图13的变化........................................... 14 ..

图14的变化.............................................. ........................ 15

更改参考部分.............................................. ......... 19

更新的外形尺寸............................................... ........ 26

更改订购指南.............................................. ............ 27

10月2日-REV。0 Rev. A的

除了一般的描述.............................................. ....... 1

改变时序规范注......................................... 4

更改为绝对最大额定值......................................... 5

除了订购指南.............................................. .............. 5

更改典型性能特性.......................... 8

增加了新的图9 .............................................. ............................ 8

图12和图14的变化........................................... 11 ..

图20的变化.............................................. ........................ 13

变为图20至图26 ........................................... ..... 14

除了模拟输入部分............................................. ... 14

更改图29说明............................................. ............ 18

改变图30至图32 ........................................... ...... 18

新增应用提示.............................................. ... 20

1月2日,修订0:初始版本

牧师d | 第2页28

�

数据表

规格

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

V DD = V DRIVE = 2.7 V至5.25 V,REF IN = 2.5 V,F SCLK1 = 20兆赫,T A = Ť MIN 至T MAX, 除非另有说明。温度范围(B版):-40°C到+ 85℃。

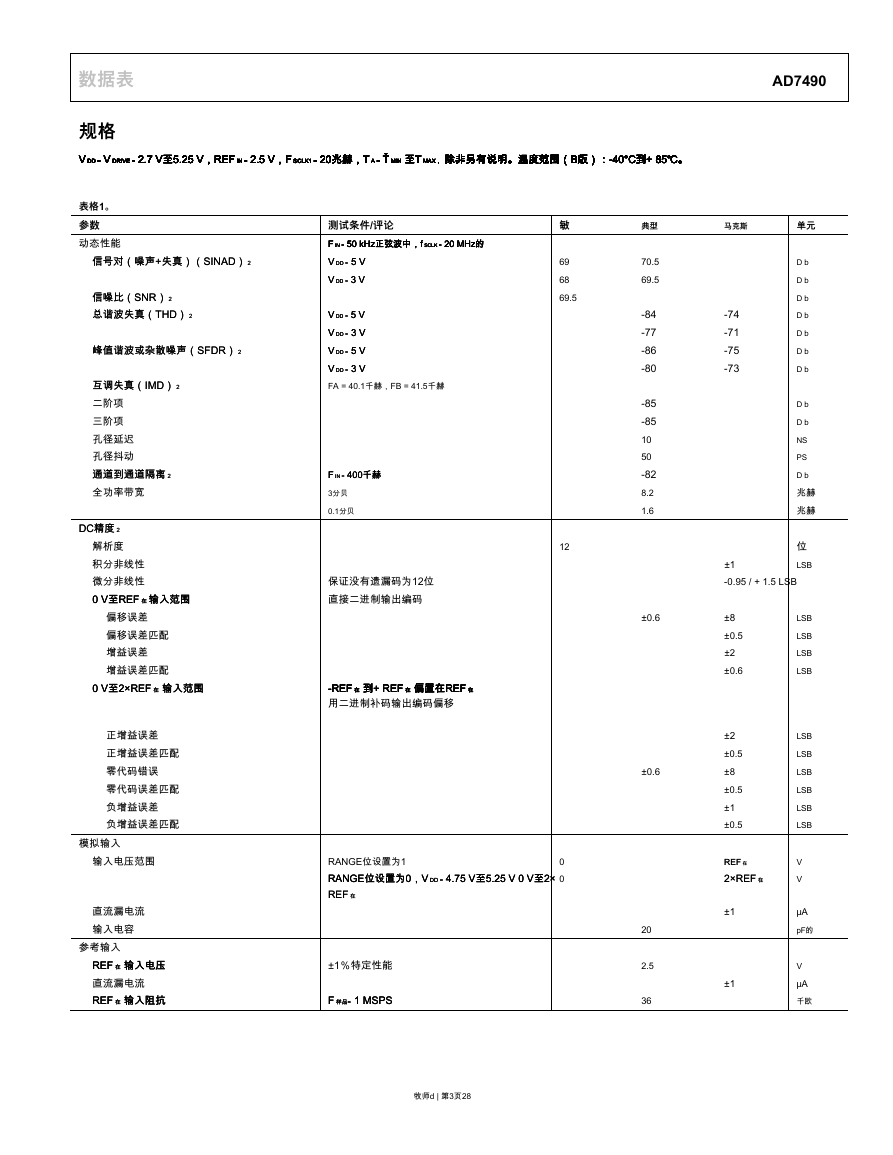

表格1。

参数

动态性能

信号对(噪声+失真)(SINAD) 2

信号对(噪声+失真)(SINAD) 2

信噪比(SNR) 2

信噪比(SNR) 2

总谐波失真(THD) 2

总谐波失真(THD) 2

峰值谐波或杂散噪声(SFDR) 2

峰值谐波或杂散噪声(SFDR) 2

互调失真(IMD) 2

互调失真(IMD) 2

二阶项

三阶项

孔径延迟

孔径抖动

通道到通道隔离 2

通道到通道隔离 2

全功率带宽

DC精度 2

DC精度 2

解析度

积分非线性

微分非线性

0 V至REF 在 输入范围

0 V至REF 在 输入范围

0 V至REF 在 输入范围

偏移误差

偏移误差匹配

增益误差

增益误差匹配

0 V至2×REF 在 输入范围

0 V至2×REF 在 输入范围

0 V至2×REF 在 输入范围

正增益误差

正增益误差匹配

零代码错误

零代码误差匹配

负增益误差

负增益误差匹配

模拟输入

输入电压范围

直流漏电流

输入电容

参考输入

REF 在 输入电压

REF 在 输入电压

REF 在 输入电压

直流漏电流

REF 在 输入阻抗

REF 在 输入阻抗

REF 在 输入阻抗

敏

69

68

69.5

12

测试条件/评论

F IN = 50 kHz正弦波中,f SCLK = 20 MHz的

F IN = 50 kHz正弦波中,f SCLK = 20 MHz的

F IN = 50 kHz正弦波中,f SCLK = 20 MHz的

F IN = 50 kHz正弦波中,f SCLK = 20 MHz的

F IN = 50 kHz正弦波中,f SCLK = 20 MHz的

V DD = 5 V

V DD = 5 V

V DD = 5 V

V DD = 3 V

V DD = 3 V

V DD = 3 V

V DD = 5 V

V DD = 5 V

V DD = 5 V

V DD = 3 V

V DD = 3 V

V DD = 3 V

V DD = 5 V

V DD = 5 V

V DD = 5 V

V DD = 3 V

V DD = 3 V

V DD = 3 V

FA = 40.1千赫,FB = 41.5千赫

F IN = 400千赫

F IN = 400千赫

F IN = 400千赫

3分贝

0.1分贝

保证没有遗漏码为12位

直接二进制输出编码

-REF 在 到+ REF 在 偏置在REF 在

-REF 在 到+ REF 在 偏置在REF 在

-REF 在 到+ REF 在 偏置在REF 在

-REF 在 到+ REF 在 偏置在REF 在

-REF 在 到+ REF 在 偏置在REF 在

-REF 在 到+ REF 在 偏置在REF 在

用二进制补码输出编码偏移

RANGE位设置为1

RANGE位设置为0,V DD = 4.75 V至5.25 V 0 V至2×

RANGE位设置为0,V DD = 4.75 V至5.25 V 0 V至2×

RANGE位设置为0,V DD = 4.75 V至5.25 V 0 V至2×

REF 在REF 在

0

0

±1%特定性能

F 样品= 1 MSPS

F 样品= 1 MSPS

F 样品= 1 MSPS

牧师d | 第3页28

典型

70.5

69.5

-84

-77

-86

-80

-85

-85

10

50

-82

8.2

1.6

±0.6

±0.6

20

2.5

36

AD7490

马克斯

单元

-74

-71

-75

-73

D b

D b

D b

D b

D b

D b

D b

D b

D b

NS

PS

D b

兆赫

兆赫

位

LSB

±1

-0.95 / + 1.5 LSB

±8

±0.5

±2

±0.6

±2

±0.5

±8

±0.5

±1

±0.5

REF 在REF 在

2×REF 在

2×REF 在

±1

±1

LSB

LSB

LSB

LSB

LSB

LSB

LSB

LSB

LSB

LSB

V

V

μA

pF的

V

μA

千欧

�

AD7490

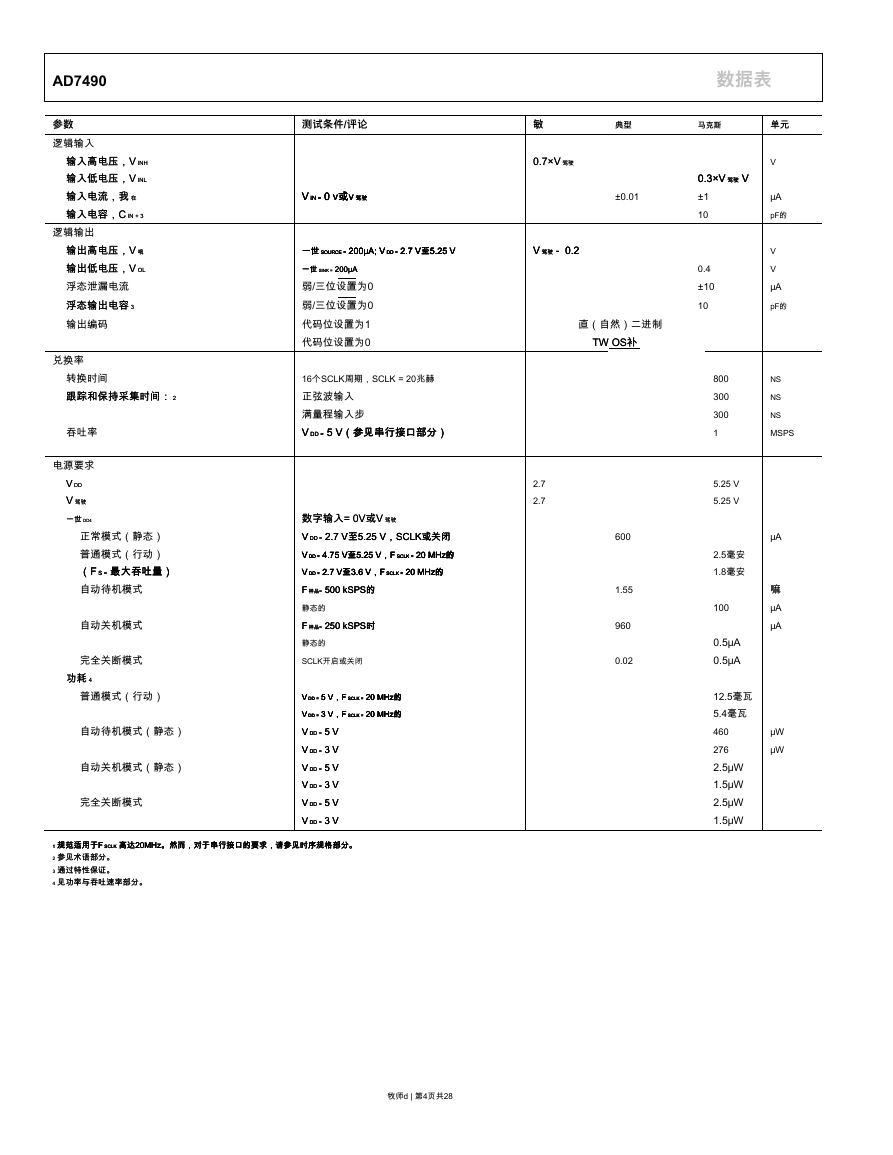

参数

逻辑输入

输入高电压,V INH

输入高电压,V INH

输入低电压,V INL

输入低电压,V INL

输入电流,我 在

输入电流,我 在

输入电容,C IN + 3

输入电容,C IN + 3

逻辑输出

输出高电压,V 哦

输出高电压,V 哦

输出低电压,V OL

输出低电压,V OL

浮态泄漏电流

浮态输出电容 3

浮态输出电容 3

输出编码

兑换率

转换时间

跟踪和保持采集时间: 2

跟踪和保持采集时间: 2

吞吐率

电源要求

V DDV DD

V 驾驶V 驾驶

一世 DD4一世 DD4

正常模式(静态)

普通模式(行动)

(F S = 最大吞吐量)

(F S = 最大吞吐量)

(F S = 最大吞吐量)

自动待机模式

自动关机模式

完全关断模式

功耗 4功耗 4

普通模式(行动)

自动待机模式(静态)

自动关机模式(静态)

完全关断模式

测试条件/评论

敏

0.7×V 驾驶

0.7×V 驾驶

V IN = 0 v或v 驾驶

V IN = 0 v或v 驾驶

V IN = 0 v或v 驾驶

V IN = 0 v或v 驾驶

±0.01

一世 SOURCE = 200μA; V DD = 2.7 V至5.25 V

一世 SOURCE = 200μA; V DD = 2.7 V至5.25 V

一世 SOURCE = 200μA; V DD = 2.7 V至5.25 V

一世 SOURCE = 200μA; V DD = 2.7 V至5.25 V

一世 SOURCE = 200μA; V DD = 2.7 V至5.25 V

V 驾驶 - 0.2

V 驾驶 - 0.2

V 驾驶 - 0.2

直(自然)二进制

TW OS补

TW OS补

2.7

2.7

600

1.55

960

0.02

一世 SINK = 200μA

一世 SINK = 200μA

一世 SINK = 200μA

弱/三位设置为0

弱/三位设置为0

代码位设置为1

代码位设置为0

16个SCLK周期,SCLK = 20兆赫

正弦波输入

满量程输入步

V DD = 5 V(参见串行接口部分)

V DD = 5 V(参见串行接口部分)

V DD = 5 V(参见串行接口部分)

数字输入= 0V或V 驾驶

数字输入= 0V或V 驾驶

V DD = 2.7 V至5.25 V,SCLK或关闭

V DD = 2.7 V至5.25 V,SCLK或关闭

V DD = 2.7 V至5.25 V,SCLK或关闭

V DD = 4.75 V至5.25 V,F SCLK = 20 MHz的

V DD = 4.75 V至5.25 V,F SCLK = 20 MHz的

V DD = 4.75 V至5.25 V,F SCLK = 20 MHz的

V DD = 4.75 V至5.25 V,F SCLK = 20 MHz的

V DD = 4.75 V至5.25 V,F SCLK = 20 MHz的

V DD = 2.7 V至3.6 V,F SCLK = 20 MHz的

V DD = 2.7 V至3.6 V,F SCLK = 20 MHz的

V DD = 2.7 V至3.6 V,F SCLK = 20 MHz的

V DD = 2.7 V至3.6 V,F SCLK = 20 MHz的

V DD = 2.7 V至3.6 V,F SCLK = 20 MHz的

F 样品= 500 kSPS的

F 样品= 500 kSPS的

F 样品= 500 kSPS的

静态的

F 样品= 250 kSPS时

F 样品= 250 kSPS时

F 样品= 250 kSPS时

静态的

SCLK开启或关闭

V DD = 5 V,F SCLK = 20 MHz的

V DD = 5 V,F SCLK = 20 MHz的

V DD = 5 V,F SCLK = 20 MHz的

V DD = 5 V,F SCLK = 20 MHz的

V DD = 5 V,F SCLK = 20 MHz的

V DD = 3 V,F SCLK = 20 MHz的

V DD = 3 V,F SCLK = 20 MHz的

V DD = 3 V,F SCLK = 20 MHz的

V DD = 3 V,F SCLK = 20 MHz的

V DD = 3 V,F SCLK = 20 MHz的

V DD = 5 V

V DD = 5 V

V DD = 5 V

V DD = 3 V

V DD = 3 V

V DD = 3 V

V DD = 5 V

V DD = 5 V

V DD = 5 V

V DD = 3 V

V DD = 3 V

V DD = 3 V

V DD = 5 V

V DD = 5 V

V DD = 5 V

V DD = 3 V

V DD = 3 V

V DD = 3 V

数据表

典型

马克斯

单元

V

μA

pF的

V

V

μA

pF的

NS

NS

NS

MSPS

μA

嘛

μA

μA

μW

μW

0.3×V 驾驶 V

0.3×V 驾驶 V

0.3×V 驾驶 V

±1

10

0.4

±10

10

800

300

300

1

5.25 V

5.25 V

2.5毫安

1.8毫安

100

0.5μA

0.5μA

12.5毫瓦

5.4毫瓦

460

276

2.5μW

1.5μW

2.5μW

1.5μW

1 规范适用于F SCLK 高达20MHz。然而,对于串行接口的要求,请参见时序规格部分。

1 规范适用于F SCLK 高达20MHz。然而,对于串行接口的要求,请参见时序规格部分。

1 规范适用于F SCLK 高达20MHz。然而,对于串行接口的要求,请参见时序规格部分。

1 规范适用于F SCLK 高达20MHz。然而,对于串行接口的要求,请参见时序规格部分。

2 参见术语部分。

2 参见术语部分。

3 通过特性保证。

3 通过特性保证。

4 见功率与吞吐速率部分。

4 见功率与吞吐速率部分。

牧师d | 第4页共28

�

数据表

时序规范

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

V DD = 2.7 V至5.25 V,V 驾驶 ≤V DD, REF IN = 2.5 V; Ť A = Ť MIN 至T MAX, 除非另有说明。

表2.钛 明规格 1

表2.钛 明规格 1

表2.钛 明规格 1

限制在T MIN, Ť MAX

限制在T MIN, Ť MAX

限制在T MIN, Ť MAX

限制在T MIN, Ť MAX

AD7490

参数V DD = 3 V V DD = 5 V

参数V DD = 3 V V DD = 5 V

参数V DD = 3 V V DD = 5 V

参数V DD = 3 V V DD = 5 V

参数V DD = 3 V V DD = 5 V

参数V DD = 3 V V DD = 5 V

F SCLK2

F SCLK2

10

16

16×吨 SCLK

16×吨 SCLK

50

12

20

三十

60

0.4×吨 SCLK

0.4×吨 SCLK

0.4×吨 SCLK

0.4×吨 SCLK

15

15/50

20

五

20

1

10

20

16×吨 SCLK

16×吨 SCLK

50

10

14

20

40

0.4×吨 SCLK

0.4×吨 SCLK

0.4×吨 SCLK

0.4×吨 SCLK

15

15/50

20

五

20

1

单元

千赫分钟

最高1.5MHz

ns(最小值)

ns(最小值)

ns(最大值)

ns(最大值)

ns(最大值)

ns(最小值)

ns(最小值)

ns(最小值)

ns(最小值)/最大

ns(最小值)

ns(最小值)

ns(最小值)

微秒最大

描述

总线释放和未来转换的开始之间最少需要安静的时间

CS到SCLK建立时间

延迟从CS到DOUT三态禁用

延迟从CS到DOUT有效

SCLK的下降沿后的数据访问时间

SCLK低脉冲宽度

SCLK高脉冲宽度

SCLK到DOUT有效保持时间

SCLK的下降沿到DOUT高阻抗

到SCLK下降沿DIN建立时间之前

DIN保持时间SCLK的下降沿后

16 日 SCLK的下降沿到CS高

16 日 SCLK的下降沿到CS高

16 日 SCLK的下降沿到CS高

从完全掉电/自动关机/自动待机模式上电时间

Ť 兑换Ť 兑换

Ť 安静Ť 安静

Ť 2Ť 2

Ť 33Ť 33

Ť 3 b 4

Ť 3 b 4

Ť 3 b 4

Ť 3 b 4

Ť 43Ť 43

Ť 五Ť 五

Ť 6Ť 6

Ť 7Ť 7

Ť 85Ť 85

Ť 9Ť 9

Ť 10Ť 10

Ť 11Ť 11

Ť 12Ť 12

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

1 通过特性保证。所有输入信号均具有t指定 R = Ť F = 5个纳秒(10%至90%V的 DD) 和从1.6伏的电压电平的定时(参照图2)。3 V工作范围跨越从2.7 V至3.6 V的5 V的工作范围从4.75 V跨越至5.25 V.

2 为SCLK输入标志/空间比是40/60至60/40。最大SCLK频率为16兆赫为V DD = 3 V,得到吞吐量870 kSPS时。必须注意的接口,以考虑数据存取时间时,应考虑,T 4, 并需要为用户的处理器的设置时间。这两个时

2 为SCLK输入标志/空间比是40/60至60/40。最大SCLK频率为16兆赫为V DD = 3 V,得到吞吐量870 kSPS时。必须注意的接口,以考虑数据存取时间时,应考虑,T 4, 并需要为用户的处理器的设置时间。这两个时

2 为SCLK输入标志/空间比是40/60至60/40。最大SCLK频率为16兆赫为V DD = 3 V,得到吞吐量870 kSPS时。必须注意的接口,以考虑数据存取时间时,应考虑,T 4, 并需要为用户的处理器的设置时间。这两个时

2 为SCLK输入标志/空间比是40/60至60/40。最大SCLK频率为16兆赫为V DD = 3 V,得到吞吐量870 kSPS时。必须注意的接口,以考虑数据存取时间时,应考虑,T 4, 并需要为用户的处理器的设置时间。这两个时

2 为SCLK输入标志/空间比是40/60至60/40。最大SCLK频率为16兆赫为V DD = 3 V,得到吞吐量870 kSPS时。必须注意的接口,以考虑数据存取时间时,应考虑,T 4, 并需要为用户的处理器的设置时间。这两个时

2 为SCLK输入标志/空间比是40/60至60/40。最大SCLK频率为16兆赫为V DD = 3 V,得到吞吐量870 kSPS时。必须注意的接口,以考虑数据存取时间时,应考虑,T 4, 并需要为用户的处理器的设置时间。这两个时

间确定与用户的系统可以操作(见串行接口部分)的最大SCLK频率。

3 测定与图2的负载电路并且被定义为跨越0.4 V或0.7伏用于输出所需的时间 驾驶 。4 Ť 3 b表示为具有ADD3上DOUT线可用最坏情况的图,也就是,如果AD7490就返回到三态在一个转换结束和其他一些设备需要转换之间

3 测定与图2的负载电路并且被定义为跨越0.4 V或0.7伏用于输出所需的时间 驾驶 。4 Ť 3 b表示为具有ADD3上DOUT线可用最坏情况的图,也就是,如果AD7490就返回到三态在一个转换结束和其他一些设备需要转换之间

3 测定与图2的负载电路并且被定义为跨越0.4 V或0.7伏用于输出所需的时间 驾驶 。4 Ť 3 b表示为具有ADD3上DOUT线可用最坏情况的图,也就是,如果AD7490就返回到三态在一个转换结束和其他一些设备需要转换之间

3 测定与图2的负载电路并且被定义为跨越0.4 V或0.7伏用于输出所需的时间 驾驶 。4 Ť 3 b表示为具有ADD3上DOUT线可用最坏情况的图,也就是,如果AD7490就返回到三态在一个转换结束和其他一些设备需要转换之间

3 测定与图2的负载电路并且被定义为跨越0.4 V或0.7伏用于输出所需的时间 驾驶 。4 Ť 3 b表示为具有ADD3上DOUT线可用最坏情况的图,也就是,如果AD7490就返回到三态在一个转换结束和其他一些设备需要转换之间

3 测定与图2的负载电路并且被定义为跨越0.4 V或0.7伏用于输出所需的时间 驾驶 。4 Ť 3 b表示为具有ADD3上DOUT线可用最坏情况的图,也就是,如果AD7490就返回到三态在一个转换结束和其他一些设备需要转换之间

的总线的控制下,用户必须等待t的最大时间 3 b。具有ADD3上DOUT线有效之前。如果DOUT线被转换之间弱驱动到ADD3,用户通常具有看到ADD3上DOUT有效之前等待在3 V 17纳秒,在5 V 12纳秒的CS下降沿

的总线的控制下,用户必须等待t的最大时间 3 b。具有ADD3上DOUT线有效之前。如果DOUT线被转换之间弱驱动到ADD3,用户通常具有看到ADD3上DOUT有效之前等待在3 V 17纳秒,在5 V 12纳秒的CS下降沿

的总线的控制下,用户必须等待t的最大时间 3 b。具有ADD3上DOUT线有效之前。如果DOUT线被转换之间弱驱动到ADD3,用户通常具有看到ADD3上DOUT有效之前等待在3 V 17纳秒,在5 V 12纳秒的CS下降沿

之后。

五 Ť 8 从当与图2的电路然后将测得数外推回除去的充电或放电25 pF电容的影响加载来改变0.5 V截取由所述数据输出测量出的时间导出的。这意味着时间t 8, 在时序特性引用,是该部分的真正的总线释放时间,并且独

五 Ť 8 从当与图2的电路然后将测得数外推回除去的充电或放电25 pF电容的影响加载来改变0.5 V截取由所述数据输出测量出的时间导出的。这意味着时间t 8, 在时序特性引用,是该部分的真正的总线释放时间,并且独

五 Ť 8 从当与图2的电路然后将测得数外推回除去的充电或放电25 pF电容的影响加载来改变0.5 V截取由所述数据输出测量出的时间导出的。这意味着时间t 8, 在时序特性引用,是该部分的真正的总线释放时间,并且独

五 Ť 8 从当与图2的电路然后将测得数外推回除去的充电或放电25 pF电容的影响加载来改变0.5 V截取由所述数据输出测量出的时间导出的。这意味着时间t 8, 在时序特性引用,是该部分的真正的总线释放时间,并且独

五 Ť 8 从当与图2的电路然后将测得数外推回除去的充电或放电25 pF电容的影响加载来改变0.5 V截取由所述数据输出测量出的时间导出的。这意味着时间t 8, 在时序特性引用,是该部分的真正的总线释放时间,并且独

五 Ť 8 从当与图2的电路然后将测得数外推回除去的充电或放电25 pF电容的影响加载来改变0.5 V截取由所述数据输出测量出的时间导出的。这意味着时间t 8, 在时序特性引用,是该部分的真正的总线释放时间,并且独

立于总线负载的。

200μA

IOL

200μA

IOH

1.6V

2

0

0

-

1

9

6

2

0

TO OUTPUT

PIN CL

为25pF

图数字输出时序规格2.负载电路

牧师d | 第5页28

�

数据表

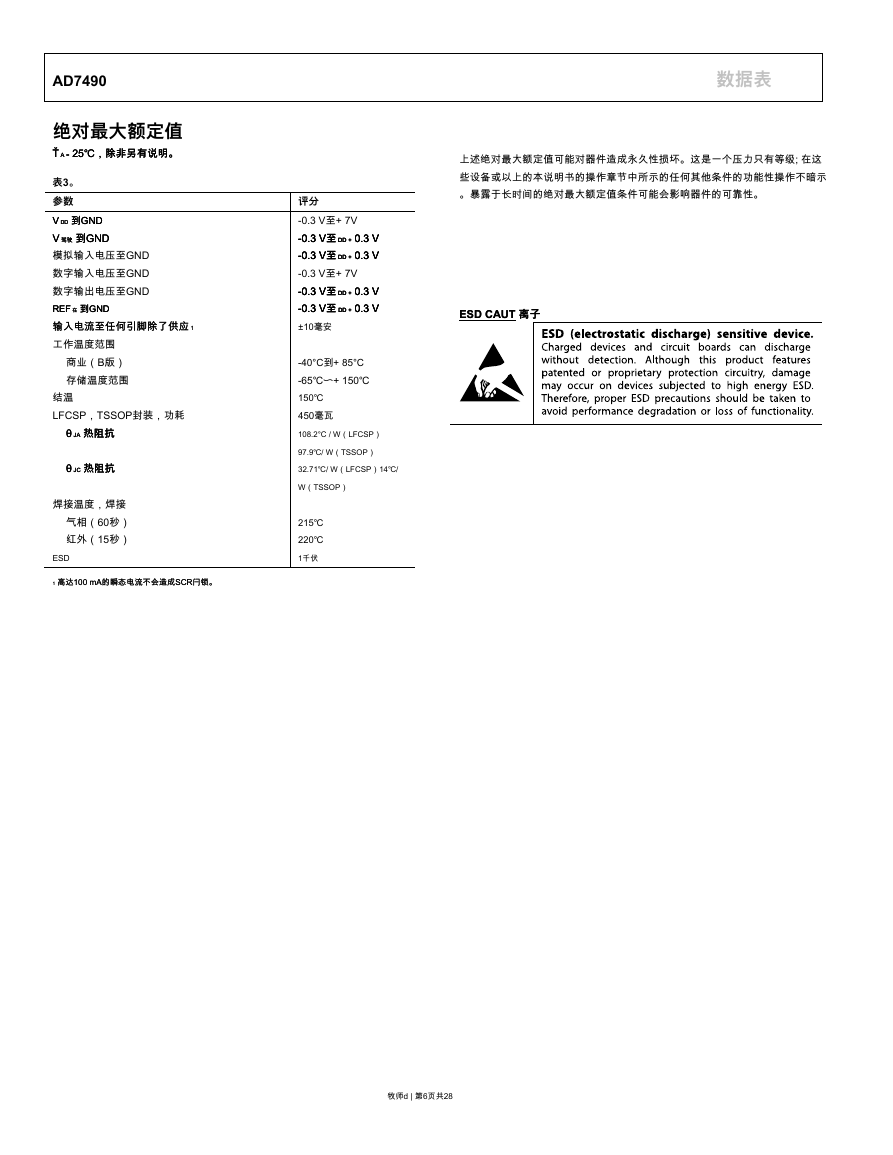

上述绝对最大额定值可能对器件造成永久性损坏。这是一个压力只有等级; 在这

些设备或以上的本说明书的操作章节中所示的任何其他条件的功能性操作不暗示

。暴露于长时间的绝对最大额定值条件可能会影响器件的可靠性。

ESD CAUT 离子

ESD CAUT 离子

AD7490

绝对最大额定值

Ť A = 25℃,除非另有说明。

Ť A = 25℃,除非另有说明。

Ť A = 25℃,除非另有说明。

表3。

参数

V DD 到GND

V DD 到GND

V DD 到GND

V 驾驶 到GND

V 驾驶 到GND

V 驾驶 到GND

模拟输入电压至GND

数字输入电压至GND

数字输出电压至GND

REF 在 到GND

REF 在 到GND

REF 在 到GND

输入电流至任何引脚除了供应 1

输入电流至任何引脚除了供应 1

工作温度范围

商业(B版)

存储温度范围

结温

LFCSP,TSSOP封装,功耗

θ JA 热阻抗

θ JA 热阻抗

θ JA 热阻抗

θ JC 热阻抗

θ JC 热阻抗

θ JC 热阻抗

焊接温度,焊接

气相(60秒)

红外(15秒)

ESD

1 高达100 mA的瞬态电流不会造成SCR闩锁。

1 高达100 mA的瞬态电流不会造成SCR闩锁。

评分

-0.3 V至+ 7V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至+ 7V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

-0.3 V至 DD + 0.3 V

±10毫安

-40°C到+ 85°C

-65℃〜+ 150℃

150℃

450毫瓦

108.2°C / W(LFCSP)

97.9℃/ W(TSSOP)

32.71℃/ W(LFCSP)14℃/

W(TSSOP)

215℃

220℃

1千伏

牧师d | 第6页共28

�

数据表

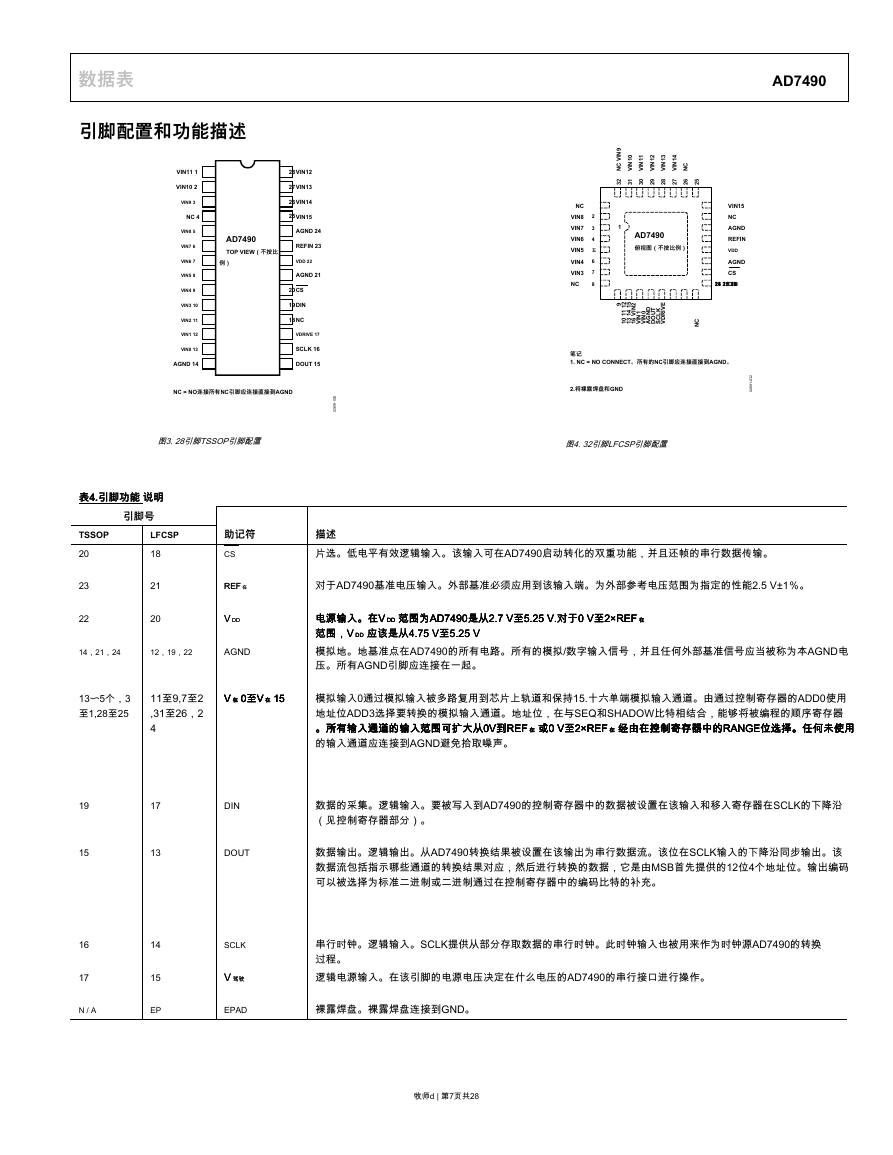

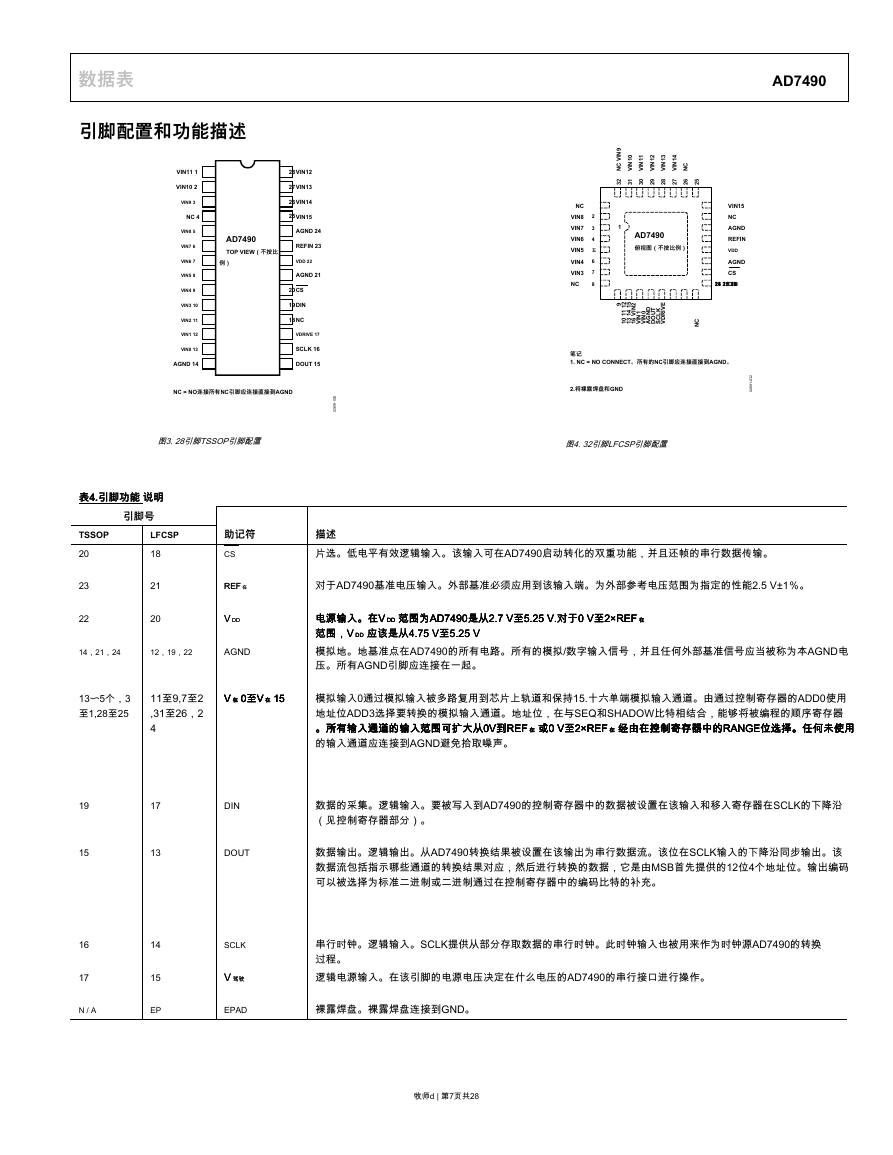

引脚配置和功能描述

VIN11 1

VIN10 2

VIN9 3

NC 4

VIN8 5

VIN7 6

VIN6 7

VIN5 8

VIN4 9

VIN3 10

VIN2 11

VIN1 12

VIN0 13

AGND 14

AD7490

TOP VIEW(不按比

例)

28

VIN12

27

VIN13

26

VIN14

25

VIN15

AGND 24

REFIN 23

VDD 22

AGND 21

20

CS

19

DIN

18

NC

VDRIVE 17

SCLK 16

DOUT 15

NC = NO连接所有NC引脚应连接直接到AGND

3

0

0

-

1

9

6

2

0

AD7490

C

N

0

1

N

V

I

1

1

N

V

I

2

1

N

V

I

3

1

N

V

I

4

1

N

V

I

I

9

N

V

C

N

2

3

1

3

0

3

9

2

8

2

7

2

6

2

5

2

1

AD7490

俯视图(不按比例)

VIN15

NC

AGND

REFIN

VDD

AGND

CS

DIN

24 23 22

21 20 19

18 17

NC

VIN8

VIN7

VIN6

VIN5

VIN4

VIN3

NC

2

3

4

五

6

7

8

9

2

1

1

1

0

1

5

1

4

1

3

1

2

N

V

6

1

I

D

N

G

A

T

U

O

D

K

L

C

S

1

N

V

0

N

V

I

I

I

E

V

R

D

V

C

N

笔记

1. NC = NO CONNECT。所有的NC引脚应连接直接到AGND。

2.将裸露焊盘和GND

2

3

0

-

1

9

6

2

0

图3. 28引脚TSSOP引脚配置

图4. 32引脚LFCSP引脚配置

表4.引脚功能 说明

表4.引脚功能 说明

引脚号

TSSOP

20

LFCSP

18

23

22

21

20

助记符

CS

REF 在REF 在

V DDV DD

14,21,24

12,19,22

AGND

描述

片选。低电平有效逻辑输入。该输入可在AD7490启动转化的双重功能,并且还帧的串行数据传输。

对于AD7490基准电压输入。外部基准必须应用到该输入端。为外部参考电压范围为指定的性能2.5 V±1%。

电源输入。在V DD 范围为AD7490是从2.7 V至5.25 V.对于0 V至2×REF 在

电源输入。在V DD 范围为AD7490是从2.7 V至5.25 V.对于0 V至2×REF 在

电源输入。在V DD 范围为AD7490是从2.7 V至5.25 V.对于0 V至2×REF 在

电源输入。在V DD 范围为AD7490是从2.7 V至5.25 V.对于0 V至2×REF 在

范围,V DD 应该是从4.75 V至5.25 V

范围,V DD 应该是从4.75 V至5.25 V

范围,V DD 应该是从4.75 V至5.25 V

模拟地。地基准点在AD7490的所有电路。所有的模拟/数字输入信号,并且任何外部基准信号应当被称为本AGND电

压。所有AGND引脚应连接在一起。

13〜5个,3

至1,28至25

11至9,7至2

,31至26,2

4

V 在 0至V 在 15

V 在 0至V 在 15

V 在 0至V 在 15

V 在 0至V 在 15

V 在 0至V 在 15

模拟输入0通过模拟输入被多路复用到芯片上轨道和保持15.十六单端模拟输入通道。由通过控制寄存器的ADD0使用

地址位ADD3选择要转换的模拟输入通道。地址位,在与SEQ和SHADOW比特相结合,能够将被编程的顺序寄存器

。所有输入通道的输入范围可扩大从0V到REF 在 或0 V至2×REF 在 经由在控制寄存器中的RANGE位选择。任何未使用

。所有输入通道的输入范围可扩大从0V到REF 在 或0 V至2×REF 在 经由在控制寄存器中的RANGE位选择。任何未使用

。所有输入通道的输入范围可扩大从0V到REF 在 或0 V至2×REF 在 经由在控制寄存器中的RANGE位选择。任何未使用

。所有输入通道的输入范围可扩大从0V到REF 在 或0 V至2×REF 在 经由在控制寄存器中的RANGE位选择。任何未使用

。所有输入通道的输入范围可扩大从0V到REF 在 或0 V至2×REF 在 经由在控制寄存器中的RANGE位选择。任何未使用

的输入通道应连接到AGND避免拾取噪声。

19

15

16

17

N / A

17

13

14

15

EP

DIN

DOUT

SCLK

V 驾驶V 驾驶

EPAD

数据的采集。逻辑输入。要被写入到AD7490的控制寄存器中的数据被设置在该输入和移入寄存器在SCLK的下降沿

(见控制寄存器部分)。

数据输出。逻辑输出。从AD7490转换结果被设置在该输出为串行数据流。该位在SCLK输入的下降沿同步输出。该

数据流包括指示哪些通道的转换结果对应,然后进行转换的数据,它是由MSB首先提供的12位4个地址位。输出编码

可以被选择为标准二进制或二进制通过在控制寄存器中的编码比特的补充。

串行时钟。逻辑输入。SCLK提供从部分存取数据的串行时钟。此时钟输入也被用来作为时钟源AD7490的转换

过程。

逻辑电源输入。在该引脚的电源电压决定在什么电压的AD7490的串行接口进行操作。

裸露焊盘。裸露焊盘连接到GND。

牧师d | 第7页共28

�

AD7490

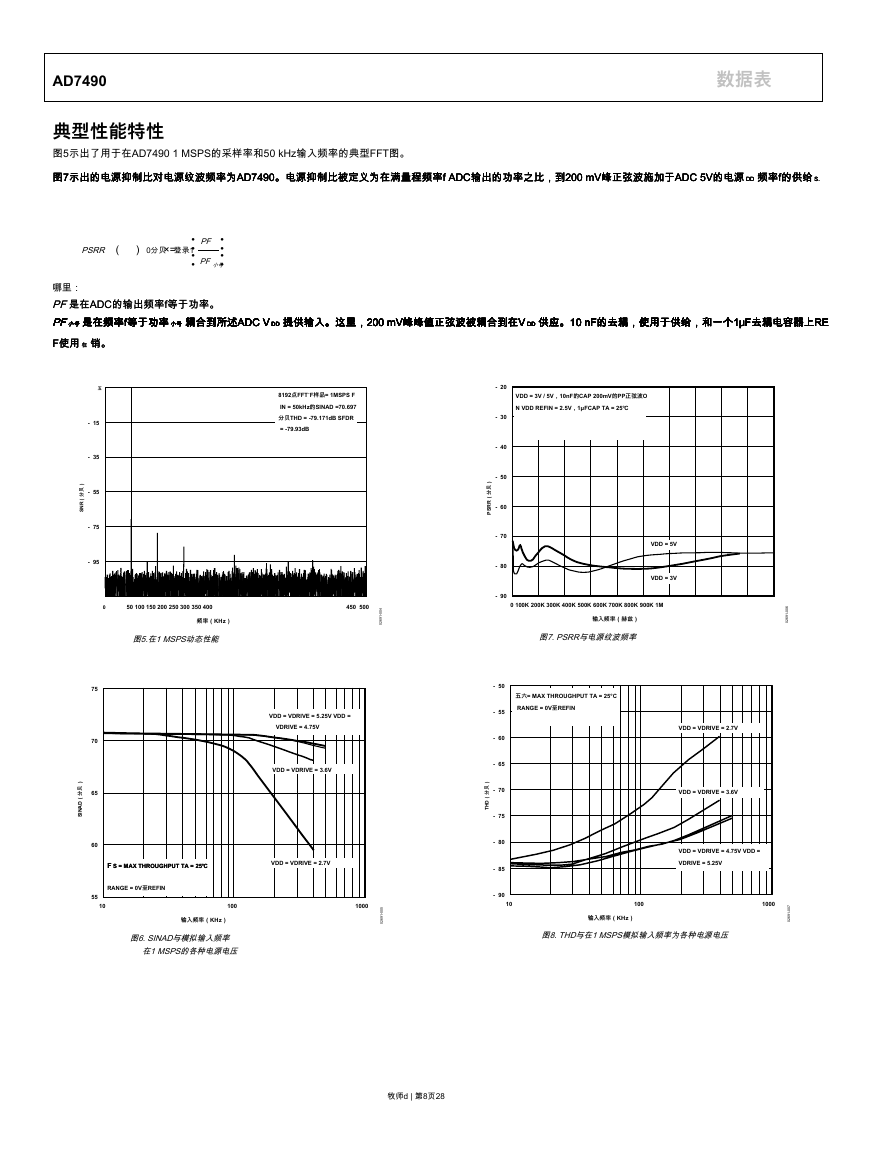

典型性能特性

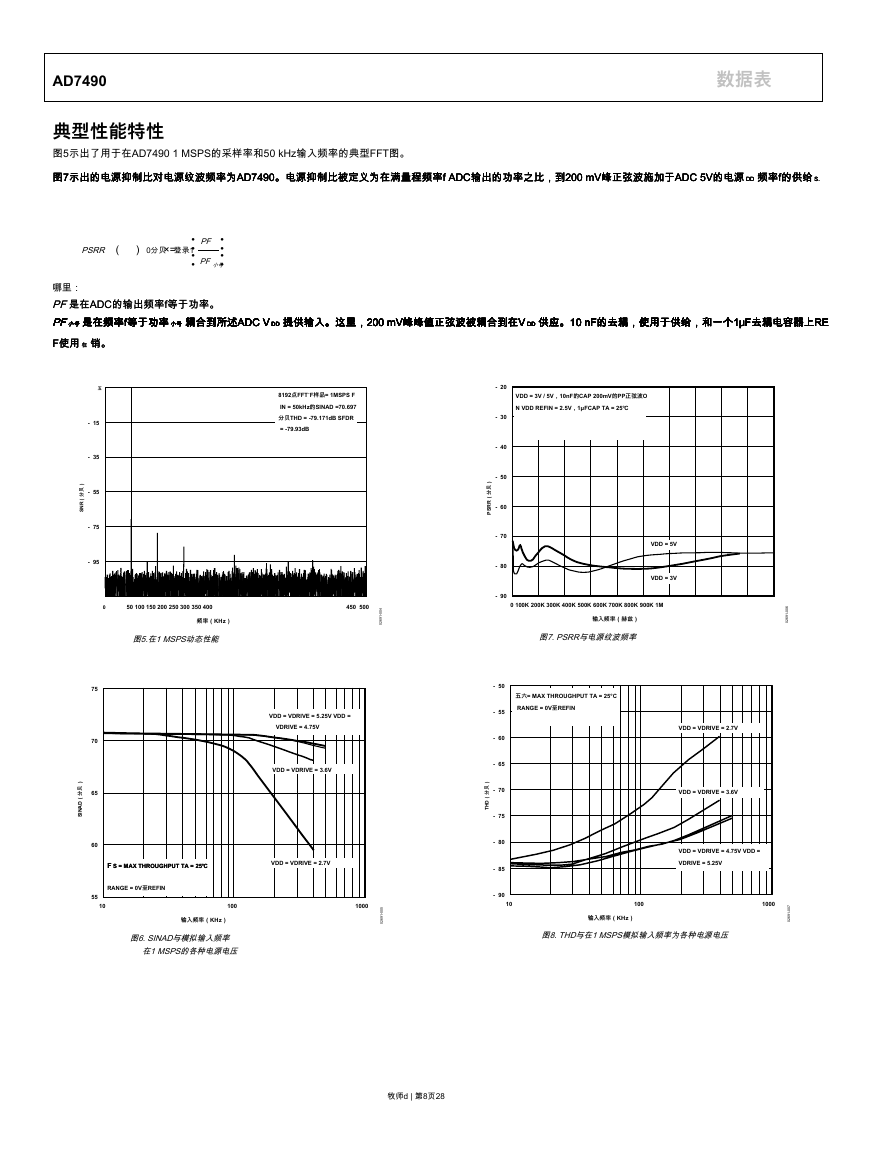

图5示出了用于在AD7490 1 MSPS的采样率和50 kHz输入频率的典型FFT图。

数据表

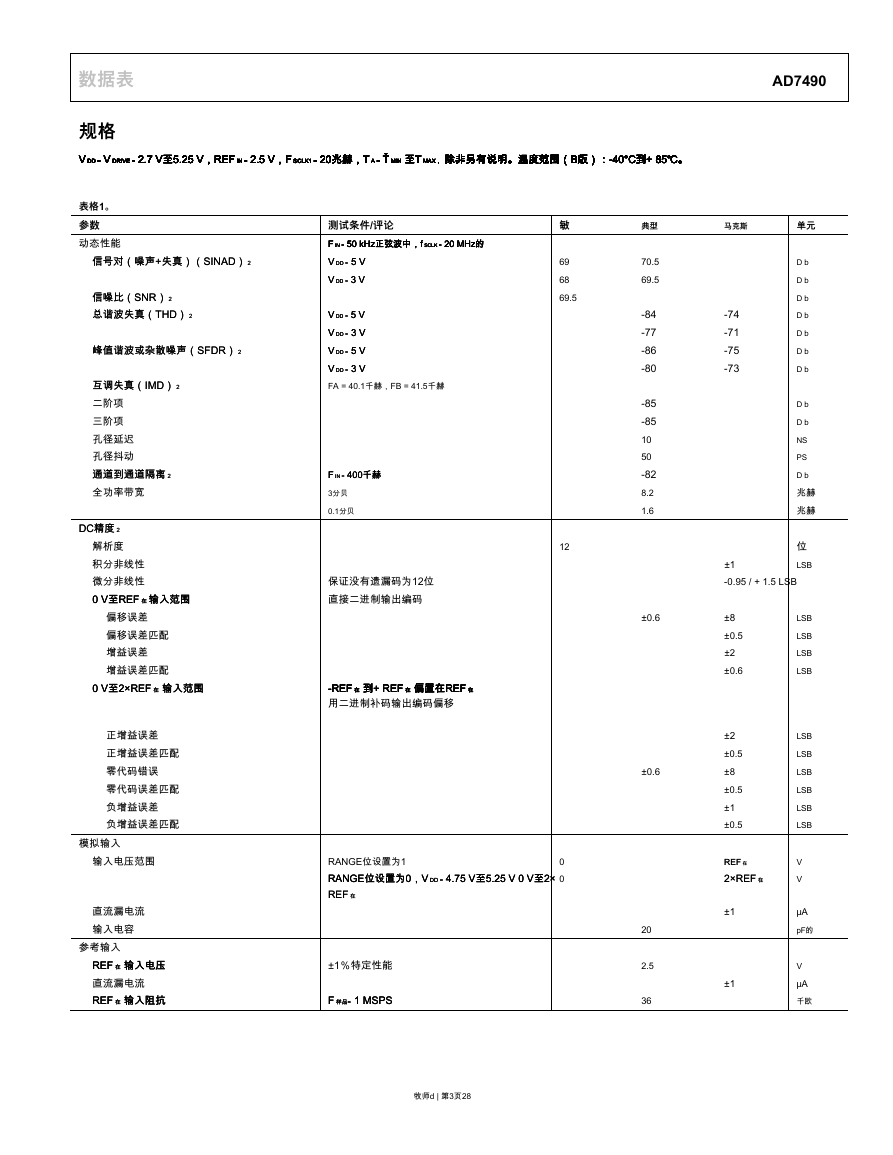

图7示出的电源抑制比对电源纹波频率为AD7490。电源抑制比被定义为在满量程频率f ADC输出的功率之比,到200 mV峰正弦波施加于ADC 5V的电源 DD 频率f的供给 S.

图7示出的电源抑制比对电源纹波频率为AD7490。电源抑制比被定义为在满量程频率f ADC输出的功率之比,到200 mV峰正弦波施加于ADC 5V的电源 DD 频率f的供给 S.

图7示出的电源抑制比对电源纹波频率为AD7490。电源抑制比被定义为在满量程频率f ADC输出的功率之比,到200 mV峰正弦波施加于ADC 5V的电源 DD 频率f的供给 S.

图7示出的电源抑制比对电源纹波频率为AD7490。电源抑制比被定义为在满量程频率f ADC输出的功率之比,到200 mV峰正弦波施加于ADC 5V的电源 DD 频率f的供给 S.

PSRR

( )

0分贝

×=

•

••

登录1

•

PF

•

••

小号PF

•

哪里:

PF 是在ADC的输出频率f等于功率。

PF 是在ADC的输出频率f等于功率。

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

PF 小号 是在频率f等于功率 小号 耦合到所述ADC V DD 提供输入。这里,200 mV峰峰值正弦波被耦合到在V DD 供应。10 nF的去耦,使用于供给,和一个1μF去耦电容器上RE

F使用 在 销。

F使用 在 销。

F使用 在 销。

8192点FFT˚F样品= 1MSPS F

IN = 50kHz的SINAD =70.697

分贝THD = -79.171dB SFDR

= -79.93dB

- 20

- 30

- 40

- 50

- 60

- 70

- 80

- 90

)

贝

分

(

R

R

S

P

VDD = 3V / 5V,10nF的CAP 200mV的PP正弦波O

N VDD REFIN = 2.5V,1μFCAP TA = 25℃

VDD = 5V

VDD = 3V

0

50 100 150 200 250 300 350 400

频率(KHz)

图5.在1 MSPS动态性能

450

500

4

0

0

-

1

9

6

2

0

0 100K 200K 300K 400K 500K 600K 700K 800K 900K 1M

输入频率(赫兹)

图7. PSRR与电源纹波频率

6

0

0

-

1

9

6

2

0

五

- 15

- 35

- 55

- 75

- 95

)

贝

分

(

R

N

S

75

70

65

60

)

贝

分

(

D

A

N

S

I

- 50

- 55

- 60

- 65

- 70

- 75

- 80

- 85

)

贝

分

(

D

H

T

- 90

10

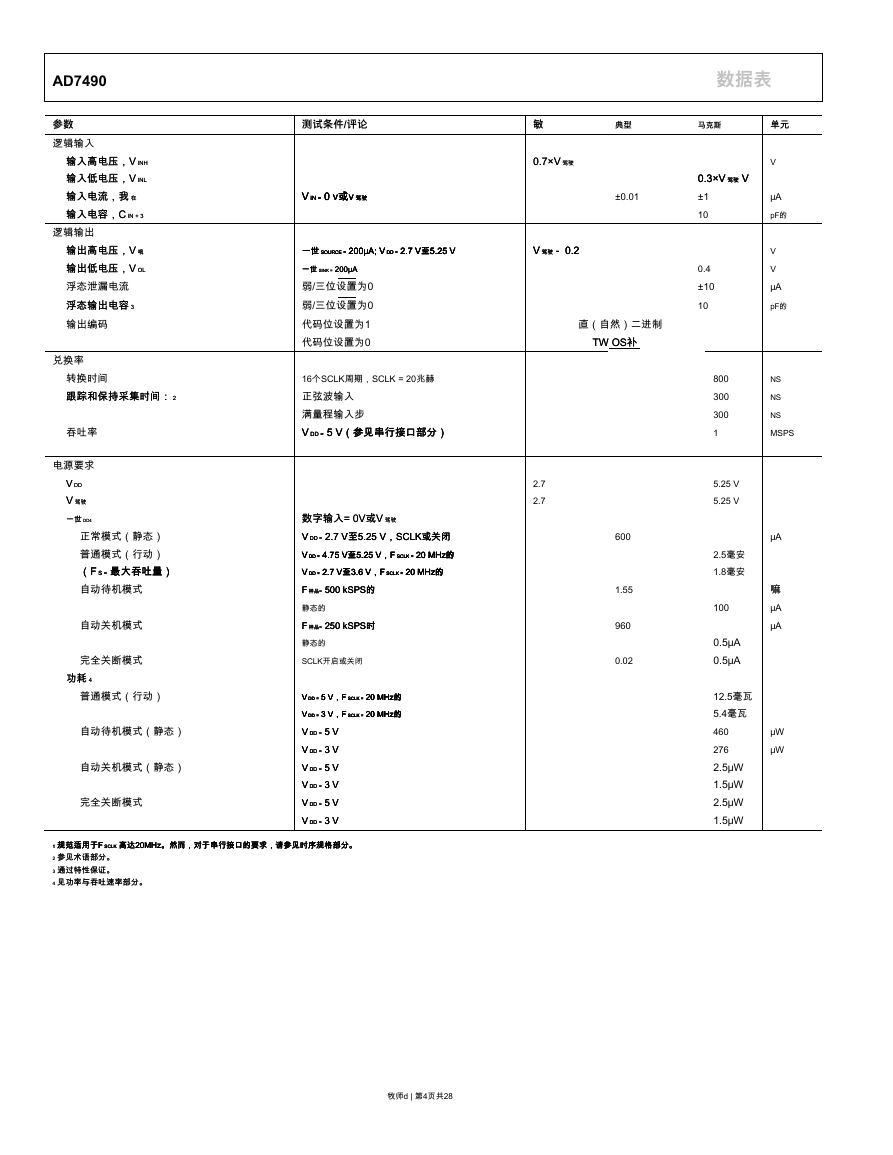

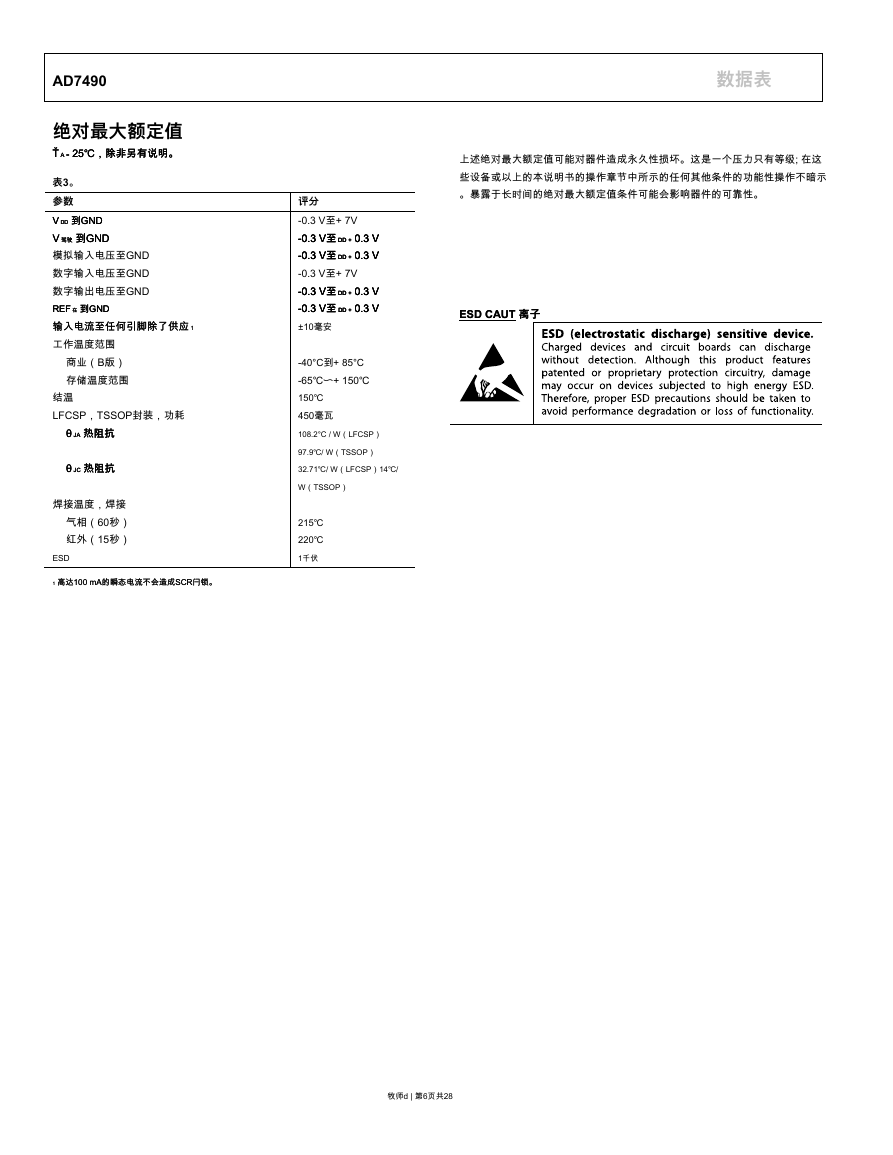

五六= MAX THROUGHPUT TA = 25°C

RANGE = 0V至REFIN

VDD = VDRIVE = 2.7V

VDD = VDRIVE = 3.6V

VDD = VDRIVE = 4.75V VDD =

VDRIVE = 5.25V

100

输入频率(KHz)

1000

7

0

0

-

1

9

6

2

0

图8. THD与在1 MSPS模拟输入频率为各种电源电压

VDD = VDRIVE = 5.25V VDD =

VDRIVE = 4.75V

VDD = VDRIVE = 3.6V

F S = MAX THROUGHPUT TA = 25℃

F S = MAX THROUGHPUT TA = 25℃

VDD = VDRIVE = 2.7V

RANGE = 0V至REFIN

55

10

100

输入频率(KHz)

1000

5

0

0

-

1

9

6

2

0

图6. SINAD与模拟输入频率

在1 MSPS的各种电源电压

牧师d | 第8页28

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc