ARM System Developer’s Guide Designing and Optimizing System Software

Copyright Page

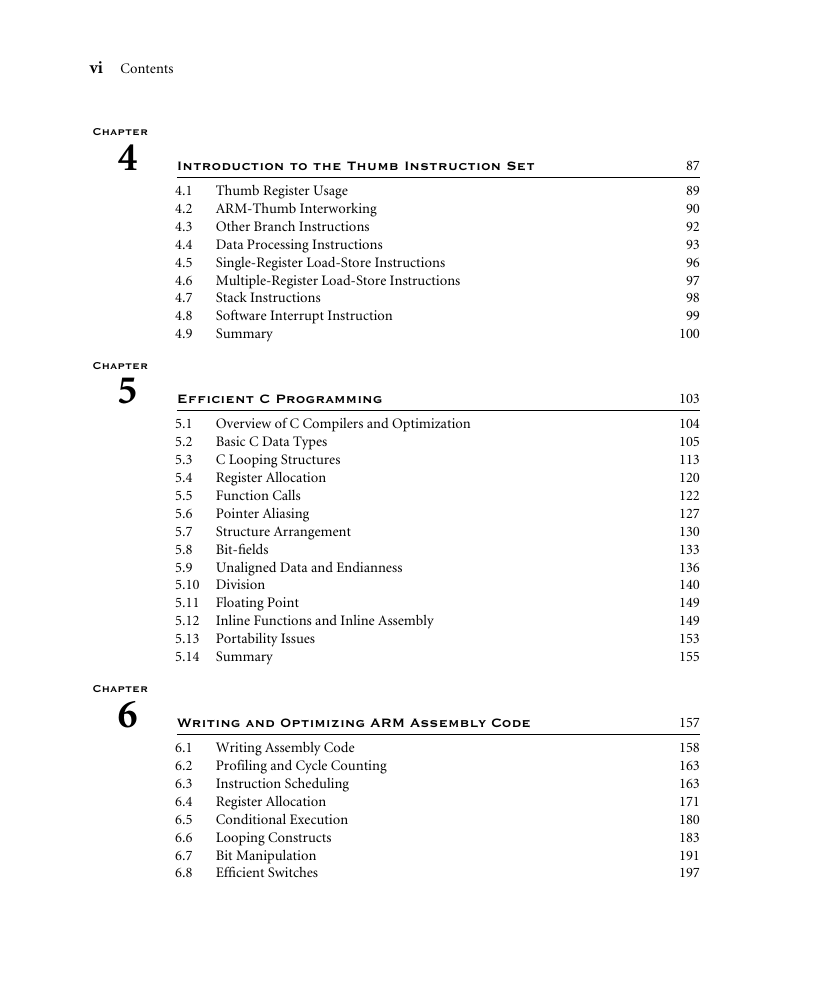

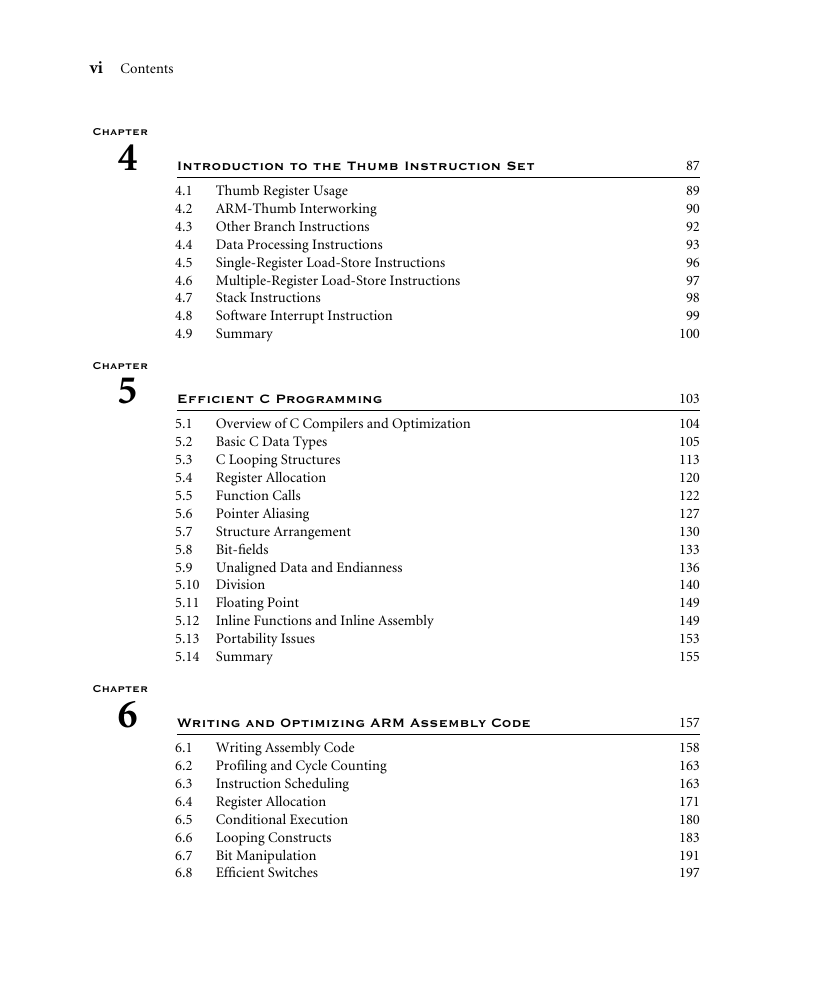

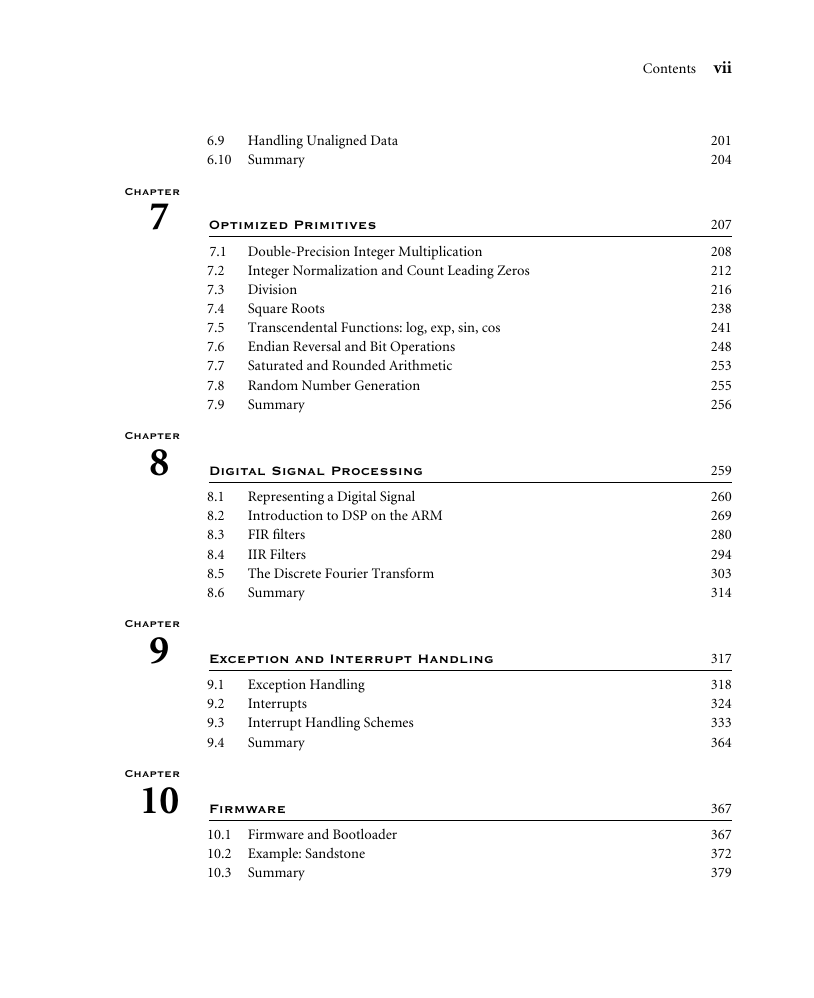

Contents

About the Authors

Preface

Chapter 1. ARM Embedded Systems

1.1 The RISC design philosophy

1.2 The ARM Design Philosophy

1.3 Embedded System Hardware

1.4 Embedded System Software

1.5 Summary

Chapter 2. ARM Processor Fundamentals

2.1 Registers

2.2 Current Program Status Register

2.3 Pipeline

2.4 Exceptions, Interrupts, and the Vector Table

2.5 Core Extensions

2.6 Architecture Revisions

2.7 ARM Processor Families

2.8 Summary

Chapter 3. Introduction to the ARM Instruction Set

3.1 Data Processing Instructions

3.2 Branch Instructions

3.3 Load-Store Instructions

3.4 Software Interrupt Instruction

3.5 Program Status Register Instructions

3.6 Loading Constants

3.7 ARMv5E Extensions

3.8 Conditional Execution

3.9 Summary

Chapter 4. Introduction to the Thumb Instruction Set

4.1 Thumb Register Usage

4.2 ARM-Thumb Interworking

4.3 Other Branch Instructions

4.4 Data Processing Instructions

4.5 Single-Register Load-Store Instructions

4.6 Multiple-Register Load-Store Instructions

4.7 Stack Instructions

4.8 Software Interrupt Instruction

4.9 Summary

Chapter 5. Efficient C Programming

5.1 Overview of C Compilers and Optimization

5.2 Basic C Data Types

5.3 C Looping Structures

5.4 Register Allocation

5.5 Function Calls

5.6 Pointer Aliasing

5.7 Structure Arrangement

5.8 Bit-fields

5.9 Unaligned Data and Endianness

5.10 Division

5.11 Floating Point

5.12 Inline Functions and Inline Assembly

5.13 Portability Issues

5.14 Summary

Chapter 6. Writing and Optimizing ARM Assembly Code

6.1 Writing Assembly Code

6.2 Profiling and Cycle Counting

6.3 Instruction Scheduling

6.4 Register Allocation

6.5 Conditional Execution

6.6 Looping Constructs

6.7 Bit Manipulation

6.8 Efficient Switches

6.9 Handling Unaligned Data

6.10 Summary

Chapter 7. Optimized Primitives

7.1 Double-Precision Integer Multiplication

7.2 Integer Normalization and Count Leading Zeros

7.3 Division

7.4 Square Roots

7.5 Transcendental Functions: log, exp, sin, cos

7.6 Endian Reversal and Bit Operations

7.7 Saturated and Rounded Arithmetic

7.8 Random Number Generation

7.9 Summary

Chapter 8. Digital Signal Processing

8.1 Representing a Digital Signal

8.2 Introduction to DSP on the ARM

8.3 FIR filters

8.4 IIR Filters

8.5 The Discrete Fourier Transform

8.6 Summary

Chapter 9. Exception and Interrupt Handling

9.1 Exception Handling

9.2 Interrupts

9.3 Interrupt Handling Schemes

9.4 Summary

Chapter 10. Firmware

10.1 Firmware and Bootloader

10.2 Example: Sandstone

10.3 Summary

Chapter 11. Embedded Operating Systems

11.1 Fundamental Components

11.2 Example: Simple Little Operating System

11.3 Summary

Chapter 12. Caches

12.1 The Memory Hierarchy and Cache Memory

12.2 Cache Architecture

12.3 Cache Policy

12.4 Coprocessor 15 and Caches

12.5 Flushing and Cleaning Cache Memory

12.6 Cache Lockdown

12.7 Caches and Software Performance

12.8 Summary

Chapter 13. Memory Protection Units

13.1 Protected Regions

13.2 Initializing the MPU, Caches, and Write Buffer

13.3 Demonstration of an MPU system

13.4 Summary

Chapter 14. Memory Management Units

14.1 Moving from an MPU to an MMU

14.2 How Virtual Memory Works

14.3 Details of the ARM MMU

14.4 Page Tables

14.5 The Translation Lookaside Buffer

14.6 Domains and Memory Access Permission

14.7 The Caches and Write Buffer

14.8 Coprocessor 15 and MMU Configuration

14.9 The Fast Context Switch Extension

14.10 Demonstration: A Small Virtual Memory System

14.11 The Demonstration as mmuSLOS

14.12 Summary

Chapter 15. The Future of the Architecture

15.1 Advanced DSP and SIMD Support in ARMv6

15.2 System and Multiprocessor Support Additions to ARMv6

15.3 ARMv6 Implementations

15.4 Future Technologies beyond ARMv6

15.5 Summary

Appendix A. ARM and Thumb Assembler Instructions

A.1 Using This Appendix

A.2 Syntax

A.3 Alphabetical List of ARM and Thumb Instructions

A.4 ARM Assembler Quick Reference

A.5 GNU Assembler Quick Reference

Appendix B. ARM and Thumb Instruction Encodings

B.1 ARM Instruction Set Encodings

B.2 Thumb Instruction Set Encodings

B.3 Program Status Registers

Appendix C. Processors and Architecture

C.1 ARM Naming Convention

C.2 Core and Architectures

Appendix D. Instruction Cycle Timings

D.1 Using the Instruction Cycle Timing Tables

D.2 ARM7TDMI Instruction Cycle Timings

D.3 ARM9TDMI Instruction Cycle Timings

D.4 StrongARM1 Instruction Cycle Timings

D.5 ARM9E Instruction Cycle Timings

D.6 ARM10E Instruction Cycle Timings

D.7 Intel XScale Instruction Cycle Timings

D.8 ARM11 Cycle Timings

Appendix E. Suggested Reading

E.1 ARM References

E.2 Algorithm References

E.3 Memory Management and Cache Architecture (Hardware Overview and Reference)

E.4 Operating System References

Index

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc