D

C

B

A

4

3

2

1

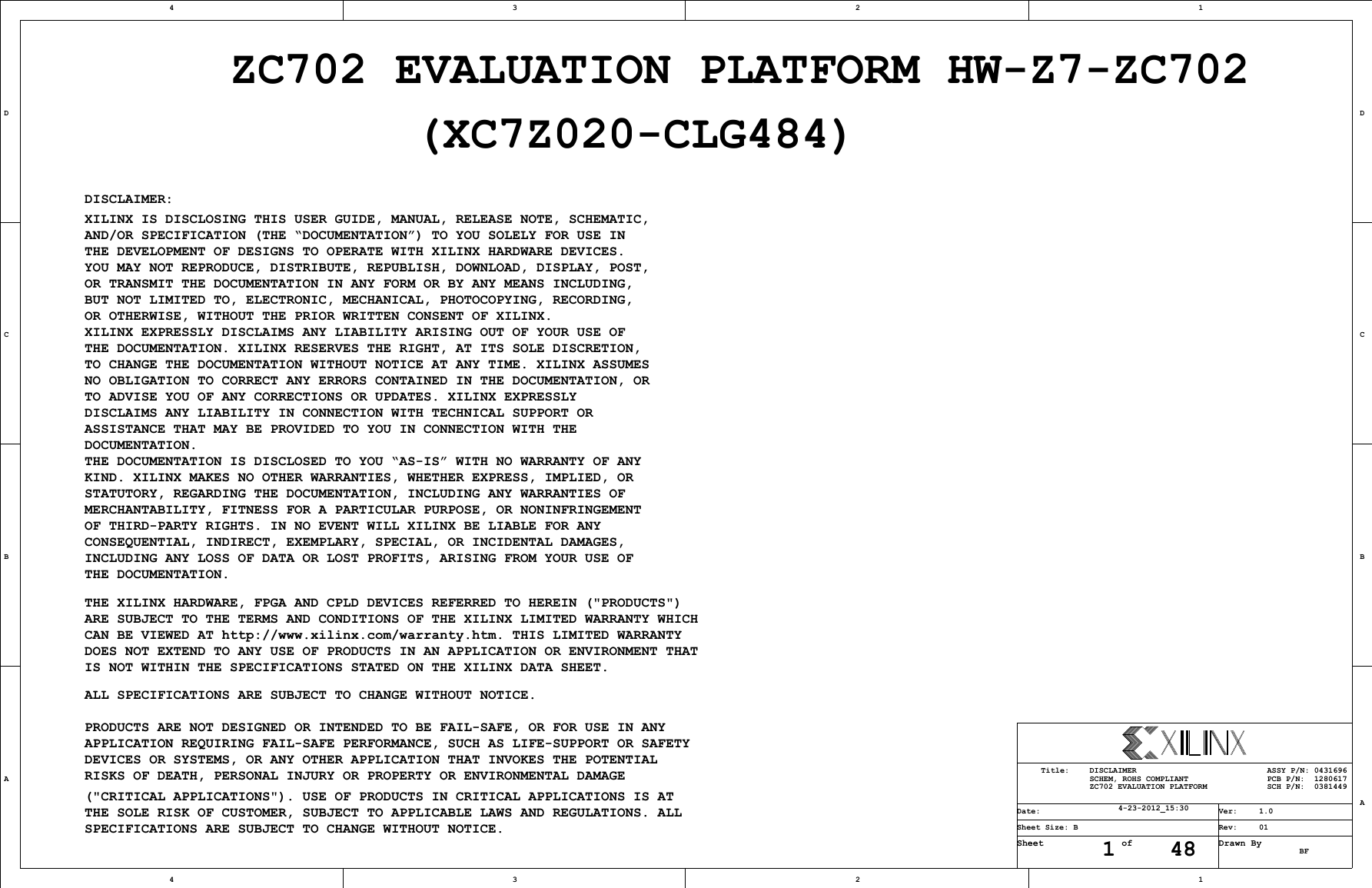

ZC702 EVALUATION PLATFORM HW-Z7-ZC702

(XC7Z020-CLG484)

DISCLAIMER:

XILINX IS DISCLOSING THIS USER GUIDE, MANUAL, RELEASE NOTE, SCHEMATIC,

AND/OR SPECIFICATION (THE “DOCUMENTATION”) TO YOU SOLELY FOR USE IN

THE DEVELOPMENT OF DESIGNS TO OPERATE WITH XILINX HARDWARE DEVICES.

YOU MAY NOT REPRODUCE, DISTRIBUTE, REPUBLISH, DOWNLOAD, DISPLAY, POST,

OR TRANSMIT THE DOCUMENTATION IN ANY FORM OR BY ANY MEANS INCLUDING,

BUT NOT LIMITED TO, ELECTRONIC, MECHANICAL, PHOTOCOPYING, RECORDING,

OR OTHERWISE, WITHOUT THE PRIOR WRITTEN CONSENT OF XILINX.

XILINX EXPRESSLY DISCLAIMS ANY LIABILITY ARISING OUT OF YOUR USE OF

THE DOCUMENTATION. XILINX RESERVES THE RIGHT, AT ITS SOLE DISCRETION,

TO CHANGE THE DOCUMENTATION WITHOUT NOTICE AT ANY TIME. XILINX ASSUMES

NO OBLIGATION TO CORRECT ANY ERRORS CONTAINED IN THE DOCUMENTATION, OR

TO ADVISE YOU OF ANY CORRECTIONS OR UPDATES. XILINX EXPRESSLY

DISCLAIMS ANY LIABILITY IN CONNECTION WITH TECHNICAL SUPPORT OR

ASSISTANCE THAT MAY BE PROVIDED TO YOU IN CONNECTION WITH THE

DOCUMENTATION.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS-IS” WITH NO WARRANTY OF ANY

KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR

STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF

MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT

OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY

CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES,

INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF

THE DOCUMENTATION.

THE XILINX HARDWARE, FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS")

ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH

CAN BE VIEWED AT http://www.xilinx.com/warranty.htm. THIS LIMITED WARRANTY

DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT

IS NOT WITHIN THE SPECIFICATIONS STATED ON THE XILINX DATA SHEET.

ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY

APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY

DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL

RISKS OF DEATH, PERSONAL INJURY OR PROPERTY OR ENVIRONMENTAL DAMAGE

("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT

THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS. ALL

SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

4

3

2

Title:

DISCLAIMER

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

1

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

�

4

3

2

1

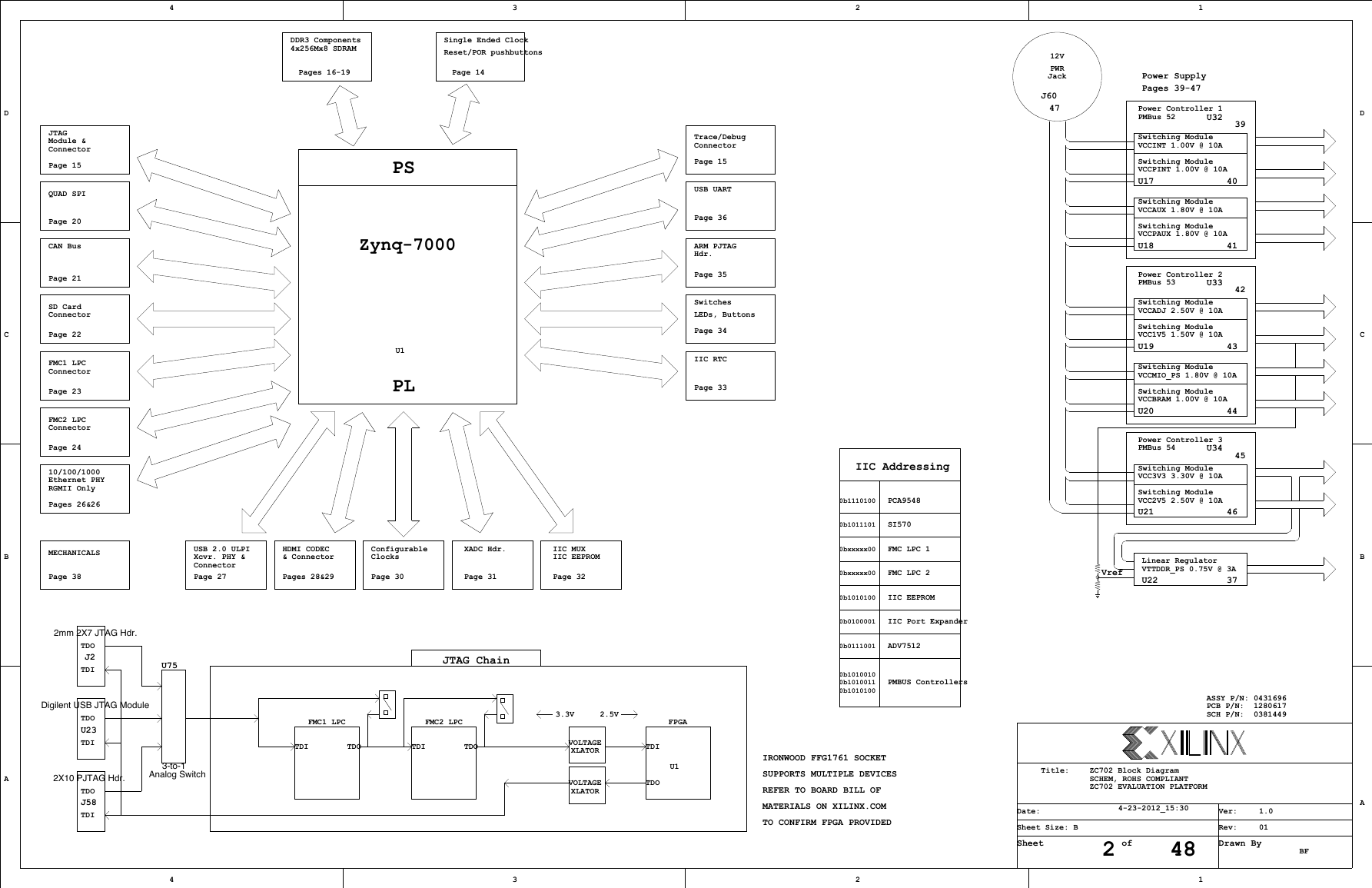

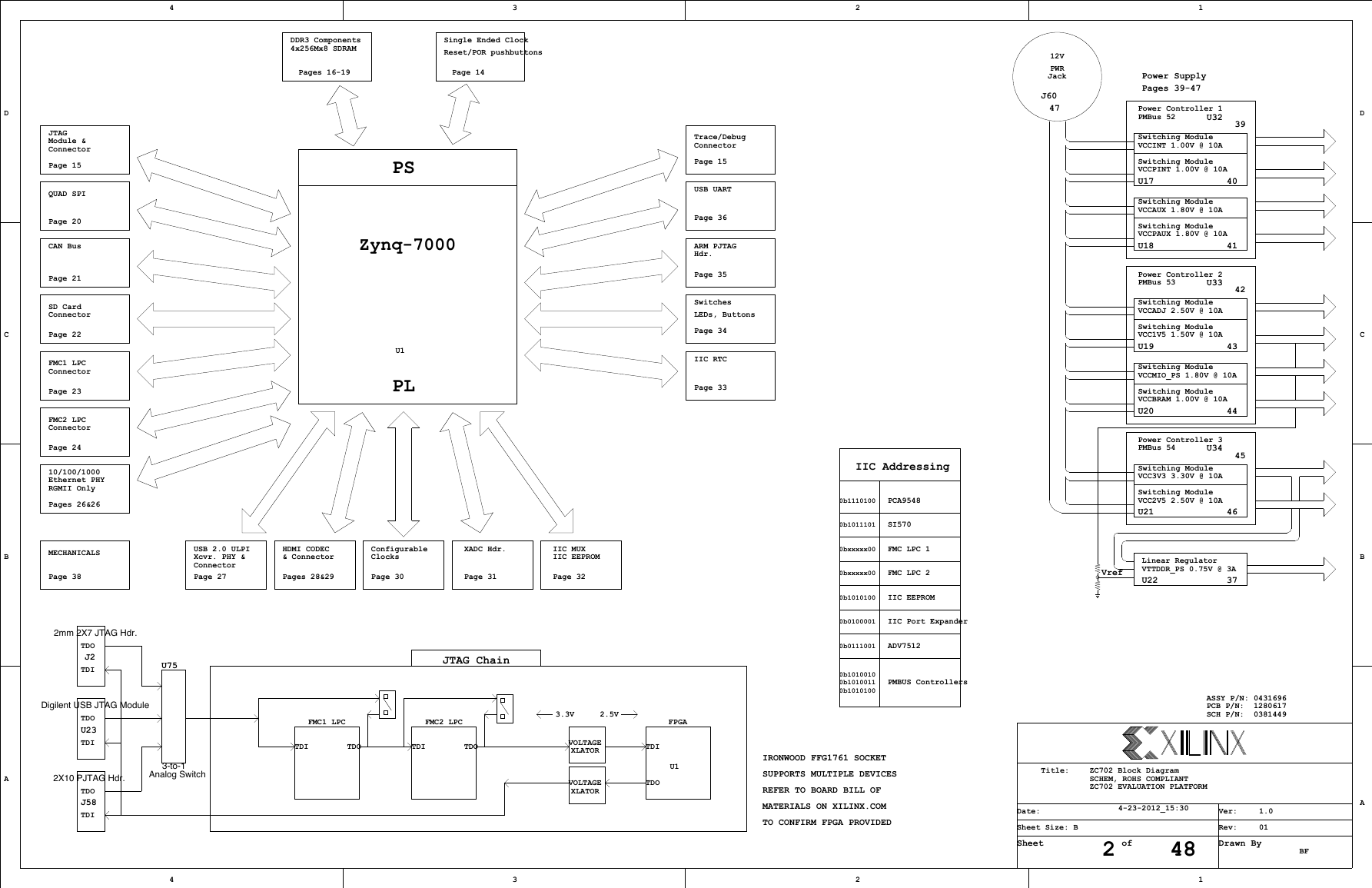

DDR3 Components

4x256Mx8 SDRAM

Single Ended Clock

Reset/POR pushbuttons

Pages 16-19

Page 14

PS

Zynq-7000

U1

PL

Trace/Debug

Connector

Page 15

USB UART

Page 36

ARM PJTAG

Hdr.

Page 35

Switches

LEDs, Buttons

Page 34

IIC RTC

Page 33

D

JTAG

Module &

Connector

Page 15

QUAD SPI

Page 20

CAN Bus

Page 21

SD Card

Connector

C

Page 22

FMC1 LPC

Connector

Page 23

FMC2 LPC

Connector

Page 24

10/100/1000

Ethernet PHY

RGMII Only

Pages 26&26

B

MECHANICALS

Page 38

USB 2.0 ULPI

Xcvr. PHY &

Connector

Page 27

HDMI CODEC

& Connector

Configurable

Clocks

XADC Hdr.

IIC MUX

IIC EEPROM

Pages 28&29

Page 30

Page 31

Page 32

12V

PWR

Jack

J60

47

Power Supply

Pages 39-47

Power Controller 1

U32

PMBus 52

Switching Module

VCCINT 1.00V @ 10A

39

Switching Module

VCCPINT 1.00V @ 10A

U17

40

Switching Module

VCCAUX 1.80V @ 10A

Switching Module

VCCPAUX 1.80V @ 10A

U18

41

Power Controller 2

U33

PMBus 53

Switching Module

VCCADJ 2.50V @ 10A

42

Switching Module

VCC1V5 1.50V @ 10A

U19

43

Switching Module

VCCMIO_PS 1.80V @ 10A

Switching Module

VCCBRAM 1.00V @ 10A

U20

44

Power Controller 3

U34

PMBus 54

Switching Module

VCC3V3 3.30V @ 10A

45

Switching Module

VCC2V5 2.50V @ 10A

U21

46

Vref

Linear Regulator

VTTDDR_PS 0.75V @ 3A

U22

37

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Title:

ZC702 Block Diagram

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

2

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

IIC Addressing

0b1110100

PCA9548

0b1011101

SI570

0bxxxxx00

FMC LPC 1

0bxxxxx00

FMC LPC 2

0b1010100

IIC EEPROM

0b0100001

IIC Port Expander

0b0111001

ADV7512

0b1010010

0b1010011

0b1010100

PMBUS Controllers

2mm 2X7 JTAG Hdr.

TDO

J2

TDI

U75

Digilent USB JTAG Module

TDO

U23

TDI

A

2X10 PJTAG Hdr.

3-to-1

Analog Switch

TDO

J58

TDI

JTAG Chain

FMC1 LPC

FMC2 LPC

TDI

TDO

TDI

TDO

3.3V

2.5V

VOLTAGE

XLATOR

VOLTAGE

XLATOR

FPGA

U1

TDI

TDO

IRONWOOD FFG1761 SOCKET

SUPPORTS MULTIPLE DEVICES

REFER TO BOARD BILL OF

MATERIALS ON XILINX.COM

TO CONFIRM FPGA PROVIDED

4

3

2

�

D

C

B

A

4

SOC_IRON_CL484

BANK 0

XC7Z020CLG484

3

VCC2V5

1

2

R177

10.0K

1/10W

1%

DXN_0_N12

VCCADC_0_K11

GNDADC_0_K12

DXP_0_N11

VREFN_0_L12

VREFP_0_M11

VP_0_L11

VN_0_M12

VCCBATT_0_G9

RSVDGND_G10_G10

TCK_0_G11

TMS_0_G12

TDO_0_G14

TDI_0_H13

INIT_B_0_T14

PROGRAM_B_0_T11

CFGBVS_0_T13

DONE_0_T12

RSVDVCC_T7_T7

RSVDVCC_T10_T10

RSVDVCC_T8_T8

N12

K11

K12

N11

L12

M11

L11

M12

G9

G10

G11

G12

G14

H13

T14

T11

T13

T12

T7

T10

T8

VCC2V5_PL

R12

VCCO_0_R12

U1

VCC3V3

SOC_IRON_CL484

L

E

D

-

G

R

N

-

S

M

T

1%

1/10W

261

R279

VCC2V5

2

D

S

3

1

2

1

1

2

GND

C1

0.1UF

25V

X5R

1

2

C2

0.1UF

25V

X5R

XADC_AGND

GND

31

31

31

31

31

31

3

15

15

15

15

3

34

3,32

XADC_DXN

XADC_VCC

XADC_DXP

XADC_VREFP

XADC_VP_R

XADC_VN_R

FPGA_VBATT

FPGA_TCK_BUF

FPGA_TMS_BUF

JTAG_TDO_BUF

FPGA_TDI_BUF

FPGA_INIT_B

FPGA_PROG_B

FPGA_DONE

J5

1

2

2

1

VCC2V5

5%

1/10W

0

R433

2

5%

1/10W

0

R434

1

2

5%

1/10W

0

R435

1

2

1

R430

DNP

DNP

DNP

2

1 R431

1

DNP

DNP

DNP

2

R432

DNP

DNP

DNP

1

2

GND

1 R278

261

1/10W

1%

2

3,32

FPGA_DONE

1

3

Q1

2

NDS331N

460MW

GND

3

FPGA_VBATT

VCCAUX

C

N

BAS40-04

1

3

40V

200MW

2

D8

1 R2

4.7K

1/10W

5%

2

B1

1

2

GND

4

TS518FE_FL35E

TS518FE_FL35E

VCC2V5

VCC2V5

1

2

R1

4.7K

1/10W

5%

SN74AVC1T45

6

4

5

VCCB

B

DIR

VCCA

A

GND

1

3

2

3

FPGA_INIT_B

GND

U37

SC70_6

GND

1%

3

1 2

1/10W

VCC3V3

R276

261

Zynq Bank 0

21

1/10W

1%

R277

261

DS2

VCC3V3

RED

4

1

3

2

GRN

LED-GRN-RED

GND

2

Title:

Zynq Bank 0

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

3

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

�

D

C

B

A

4

3

2

1

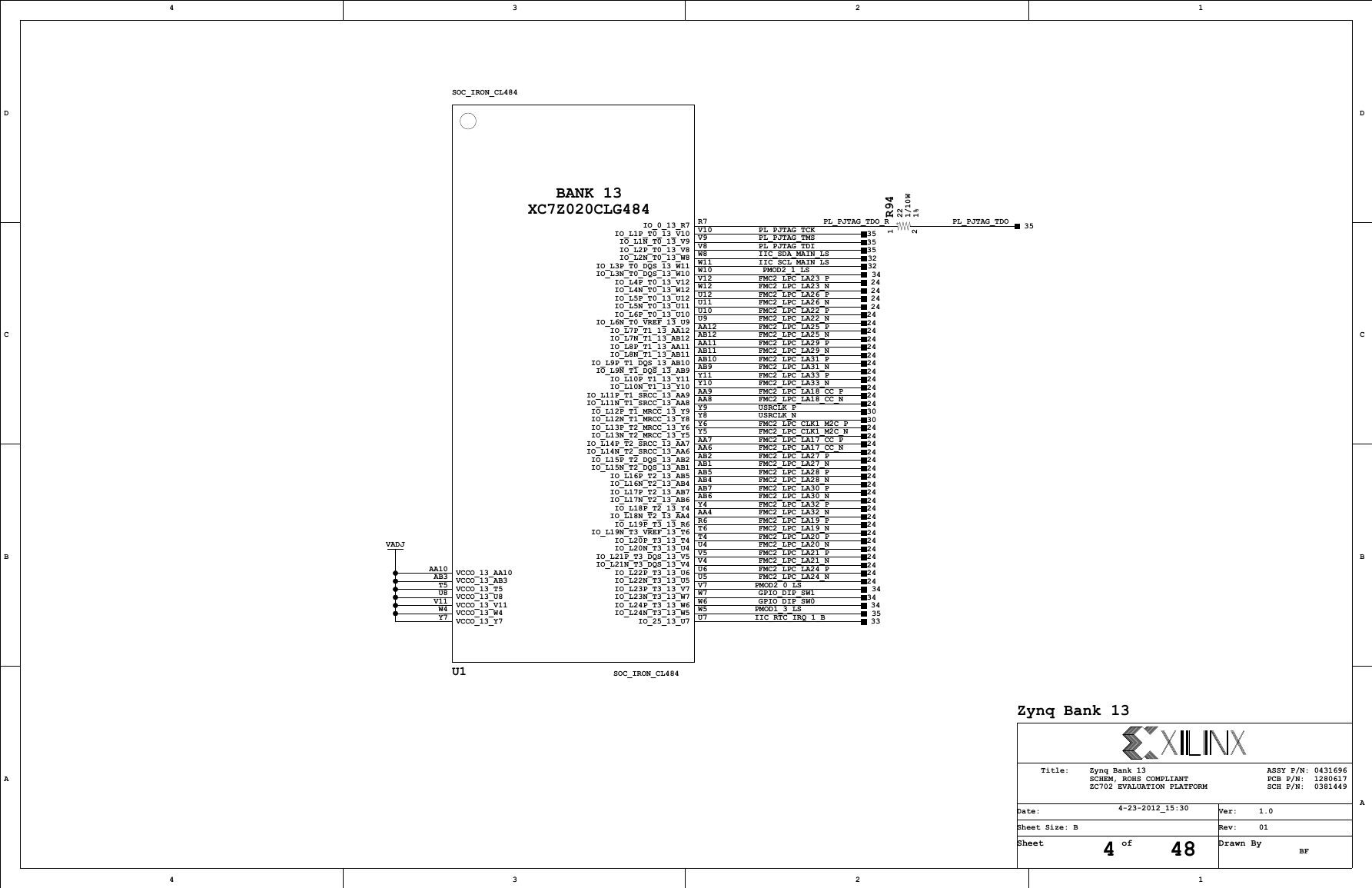

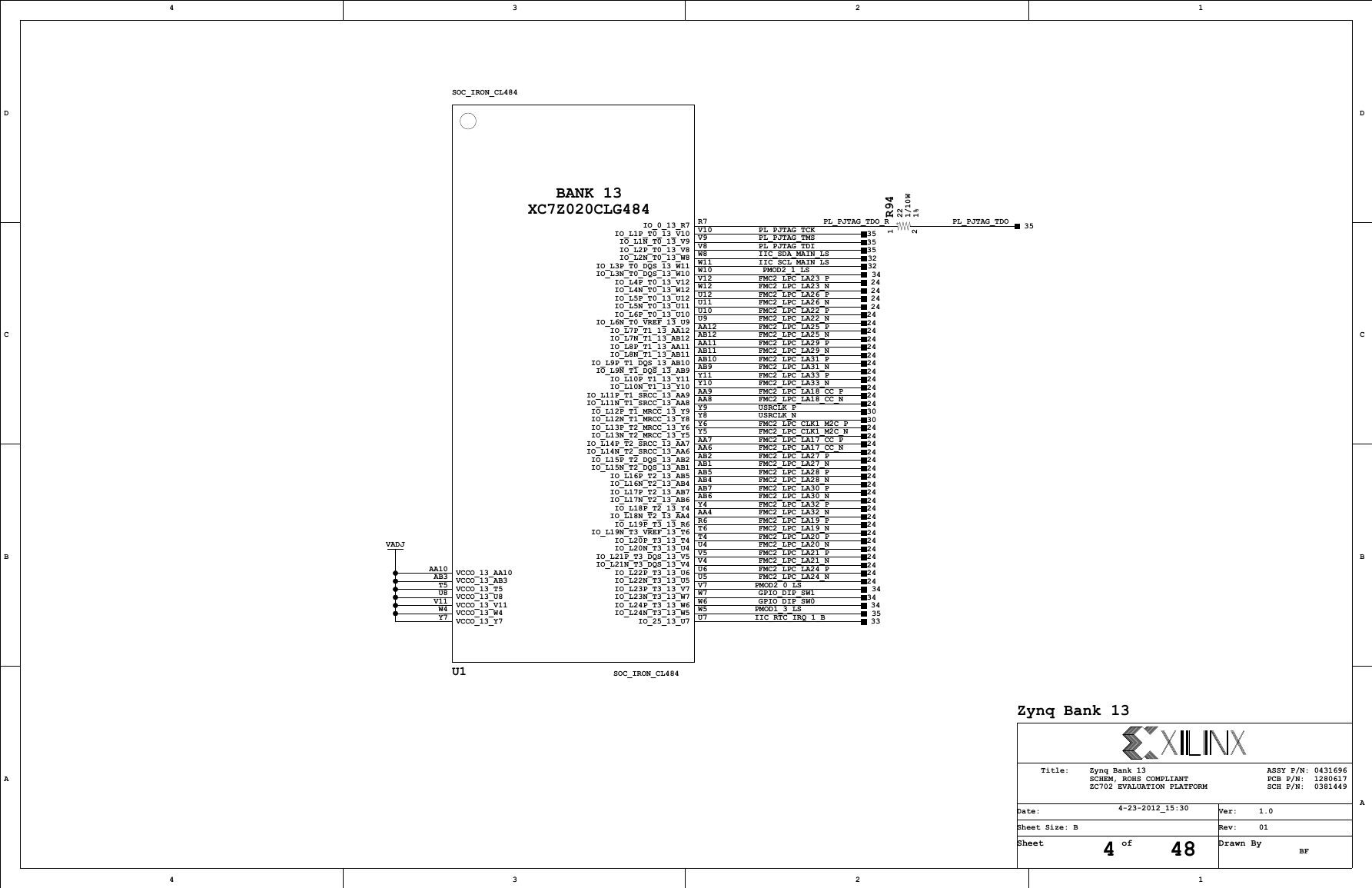

SOC_IRON_CL484

BANK 13

XC7Z020CLG484

IO_0_13_R7

IO_L1P_T0_13_V10

IO_L1N_T0_13_V9

IO_L2P_T0_13_V8

IO_L2N_T0_13_W8

IO_L3P_T0_DQS_13_W11

IO_L3N_T0_DQS_13_W10

IO_L4P_T0_13_V12

IO_L4N_T0_13_W12

IO_L5P_T0_13_U12

IO_L5N_T0_13_U11

IO_L6P_T0_13_U10

IO_L6N_T0_VREF_13_U9

IO_L7P_T1_13_AA12

IO_L7N_T1_13_AB12

IO_L8P_T1_13_AA11

IO_L8N_T1_13_AB11

IO_L9P_T1_DQS_13_AB10

IO_L9N_T1_DQS_13_AB9

IO_L10P_T1_13_Y11

IO_L10N_T1_13_Y10

IO_L11P_T1_SRCC_13_AA9

IO_L11N_T1_SRCC_13_AA8

IO_L12P_T1_MRCC_13_Y9

IO_L12N_T1_MRCC_13_Y8

IO_L13P_T2_MRCC_13_Y6

IO_L13N_T2_MRCC_13_Y5

IO_L14P_T2_SRCC_13_AA7

IO_L14N_T2_SRCC_13_AA6

IO_L15P_T2_DQS_13_AB2

IO_L15N_T2_DQS_13_AB1

IO_L16P_T2_13_AB5

IO_L16N_T2_13_AB4

IO_L17P_T2_13_AB7

IO_L17N_T2_13_AB6

IO_L18P_T2_13_Y4

IO_L18N_T2_13_AA4

IO_L19P_T3_13_R6

IO_L19N_T3_VREF_13_T6

IO_L20P_T3_13_T4

IO_L20N_T3_13_U4

IO_L21P_T3_DQS_13_V5

IO_L21N_T3_DQS_13_V4

IO_L22P_T3_13_U6

IO_L22N_T3_13_U5

IO_L23P_T3_13_V7

IO_L23N_T3_13_W7

IO_L24P_T3_13_W6

IO_L24N_T3_13_W5

IO_25_13_U7

R7

V10

V9

V8

W8

W11

W10

V12

W12

U12

U11

U10

U9

AA12

AB12

AA11

AB11

AB10

AB9

Y11

Y10

AA9

AA8

Y9

Y8

Y6

Y5

AA7

AA6

AB2

AB1

AB5

AB4

AB7

AB6

Y4

AA4

R6

T6

T4

U4

V5

V4

U6

U5

V7

W7

W6

W5

U7

VADJ

AA10

AB3

T5

U8

V11

W4

Y7

VCCO_13_AA10

VCCO_13_AB3

VCCO_13_T5

VCCO_13_U8

VCCO_13_V11

VCCO_13_W4

VCCO_13_Y7

U1

SOC_IRON_CL484

PL_PJTAG_TDO_R

2

2

%

1

PL_PJTAG_TDO

35

PL_PJTAG_TCK

PL_PJTAG_TMS

PL_PJTAG_TDI

IIC_SDA_MAIN_LS

IIC_SCL_MAIN_LS

PMOD2_1_LS

FMC2_LPC_LA23_P

FMC2_LPC_LA23_N

FMC2_LPC_LA26_P

FMC2_LPC_LA26_N

FMC2_LPC_LA22_P

FMC2_LPC_LA22_N

FMC2_LPC_LA25_P

FMC2_LPC_LA25_N

FMC2_LPC_LA29_P

FMC2_LPC_LA29_N

FMC2_LPC_LA31_P

FMC2_LPC_LA31_N

FMC2_LPC_LA33_P

FMC2_LPC_LA33_N

FMC2_LPC_LA18_CC_P

FMC2_LPC_LA18_CC_N

USRCLK_P

USRCLK_N

FMC2_LPC_CLK1_M2C_P

FMC2_LPC_CLK1_M2C_N

FMC2_LPC_LA17_CC_P

FMC2_LPC_LA17_CC_N

FMC2_LPC_LA27_P

FMC2_LPC_LA27_N

FMC2_LPC_LA28_P

FMC2_LPC_LA28_N

FMC2_LPC_LA30_P

FMC2_LPC_LA30_N

FMC2_LPC_LA32_P

FMC2_LPC_LA32_N

FMC2_LPC_LA19_P

FMC2_LPC_LA19_N

FMC2_LPC_LA20_P

FMC2_LPC_LA20_N

FMC2_LPC_LA21_P

FMC2_LPC_LA21_N

FMC2_LPC_LA24_P

FMC2_LPC_LA24_N

PMOD2_0_LS

GPIO_DIP_SW1

GPIO_DIP_SW0

PMOD1_3_LS

IIC_RTC_IRQ_1_B

4

9

R

W

0

1

/

1

21

35

35

35

32

32

34

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

30

30

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

24

34

34

34

35

33

4

3

2

Zynq Bank 13

Title:

Zynq Bank 13

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

4

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

�

D

C

B

A

4

3

2

1

SOC_IRON_CL484

BANK 33

XC7Z020CLG484

IO_0_33_U19

IO_L1P_T0_33_T21

IO_L1N_T0_33_U21

IO_L2P_T0_33_T22

IO_L2N_T0_33_U22

IO_L3P_T0_DQS_33_V22

IO_L3N_T0_DQS_33_W22

IO_L4P_T0_33_W20

IO_L4N_T0_33_W21

IO_L5P_T0_33_U20

IO_L5N_T0_33_V20

IO_L6P_T0_33_V18

IO_L6N_T0_VREF_33_V19

IO_L7P_T1_33_AA22

IO_L7N_T1_33_AB22

IO_L8P_T1_33_AA21

IO_L8N_T1_33_AB21

IO_L9P_T1_DQS_33_Y20

IO_L9N_T1_DQS_33_Y21

IO_L10P_T1_33_AB19

IO_L10N_T1_33_AB20

IO_L11P_T1_SRCC_33_Y19

IO_L11N_T1_SRCC_33_AA19

IO_L12P_T1_MRCC_33_Y18

IO_L12N_T1_MRCC_33_AA18

IO_L13P_T2_MRCC_33_W17

IO_L13N_T2_MRCC_33_W18

IO_L14P_T2_SRCC_33_W16

IO_L14N_T2_SRCC_33_Y16

IO_L15P_T2_DQS_33_U15

IO_L15N_T2_DQS_33_U16

IO_L16P_T2_33_U17

IO_L16N_T2_33_V17

IO_L17P_T2_33_AA17

IO_L17N_T2_33_AB17

IO_L18P_T2_33_AA16

IO_L18N_T2_33_AB16

IO_L19P_T3_33_V14

IO_L19N_T3_VREF_33_V15

IO_L20P_T3_33_V13

IO_L20N_T3_33_W13

IO_L21P_T3_DQS_33_W15

IO_L21N_T3_DQS_33_Y15

IO_L22P_T3_33_Y14

IO_L22N_T3_33_AA14

IO_L23P_T3_33_Y13

IO_L23N_T3_33_AA13

IO_L24P_T3_33_AB14

IO_L24N_T3_33_AB15

IO_25_33_U14

U19

T21

U21

T22

U22

V22

W22

W20

W21

U20

V20

V18

V19

AA22

AB22

AA21

AB21

Y20

Y21

AB19

AB20

Y19

AA19

Y18

AA18

W17

W18

W16

Y16

U15

U16

U17

V17

AA17

AB17

AA16

AB16

V14

V15

V13

W13

W15

Y15

Y14

AA14

Y13

AA13

AB14

AB15

U14

HDMI_R_D12

29

FMC2_LPC_LA07_P

24

FMC2_LPC_LA07_N

24

FMC2_LPC_LA14_P

24

FMC2_LPC_LA14_N

24

FMC2_LPC_LA13_P

24

FMC2_LPC_LA13_N

24

HDMI_R_D9

29

HDMI_R_D8

29

HDMI_R_D7

29

HDMI_R_D6

29

HDMI_R_D5

29

HDMI_R_D4

29

HDMI_R_D3

29

HDMI_R_D2

29

HDMI_R_D1

29

HDMI_R_D0

29

FMC2_LPC_LA10_P

24

FMC2_LPC_LA10_N

24

FMC2_LPC_LA05_P

24

FMC2_LPC_LA05_N

24

FMC2_LPC_LA00_CC_P

FMC2_LPC_LA00_CC_N 24

24

FMC2_LPC_CLK0_M2C_P

24

FMC2_LPC_CLK0_M2C_N

24

PMOD1_2_LS

HDMI_R_D10

29

FMC2_LPC_LA01_CC_P

24

FMC2_LPC_LA01_CC_N 24

FMC2_LPC_LA09_P

24

FMC2_LPC_LA09_N

24

FMC2_LPC_LA06_P

24

FMC2_LPC_LA06_N

24

FMC2_LPC_LA08_P

24

FMC2_LPC_LA08_N

24

FMC2_LPC_LA03_P

24

FMC2_LPC_LA03_N

24

FMC2_LPC_LA02_P

24

FMC2_LPC_LA02_N

24

FMC2_LPC_LA04_P

24

FMC2_LPC_LA04_N

24

FMC2_LPC_LA12_P

24

FMC2_LPC_LA12_N

24

FMC2_LPC_LA11_P

24

FMC2_LPC_LA11_N

24

FMC2_LPC_LA15_P

24

FMC2_LPC_LA15_N

24

FMC2_LPC_LA16_P

24

FMC2_LPC_LA16_N

24

HDMI_INT

28

35

VADJ

AA20

AB13

U18

V21

W14

Y17

VCCO_33_AA20

VCCO_33_AB13

VCCO_33_U18

VCCO_33_V21

VCCO_33_W14

VCCO_33_Y17

U1

SOC_IRON_CL484

4

3

2

Zynq Bank 33

Title:

Zynq Bank 33

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

5

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

�

D

C

B

A

4

3

2

1

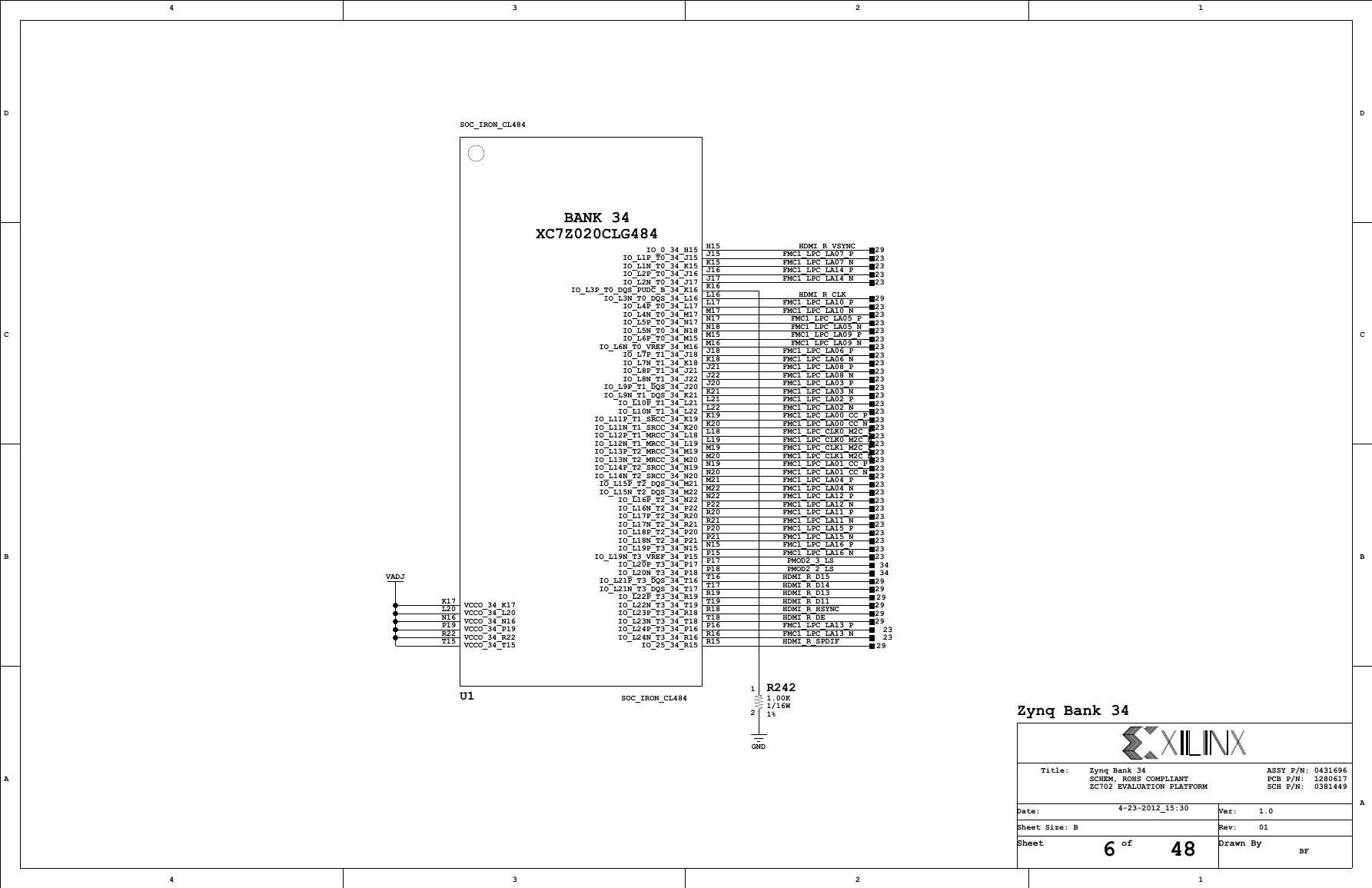

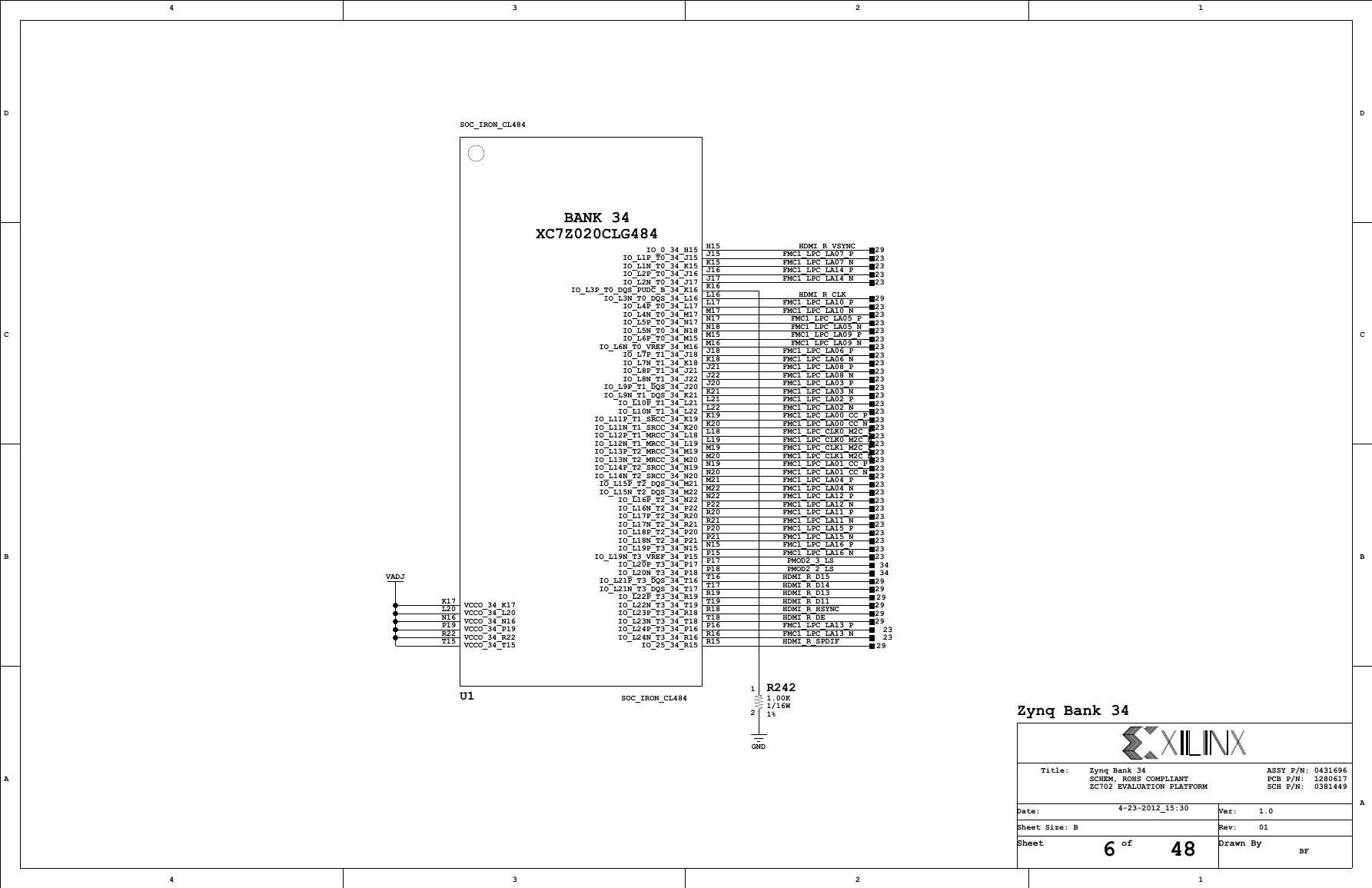

SOC_IRON_CL484

BANK 34

XC7Z020CLG484

IO_0_34_H15

IO_L1P_T0_34_J15

IO_L1N_T0_34_K15

IO_L2P_T0_34_J16

IO_L2N_T0_34_J17

IO_L3P_T0_DQS_PUDC_B_34_K16

IO_L3N_T0_DQS_34_L16

IO_L4P_T0_34_L17

IO_L4N_T0_34_M17

IO_L5P_T0_34_N17

IO_L5N_T0_34_N18

IO_L6P_T0_34_M15

IO_L6N_T0_VREF_34_M16

IO_L7P_T1_34_J18

IO_L7N_T1_34_K18

IO_L8P_T1_34_J21

IO_L8N_T1_34_J22

IO_L9P_T1_DQS_34_J20

IO_L9N_T1_DQS_34_K21

IO_L10P_T1_34_L21

IO_L10N_T1_34_L22

IO_L11P_T1_SRCC_34_K19

IO_L11N_T1_SRCC_34_K20

IO_L12P_T1_MRCC_34_L18

IO_L12N_T1_MRCC_34_L19

IO_L13P_T2_MRCC_34_M19

IO_L13N_T2_MRCC_34_M20

IO_L14P_T2_SRCC_34_N19

IO_L14N_T2_SRCC_34_N20

IO_L15P_T2_DQS_34_M21

IO_L15N_T2_DQS_34_M22

IO_L16P_T2_34_N22

IO_L16N_T2_34_P22

IO_L17P_T2_34_R20

IO_L17N_T2_34_R21

IO_L18P_T2_34_P20

IO_L18N_T2_34_P21

IO_L19P_T3_34_N15

IO_L19N_T3_VREF_34_P15

IO_L20P_T3_34_P17

IO_L20N_T3_34_P18

IO_L21P_T3_DQS_34_T16

IO_L21N_T3_DQS_34_T17

IO_L22P_T3_34_R19

IO_L22N_T3_34_T19

IO_L23P_T3_34_R18

IO_L23N_T3_34_T18

IO_L24P_T3_34_P16

IO_L24N_T3_34_R16

IO_25_34_R15

H15

J15

K15

J16

J17

K16

L16

L17

M17

N17

N18

M15

M16

J18

K18

J21

J22

J20

K21

L21

L22

K19

K20

L18

L19

M19

M20

N19

N20

M21

M22

N22

P22

R20

R21

P20

P21

N15

P15

P17

P18

T16

T17

R19

T19

R18

T18

P16

R16

R15

VADJ

K17

L20

N16

P19

R22

T15

VCCO_34_K17

VCCO_34_L20

VCCO_34_N16

VCCO_34_P19

VCCO_34_R22

VCCO_34_T15

HDMI_R_VSYNC

FMC1_LPC_LA07_P

FMC1_LPC_LA07_N

FMC1_LPC_LA14_P

FMC1_LPC_LA14_N

29

23

23

23

23

HDMI_R_CLK

FMC1_LPC_LA10_P

FMC1_LPC_LA10_N

FMC1_LPC_LA05_P

FMC1_LPC_LA05_N

FMC1_LPC_LA09_P

FMC1_LPC_LA09_N

29

23

23

23

23

23

23

FMC1_LPC_LA06_P

23

FMC1_LPC_LA06_N

23

FMC1_LPC_LA08_P

23

FMC1_LPC_LA08_N

23

FMC1_LPC_LA03_P

23

FMC1_LPC_LA03_N

23

FMC1_LPC_LA02_P

23

FMC1_LPC_LA02_N

23

FMC1_LPC_LA00_CC_P 23

FMC1_LPC_LA00_CC_N 23

FMC1_LPC_CLK0_M2C_P 23

FMC1_LPC_CLK0_M2C_N 23

FMC1_LPC_CLK1_M2C_P 23

FMC1_LPC_CLK1_M2C_N 23

FMC1_LPC_LA01_CC_P

23

FMC1_LPC_LA01_CC_N 23

FMC1_LPC_LA04_P

23

FMC1_LPC_LA04_N

23

FMC1_LPC_LA12_P

23

FMC1_LPC_LA12_N

23

FMC1_LPC_LA11_P

23

FMC1_LPC_LA11_N

23

FMC1_LPC_LA15_P

23

FMC1_LPC_LA15_N

23

FMC1_LPC_LA16_P

23

FMC1_LPC_LA16_N

23

PMOD2_3_LS

PMOD2_2_LS

HDMI_R_D15

HDMI_R_D14

HDMI_R_D13

HDMI_R_D11

HDMI_R_HSYNC

HDMI_R_DE

FMC1_LPC_LA13_P

FMC1_LPC_LA13_N

HDMI_R_SPDIF

34

34

29

29

29

29

29

29

23

23

29

U1

SOC_IRON_CL484

1 R242

1.00K

1/16W

1%

2

GND

4

3

2

Zynq Bank 34

Title:

Zynq Bank 34

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

6

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

�

D

C

B

A

4

3

2

1

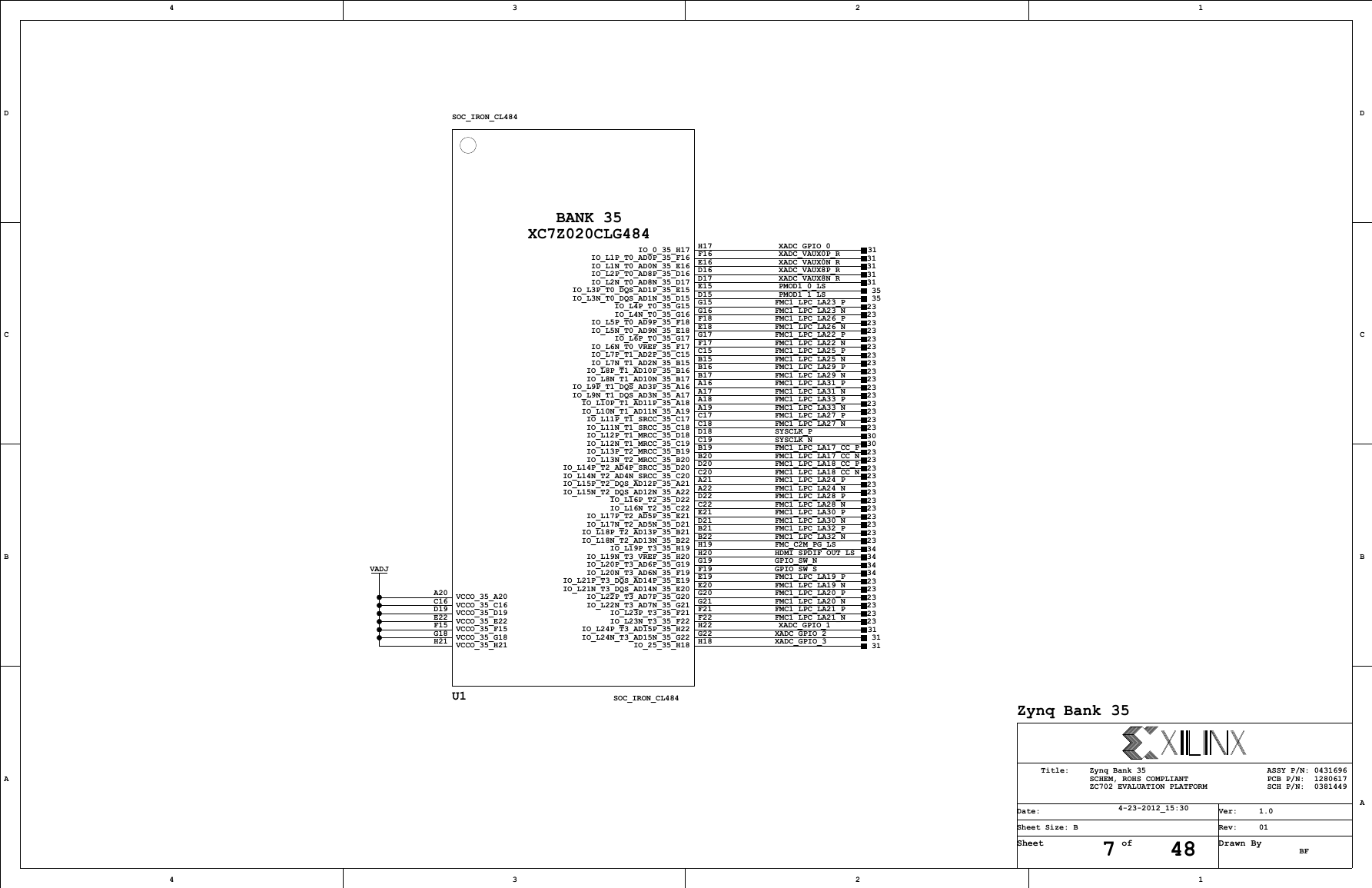

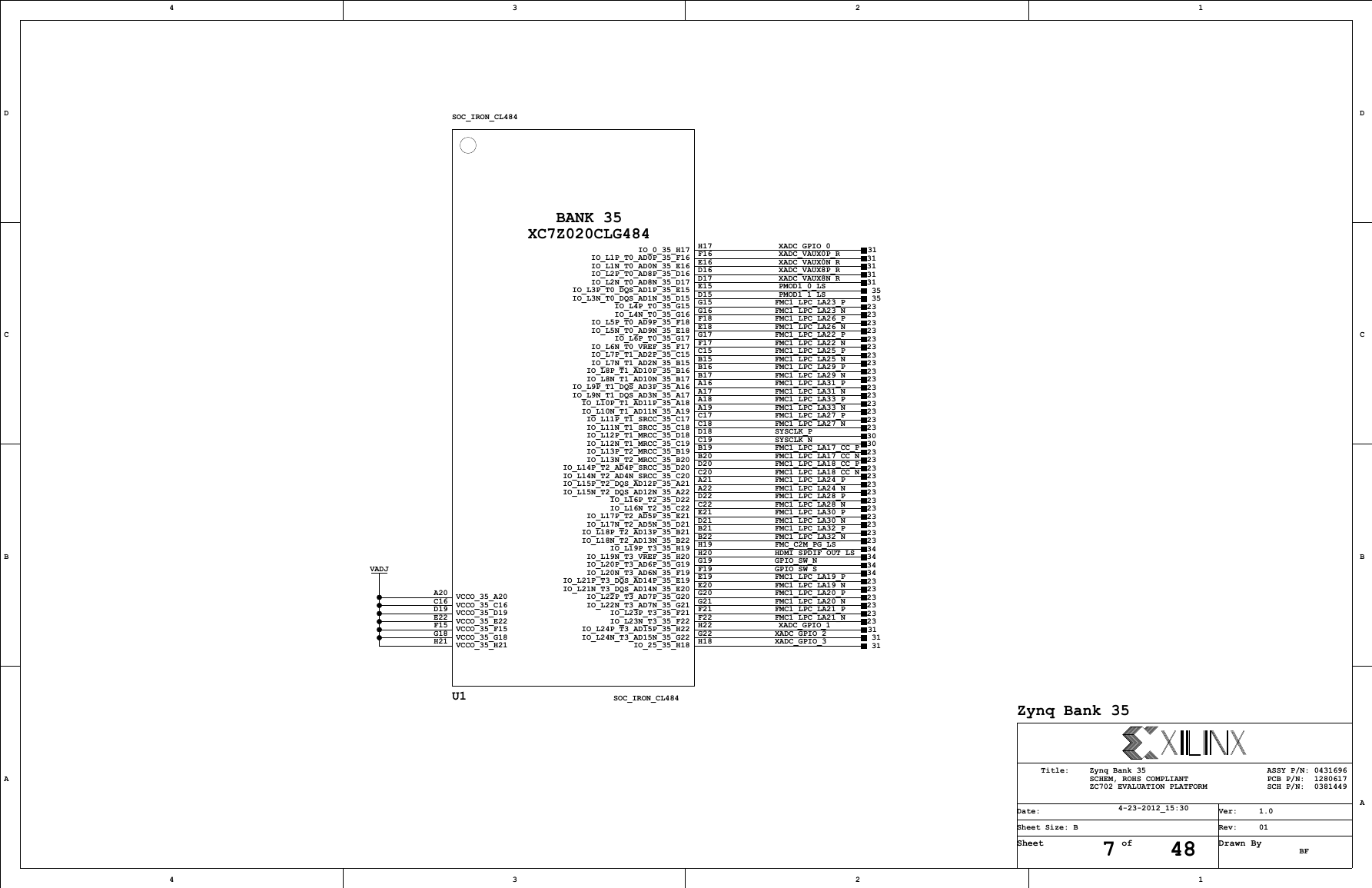

SOC_IRON_CL484

BANK 35

XC7Z020CLG484

IO_0_35_H17

IO_L1P_T0_AD0P_35_F16

IO_L1N_T0_AD0N_35_E16

IO_L2P_T0_AD8P_35_D16

IO_L2N_T0_AD8N_35_D17

IO_L3P_T0_DQS_AD1P_35_E15

IO_L3N_T0_DQS_AD1N_35_D15

IO_L4P_T0_35_G15

IO_L4N_T0_35_G16

IO_L5P_T0_AD9P_35_F18

IO_L5N_T0_AD9N_35_E18

IO_L6P_T0_35_G17

IO_L6N_T0_VREF_35_F17

IO_L7P_T1_AD2P_35_C15

IO_L7N_T1_AD2N_35_B15

IO_L8P_T1_AD10P_35_B16

IO_L8N_T1_AD10N_35_B17

IO_L9P_T1_DQS_AD3P_35_A16

IO_L9N_T1_DQS_AD3N_35_A17

IO_L10P_T1_AD11P_35_A18

IO_L10N_T1_AD11N_35_A19

IO_L11P_T1_SRCC_35_C17

IO_L11N_T1_SRCC_35_C18

IO_L12P_T1_MRCC_35_D18

IO_L12N_T1_MRCC_35_C19

IO_L13P_T2_MRCC_35_B19

IO_L13N_T2_MRCC_35_B20

IO_L14P_T2_AD4P_SRCC_35_D20

IO_L14N_T2_AD4N_SRCC_35_C20

IO_L15P_T2_DQS_AD12P_35_A21

IO_L15N_T2_DQS_AD12N_35_A22

IO_L16P_T2_35_D22

IO_L16N_T2_35_C22

IO_L17P_T2_AD5P_35_E21

IO_L17N_T2_AD5N_35_D21

IO_L18P_T2_AD13P_35_B21

IO_L18N_T2_AD13N_35_B22

IO_L19P_T3_35_H19

IO_L19N_T3_VREF_35_H20

IO_L20P_T3_AD6P_35_G19

IO_L20N_T3_AD6N_35_F19

IO_L21P_T3_DQS_AD14P_35_E19

IO_L21N_T3_DQS_AD14N_35_E20

IO_L22P_T3_AD7P_35_G20

IO_L22N_T3_AD7N_35_G21

IO_L23P_T3_35_F21

IO_L23N_T3_35_F22

IO_L24P_T3_AD15P_35_H22

IO_L24N_T3_AD15N_35_G22

IO_25_35_H18

H17

F16

E16

D16

D17

E15

D15

G15

G16

F18

E18

G17

F17

C15

B15

B16

B17

A16

A17

A18

A19

C17

C18

D18

C19

B19

B20

D20

C20

A21

A22

D22

C22

E21

D21

B21

B22

H19

H20

G19

F19

E19

E20

G20

G21

F21

F22

H22

G22

H18

VADJ

A20

C16

D19

E22

F15

G18

H21

VCCO_35_A20

VCCO_35_C16

VCCO_35_D19

VCCO_35_E22

VCCO_35_F15

VCCO_35_G18

VCCO_35_H21

35

35

31

31

31

31

31

XADC_GPIO_0

XADC_VAUX0P_R

XADC_VAUX0N_R

XADC_VAUX8P_R

XADC_VAUX8N_R

PMOD1_0_LS

PMOD1_1_LS

FMC1_LPC_LA23_P

23

FMC1_LPC_LA23_N

23

FMC1_LPC_LA26_P

23

FMC1_LPC_LA26_N

23

FMC1_LPC_LA22_P

23

FMC1_LPC_LA22_N

23

FMC1_LPC_LA25_P

23

FMC1_LPC_LA25_N

23

FMC1_LPC_LA29_P

23

FMC1_LPC_LA29_N

23

FMC1_LPC_LA31_P

23

FMC1_LPC_LA31_N

23

FMC1_LPC_LA33_P

23

FMC1_LPC_LA33_N

23

FMC1_LPC_LA27_P

23

FMC1_LPC_LA27_N

23

SYSCLK_P

30

SYSCLK_N

30

FMC1_LPC_LA17_CC_P 23

FMC1_LPC_LA17_CC_N 23

FMC1_LPC_LA18_CC_P 23

FMC1_LPC_LA18_CC_N 23

FMC1_LPC_LA24_P

23

FMC1_LPC_LA24_N

23

FMC1_LPC_LA28_P

23

FMC1_LPC_LA28_N

23

FMC1_LPC_LA30_P

23

FMC1_LPC_LA30_N

23

FMC1_LPC_LA32_P

23

FMC1_LPC_LA32_N

23

FMC_C2M_PG_LS

34

HDMI_SPDIF_OUT_LS

34

GPIO_SW_N

34

GPIO_SW_S

34

FMC1_LPC_LA19_P

23

FMC1_LPC_LA19_N

23

FMC1_LPC_LA20_P

23

FMC1_LPC_LA20_N

23

FMC1_LPC_LA21_P

23

FMC1_LPC_LA21_N

23

XADC_GPIO_1

31

XADC_GPIO_2

31

XADC_GPIO_3

31

U1

SOC_IRON_CL484

Zynq Bank 35

4

3

2

Title:

Zynq Bank 35

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

7

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

�

D

C

B

A

4

3

2

1

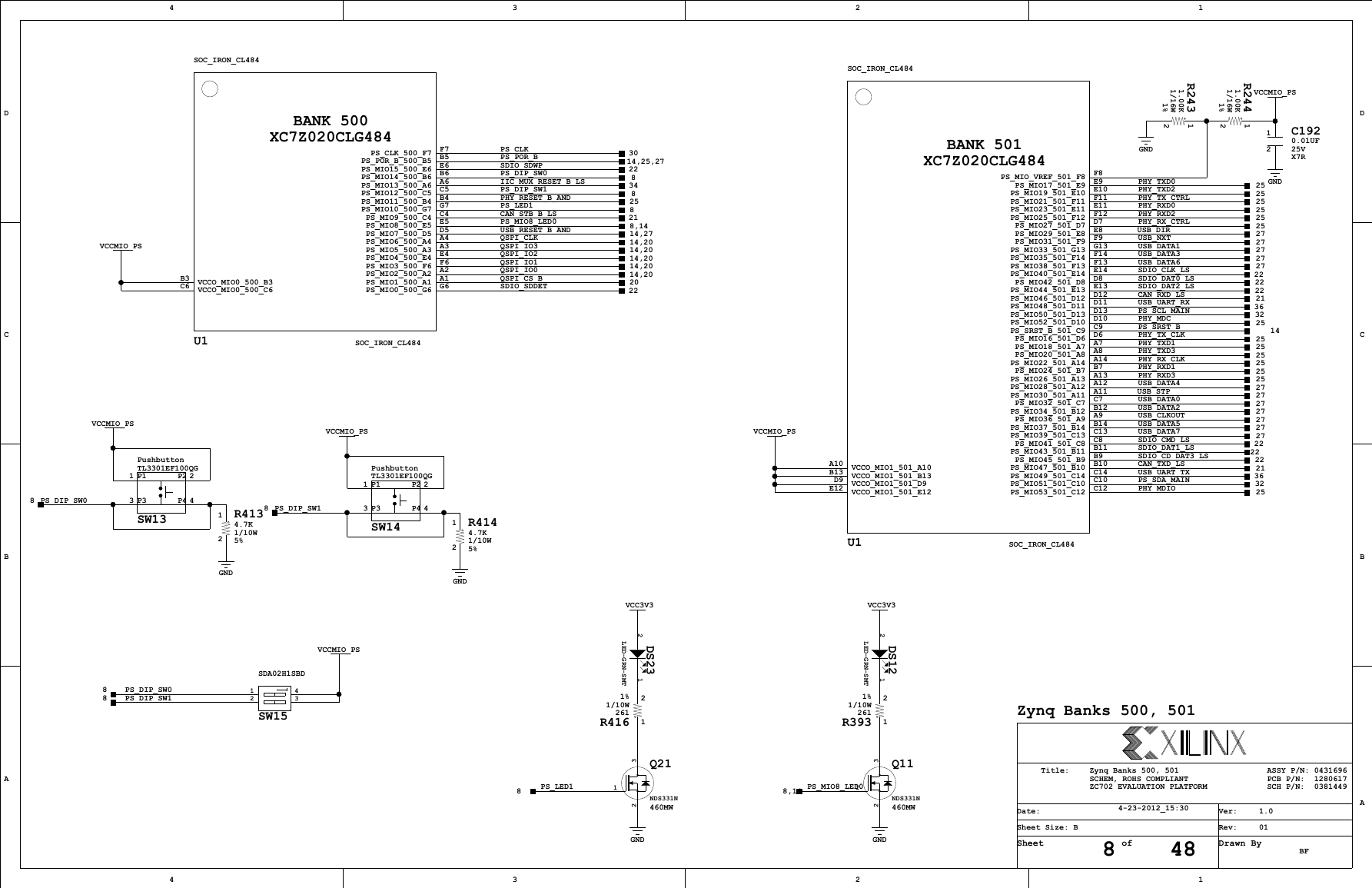

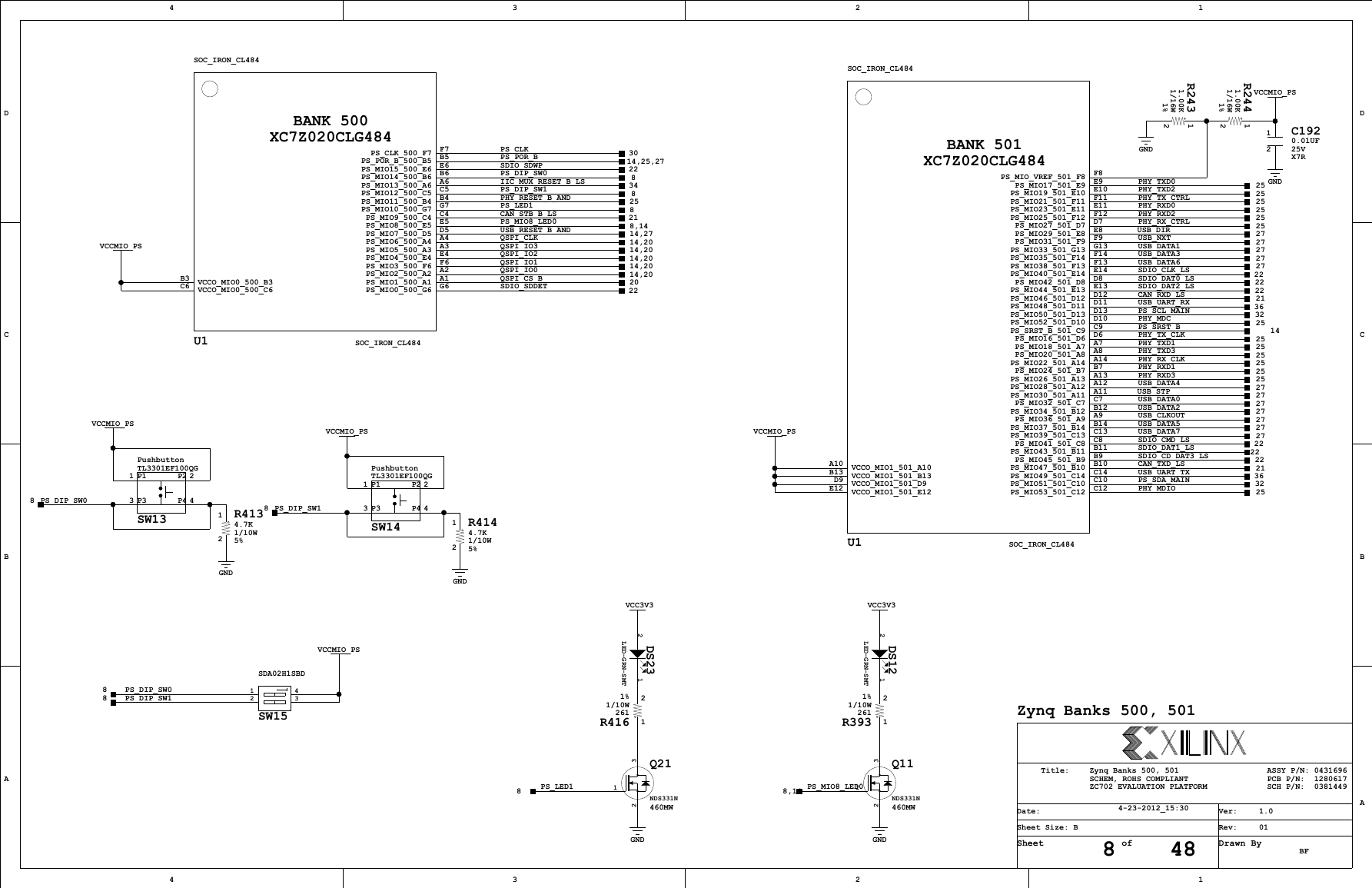

SOC_IRON_CL484

SOC_IRON_CL484

BANK 500

XC7Z020CLG484

PS_CLK_500_F7

PS_POR_B_500_B5

PS_MIO15_500_E6

PS_MIO14_500_B6

PS_MIO13_500_A6

PS_MIO12_500_C5

PS_MIO11_500_B4

PS_MIO10_500_G7

PS_MIO9_500_C4

PS_MIO8_500_E5

PS_MIO7_500_D5

PS_MIO6_500_A4

PS_MIO5_500_A3

PS_MIO4_500_E4

PS_MIO3_500_F6

PS_MIO2_500_A2

PS_MIO1_500_A1

PS_MIO0_500_G6

F7

B5

E6

B6

A6

C5

B4

G7

C4

E5

D5

A4

A3

E4

F6

A2

A1

G6

PS_CLK

PS_POR_B

SDIO_SDWP

PS_DIP_SW0

IIC_MUX_RESET_B_LS

PS_DIP_SW1

PHY_RESET_B_AND

PS_LED1

CAN_STB_B_LS

PS_MIO8_LED0

USB_RESET_B_AND

QSPI_CLK

QSPI_IO3

QSPI_IO2

QSPI_IO1

QSPI_IO0

QSPI_CS_B

SDIO_SDDET

30

14,25,27

22

8

34

8

25

8

21

8,14

14,27

14,20

14,20

14,20

14,20

14,20

20

22

VCCMIO_PS

B3

C6

VCCO_MIO0_500_B3

VCCO_MIO0_500_C6

U1

SOC_IRON_CL484

VCCMIO_PS

Pushbutton

TL3301EF100QG

P1

2

P2

1

8 PS_DIP_SW0

3

P3

P4

4

SW13

VCCMIO_PS

VCCMIO_PS

Pushbutton

TL3301EF100QG

P1

2

P2

1

8 PS_DIP_SW1

3

P3

P4

4

SW14

1

2

R414

4.7K

1/10W

5%

GND

1 R413

4.7K

1/10W

5%

2

GND

R

2

4

3

1

/

1

6

W

1

.

0

0

K

1

%

R

2

4

4

1

/

1

6

W

1

.

0

0

K

1

%

VCCMIO_PS

BANK 501

XC7Z020CLG484

PS_MIO_VREF_501_F8

PS_MIO17_501_E9

PS_MIO19_501_E10

PS_MIO21_501_F11

PS_MIO23_501_E11

PS_MIO25_501_F12

PS_MIO27_501_D7

PS_MIO29_501_E8

PS_MIO31_501_F9

PS_MIO33_501_G13

PS_MIO35_501_F14

PS_MIO38_501_F13

PS_MIO40_501_E14

PS_MIO42_501_D8

PS_MIO44_501_E13

PS_MIO46_501_D12

PS_MIO48_501_D11

PS_MIO50_501_D13

PS_MIO52_501_D10

PS_SRST_B_501_C9

PS_MIO16_501_D6

PS_MIO18_501_A7

PS_MIO20_501_A8

PS_MIO22_501_A14

PS_MIO24_501_B7

PS_MIO26_501_A13

PS_MIO28_501_A12

PS_MIO30_501_A11

PS_MIO32_501_C7

PS_MIO34_501_B12

PS_MIO36_501_A9

PS_MIO37_501_B14

PS_MIO39_501_C13

PS_MIO41_501_C8

PS_MIO43_501_B11

PS_MIO45_501_B9

PS_MIO47_501_B10

PS_MIO49_501_C14

PS_MIO51_501_C10

PS_MIO53_501_C12

F8

E9

E10

F11

E11

F12

D7

E8

F9

G13

F14

F13

E14

D8

E13

D12

D11

D13

D10

C9

D6

A7

A8

A14

B7

A13

A12

A11

C7

B12

A9

B14

C13

C8

B11

B9

B10

C14

C10

C12

A10

B13

D9

E12

VCCO_MIO1_501_A10

VCCO_MIO1_501_B13

VCCO_MIO1_501_D9

VCCO_MIO1_501_E12

U1

SOC_IRON_CL484

C192

0.01UF

25V

X7R

1

2

GND

14

2 1

2 1

GND

PHY_TXD0

PHY_TXD2

PHY_TX_CTRL

PHY_RXD0

PHY_RXD2

PHY_RX_CTRL

USB_DIR

USB_NXT

USB_DATA1

USB_DATA3

USB_DATA6

SDIO_CLK_LS

SDIO_DAT0_LS

SDIO_DAT2_LS

CAN_RXD_LS

USB_UART_RX

PS_SCL_MAIN

PHY_MDC

PS_SRST_B

PHY_TX_CLK

PHY_TXD1

PHY_TXD3

PHY_RX_CLK

PHY_RXD1

PHY_RXD3

USB_DATA4

USB_STP

USB_DATA0

USB_DATA2

USB_CLKOUT

USB_DATA5

USB_DATA7

SDIO_CMD_LS

SDIO_DAT1_LS

SDIO_CD_DAT3_LS

CAN_TXD_LS

USB_UART_TX

PS_SDA_MAIN

PHY_MDIO

25

25

25

25

25

25

27

27

27

27

27

22

22

22

21

36

32

25

25

25

25

25

25

25

27

27

27

27

27

27

27

22

22

22

21

36

32

25

8

8

PS_DIP_SW0

PS_DIP_SW1

VCCMIO_PS

SDA02H1SBD

1

2

4

3

SW15

VCC3V3

L

E

D

-

G

R

N

-

S

M

T

1%

1/10W

261

R416

2

D

S

2

3

1

2

1

8

PS_LED1

1

3

Q21

2

NDS331N

460MW

GND

4

3

VCC3V3

L

E

D

-

G

R

N

-

S

M

T

1%

1/10W

261

R393

2

D

S

1

2

1

2

1

8,14

PS_MIO8_LED0

1

3

Q11

2

NDS331N

460MW

GND

2

Zynq Banks 500, 501

Title:

Zynq Banks 500, 501

SCHEM, ROHS COMPLIANT

ZC702 EVALUATION PLATFORM

ASSY P/N: 0431696

PCB P/N: 1280617

SCH P/N: 0381449

Date:

Sheet Size: B

Sheet

4-23-2012_15:30

of

8

48

1

Ver:

Rev:

1.0

01

Drawn By

BF

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc