5

4

3

2

1

Block Diagram

REV

0.0.0

DATE

09/04/2015

PAGES

ALL

DESCRIPTION

Created

iCore3 双核心工控板

银杏公司出品

GINGKO Technology Co.,LTd.

E-mail: gingko@vip.163.com

Tel: 0379-63002125 15516367209

http://i-board.taobao.com (点击进入)

D

C

B

A

NOTES:

1. Notes here.

D

C

B

A

PAGES

DESCRIPTION

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10

11

12

13

Title, Note, Block Diagram, Revision History

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

---------------------

Engineer: XiaomaGee

Engineer: ------

GINGKO Technology Co.,Ltd.

Title

Title

Title

Size

Size

Size

B

B

B

------

------

------

Document Number

Document Number

Document Number

0_Title

0_Title

0_Title

Rev

Rev

Rev

0.0.0

0.0.0

0.0.0

5

4

3

2

Date:

Date:

Date:

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Sheet

Sheet

Sheet

1

1

1

1

of

of

of

9

9

9

�

D

C

B

A

5

4

3

2

1

VIN

VUSBA

VUSBB

J3

PSEL

2

4

6

1

3

5

F1

2A

R1

0.02/1206

VCC

D1

SMBJ5.0CA

DCOM

2

1

-

N

E

S

V

+

N

E

S

V

T

U

O

I

3

ZXCT1009F

U2

ISENSE

ISENSE

C4

22uF/6.3V

DCOM

C5

104

R5

10K

C1

103

D3V3

DCOM

U1

1

2

3

BST

SW

GND

IN

FB

EN

MP2359

6

5

4

L1

4.7uH

D

R2

49.9K

D2

1N5819

C2

22uF/6.3V

C3

22uF/6.3V

DCOM

DCOM

DCOM

R3

49.9K

R4

16.2K

DCOM

D3V3

LED1

DCOM

C

R6

1K

DCOM

DCOM

D3V3

D3V3_ARM

R7

49.9K

R10

10K

C8

104

DCOM

DCOM

VSENSE

VSENSE

C6

22uF/6.3V

C7

22uF/6.3V

R8

0

D1V2

R9

10K

1V2SENSE

1V2SENSE

DCOM

D3V3_ARM

R11

10K

3V3SENSE

3V3SENSE

D3V3

D3V3_FPGA

R13

0

C9

22uF/6.3V

DCOM

R12

10K

DCOM

A2V5

R14

10K

2V5SENSE

2V5SENSE

B

R15

10K

DCOM

D3V3

D1V2

C14

22uF/6.3V

4

1

5

2

U3

VIN

EN

FB/VOUT

GND

RT8008-1.2

L3

4.7uH

D1V2

3

LX

C15

22uF/6.3V

C10

22uF/6.3V

C12

22uF/6.3V

C13

223

D3V3

A2V5

1

4

3

2

U4

VIN

VOUT

5

ADJ

EN

GND

RT9193-25B

C11

22uF/6.3V

DCOM

DCOM

DCOM

DCOM

DCOM

DCOM

DCOM

5

4

3

2

GINGKO Technology Co.,Ltd.

Title

Title

Title

Size

Size

Size

B

B

B

iCore3

iCore3

iCore3

Document Number

Document Number

Document Number

1_Power

1_Power

1_Power

Date:

Date:

Date:

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Sheet

Sheet

Sheet

1

2

2

2

of

of

of

9

9

9

A

Rev

Rev

Rev

0

0

0

�

D

C

B

A

5

4

3

2

1

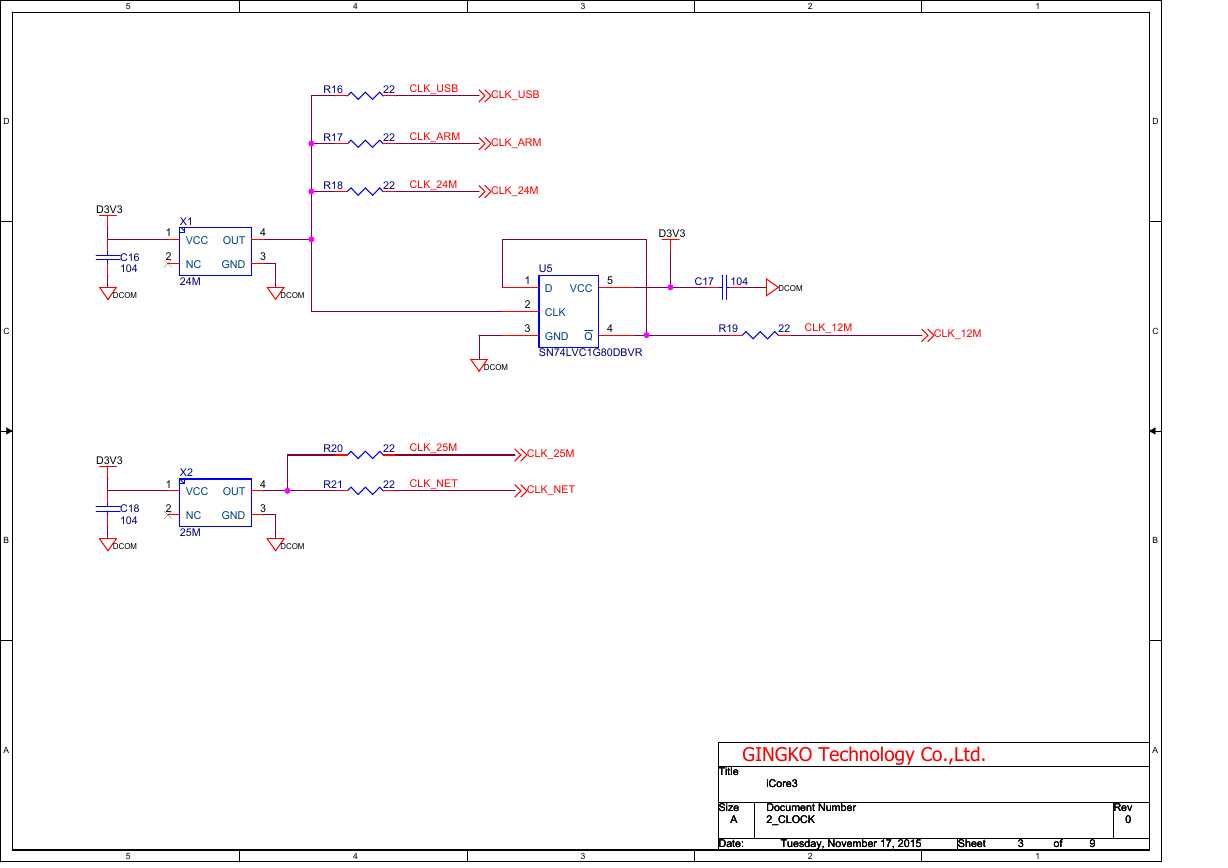

R16

22

CLK_USB

CLK_USB

R17

22

CLK_ARM

CLK_ARM

R18

22

CLK_24M

CLK_24M

D3V3

C16

104

DCOM

X1

1

2

VCC

OUT

NC

GND

4

3

24M

DCOM

D3V3

C17

104

DCOM

R19

22

CLK_12M

CLK_12M

1

2

3

U5

D

VCC

CLK

GND

Q

5

4

SN74LVC1G80DBVR

DCOM

D3V3

C18

104

DCOM

1

2

X2

VCC

OUT

NC

GND

25M

4

3

DCOM

R20

22

CLK_25M

R21

22

CLK_NET

CLK_25M

CLK_NET

5

4

3

2

1

Date:

Date:

Date:

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Sheet

Sheet

Sheet

3

3

3

of

of

of

9

9

9

GINGKO Technology Co.,Ltd.

Title

Title

Title

Size

Size

Size

A

A

A

iCore3

iCore3

iCore3

Document Number

Document Number

Document Number

2_CLOCK

2_CLOCK

2_CLOCK

Rev

Rev

Rev

0

0

0

D

C

B

A

�

5

4

3

2

1

C19

104

C20

104

C21

104

C22

104

C23

104

C24

104

C25

104

C26

104

C27

104

C28

104

C29

104

C30

104

C31

104

C32

104

C33

104

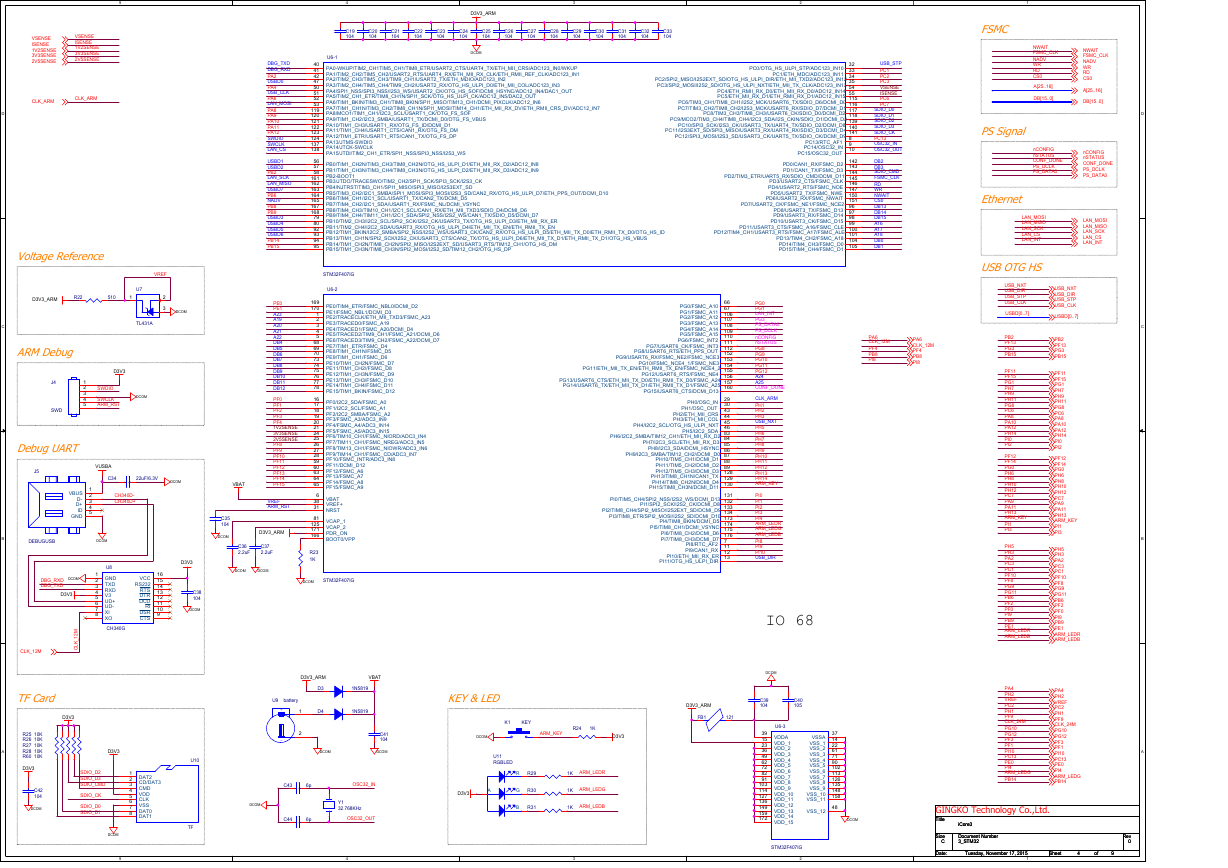

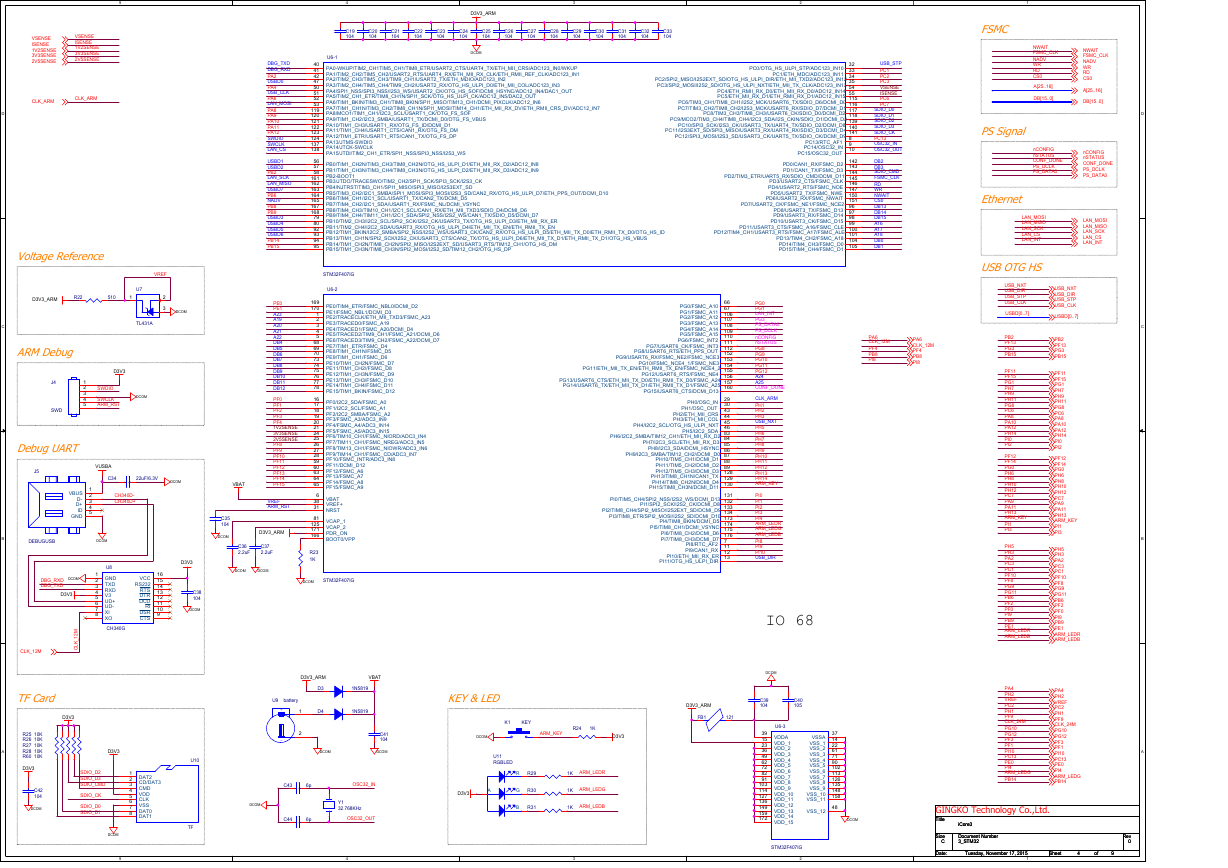

D3V3_ARM

U6-1

DCOM

PA0-WKUP/TIM2_CH1TIM5_CH1/TIM8_ETR/USART2_CTS/UART4_TX/ETH_MII_CRS/ADC123_IN0/WKUP

PA1/TIM2_CH2/TIM5_CH2/USART2_RTS/UART4_RX/ETH_MII_RX_CLK/ETH_RMII_REF_CLK/ADC123_IN1

PA2/TIM2_CH3/TIM5_CH3/TIM9_CH1/USART2_TX/ETH_MDIO/ADC123_IN2

PA3/TIM2_CH4/TIM5_CH4/TIM9_CH2/USART2_RX/OTG_HS_ULPI_D0/ETH_MII_COL/ADC123_IN3

PA4/SPI1_NSS/SPI3_NSS/I2S3_WS/USART2_CK/OTG_HS_SOF/DCMI_HSYNC/ADC12_IN4/DAC1_OUT

PA5/TIM2_CH1_ETR/TIM8_CH1N/SPI1_SCK/OTG_HS_ULPI_CK/ADC12_IN5/DAC2_OUT

PA6/TIM1_BKIN/TIM3_CH1/TIM8_BKIN/SPI1_MISO/TIM13_CH1/DCMI_PIXCLK/ADC12_IN6

PA7/TIM1_CH1N/TIM3_CH2/TIM8_CH1N/SPI1_MOSI/TIM14_CH1/ETH_MII_RX_DV/ETH_RMII_CRS_DV/ADC12_IN7

PA8/MCO1/TIM1_CH1/I2C3_SCL/USART1_CK/OTG_FS_SOF

PA9/TIM1_CH2/I2C3_SMBA/USART1_TX/DCMI_D0/OTG_FS_VBUS

PA10/TIM1_CH3/USART1_RX/OTG_FS_ID/DCMI_D1

PA11/TIM1_CH4/USART1_CTS/CAN1_RX/OTG_FS_DM

PA12/TIM1_ETR/USART1_RTS/CAN1_TX/OTG_FS_DP

PA13/JTMS-SWDIO

PA14/JTCK-SWCLK

PA15/JTDI/TIM2_CH1_ETR/SPI1_NSS/SPI3_NSS/I2S3_WS

PB0/TIM1_CH2N/TIM3_CH3/TIM8_CH2N/OTG_HS_ULPI_D1/ETH_MII_RX_D2/ADC12_IN8

PB1/TIM1_CH3N/TIM3_CH4/TIM8_CH3N/OTG_HS_ULPI_D2/ETH_MII_RX_D3/ADC12_IN9

PB2-BOOT1

PB3/JTDO/TRACESWO/TIM2_CH2/SPI1_SCK/SPI3_SCK/I2S3_CK

PB4/NJTRST/TIM3_CH1/SPI1_MISO/SPI3_MISO/I2S3EXT_SD

PB5/TIM3_CH2/I2C1_SMBA/SPI1_MOSI/SPI3_MOSI/I2S3_SD/CAN2_RX/OTG_HS_ULPI_D7/ETH_PPS_OUT/DCMI_D10

PB6/TIM4_CH1/I2C1_SCL/USART1_TX/CAN2_TX/DCMI_D5

PB7/TIM4_CH2/I2C1_SDA/USART1_RX/FSMC_NL/DCMI_VSYNC

PB8/TIM4_CH3/TIM10_CH1/I2C1_SCL/CAN1_RX/ETH_MII_TXD3/SDIO_D4/DCMI_D6

PB9/TIM4_CH4/TIM11_CH1/I2C1_SDA/SPI2_NSS/I2S2_WS/CAN1_TX/SDIO_D5/DCMI_D7

PB10/TIM2_CH3/I2C2_SCL/SPI2_SCK/I2S2_CK/USART3_TX/OTG_HS_ULPI_D3/ETH_MII_RX_ER

PB11/TIM2_CH4/I2C2_SDA/USART3_RX/OTG_HS_ULPI_D4/ETH_MII_TX_EN/ETH_RMII_TX_EN

PB12/TIM1_BKIN/I2C2_SMBA/SPI2_NSS/I2S2_WS/USART3_CK/CAN2_RX/OTG_HS_ULPI_D5/ETH_MII_TX_D0/ETH_RMII_TX_D0/OTG_HS_ID

PB13/TIM1_CH1N/SPI2_SCK/I2S2_CK/USART3_CTS/CAN2_TX/OTG_HS_ULPI_D6/ETH_MII_TX_D1/ETH_RMII_TX_D1/OTG_HS_VBUS

PB14/TIM1_CH2N/TIM8_CH2N/SPI2_MISO/I2S2EXT_SD/USART3_RTS/TIM12_CH1/OTG_HS_DM

PB15/TIM1_CH3N/TIM8_CH3N/SPI2_MOSI/I2S2_SD/TIM12_CH2/OTG_HS_DP

PC0/OTG_HS_ULPI_STP/ADC123_IN10

PC1/ETH_MDC/ADC123_IN11

PC2/SPI2_MISO/I2S2EXT_SD/OTG_HS_ULPI_DIR/ETH_MII_TXD2/ADC123_IN12

PC3/SPI2_MOSI/I2S2_SD/OTG_HS_ULPI_NXT/ETH_MII_TX_CLK/ADC123_IN13

PC4/ETH_RMII_RX_D0/ETH_MII_RX_D0/ADC12_IN14

PC5/ETH_MII_RX_D1/ETH_RMII_RX_D1/ADC12_IN15

PC6/TIM3_CH1/TIM8_CH1/I2S2_MCK/USART6_TX/SDIO_D6/DCMI_D0

PC7/TIM3_CH2/TIM8_CH2/I2S3_MCK/USART6_RX/SDIO_D7/DCMI_D1

PC8/TIM3_CH3/TIM8_CH3/USART6_CK/SDIO_D0/DCMI_D2

PC9/MCO2/TIM3_CH4/TIM8_CH4/I2C3_SDA/I2S_CKIN/SDIO_D1/DCMI_D3

PC10/SPI3_SCK/I2S3_CK/USART3_TX/UART4_TX/SDIO_D2/DCMI_D8

PC11/I2S3EXT_SD/SPI3_MISO/USART3_RX/UART4_RX/SDIO_D3/DCMI_D4

PC12/SPI3_MOSI/I2S3_SD/USART3_CK/UART5_TX/SDIO_CK/DCMI_D9

PC13/RTC_AF1

PC14/OSC32_IN

PC15/OSC32_OUT

PD0/CAN1_RX/FSMC_D2

PD1/CAN1_TX/FSMC_D3

PD2/TIM3_ETR/UART5_RX/SDIO_CMD/DCMI_D11

PD3/USART2_CTS/FSMC_CLK

PD4/USART2_RTS/FSMC_NOE

PD5/USART2_TX/FSMC_NWE

PD6/USART2_RX/FSMC_NWAIT

PD7/USART2_CK/FSMC_NE1/FSMC_NCE2

PD8/USART3_TX/FSMC_D13

PD9/USART3_RX/FSMC_D14

PD10/USART3_CK/FSMC_D15

PD11/USART3_CTS/FSMC_A16/FSMC_CLE

PD12/TIM4_CH1/USART3_RTS/FSMC_A17/FSMC_ALE

PD13/TIM4_CH2/FSMC_A18

PD14/TIM4_CH3/FSMC_D0

PD15/TIM4_CH4/FSMC_D1

VSENSE

ISENSE

1V2SENSE

3V3SENSE

2V5SENSE

VSENSE

ISENSE

1V2SENSE

3V3SENSE

2V5SENSE

CLK_ARM

CLK_ARM

D

C

Voltage Reference

D3V3_ARM

R22

510

1

VREF

U7

2

3

DCOM

TL431A

ARM Debug

D3V3

1

2

3

4

5

SWDIO

SWCLK

ARM_RST

DCOM

J4

SWD

Debug UART

J5

VUSBA

C34

22uF/6.3V

DCOM

VBAT

DBG_TXD

DBG_RXD

PA2

USBD0

PA4

USB_CLK

PA6

LAN_MOSI

PA8

PA9

PA10

PA11

PA12

SWDIO

SWCLK

LAN_CS

USBD1

USBD2

PB2

LAN_SCK

LAN_MISO

USBD7

PB6

NADV

PB8

PB9

USBD3

USBD4

USBD5

USBD6

PB14

PB15

PE0

PE1

A23

A19

A20

A21

A22

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

DB12

PF0

PF1

PF2

PF3

PF4

1V2SENSE

3V3SENSE

2V5SENSE

PF8

PF9

PF10

PF11

PF12

PF13

PF14

PF15

40

41

42

47

50

51

52

53

119

120

121

122

123

124

137

138

56

57

58

161

162

163

164

165

167

168

79

80

92

93

94

95

169

170

1

2

3

4

5

68

69

70

73

74

75

76

77

78

16

17

18

19

20

21

24

25

26

27

28

59

60

63

64

65

STM32F407IG

U6-2

PE0/TIM4_ETR/FSMC_NBL0/DCMI_D2

PE1/FSMC_NBL1/DCMI_D3

PE2/TRACECLK/ETH_MII_TXD3/FSMC_A23

PE3/TRACED0/FSMC_A19

PE4/TRACED1/FSMC_A20/DCMI_D4

PE5/TRACED2/TIM9_CH1/FSMC_A21/DCMI_D6

PE6/TRACED3/TIM9_CH2/FSMC_A22/DCMI_D7

PE7/TIM1_ETR/FSMC_D4

PE8/TIM1_CH1N/FSMC_D5

PE9/TIM1_CH1/FSMC_D6

PE10/TIM1_CH2N/FSMC_D7

PE11/TIM1_CH2//FSMC_D8

PE12/TIM1_CH3N/FSMC_D9

PE13/TIM1_CH3/FSMC_D10

PE14/TIM1_CH4/FSMC_D11

PE15/TIM1_BKIN/FSMC_D12

PF0/I2C2_SDA/FSMC_A0

PF1/I2C2_SCL/FSMC_A1

PF2/I2C2_SMBA/FSMC_A2

PF3/FSMC_A3/ADC3_IN9

PF4/FSMC_A4/ADC3_IN14

PF5/FSMC_A5/ADC3_IN15

PF6/TIM10_CH1/FSMC_NIORD/ADC3_IN4

PF7/TIM11_CH1/FSMC_NREG/ADC3_IN5

PF8/TIM13_CH1/FSMC_NIOWR/ADC3_IN6

PF9/TIM14_CH1/FSMC_CD/ADC3_IN7

PF10/FSMC_INTR/ADC3_IN8

PF11/DCMI_D12

PF12/FSMC_A6

PF13/FSMC_A7

PF14/FSMC_A8

PF15/FSMC_A9

PG0/FSMC_A10

PG1/FSMC_A11

PG2/FSMC_A12

PG3/FSMC_A13

PG4/FSMC_A14

PG5/FSMC_A15

PG6/FSMC_INT2

PG7/USART6_CK/FSMC_INT3

PG8/USART6_RTS/ETH_PPS_OUT

PG9/USART6_RX/FSMC_NE2/FSMC_NCE3

PG10/FSMC_NCE4_1/FSMC_NE3

PG11/ETH_MII_TX_EN/ETH_RMII_TX_EN/FSMC_NCE4_2

PG12/USART6_RTS/FSMC_NE4

PG13/USART6_CTS/ETH_MII_TX_D0/ETH_RMII_TX_D0/FSMC_A24

PG14/USART6_TX/ETH_MII_TX_D1/ETH_RMII_TX_D1/FSMC_A25

PG15/USART6_CTS/DCMI_D13

PH0/OSC_IN

PH1/OSC_OUT

PH2/ETH_MII_CRS

PH3/ETH_MII_COL

PH4/I2C2_SCL/OTG_HS_ULPI_NXT

PH5/I2C2_SDA

PH6/I2C2_SMBA/TIM12_CH1/ETH_MII_RX_D2

PH7/I2C3_SCL/ETH_MII_RX_D3

PH8/I2C3_SDA/DCMI_HSYNC

PH9/I2C3_SMBA/TIM12_CH2//DCMI_D0

PH10/TIM5_CH1/DCMI_D1

PH11/TIM5_CH2/DCMI_D2

PH12/TIM5_CH3/DCMI_D3

PH13/TIM8_CH1N/CAN1_TX

PH14/TIM8_CH2N/DCMI_D4

PH15/TIM8_CH3N/DCMI_D11

PI0/TIM5_CH4/SPI2_NSS/I2S2_WS/DCMI_D13

PI1/SPI2_SCK/I2S2_CK/DCMI_D8

PI2/TIM8_CH4/SPI2_MISO/I2S2EXT_SD/DCMI_D9

PI3/TIM8_ETR/SPI2_MOSI/I2S2_SD/DCMI_D10

PI4/TIM8_BKIN/DCMI_D5

PI5/TIM8_CH1/DCMI_VSYNC

PI6/TIM8_CH2/DCMI_D6

PI7/TIM8_CH3/DCMI_D7

PI8/RTC_AF2

PI9/CAN1_RX

PI10/ETH_MII_RX_ER

PI11/OTG_HS_ULPI_DIR

66

67

106

107

108

109

110

111

112

152

153

154

155

156

157

160

29

30

43

44

45

46

83

84

85

86

87

88

89

128

129

130

131

132

133

134

173

174

175

176

7

11

12

13

PG0

PG1

LAN_INT

PG3

PS_DATA0

PS_DCLK

nCONFIG

nSTATUS

PG8

PG9

PG10

PG11

PG12

A24

A25

CONF_DONE

CLK_ARM

PH1

PH2

PH3

USB_NXT

PH5

PH6

PH7

PH8

PH9

PH10

PH11

PH12

PH13

PH14

ARM_KEY

PI0

PI1

PI2

PI3

PI4

ARM_LEDR

ARM_LEDG

ARM_LEDB

PI8

PI9

PI10

USB_DIR

VREF

ARM_RST

D3V3_ARM

C35

104

DCOM

C36

2.2uF

C37

2.2uF

DCOM

DCOM

6

VBAT

38

31 VREF+

NRST

81

VCAP_1

125

VCAP_2

171

166 PDR_ON

BOOT0/VPP

R23

1K

DCOM

STM32F407IG

1

2

3

4

5

VBUS

D-

D+

ID

GND

CH340D-

CH340D+

B

DEBUGUSB

DCOM

DBG_RXD

DBG_TXD

DCOM

D3V3

M

2

1

_

K

L

C

CLK_12M

TF Card

D3V3

A

R25 10K

R26 10K

R27 10K

R28 10K

R60 10K

D3V3

C42

104

DCOM

U8

GND

TXD

RXD

V3

UD+

UD-

XI

XO

1

2

3

4

5

6

7

8

CH340G

VCC

RS232

RTS

DTR

DCD

RI

DSR

CTS

16

15

14

13

12

11

10

9

D3V3

C38

104

DCOM

1

2

3

4

5

6

7

8

DAT2

CD/DAT3

CMD

VDD

CLK

VSS

DAT0

DAT1

U10

TF

SDIO_D2

SDIO_D3

SDIO_CMD

SDIO_CK

SDIO_D0

SDIO_D1

D3V3

DCOM

5

D3V3_ARM

VBAT

U9

battery

+

-

1

2

D3

D4

DCOM

1N5819

1N5819

C41

104

DCOM

C43

6p

OSC32_IN

DCOM

Y1

32.768KHz

C44

6p

OSC32_OUT

D3V3_ARM

FB1

121

KEY & LED

K1

KEY

DCOM

ARM_KEY

R24

1K

D3V3

U11

RGBLED

R

R29

1K

ARM_LEDR

D3V3

A

G

R30

1K

ARM_LEDG

B

R31

1K

ARM_LEDB

4

3

IO 68

DCOM

C39

104

C40

105

39

15

23

36

49

62

72

82

91

103

114

127

136

149

159

172

U6-3

VDDA

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

STM32F407IG

2

VSSA

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

37

14

22

61

71

90

102

113

126

135

148

158

48

32

33

34

35

54

55

115

116

117

118

139

140

141

8

9

10

142

143

144

145

146

147

150

151

96

97

98

99

100

101

104

105

USB_STP

PC1

PC2

PC3

VSENSE

ISENSE

PC6

PC7

SDIO_D0

SDIO_D1

SDIO_D2

SDIO_D3

SDIO_CK

PC13

OSC32_IN

OSC32_OUT

DB2

DB3

SDIO_CMD

FSMC_CLK

RD

WR

NWAIT

CS0

DB13

DB14

DB15

A16

A17

A18

DB0

DB1

PA6

CLK_12M

PF4

PB8

PI8

PA6

CLK_12M

PF4

PB8

PI8

FSMC

PS Signal

Ethernet

NWAIT

FSMC_CLK

NADV

WR

RD

CS0

A[25..16]

DB[15..0]

NWAIT

FSMC_CLK

NADV

WR

RD

CS0

A[25..16]

DB[15..0]

nCONFIG

nSTATUS

CONF_DONE

PS_DCLK

PS_DATA0

nCONFIG

nSTATUS

CONF_DONE

PS_DCLK

PS_DATA0

LAN_MOSI

LAN_MISO

LAN_SCK

LAN_CS

LAN_INT

LAN_MOSI

LAN_MISO

LAN_SCK

LAN_CS

LAN_INT

USB OTG HS

USB_NXT

USB_DIR

USB_STP

USB_CLK

USBD[0..7]

USB_NXT

USB_DIR

USB_STP

USB_CLK

USBD[0..7]

PB2

PF13

PG3

PB15

PF11

PF15

PG1

PH7

PH9

PH11

PG8

PC6

PA8

PA10

PA12

PH14

PI0

PI2

PF12

PF14

PG0

PH6

PH8

PH10

PH12

PC7

PA9

PA11

PH13

ARM_KEY

PI1

PI3

PH5

PH3

PA2

PC3

PC1

PF10

PF8

PG9

PG11

PB6

PF2

PF0

PI9

PB9

PE1

ARM_LEDR

ARM_LEDB

PA4

PH2

VREF

PC2

PH1

PF9

CLK_24M

PG10

PG12

PF3

PF1

PI10

PC13

PE0

PI4

ARM_LEDG

PB14

PB2

PF13

PG3

PB15

PF11

PF15

PG1

PH7

PH9

PH11

PG8

PC6

PA8

PA10

PA12

PH14

PI0

PI2

PF12

PF14

PG0

PH6

PH8

PH10

PH12

PC7

PA9

PA11

PH13

ARM_KEY

PI1

PI3

PH5

PH3

PA2

PC3

PC1

PF10

PF8

PG9

PG11

PB6

PF2

PF0

PI9

PB9

PE1

ARM_LEDR

ARM_LEDB

PA4

PH2

VREF

PC2

PH1

PF9

CLK_24M

PG10

PG12

PF3

PF1

PI10

PC13

PE0

PI4

ARM_LEDG

PB14

D

C

B

A

DCOM

GINGKO Technology Co.,Ltd.

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

iCore3

iCore3

iCore3

Document Number

Document Number

Document Number

3_STM32

3_STM32

3_STM32

Rev

Rev

Rev

0

0

0

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

1

Sheet

Sheet

Sheet

4

4

4

of

of

of

9

9

9

�

D

C

B

A

5

4

3

2

1

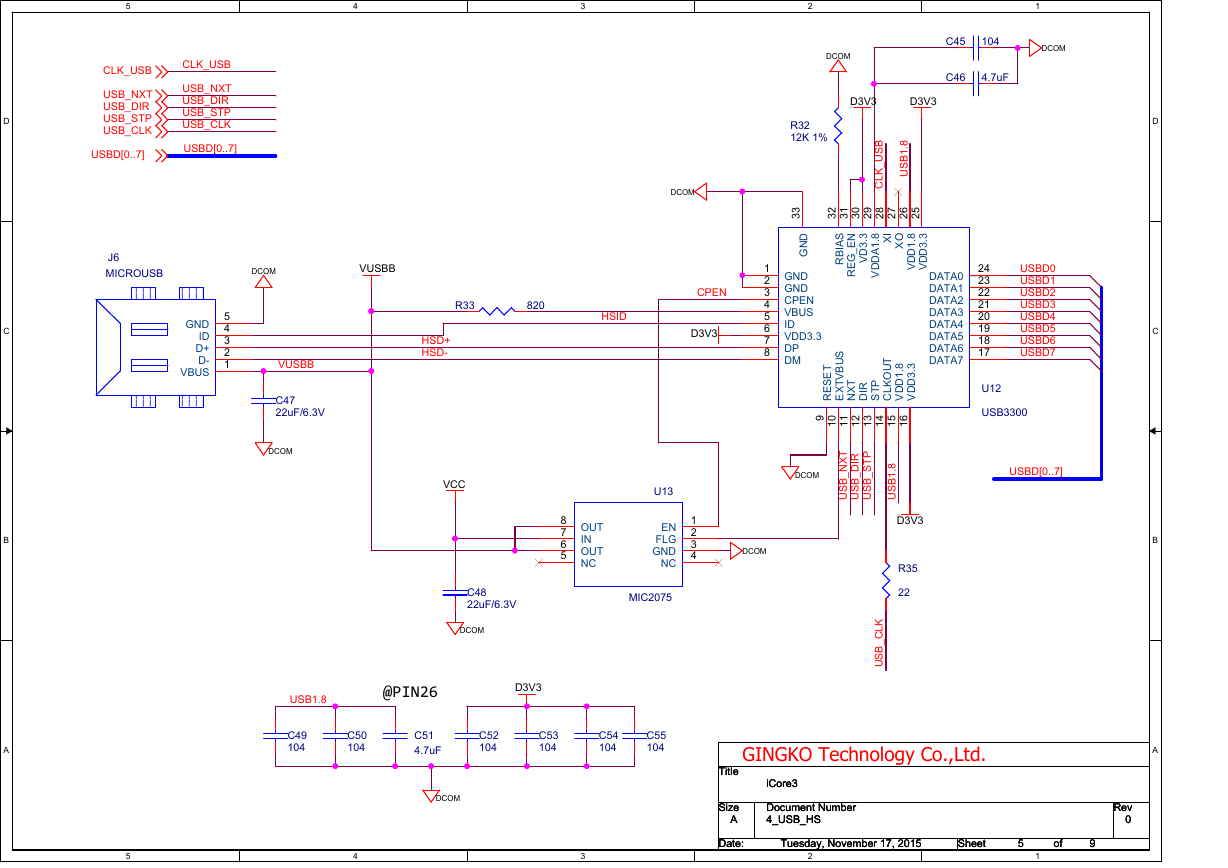

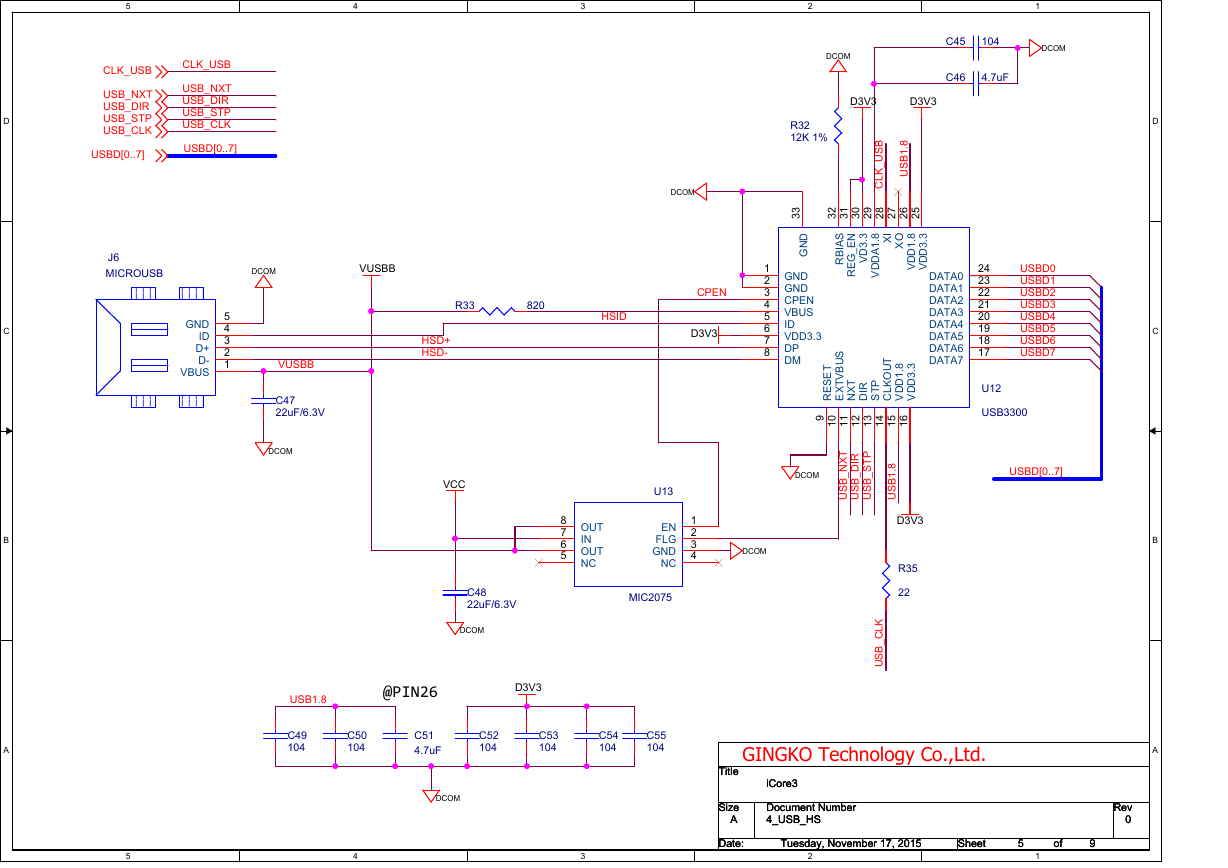

CLK_USB

USB_NXT

USB_DIR

USB_STP

USB_CLK

USBD[0..7]

CLK_USB

USB_NXT

USB_DIR

USB_STP

USB_CLK

USBD[0..7]

J6

MICROUSB

DCOM

VUSBB

5

4

3

2

1

GND

ID

D+

D-

VBUS

VUSBB

C47

22uF/6.3V

DCOM

R33

820

HSID

DCOM

CPEN

D3V3

D

N

G

GND

GND

CPEN

VBUS

ID

VDD3.3

DP

DM

1

2

3

4

5

6

7

8

DCOM

D3V3

D3V3

C45

104

DCOM

C46

4.7uF

R32

12K 1%

.

8

1

B

S

U

B

S

U

_

K

L

C

3

3

2

3

1

3

0

3

9

2

8

2

7

2

6

2

5

2

.

3

3

D

V

I

S

A

B

R

N

E

_

G

E

R

.

8

1

A

D

D

V

I

X

O

X

.

8

1

D

D

V

.

3

3

D

D

V

S

U

B

V

T

X

E

T

E

S

E

R

T

U

O

K

L

C

.

8

1

D

D

V

.

3

3

D

D

V

T

X

N

R

D

I

P

T

S

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

24

23

22

21

20

19

18

17

USBD0

USBD1

USBD2

USBD3

USBD4

USBD5

USBD6

USBD7

U12

USB3300

USBD[0..7]

HSD+

HSD-

VCC

C48

22uF/6.3V

DCOM

8

7

6

5

OUT

IN

OUT

NC

U13

EN

FLG

GND

NC

1

2

3

4

MIC2075

DCOM

9

0

1

1

1

2

1

3

1

4

1

5

1

6

1

DCOM

T

X

N

_

B

S

U

I

R

D

_

B

S

U

P

T

S

_

B

S

U

.

8

1

B

S

U

D3V3

R35

22

K

L

C

_

B

S

U

USB1.8

@PIN26

D3V3

C49

104

C50

104

C51

4.7uF

C52

104

C53

104

C54

104

C55

104

DCOM

GINGKO Technology Co.,Ltd.

Title

Title

Title

Size

Size

Size

A

A

A

iCore3

iCore3

iCore3

Document Number

Document Number

Document Number

4_USB_HS

4_USB_HS

4_USB_HS

Rev

Rev

Rev

0

0

0

5

4

3

2

1

Date:

Date:

Date:

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Sheet

Sheet

Sheet

5

5

5

of

of

of

9

9

9

D

C

B

A

�

5

4

3

2

1

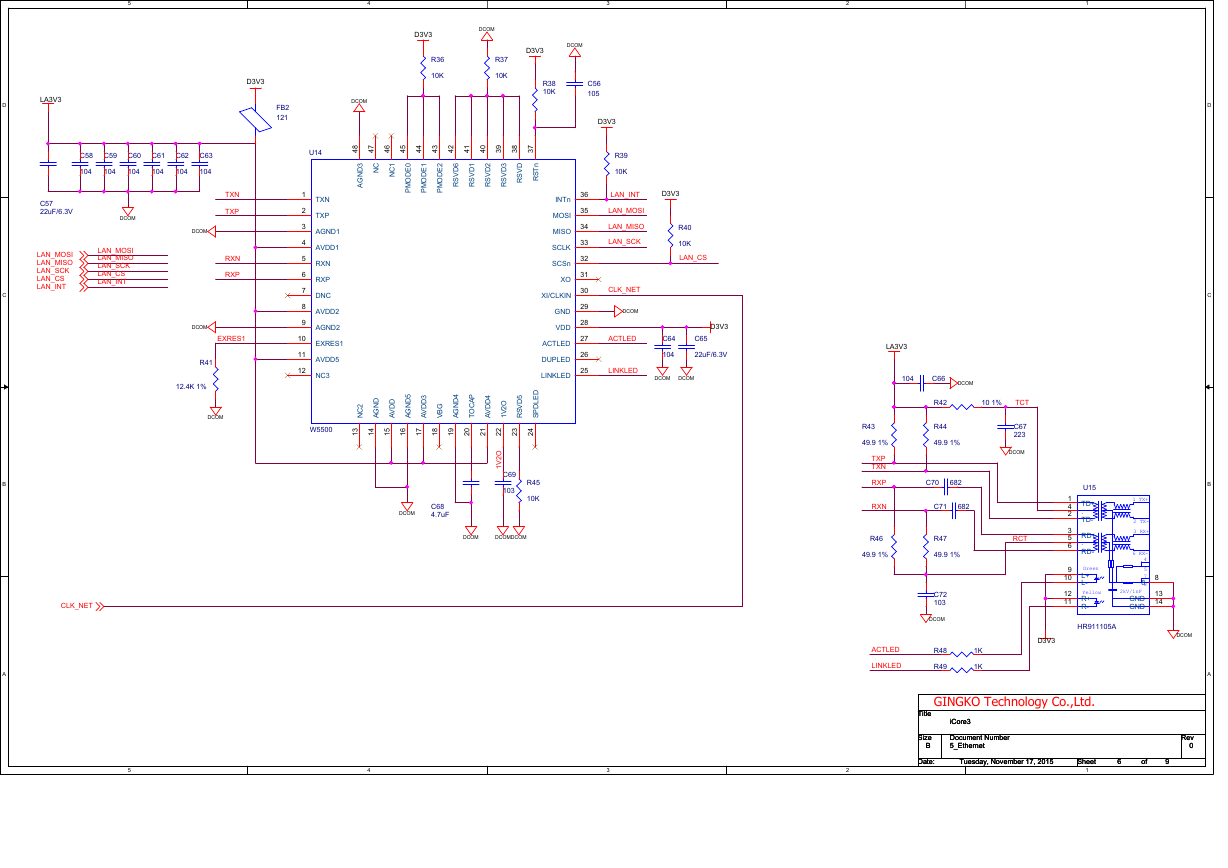

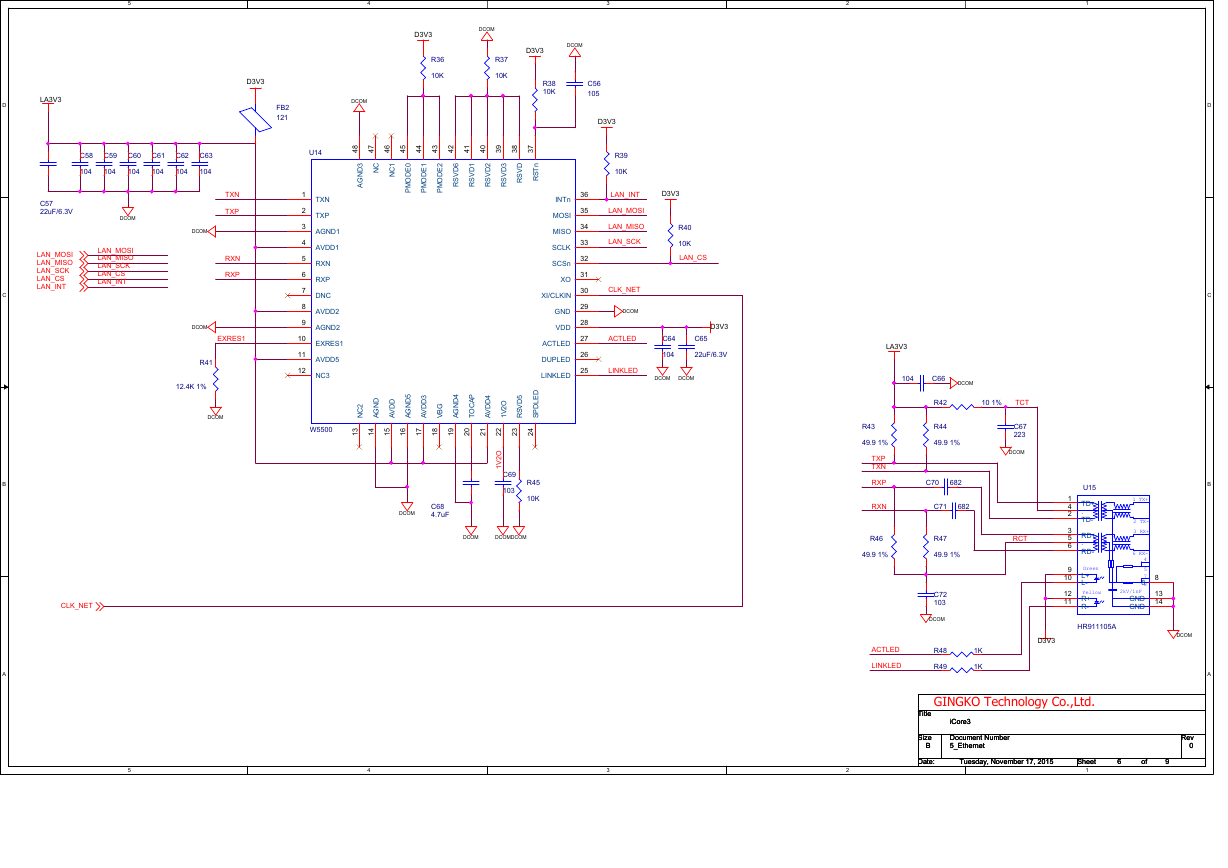

D3V3

DCOM

R36

10K

R37

10K

D3V3

DCOM

R38

10K

C56

105

D3V3

R39

10K

LAN_INT

D3V3

R40

10K

LAN_CS

LAN_MOSI

LAN_MISO

LAN_SCK

CLK_NET

DCOM

ACTLED

C64

C65

D3V3

104

22uF/6.3V

LINKLED

DCOM DCOM

INTn

MOSI

MISO

SCLK

SCSn

XO

XI/CLKIN

GND

VDD

ACTLED

DUPLED

LINKLED

36

35

34

33

32

31

30

29

28

27

26

25

D

LA3V3

D3V3

FB2

121

DCOM

U14

8

4

7

4

6

4

5

4

4

4

3

4

2

4

1

4

0

4

9

3

8

3

7

3

C

N

1

C

N

3

D

N

G

A

0

E

D

O

M

P

1

E

D

O

M

P

2

E

D

O

M

P

6

D

V

S

R

1

D

V

S

R

2

D

V

S

R

3

D

V

S

R

D

V

S

R

n

T

S

R

1

2

3

4

5

6

7

8

9

10

11

12

TXN

TXP

AGND1

AVDD1

RXN

RXP

DNC

AVDD2

AGND2

EXRES1

AVDD5

NC3

D

N

G

A

D

D

V

A

2

C

N

5

D

N

G

A

3

D

D

V

A

G

B

V

4

D

N

G

A

P

A

C

O

T

4

D

D

V

A

O

2

V

1

5

D

V

S

R

D

E

L

D

P

S

W5500

3

1

4

1

5

1

6

1

7

1

8

1

9

1

0

2

1

2

2

2

3

2

4

2

O

2

V

1

C69

103

R45

10K

DCOM

C68

4.7uF

DCOM

DCOM

DCOM

C58

C59

C60

C61

C62

C63

104

104

104

104

104

104

C57

22uF/6.3V

LAN_MOSI

LAN_MISO

LAN_SCK

LAN_CS

LAN_INT

DCOM

LAN_MOSI

LAN_MISO

LAN_SCK

LAN_CS

LAN_INT

DCOM

TXN

TXP

RXN

RXP

DCOM

EXRES1

R41

12.4K 1%

DCOM

CLK_NET

C

B

A

5

4

3

2

D

C

B

A

LA3V3

104

C66

DCOM

R42

R44

R43

49.9 1%

49.9 1%

10 1%

TCT

C67

223

DCOM

TXP

TXN

RXP

RXN

C70

682

C71

682

R46

R47

RCT

49.9 1%

49.9 1%

C72

103

DCOM

R48

R49

1K

1K

ACTLED

LINKLED

U15

TD+

.

TD-

RD+

.

RD-

1

4

2

3

5

6

9

10

Green

L+

L-

Yellow

12

11 R+

R-

1 TX+

2 TX-

3 RX+

6 RX-

4

5

7

8

8

2kV/1nF

GND

GND

8

13

14

HR911105A

D3V3

DCOM

GINGKO Technology Co.,Ltd.

Title

Title

Title

Size

Size

Size

B

B

B

iCore3

iCore3

iCore3

Document Number

Document Number

Document Number

5_Ethernet

5_Ethernet

5_Ethernet

Rev

Rev

Rev

0

0

0

Date:

Date:

Date:

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Sheet

Sheet

Sheet

1

6

6

6

of

of

of

9

9

9

�

5

4

3

2

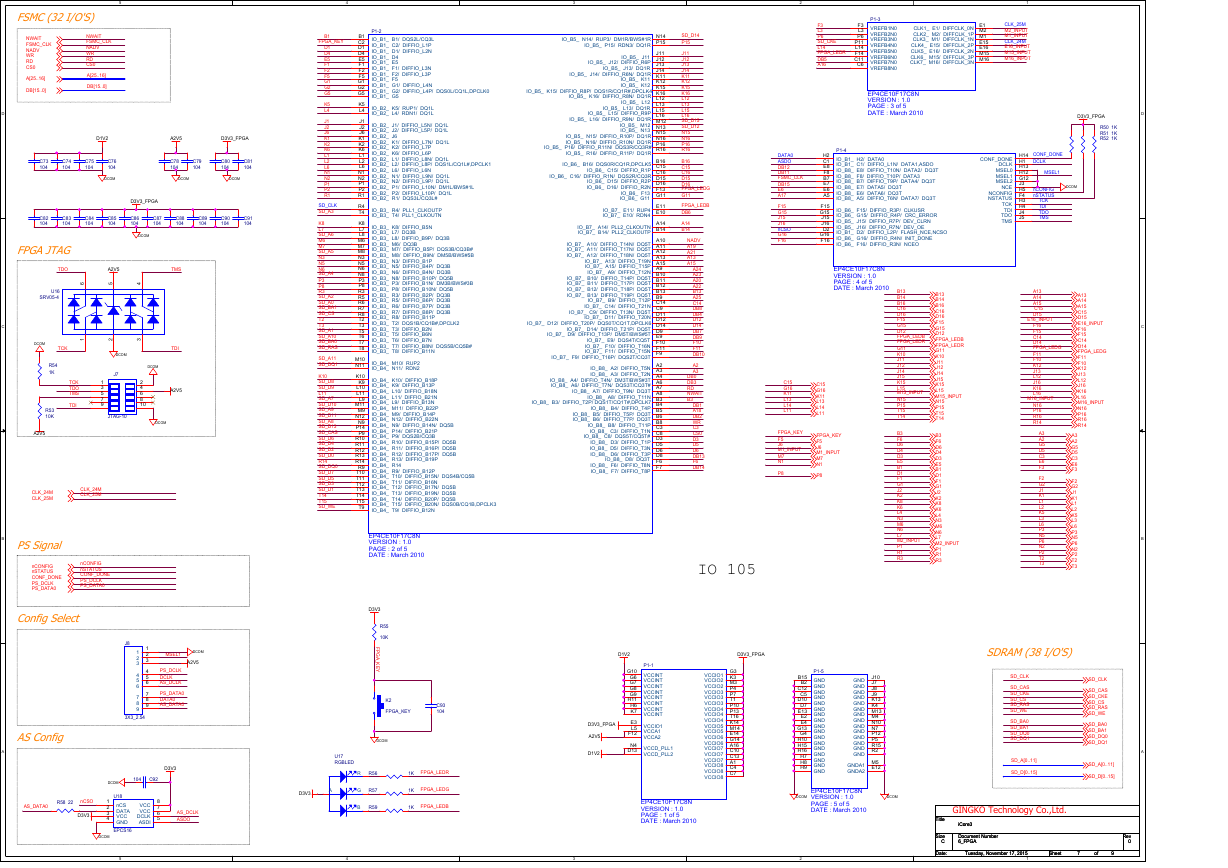

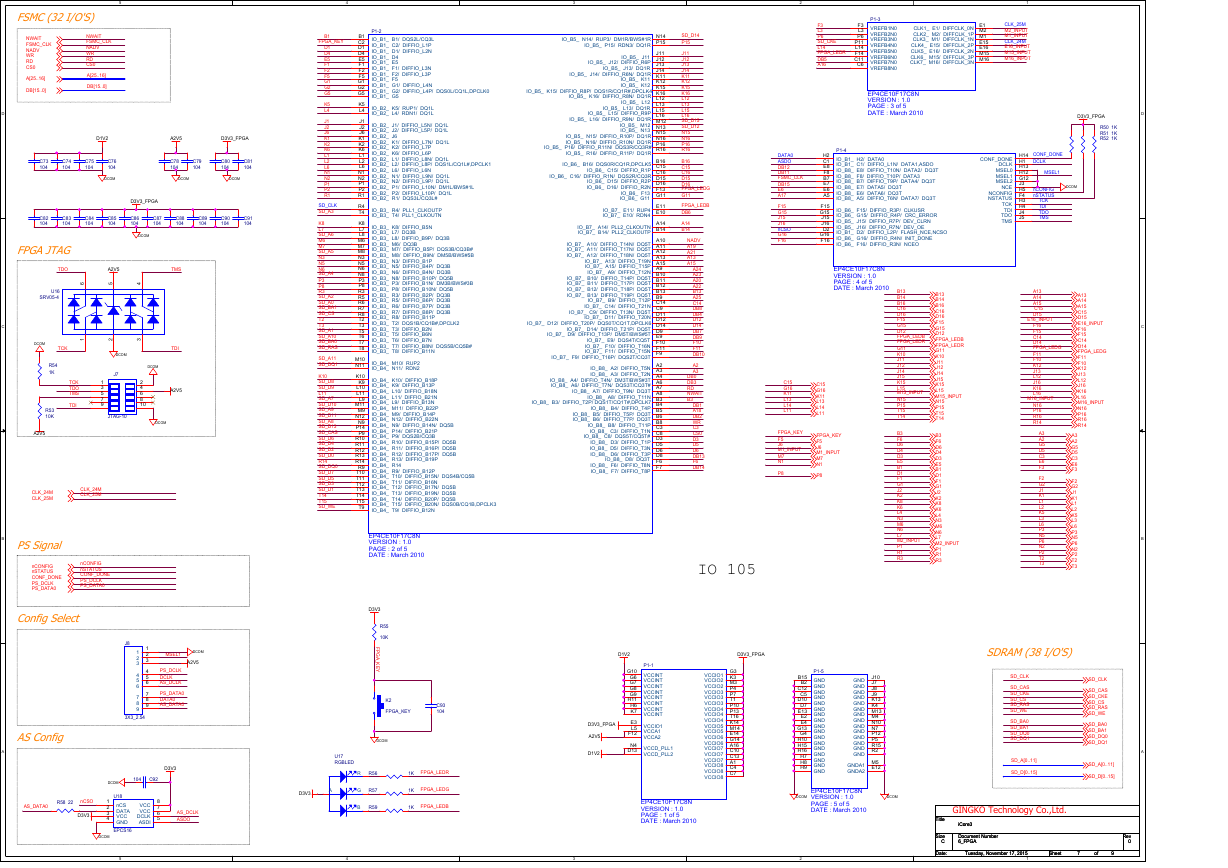

FSMC (32 I/O'S)

NWAIT

FSMC_CLK

NADV

WR

RD

CS0

A[25..16]

DB[15..0]

NWAIT

FSMC_CLK

NADV

WR

RD

CS0

A[25..16]

DB[15..0]

D

C

D1V2

A2V5

D3V3_FPGA

C73

104

C74

104

C75

104

C76

104

DCOM

C78

104

C79

104

C80

104

C81

104

DCOM

DCOM

D3V3_FPGA

C82

104

C83

104

C84

104

C85

104

C86

104

C87

104

C88

104

C89

104

C90

104

C91

104

FPGA JTAG

DCOM

TDO

A2V5

TMS

6

5

4

U16

SRV05-4

DCOM

TCK

R54

1K

R53

10K

A2V5

1

2

3

DCOM

J7

TDI

A2V5

DCOM

2

4

6

8

10

JTAG-10

DCOM

TCK

TDO

TMS

TDI

1

3

5

7

9

CLK_24M

CLK_25M

CLK_24M

CLK_25M

B

PS Signal

nCONFIG

nSTATUS

CONF_DONE

PS_DCLK

PS_DATA0

nCONFIG

nSTATUS

CONF_DONE

PS_DCLK

PS_DATA0

Config Select

J8

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

3X3_2.54

MSEL1

DCOM

A2V5

PS_DCLK

DCLK

AS_DCLK

PS_DATA0

DATA0

AS_DATA0

AS Config

A

AS_DATA0

R58 22

nCSO

D3V3

D3V3

104

C92

DCOM

U18

1

2

3

4

nCS

DATA

VCC

GND

VCC

VCC

DCLK

ASDI

8

7

6

5

EPCS16

DCOM

AS_DCLK

ASDO

B1

FPGA_KEY

D1

D4

E5

F1

F2

F5

G1

G2

G5

K5

L4

J1

J2

J6

K1

K2

K6

L1

L2

L6

N1

N2

P1

P2

R1

SD_CLK

SD_A3

K8

L7

SD_A6

M6

M7

SD_A5

N3

N5

N6

SD_A4

P3

P8

R3

SD_A2

SD_A0

SD_BA1

SD_CS

T2

T3

SD_A1

SD_A10

SD_BA0

SD_RAS

SD_A11

SD_DQ1

K10

SD_D8

SD_D9

L11

SD_A7

SD_D10

SD_A9

SD_D11

SD_A8

SD_D13

SD_CAS

SD_D6

SD_D4

SD_D2

SD_D0

R14

SD_DQ0

SD_D7

SD_D5

SD_D3

SD_D1

T14

T15

SD_WE

B1

C2

D1

D4

E5

F1

F2

F5

G1

G2

G5

K5

L4

J1

J2

J6

K1

K2

K6

L1

L2

L6

N1

N2

P1

P2

R1

R4

T4

K8

L7

L8

M6

M7

M8

N3

N5

N6

N8

P3

P8

R3

R5

R6

R7

R8

T2

T3

T5

T6

T7

T8

M10

N11

K10

K9

L10

L11

L9

M11

M9

N12

N9

P14

P9

R10

R11

R12

R13

R14

R9

T10

T11

T12

T13

T14

T15

T9

P1-2

IO_B1_ B1/ DQS2L/CQ3L

IO_B1_ C2/ DIFFIO_L1P

IO_B1_ D1/ DIFFIO_L2N

IO_B1_ D4

IO_B1_ E5

IO_B1_ F1/ DIFFIO_L3N

IO_B1_ F2/ DIFFIO_L3P

IO_B1_ F5

IO_B1_ G1/ DIFFIO_L4N

IO_B1_ G2/ DIFFIO_L4P/ DQS0L/CQ1L,DPCLK0

IO_B1_ G5

IO_B2_ K5/ RUP1/ DQ1L

IO_B2_ L4/ RDN1/ DQ1L

IO_B2_ J1/ DIFFIO_L5N/ DQ1L

IO_B2_ J2/ DIFFIO_L5P/ DQ1L

IO_B2_ J6

IO_B2_ K1/ DIFFIO_L7N/ DQ1L

IO_B2_ K2/ DIFFIO_L7P

IO_B2_ K6/ DIFFIO_L6P

IO_B2_ L1/ DIFFIO_L8N/ DQ1L

IO_B2_ L2/ DIFFIO_L8P/ DQS1L/CQ1L#,DPCLK1

IO_B2_ L6/ DIFFIO_L6N

IO_B2_ N1/ DIFFIO_L9N/ DQ1L

IO_B2_ N2/ DIFFIO_L9P/ DQ1L

IO_B2_ P1/ DIFFIO_L10N/ DM1L/BWS#1L

IO_B2_ P2/ DIFFIO_L10P/ DQ1L

IO_B2_ R1/ DQS3L/CQ3L#

IO_B3_ R4/ PLL1_CLKOUTP

IO_B3_ T4/ PLL1_CLKOUTN

IO_B3_ K8/ DIFFIO_B5N

IO_B3_ L7/ DQ3B

IO_B3_ L8/ DIFFIO_B9P/ DQ3B

IO_B3_ M6/ DQ3B

IO_B3_ M7/ DIFFIO_B5P/ DQS3B/CQ3B#

IO_B3_ M8/ DIFFIO_B9N/ DM5B/BWS#5B

IO_B3_ N3/ DIFFIO_B1P

IO_B3_ N5/ DIFFIO_B4P/ DQ3B

IO_B3_ N6/ DIFFIO_B4N/ DQ3B

IO_B3_ N8/ DIFFIO_B10P/ DQ5B

IO_B3_ P3/ DIFFIO_B1N/ DM3B/BWS#3B

IO_B3_ P8/ DIFFIO_B10N/ DQ5B

IO_B3_ R3/ DIFFIO_B2P/ DQ3B

IO_B3_ R5/ DIFFIO_B6P/ DQ3B

IO_B3_ R6/ DIFFIO_B7P/ DQ3B

IO_B3_ R7/ DIFFIO_B8P/ DQ3B

IO_B3_ R8/ DIFFIO_B11P

IO_B3_ T2/ DQS1B/CQ1B#,DPCLK2

IO_B3_ T3/ DIFFIO_B2N

IO_B3_ T5/ DIFFIO_B6N

IO_B3_ T6/ DIFFIO_B7N

IO_B3_ T7/ DIFFIO_B8N/ DQS5B/CQ5B#

IO_B3_ T8/ DIFFIO_B11N

IO_B4_ M10/ RUP2

IO_B4_ N11/ RDN2

IO_B4_ K10/ DIFFIO_B18P

IO_B4_ K9/ DIFFIO_B13P

IO_B4_ L10/ DIFFIO_B18N

IO_B4_ L11/ DIFFIO_B21N

IO_B4_ L9/ DIFFIO_B13N

IO_B4_ M11/ DIFFIO_B22P

IO_B4_ M9/ DIFFIO_B14P

IO_B4_ N12/ DIFFIO_B22N

IO_B4_ N9/ DIFFIO_B14N/ DQ5B

IO_B4_ P14/ DIFFIO_B21P

IO_B4_ P9/ DQS2B/CQ3B

IO_B4_ R10/ DIFFIO_B15P/ DQ5B

IO_B4_ R11/ DIFFIO_B16P/ DQ5B

IO_B4_ R12/ DIFFIO_B17P/ DQ5B

IO_B4_ R13/ DIFFIO_B19P

IO_B4_ R14

IO_B4_ R9/ DIFFIO_B12P

IO_B4_ T10/ DIFFIO_B15N/ DQS4B/CQ5B

IO_B4_ T11/ DIFFIO_B16N

IO_B4_ T12/ DIFFIO_B17N/ DQ5B

IO_B4_ T13/ DIFFIO_B19N/ DQ5B

IO_B4_ T14/ DIFFIO_B20P/ DQ5B

IO_B4_ T15/ DIFFIO_B20N/ DQS0B/CQ1B,DPCLK3

IO_B4_ T9/ DIFFIO_B12N

EP4CE10F17C8N

VERSION : 1.0

PAGE : 2 of 5

DATE : March 2010

D3V3

R55

10K

F

P

G

A

_

K

E

Y

K2

FPGA_KEY

C93

104

DCOM

U17

RGBLED

R

R56

1K

FPGA_LEDR

D3V3

A

G

R57

1K

FPGA_LEDG

B

R59

1K

FPGA_LEDB

IO_B5_ N14/ RUP3/ DM1R/BWS#1R

IO_B5_ P15/ RDN3/ DQ1R

IO_B5_ J11

IO_B5_ J12/ DIFFIO_R6P

IO_B5_ J13/ DQ1R

IO_B5_ J14/ DIFFIO_R6N/ DQ1R

IO_B5_ K11

IO_B5_ K12

IO_B5_ K15/ DIFFIO_R8P/ DQS1R/CQ1R#,DPCLK4

IO_B5_ K16/ DIFFIO_R8N/ DQ1R

IO_B5_ L12

IO_B5_ L13/ DQ1R

IO_B5_ L15/ DIFFIO_R9P

IO_B5_ L16/ DIFFIO_R9N/ DQ1R

IO_B5_ M12

IO_B5_ N13

IO_B5_ N15/ DIFFIO_R10P/ DQ1R

IO_B5_ N16/ DIFFIO_R10N/ DQ1R

IO_B5_ P16/ DIFFIO_R11N/ DQS3R/CQ3R#

IO_B5_ R16/ DIFFIO_R11P/ DQ1R

IO_B6_ B16/ DQS0R/CQ1R,DPCLK5

IO_B6_ C15/ DIFFIO_R1P

IO_B6_ C16/ DIFFIO_R1N/ DQS2R/CQ3R

IO_B6_ D15/ DIFFIO_R2P

IO_B6_ D16/ DIFFIO_R2N

IO_B6_ F13

IO_B6_ G11

IO_B7_ E11/ RUP4

IO_B7_ E10/ RDN4

IO_B7_ A14/ PLL2_CLKOUTN

IO_B7_ B14/ PLL2_CLKOUTP

IO_B7_ A10/ DIFFIO_T14N/ DQ5T

IO_B7_ A11/ DIFFIO_T17N/ DQ5T

IO_B7_ A12/ DIFFIO_T18N/ DQ5T

IO_B7_ A13/ DIFFIO_T19N

IO_B7_ A15/ DIFFIO_T15P

IO_B7_ A9/ DIFFIO_T12N

IO_B7_ B10/ DIFFIO_T14P/ DQ5T

IO_B7_ B11/ DIFFIO_T17P/ DQ5T

IO_B7_ B12/ DIFFIO_T18P/ DQ5T

IO_B7_ B13/ DIFFIO_T19P/ DQ5T

IO_B7_ B9/ DIFFIO_T12P

IO_B7_ C14/ DIFFIO_T21N

IO_B7_ C9/ DIFFIO_T13N/ DQ5T

IO_B7_ D11/ DIFFIO_T20N

IO_B7_ D12/ DIFFIO_T20P/ DQS0T/CQ1T,DPCLK6

IO_B7_ D14/ DIFFIO_T21P/ DQ5T

IO_B7_ D9/ DIFFIO_T13P/ DM5T/BWS#5T

IO_B7_ E9/ DQS4T/CQ5T

IO_B7_ F10/ DIFFIO_T16N

IO_B7_ F11/ DIFFIO_T15N

IO_B7_ F9/ DIFFIO_T16P/ DQS2T/CQ3T

IO_B8_ A2/ DIFFIO_T5N

IO_B8_ A3/ DIFFIO_T2N

IO_B8_ A4/ DIFFIO_T4N/ DM3T/BWS#3T

IO_B8_ A6/ DIFFIO_T7N/ DQS3T/CQ3T#

IO_B8_ A7/ DIFFIO_T9N/ DQ3T

IO_B8_ A8/ DIFFIO_T11N

IO_B8_ B3/ DIFFIO_T2P/ DQS1T/CQ1T#,DPCLK7

IO_B8_ B4/ DIFFIO_T4P

IO_B8_ B5/ DIFFIO_T5P/ DQ3T

IO_B8_ B6/ DIFFIO_T7P/ DQ3T

IO_B8_ B8/ DIFFIO_T11P

IO_B8_ C3/ DIFFIO_T1N

IO_B8_ C8/ DQS5T/CQ5T#

IO_B8_ D3/ DIFFIO_T1P

IO_B8_ D5/ DIFFIO_T3N

IO_B8_ D6/ DIFFIO_T3P

IO_B8_ D8/ DQ3T

IO_B8_ F6/ DIFFIO_T8N

IO_B8_ F7/ DIFFIO_T8P

N14

P15

J11

J12

J13

J14

K11

K12

K15

K16

L12

L13

L15

L16

M12

N13

N15

N16

P16

R16

B16

C15

C16

D15

D16

F13

G11

E11

E10

A14

B14

A10

A11

A12

A13

A15

A9

B10

B11

B12

B13

B9

C14

C9

D11

D12

D14

D9

E9

F10

F11

F9

A2

A3

A4

A6

A7

A8

B3

B4

B5

B6

B8

C3

C8

D3

D5

D6

D8

F6

F7

SD_D14

P15

J11

J12

J13

J14

K11

K12

K15

K16

L12

L13

L15

L16

SD_D15

SD_D12

N15

N16

P16

R16

B16

C15

C16

D15

D16

FPGA_LEDG

G11

FPGA_LEDB

DB6

A14

B14

NADV

A19

A21

A13

A15

A24

A23

A20

A22

B13

A25

C14

DB8

DB4

D12

D14

DB7

DB9

F10

F11

DB10

A2

A3

DB0

DB3

RD

NWAIT

B3

DB1

A18

DB2

WR

C3

CS0

D3

D5

D6

DB13

F6

DB14

IO 105

F3

L3

P6

SD_CKE

L14

FPGA_LEDR

DB5

A16

F3

L3

P6

P11

L14

F14

C11

C6

P1-3

VREFB1N0

VREFB2N0

VREFB3N0

VREFB4N0

VREFB5N0

VREFB6N0

VREFB7N0

VREFB8N0

CLK1_ E1/ DIFFCLK_0N

CLK2_ M2/ DIFFCLK_1P

CLK3_ M1/ DIFFCLK_1N

CLK4_ E15/ DIFFCLK_2P

CLK5_ E16/ DIFFCLK_2N

CLK6_ M15/ DIFFCLK_3P

CLK7_ M16/ DIFFCLK_3N

E1

M2

M1

E15

E16

M15

M16

1

CLK_25M

M2_INPUT

M1_INPUT

CLK_24M

E16_INPUT

M15_INPUT

M16_INPUT

EP4CE10F17C8N

VERSION : 1.0

PAGE : 3 of 5

DATE : March 2010

D3V3_FPGA

D

R50 1K

R51 1K

R52 1K

DATA0

ASDO

DB12

DB11

FSMC_CLK

DB15

E6

A17

F15

G15

J15

J16

nCSO

G16

F16

H2

C1

E8

F8

B7

E7

E6

A5

F15

G15

J15

J16

D2

G16

F16

P1-4

IO_B1_ H2/ DATA0

IO_B1_ C1/ DIFFIO_L1N/ DATA1,ASDO

IO_B8_ E8/ DIFFIO_T10N/ DATA2/ DQ3T

IO_B8_ F8/ DIFFIO_T10P/ DATA3

IO_B8_ B7/ DIFFIO_T9P/ DATA4/ DQ3T

IO_B8_ E7/ DATA5/ DQ3T

IO_B8_ E6/ DATA6/ DQ3T

IO_B8_ A5/ DIFFIO_T6N/ DATA7/ DQ3T

IO_B6_ F15/ DIFFIO_R3P/ CLKUSR

IO_B6_ G15/ DIFFIO_R4P/ CRC_ERROR

IO_B5_ J15/ DIFFIO_R7P/ DEV_CLRN

IO_B5_ J16/ DIFFIO_R7N/ DEV_OE

IO_B1_ D2/ DIFFIO_L2P/ FLASH_NCE,NCSO

IO_B6_ G16/ DIFFIO_R4N/ INIT_DONE

IO_B6_ F16/ DIFFIO_R3N/ NCEO

CONF_DONE

DCLK

MSEL0

MSEL1

MSEL2

NCE

NCONFIG

NSTATUS

TCK

TDI

TDO

TMS

H14

H1

H13

H12

G12

J3

H5

F4

H3

H4

J4

J5

CONF_DONE

DCLK

MSEL1

nCONFIG

nSTATUS

TCK

TDI

TDO

TMS

DCOM

EP4CE10F17C8N

VERSION : 1.0

PAGE : 4 of 5

DATE : March 2010

C15

G16

K11

L13

L14

L11

C15

G16

K11

L13

L14

L11

FPGA_KEY

F5

J6

M1_INPUT

M7

N1

P8

FPGA_KEY

F5

J6

M1_INPUT

M7

N1

P8

B13

B14

B16

C16

D16

F15

G15

D12

FPGA_LEDB

FPGA_LEDR

G11

K10

J11

J12

J14

J15

K15

L15

M15_INPUT

N15

P15

T15

T14

B3

F6

D6

D4

D3

E5

B1

D1

F1

G1

J2

K2

K8

K6

L4

N3

M6

N6

L7

M2_INPUT

P1

R1

R3

B13

B14

B16

C16

D16

F15

G15

D12

FPGA_LEDB

FPGA_LEDR

G11

K10

J11

J12

J14

J15

K15

L15

M15_INPUT

N15

P15

T15

T14

B3

F6

D6

D4

D3

E5

B1

D1

F1

G1

J2

K2

K8

K6

L4

N3

M6

N6

L7

M2_INPUT

P1

R1

R3

A13

A14

A15

C15

D15

E16_INPUT

F16

F15

C14

D14

FPGA_LEDG

F11

F10

K12

J13

L12

J16

K16

L16

M16_INPUT

N16

P16

R16

R14

A13

A14

A15

C15

D15

E16_INPUT

F16

F15

C14

D14

FPGA_LEDG

F11

F10

K12

J13

L12

J16

K16

L16

M16_INPUT

N16

P16

R16

R14

A3

A2

G5

D5

C3

E6

F3

F2

G2

J1

K1

L1

L2

K5

L3

L6

P3

N5

P6

N2

P2

T2

T3

A3

A2

G5

D5

C3

E6

F3

F2

G2

J1

K1

L1

L2

K5

L3

L6

P3

N5

P6

N2

P2

T2

T3

C

B

A

D1V2

D3V3_FPGA

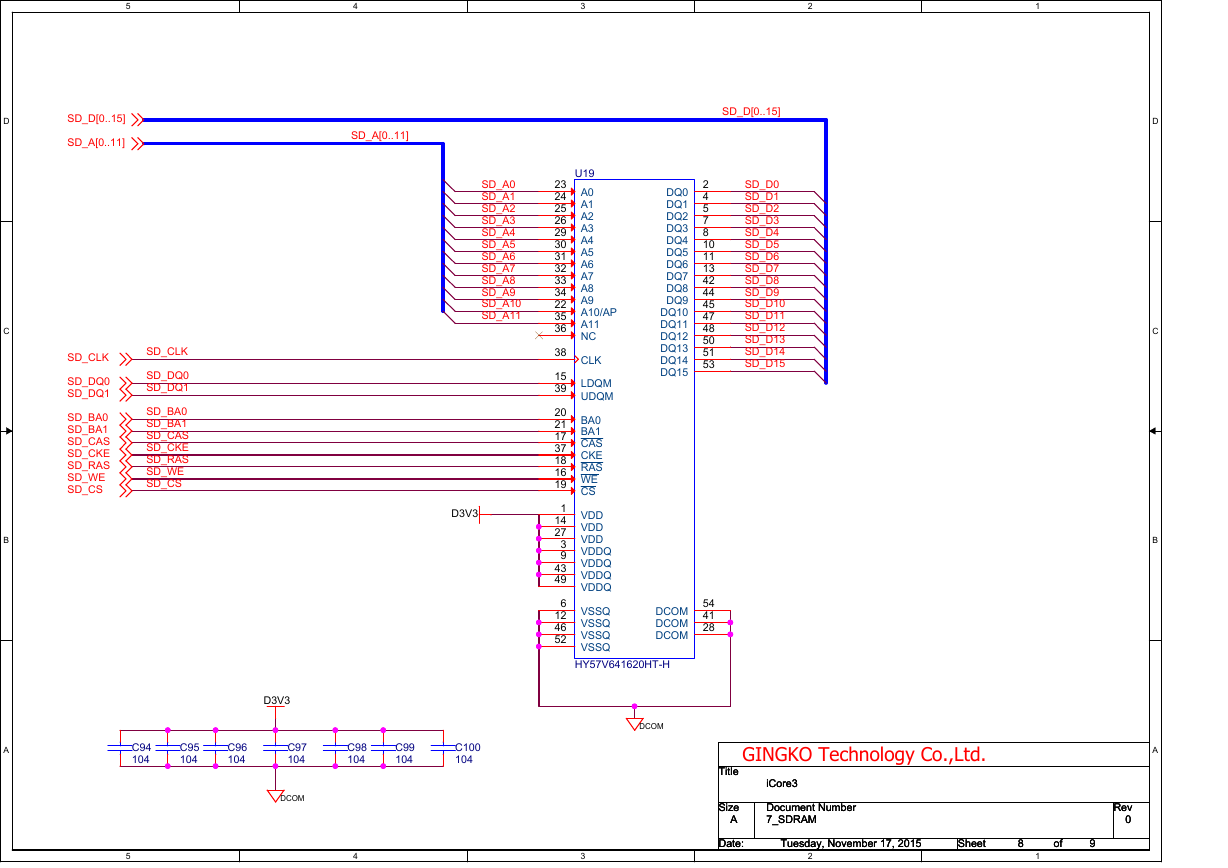

SDRAM (38 I/O'S)

G10

G6

G7

G8

G9

H11

H6

K7

E3

L5

F12

N4

D13

P1-1

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCIO1

VCCA1

VCCA2

VCCD_PLL1

VCCD_PLL2

D3V3_FPGA

A2V5

D1V2

VCCIO1

VCCIO2

VCCIO2

VCCIO3

VCCIO3

VCCIO3

VCCIO4

VCCIO4

VCCIO4

VCCIO5

VCCIO5

VCCIO6

VCCIO6

VCCIO7

VCCIO7

VCCIO7

VCCIO8

VCCIO8

VCCIO8

G3

K3

M3

P4

P7

T1

P10

P13

T16

K14

M14

E14

G14

A16

C10

C13

A1

C4

C7

EP4CE10F17C8N

VERSION : 1.0

PAGE : 1 of 5

DATE : March 2010

B15

B2

C12

C5

D10

D7

E13

E2

E4

G13

G4

H10

H15

H16

H7

H8

H9

P1-5

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDA1

GNDA2

J10

J7

J8

J9

K13

K4

M13

M4

N10

N7

P12

P5

R15

R2

M5

E12

DCOM

EP4CE10F17C8N

VERSION : 1.0

PAGE : 5 of 5

DATE : March 2010

DCOM

SD_CLK

SD_CAS

SD_CKE

SD_CS

SD_RAS

SD_WE

SD_BA0

SD_BA1

SD_DQ0

SD_DQ1

SD_A[0..11]

SD_D[0..15]

SD_CLK

SD_CAS

SD_CKE

SD_CS

SD_RAS

SD_WE

SD_BA0

SD_BA1

SD_DQ0

SD_DQ1

SD_A[0..11]

SD_D[0..15]

Title

Title

Title

Size

Size

Size

C

C

C

Date:

Date:

Date:

GINGKO Technology Co.,Ltd.

iCore3

iCore3

iCore3

Document Number

Document Number

Document Number

6_FPGA

6_FPGA

6_FPGA

Rev

Rev

Rev

0

0

0

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

1

Sheet

Sheet

Sheet

7

7

7

of

of

of

9

9

9

5

4

3

2

�

5

4

3

2

1

D

C

B

A

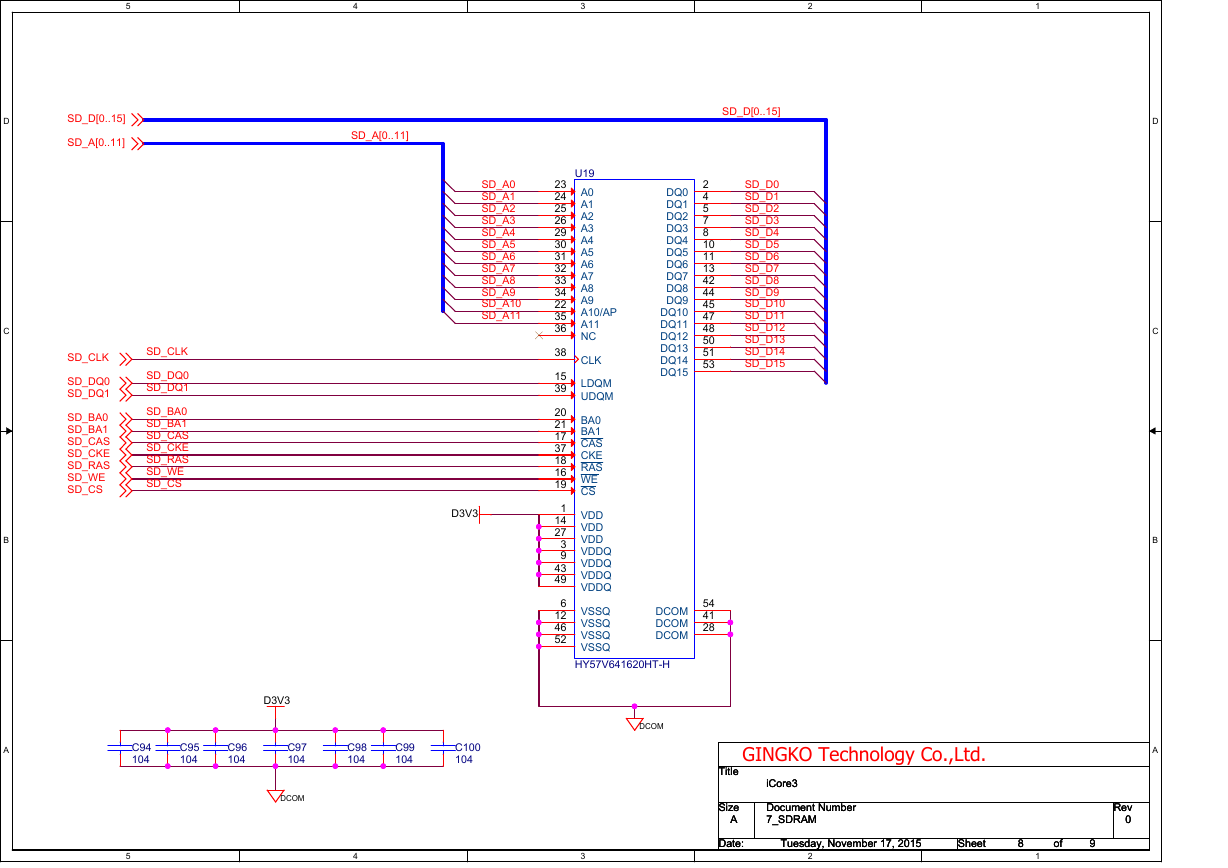

SD_D[0..15]

SD_A[0..11]

SD_A[0..11]

SD_CLK

SD_DQ0

SD_DQ1

SD_BA0

SD_BA1

SD_CAS

SD_CKE

SD_RAS

SD_WE

SD_CS

SD_CLK

SD_DQ0

SD_DQ1

SD_BA0

SD_BA1

SD_CAS

SD_CKE

SD_RAS

SD_WE

SD_CS

SD_D[0..15]

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

SD_D0

SD_D1

SD_D2

SD_D3

SD_D4

SD_D5

SD_D6

SD_D7

SD_D8

SD_D9

SD_D10

SD_D11

SD_D12

SD_D13

SD_D14

SD_D15

DCOM

DCOM

DCOM

54

41

28

SD_A0

SD_A1

SD_A2

SD_A3

SD_A4

SD_A5

SD_A6

SD_A7

SD_A8

SD_A9

SD_A10

SD_A11

D3V3

23

24

25

26

29

30

31

32

33

34

22

35

36

38

15

39

20

21

17

37

18

16

19

1

14

27

3

9

43

49

6

12

46

52

U19

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

NC

CLK

LDQM

UDQM

BA0

BA1

CAS

CKE

RAS

WE

CS

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

D3V3

HY57V641620HT-H

DCOM

C94

104

C95

104

C96

104

C97

104

C98

104

C99

104

C100

104

GINGKO Technology Co.,Ltd.

DCOM

Title

Title

Title

Size

Size

Size

A

A

A

iCore3

iCore3

iCore3

Document Number

Document Number

Document Number

7_SDRAM

7_SDRAM

7_SDRAM

Rev

Rev

Rev

0

0

0

5

4

3

2

1

Date:

Date:

Date:

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Tuesday, November 17, 2015

Sheet

Sheet

Sheet

8

8

8

of

of

of

9

9

9

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc