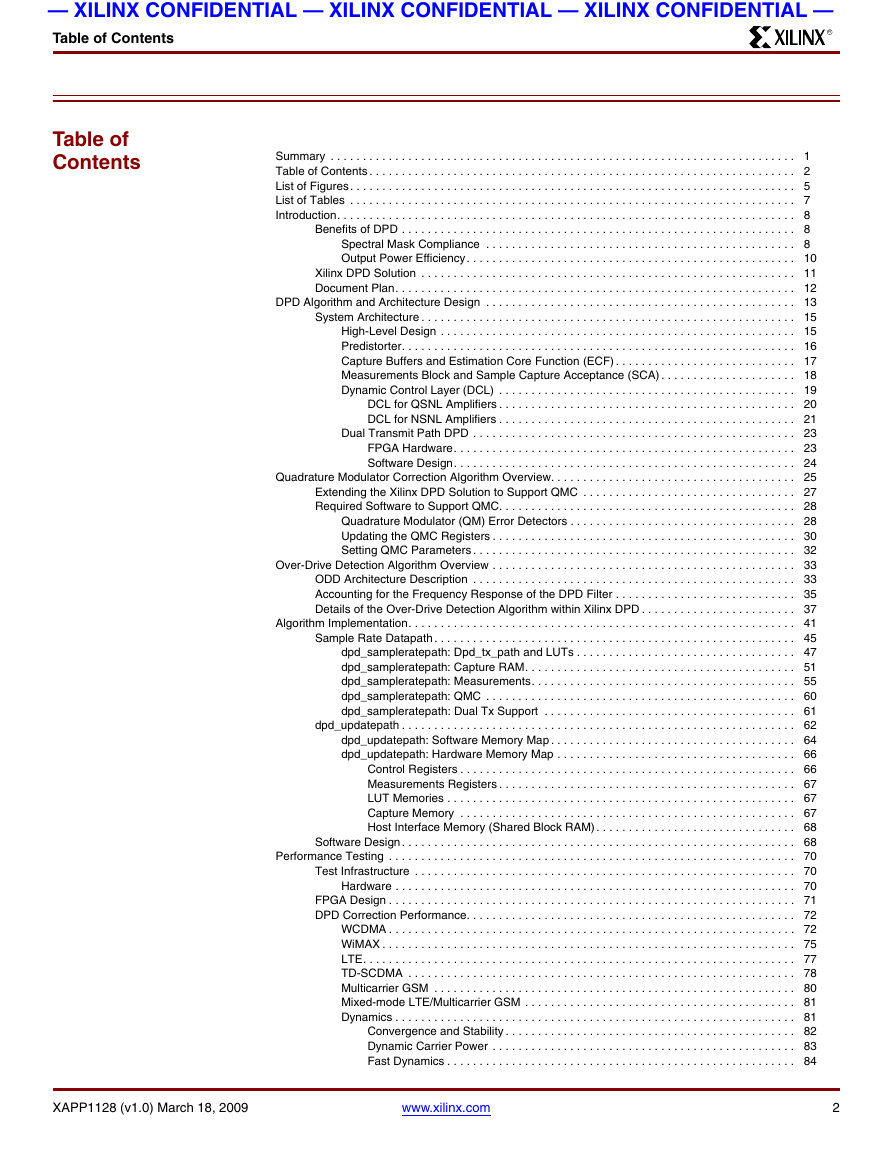

Digital Predistortion v2.0

Summary

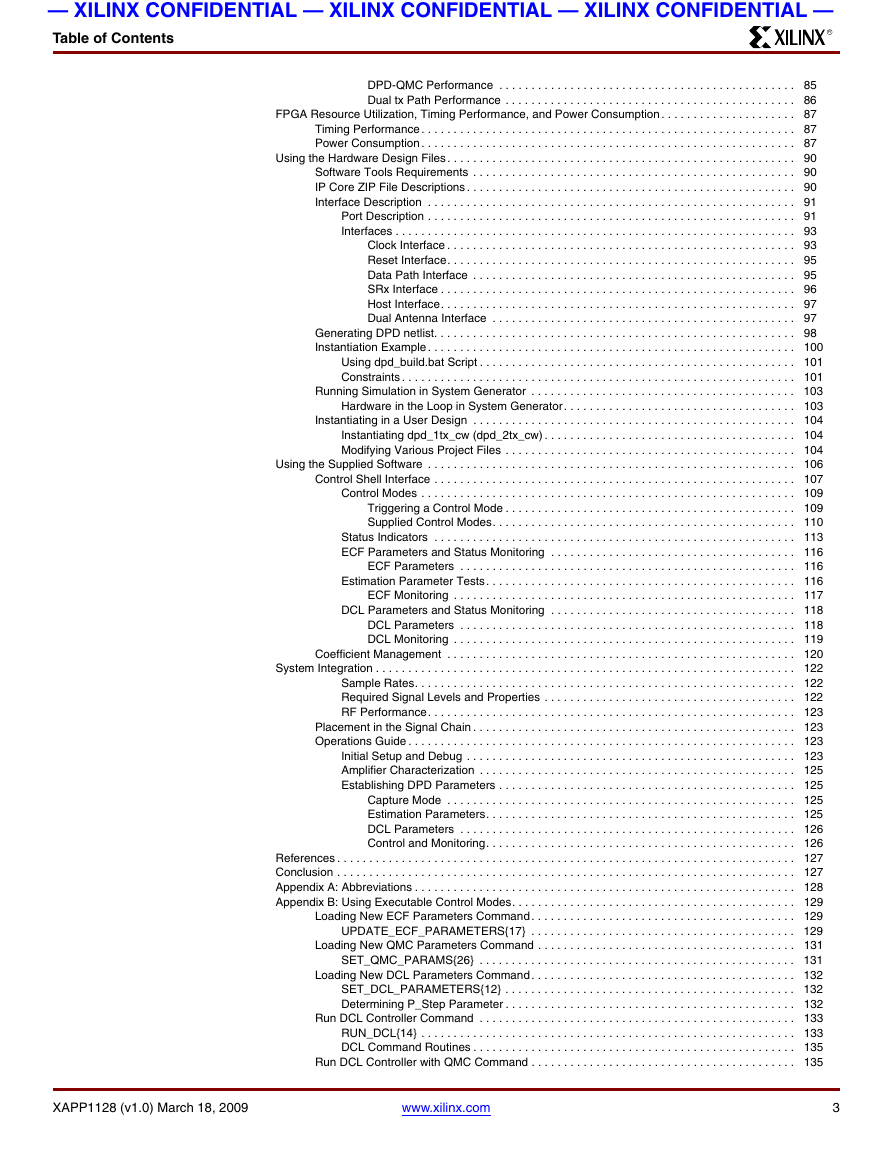

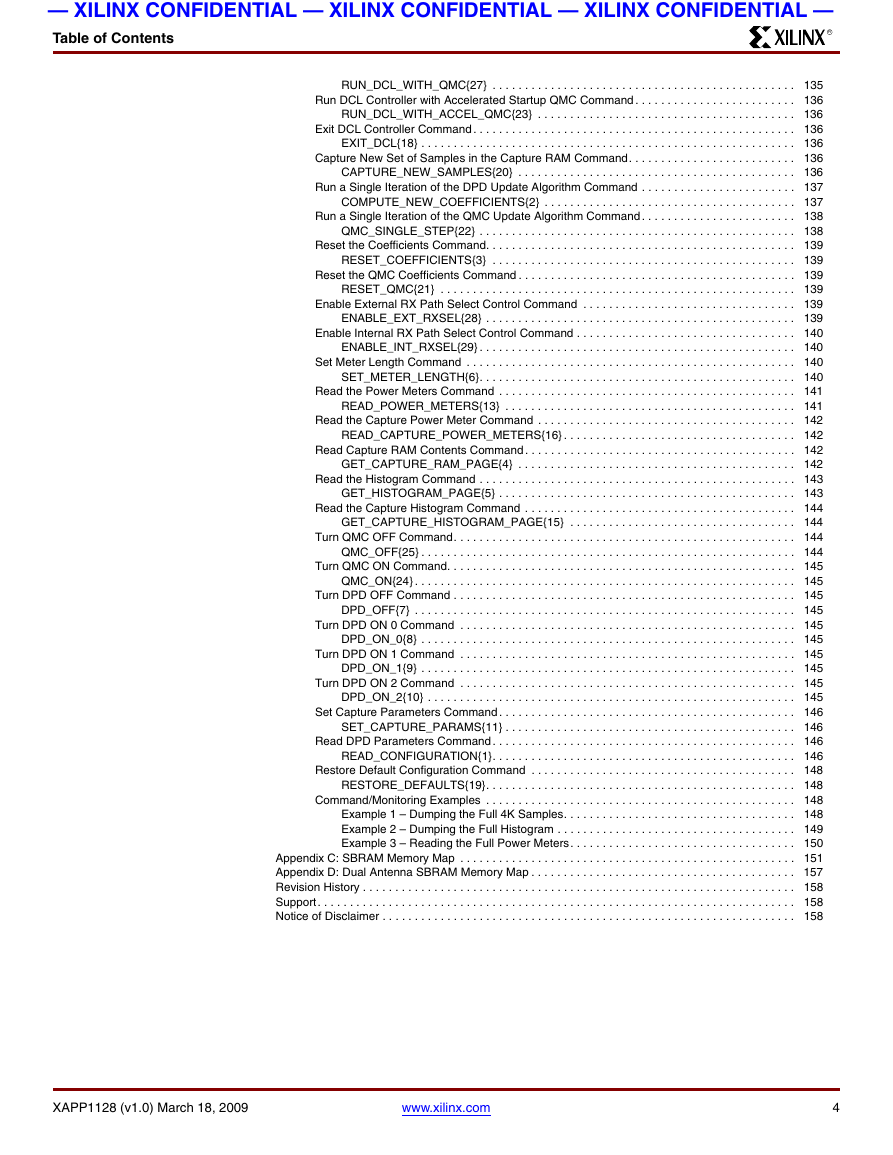

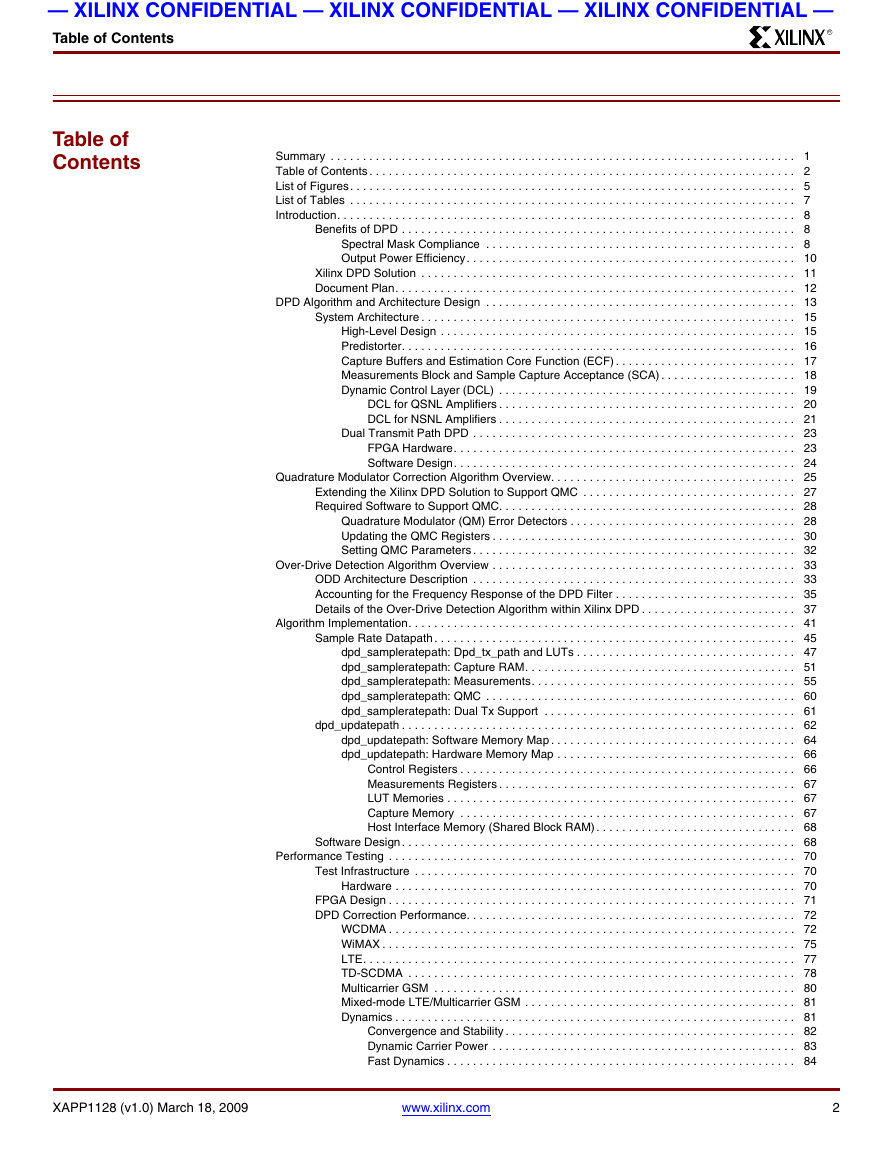

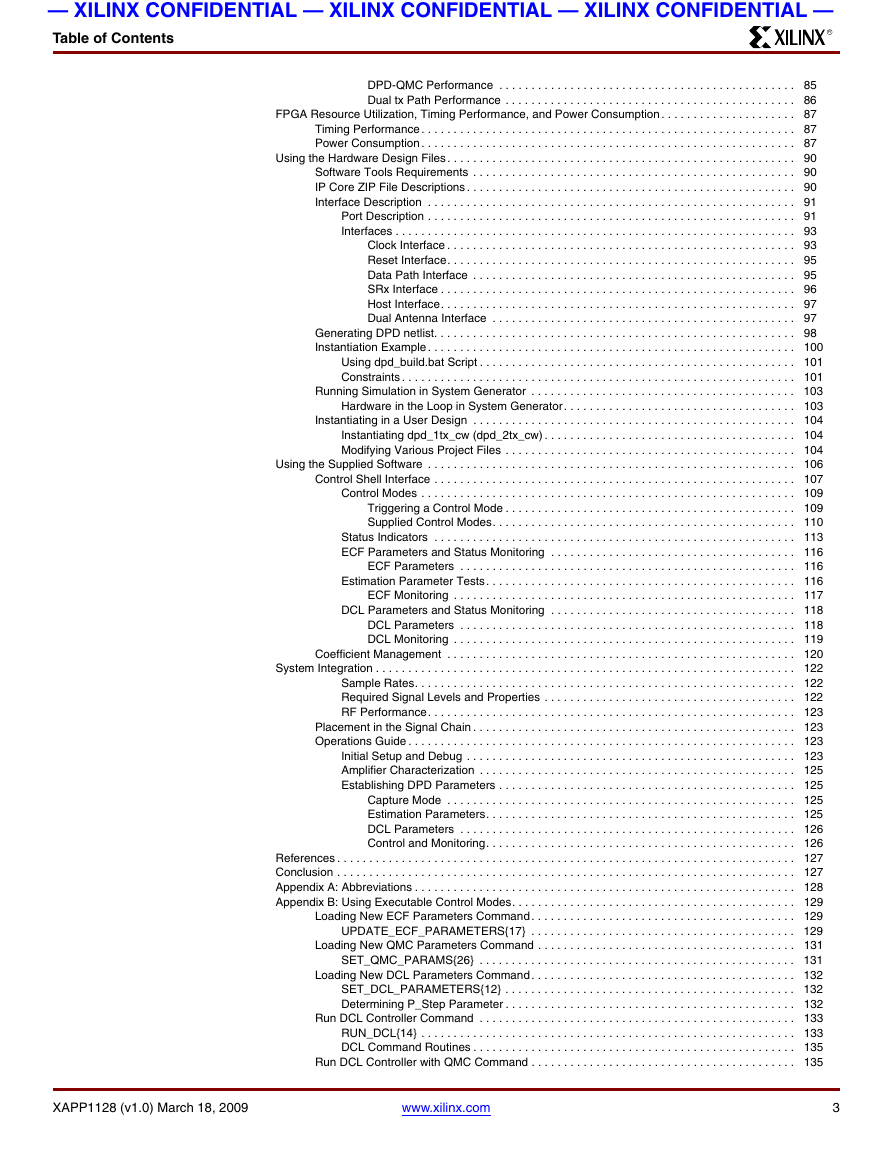

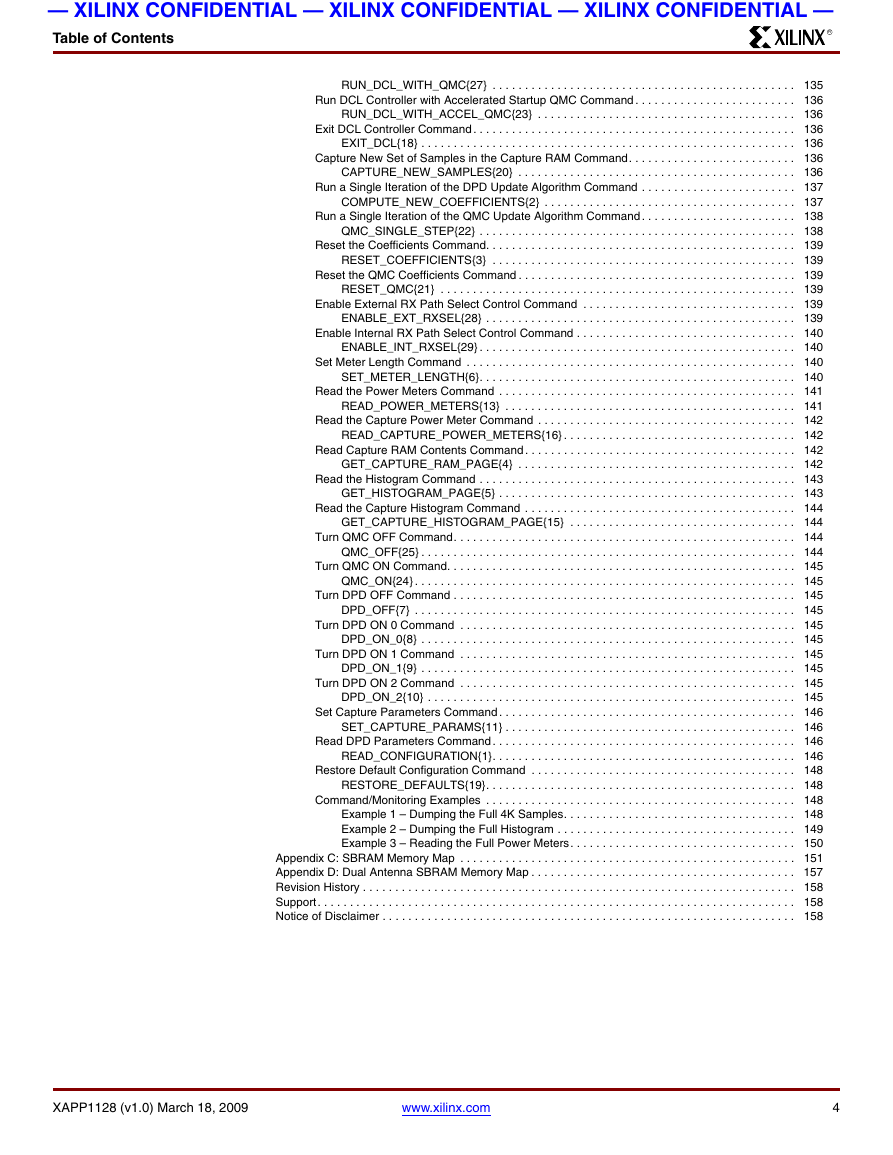

Table of Contents

List of Figures

List of Tables

Introduction

Benefits of DPD

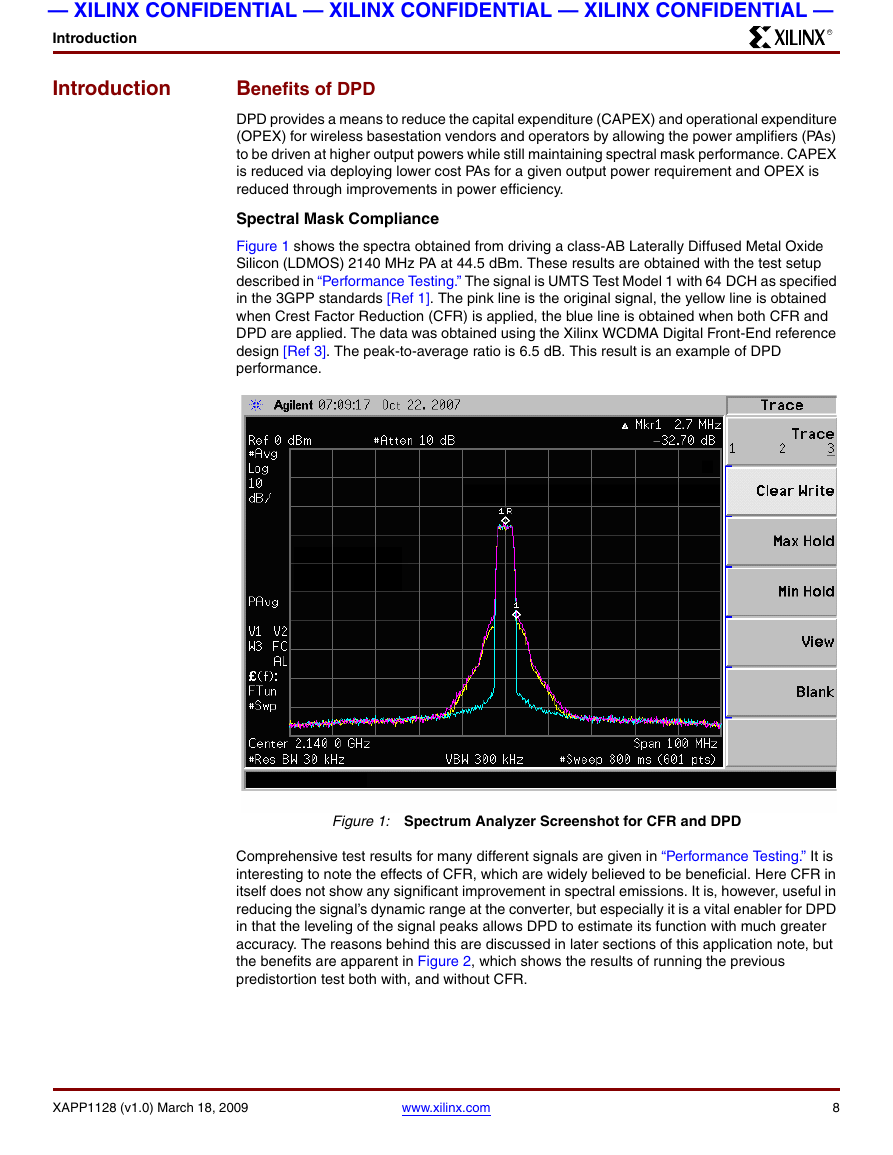

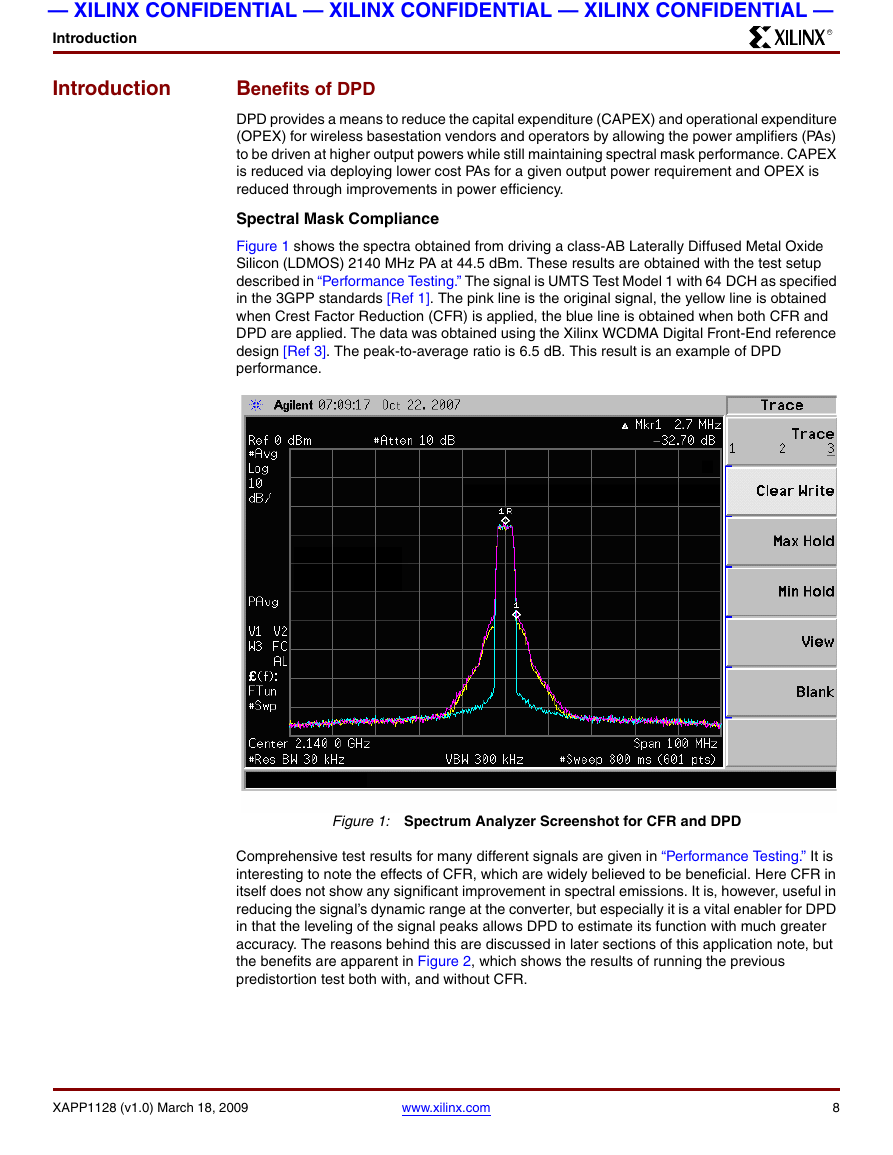

Spectral Mask Compliance

Output Power Efficiency

Xilinx DPD Solution

Document Plan

DPD Algorithm and Architecture Design

Mathematical Foundation

System Architecture

High-Level Design

Predistorter

Capture Buffers and Estimation Core Function (ECF)

Measurements Block and Sample Capture Acceptance (SCA)

Dynamic Control Layer (DCL)

Dual Transmit Path DPD

Quadrature Modulator Correction Algorithm Overview

Introduction

Extending the Xilinx DPD Solution to Support QMC

Required Software to Support QMC

Quadrature Modulator (QM) Error Detectors

Updating the QMC Registers

Setting QMC Parameters

Over-Drive Detection Algorithm Overview

Overview

ODD Architecture Description

Accounting for the Frequency Response of the DPD Filter

Details of the Over-Drive Detection Algorithm within Xilinx DPD

Algorithm Implementation

Overall Structure

Sample Rate Datapath

dpd_sampleratepath: Dpd_tx_path and LUTs

dpd_sampleratepath: Capture RAM

dpd_sampleratepath: Measurements

dpd_sampleratepath: QMC

dpd_sampleratepath: Dual Tx Support

dpd_updatepath

dpd_updatepath: Software Memory Map

dpd_updatepath: Hardware Memory Map

Software Design

Performance Testing

Test Infrastructure

Hardware

FPGA Design

DPD Correction Performance

WCDMA

WiMAX

LTE

TD-SCDMA

Multicarrier GSM

Mixed-mode LTE/Multicarrier GSM

Dynamics

FPGA Resource Utilization, Timing Performance, and Power Consumption

FPGA Resource Utilization

Timing Performance

Power Consumption

Using the Hardware Design Files

Overview

Software Tools Requirements

IP Core ZIP File Descriptions

Interface Description

Port Description

Interfaces

Generating DPD netlist

Instantiation Example

Using dpd_build.bat Script

Constraints

Running Simulation in System Generator

Hardware in the Loop in System Generator

Instantiating in a User Design

Instantiating dpd_1tx_cw (dpd_2tx_cw)

Modifying Various Project Files

Using the Supplied Software

Control Shell Interface

Control Modes

Status Indicators

ECF Parameters and Status Monitoring

Estimation Parameter Tests

DCL Parameters and Status Monitoring

Coefficient Management

System Integration

Requirements

Sample Rates

Required Signal Levels and Properties

RF Performance

Placement in the Signal Chain

Operations Guide

Initial Setup and Debug

Amplifier Characterization

Establishing DPD Parameters

References

Conclusion

Appendix A: Abbreviations

Appendix B: Using Executable Control Modes

Selecting Which Port to Control

Loading New ECF Parameters Command

UPDATE_ECF_PARAMETERS{17}

Loading New QMC Parameters Command

SET_QMC_PARAMS{26}

Loading New DCL Parameters Command

SET_DCL_PARAMETERS{12}

Determining P_Step Parameter

Run DCL Controller Command

RUN_DCL{14}

DCL Command Routines

Run DCL Controller with QMC Command

RUN_DCL_WITH_QMC{27}

Run DCL Controller with Accelerated Startup QMC Command

RUN_DCL_WITH_ACCEL_QMC{23}

Exit DCL Controller Command

EXIT_DCL{18}

Capture New Set of Samples in the Capture RAM Command

CAPTURE_NEW_SAMPLES{20}

Run a Single Iteration of the DPD Update Algorithm Command

COMPUTE_NEW_COEFFICIENTS{2}

Run a Single Iteration of the QMC Update Algorithm Command

QMC_SINGLE_STEP{22}

Reset the Coefficients Command

RESET_COEFFICIENTS{3}

Reset the QMC Coefficients Command

RESET_QMC{21}

Enable External RX Path Select Control Command

ENABLE_EXT_RXSEL{28}

Enable Internal RX Path Select Control Command

ENABLE_INT_RXSEL{29}

Set Meter Length Command

SET_METER_LENGTH{6}

Read the Power Meters Command

READ_POWER_METERS{13}

Read the Capture Power Meter Command

READ_CAPTURE_POWER_METERS{16}

Read Capture RAM Contents Command

GET_CAPTURE_RAM_PAGE{4}

Read the Histogram Command

GET_HISTOGRAM_PAGE{5}

Read the Capture Histogram Command

GET_CAPTURE_HISTOGRAM_PAGE{15}

Turn QMC OFF Command

QMC_OFF{25}

Turn QMC ON Command

QMC_ON{24}

Turn DPD OFF Command

DPD_OFF{7}

Turn DPD ON 0 Command

DPD_ON_0{8}

Turn DPD ON 1 Command

DPD_ON_1{9}

Turn DPD ON 2 Command

DPD_ON_2{10}

Set Capture Parameters Command

SET_CAPTURE_PARAMS{11}

Read DPD Parameters Command

READ_CONFIGURATION{1}

Restore Default Configuration Command

RESTORE_DEFAULTS{19}

Command/Monitoring Examples

Example 1 - Dumping the Full 4K Samples

Example 2 - Dumping the Full Histogram

Example 3 - Reading the Full Power Meters

Appendix C: SBRAM Memory Map

Appendix D: Dual Antenna SBRAM Memory Map

Revision History

Support

Notice of Disclaimer

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc