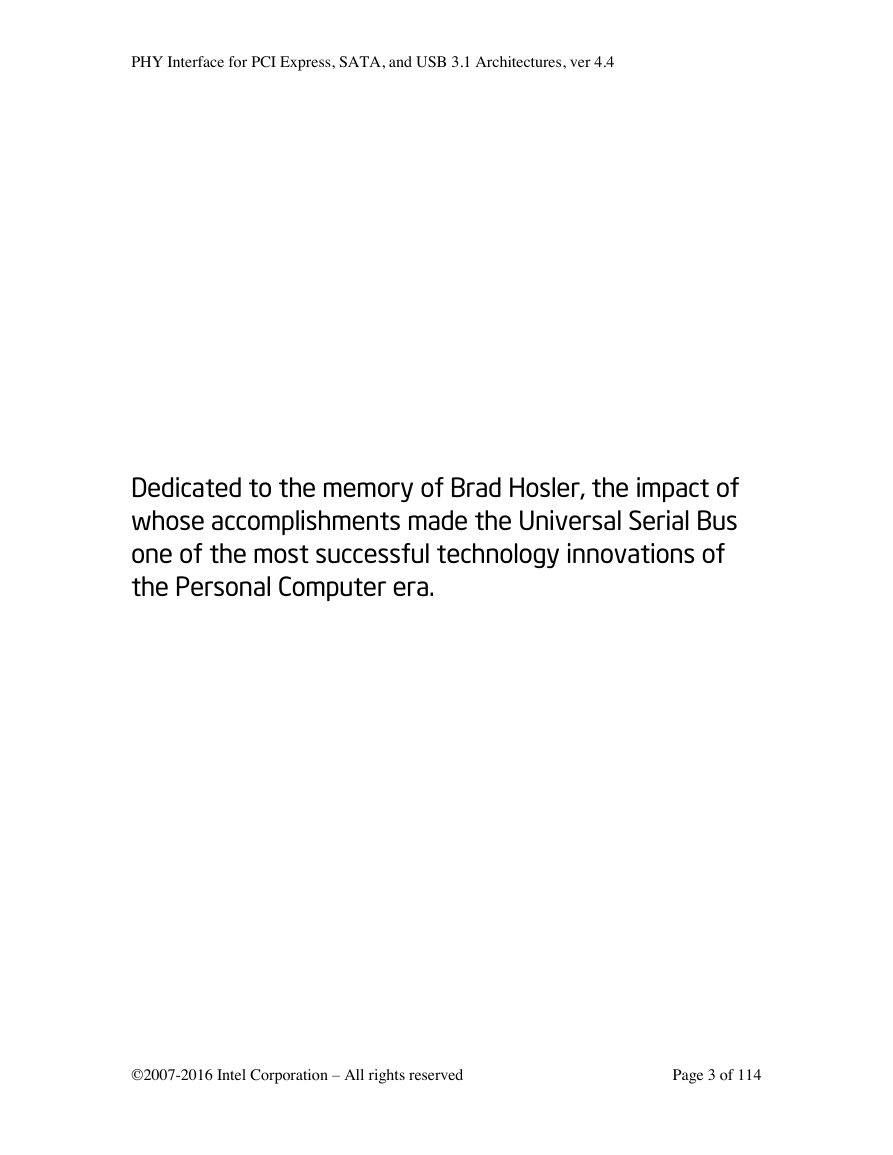

1 Preface

1.1 Scope of this Revision

1.2 Revision History

2 Introduction

2.1 PCI Express PHY Layer

2.2 USB PHY Layer

2.3 SATA PHY Layer

3 PHY/MAC Interface

4 PCI Express and USB PHY Functionality

4.1 Transmitter Block Diagram (2.5 and 5.0 GT/s)

4.2 Transmitter Block Diagram (8.0/10 GT/s)

4.3 Receiver Block Diagram (2.5 and 5.0 GT/s)

4.4 Receiver Block Diagram (8.0/10.0 GT/s)

4.5 Clocking

5 SATA PHY Functionality

5.1 Transmitter Block Diagram (1.5, 3.0, and 6.0 GT/s)

5.2 Receiver Block Diagram (1.5, 3.0 and 6.0 GT/s)

5.3 Clocking

6 PIPE Interface Signal Descriptions

6.1 PHY/MAC Interface Signals

6.1.1 Message Bus Interface

6.1.1.1 Message Bus Interface Commands

6.1.1.2 Message Bus Interface Framing

6.2 External Signals

7 PIPE Message Bus Address Spaces

7.1 PHY Registers

7.1.1 Address 0h: RX Margin Control0

7.1.2 Address 1h: RX Margin Control1

7.1.3 Address 2h: Elastic Buffer Control

7.2 MAC Registers

7.2.1 Address 0h: RX Margin Status0

7.2.2 Address 1h: RX Margin Status1

7.2.3 Address 2h: RX Margin Status2

7.2.4 Address 3h: Elastic Buffer Status

1

8 PIPE Operational Behavior

8.1 Clocking

8.2 Reset

8.3 Power Management – PCI Express Mode

1.1

8.4 Power Management – USB Mode

8.5 Power Management – SATA Mode

8.6 Changing Signaling Rate, PCLK Rate, or Data Bus Width

8.6.1 PCI Express Mode

8.6.2 USB Mode

8.6.3 SATA Mode

8.6.4 Fixed data path implementations

8.6.5 Fixed PCLK implementations

8.7 Transmitter Margining – PCI Express Mode and USB Mode

8.8 Selectable De-emphasis – PCI Express Mode

8.9 Receiver Detection – PCI Express Mode and USB Mode

8.10 Transmitting a beacon – PCI Express Mode

8.11 Transmitting LFPS – USB Mode

8.12 Detecting a beacon – PCI Express Mode

8.13 Detecting Low Frequency Periodic Signaling – USB Mode

8.14 Clock Tolerance Compensation

8.15 Error Detection

8.15.1 8B/10B Decode Errors

8.15.2 Disparity Errors

8.15.3 Elastic Buffer Errors

8.16 Loopback

8.17 Polarity Inversion – PCI Express and USBModes

8.18 Setting negative disparity (PCI Express Mode)

8.19 Electrical Idle – PCI Express Mode

8.20 Link Equalization Evaluation

8.21 Implementation specific timing and selectable parameter support

8.22 Control Signal Decode table – PCI Express Mode

8.23 Control Signal Decode table – USB Mode

8.24 Control Signal Decode table – SATA Mode

8.25 Required synchronous signal timings

8.26 128b/130b Encoding and Block Synchronization (PCI Express 8 GT/s)

8.27 128b/132b Encoding and Block Synchronization (USB 10 GT/s)

8.28 Message Bus Interface

9 Sample Operational Sequences

9.1 Active PM L0 to L0s and back to L0 – PCI Express Mode

9.2 Active PM to L1 and back to L0 - – PCI Express Mode

9.3 Receivers and Electrical Idle – PCI Express Mode Example

9.4 Using CLKREQ# with PIPE – PCI Express Mode

9.5 RX Margining Sequence

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc