T31ZX

Smart Video Application Processor

Data Sheet

Release Date: Jun. 30, 2020

�

T31ZX Smart Video Application Processor

Data Sheet

Copyright © 2005-2020 Ingenic Semiconductor Co. Ltd. All rights reserved.

Disclaimer

This documentation is provided for use with Ingenic products. No license to Ingenic property rights is

granted. Ingenic assumes no liability, provides no warranty either expressed or implied relating to the

usage, or intellectual property right infringement except as provided for by Ingenic Terms and

Conditions of Sale.

Ingenic products are not designed for and should not be used in any medical or life sustaining or

supporting equipment.

All information in this document should be treated as preliminary. Ingenic may make changes to this

document without notice. Anyone relying on this documentation should contact Ingenic for the current

documentation and errata.

Ingenic Semiconductor Co., Ltd.

Ingenic Headquarters, Zhongguancun Software Park,

Dongbeiwang West Road, Haidian District, Beijing, China,

Tel: 86-10-56345000

Fax: 86-10-56345001

Http: //www.ingenic.com

�

CONTENTS

1 Overview ............................................................................................ 1

CONTENTS

1.1

1.2

Block Diagram ......................................................................................................................... 2

Features .................................................................................................................................. 2

CPU ................................................................................................................................. 2

1.2.1

Video Processor Unit ....................................................................................................... 2

1.2.2

Image Signal Processor .................................................................................................. 3

1.2.3

Smart LCD Controller ...................................................................................................... 3

1.2.4

Video input ....................................................................................................................... 3

1.2.5

Audio System .................................................................................................................. 4

1.2.6

Memory Interface ............................................................................................................ 4

1.2.7

System Functions ............................................................................................................ 4

1.2.8

1.2.9

Peripherals ...................................................................................................................... 6

1.2.10 Bootrom ........................................................................................................................... 9

Characteristic .......................................................................................................................... 9

1.3

2 Packaging and Pinout Information ................................................... 10

2.1 Overview ............................................................................................................................... 10

2.2

Solder Process ...................................................................................................................... 10

2.3 Moisture Sensitivity Level ..................................................................................................... 10

2.4

T31ZX Package .................................................................................................................... 10

Pin Description ....................................................................................................................... 11

2.5

2.5.1

Static Memory/DVP/I2Cx/UARTx/PWM/MSC1 .............................................................. 11

2.5.2

SFC ............................................................................................................................... 12

2.5.3

MSC0/GMAC/PWMx/UARTx/I2C1/SSI1/SSI_SLV/JTAG/SLCD/DMIC/I2S .................. 13

2.5.4

System Control .............................................................................................................. 15

Digital IO/core power/ground ........................................................................................ 16

2.5.5

2.5.6

DDR power/ground ........................................................................................................ 16

2.5.7

Analog - USB ................................................................................................................. 16

2.5.8

Analog - MIPI and DVP ................................................................................................. 17

2.5.9

Analog - SARADC ......................................................................................................... 17

2.5.10 Analog - CODEC ........................................................................................................... 17

2.5.11 Analog - EFUSE ............................................................................................................ 18

2.5.12 Analog - CLOCK/PLL .................................................................................................... 18

3 Electrical Specifications ................................................................... 19

3.1

3.2

3.3

3.3.1

3.3.2

3.3.3

Absolute Maximum Ratings .................................................................................................. 19

Recommended operating conditions .................................................................................... 19

Audio codec .......................................................................................................................... 20

Microphone input ........................................................................................................... 20

ALC ................................................................................................................................ 21

Headphone output ......................................................................................................... 21

i

T31ZX Smart Video Application Processor Data Sheet

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

�

CONTENTS

3.3.4

3.4

Microphone bias ............................................................................................................ 22

Power On, Reset and BOOT ................................................................................................. 22

Power-On Timing ........................................................................................................... 22

Reset procedure ............................................................................................................ 23

BOOT ............................................................................................................................. 24

3.4.1

3.4.2

3.4.3

ii

T31ZX Smart Video Application Processor Data Sheet

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

�

1 Overview

Overview

T31ZX is a smart video application processor targeting for video devices like mobile camera, security

survey, video talking, video analysis and so on. This SoC introduces a kind of innovative architecture

to fulfill both high performance computing and high quality image and video encoding requirements

addressed by video devices. T31ZX provides high-speed CPU computing power, excellent image

signal process, fluent 2048x2048 resolution video recording.

The CPU (Central Processing Unit) core, equipped with 32kB instruction and 32kB data L1 cache, and

128kB L2 cache, operating at 1.5GHz, and full feature MMU function performs OS related tasks. At the

heart of the CPU core is XBurst® processor engine. XBurst® is an industry leading microprocessor

core which delivers superior high performance and best-in-class low power consumption. A hardware

floating-point unit which compatible with IEEE754 is also included.

The VPU (Video Processing Unit) core is a video encoder engine designed to process video streams

using the HEVC(ISO/IEC 23008-2 High Efficiency Video Coding) and AVC(ISO/IEC 14496-10

Advanced Video Coding) standards. It also supports still picture encoding using the JPEG

standard(ITU T.81). Together with the on chip video accelerating engine and post image processing

unit, T31ZX delivers high video performance. The maximum resolution of 2592x2048 in the format of

AVC are supported in encoding. up to 40Mbit/s, 2592x1920@25fps.

The ISP (Image signal processor) core supports excellent image process with the image from raw

sensors. It supports DVP,BT and MIPI interface. With the functions, such as 3A, 2D and 3D denoise,

WDR/HDR, lens shading, it can supply maximum resolution 2592x2048 resolution image for view or

encoding to store or transfer.

For more quickly and easily to use T31ZX, 1G bit DDR2 is integrated on chip.

On-chip modules such as audio CODEC, multi-channel SAR-ADC controller and camera interface

offer designers a economical suite of peripherals for video application. WLAN, Bluetooth and

expansion options are supported through high-speed SPI and MMC/SD/SDIO host controllers. Other

peripherals such as USB OTG, MAC, UART and SPI as well as general system resources provide

enough computing and connectivity capability for many applications.

1

T31ZX Smart Video Application Processor Data Sheet

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

�

Overview

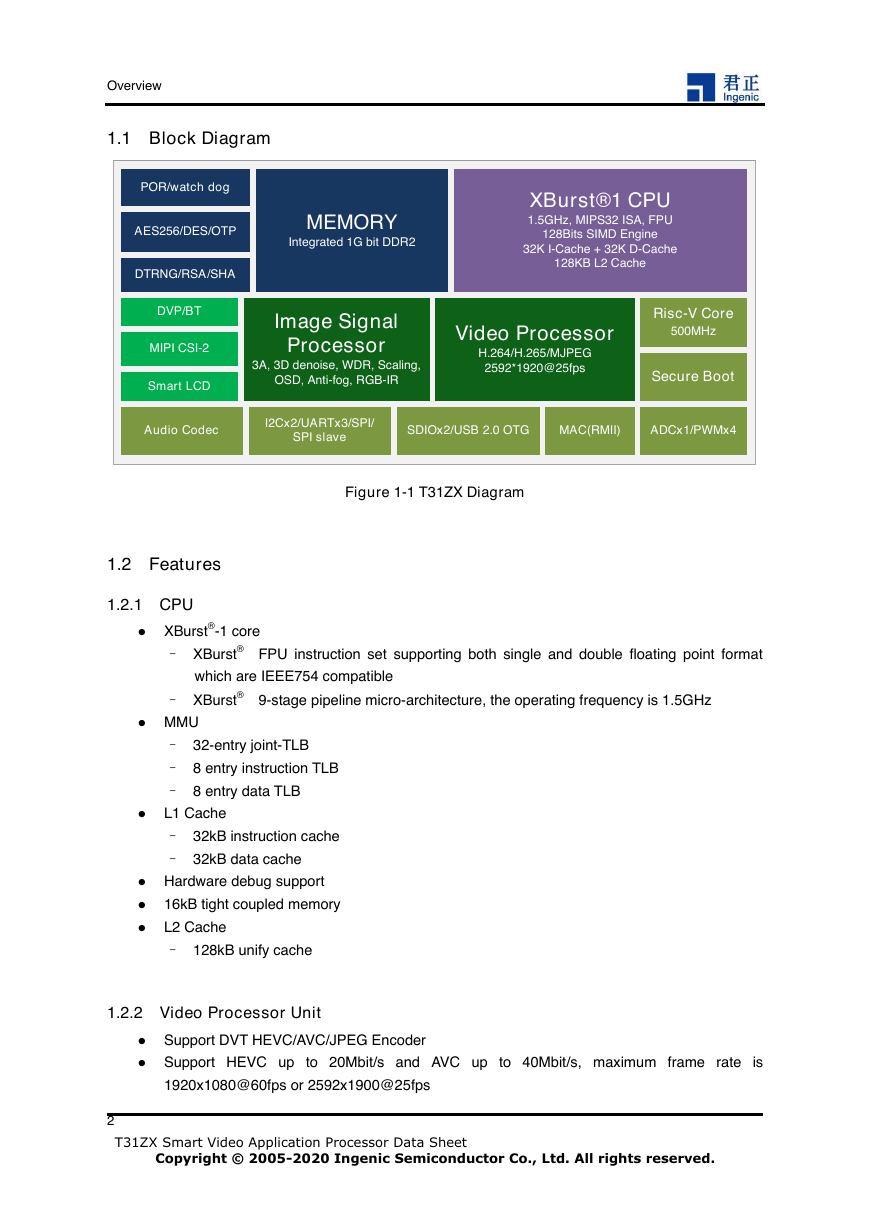

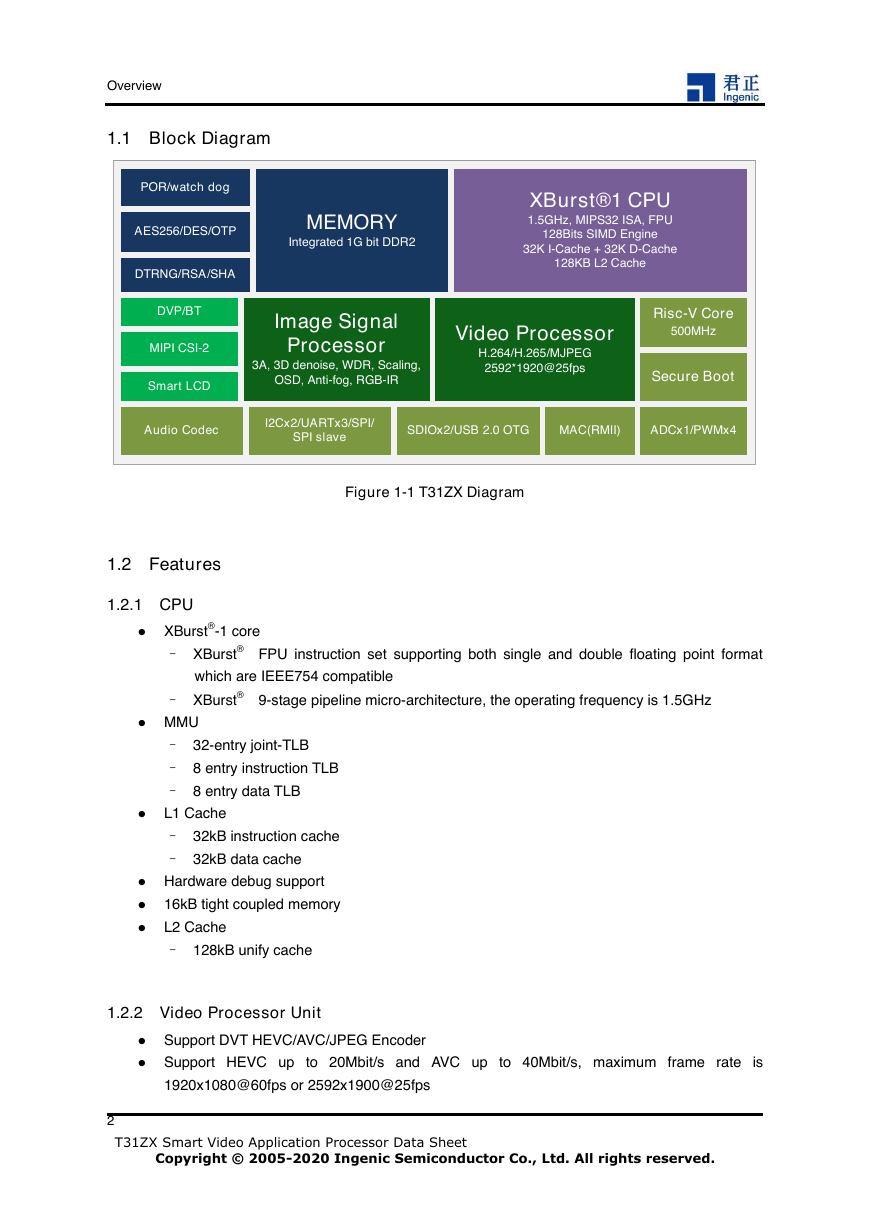

1.1 Block Diagram

POR/watch dog

AES256/DES/OTP

DTRNG/RSA/SHA

MEMORY

Integrated 1G bit DDR2

XBurst®1 CPU

1.5GHz, MIPS32 ISA, FPU

128Bits SIMD Engine

32K I-Cache + 32K D-Cache

128KB L2 Cache

DVP/BT

MIPI CSI-2

Smart LCD

Image Signal

Processor

3A, 3D denoise, WDR, Scaling,

OSD, Anti-fog, RGB-IR

Video Processor

H.264/H.265/MJPEG

2592*1920@25fps

Risc-V Core

500MHz

Secure Boot

Audio Codec

I2Cx2/UARTx3/SPI/

SPI slave

SDIOx2/USB 2.0 OTG

MAC(RMII)

ADCx1/PWMx4

Figure 1-1 T31ZX Diagram

1.2 Features

1.2.1 CPU

XBurst®-1 core

– XBurst® FPU instruction set supporting both single and double floating point format

which are IEEE754 compatible

– XBurst® 9-stage pipeline micro-architecture, the operating frequency is 1.5GHz

MMU

– 32-entry joint-TLB

– 8 entry instruction TLB

– 8 entry data TLB

L1 Cache

– 32kB instruction cache

– 32kB data cache

Hardware debug support

16kB tight coupled memory

L2 Cache

– 128kB unify cache

1.2.2 Video Processor Unit

Support DVT HEVC/AVC/JPEG Encoder

Support HEVC up to 20Mbit/s and AVC up to 40Mbit/s, maximum frame rate is

1920x1080@60fps or 2592x1900@25fps

2

T31ZX Smart Video Application Processor Data Sheet

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

�

Overview

maximum size up to 2592x4096 resolution

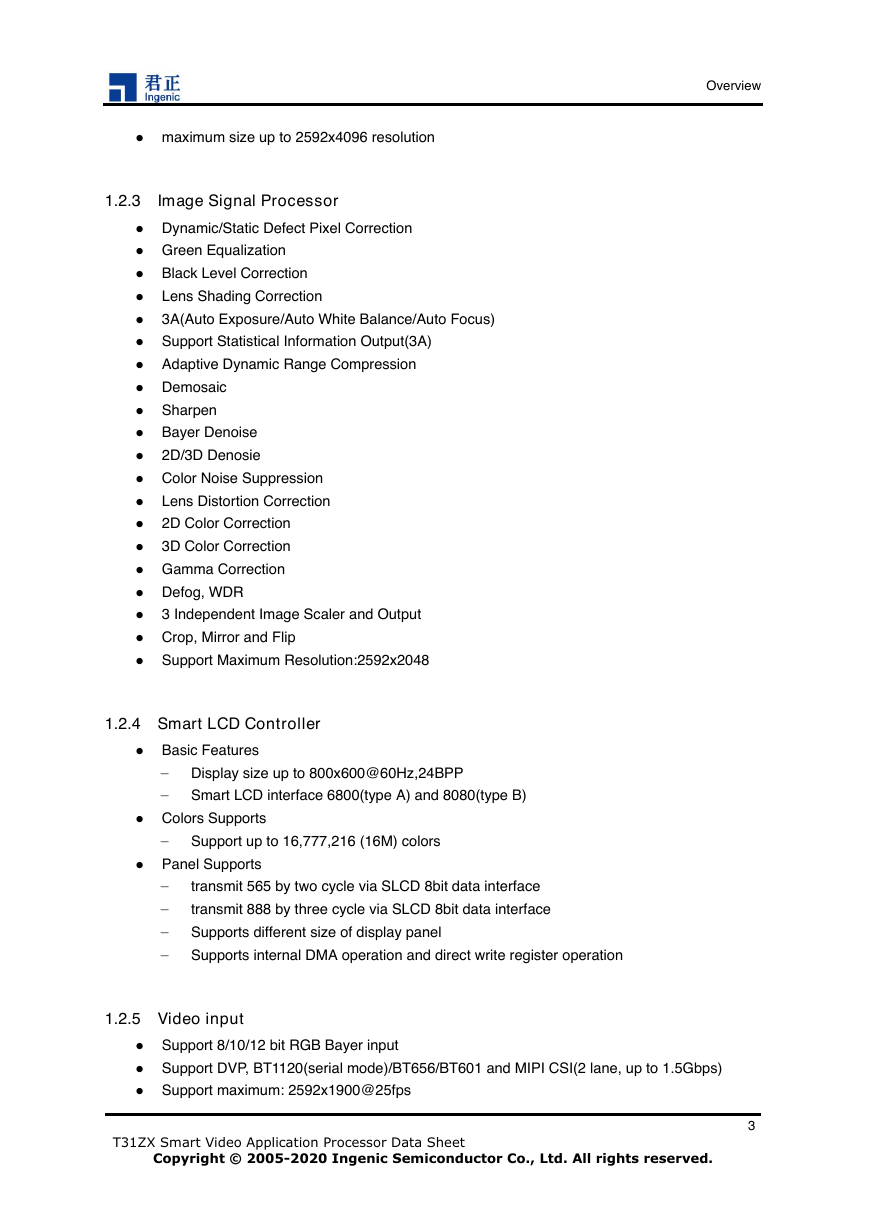

1.2.3

Image Signal Processor

Dynamic/Static Defect Pixel Correction

Green Equalization

Black Level Correction

Lens Shading Correction

3A(Auto Exposure/Auto White Balance/Auto Focus)

Support Statistical Information Output(3A)

Adaptive Dynamic Range Compression

Demosaic

Sharpen

Bayer Denoise

2D/3D Denosie

Color Noise Suppression

Lens Distortion Correction

2D Color Correction

3D Color Correction

Gamma Correction

Defog, WDR

3 Independent Image Scaler and Output

Crop, Mirror and Flip

Support Maximum Resolution:2592x2048

1.2.4 Smart LCD Controller

Basic Features

― Display size up to 800x600@60Hz,24BPP

― Smart LCD interface 6800(type A) and 8080(type B)

Colors Supports

― Support up to 16,777,216 (16M) colors

Panel Supports

―

―

transmit 565 by two cycle via SLCD 8bit data interface

transmit 888 by three cycle via SLCD 8bit data interface

― Supports different size of display panel

― Supports internal DMA operation and direct write register operation

1.2.5 Video input

Support 8/10/12 bit RGB Bayer input

Support DVP, BT1120(serial mode)/BT656/BT601 and MIPI CSI(2 lane, up to 1.5Gbps)

Support maximum: 2592x1900@25fps

3

T31ZX Smart Video Application Processor Data Sheet

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

�

Overview

Support single-sensor input

1.2.6 Audio System

Integrated Audio codec

– 24 bits DAC with 93dB SNR

– 24 bits ADC with 92dB SNR

– Support signal-ended and differential microphone input and line input

– Automatic Level Control (ALC) for smooth audio recording

– Pure logic process: no need for mixed signal layers and less mask cost

– Programmable input and output analog gains

– Digital interpolation and decimation filter integrated

– Sampling rate 8K/12K/16K/24K/32/44.1K/48K/96K

1.2.7 Memory Interface

Integrated 1G bit DDR2 on chip

Static memory interface

– Support 6 external chip selection CS6~1#. Each bank can be configured separately

– The size and base address of static memory banks are programmable

– Direct interface to 8-bit bus width external memory interface devices or external static

memory to each bank. Read/Write strobe setup time and hold time periods can be

programmed and inserted in an access cycle to enable connection to low-speed memory

– Wait insertion by WAIT pin

– Automatic wait cycle insertion to prevent data bus collisions in case of consecutive

memory accesses to different banks, or a read access followed by a write access to the

same bank

1.2.8 System Functions

Clock generation and power management

– On-chip 12/24/48MHZ oscillator circuit

– One three-chip phase-locked loops (PLL) with programmable multiplier

– CCLK, HHCLK, H2CLK, PCLK, H0CLK, DDR_CLK, VPU_CLK frequency can be

changed separately for software by setting registers

– SSI clock supports 50M clock

– MSC clock supports 100M clock

– Functional-unit clock gating

– Shut down power supply for P0, ISP, VPU, IPU

Timer and counter unit with PWM output and/or input edge counter

– Provide eight separate channels, six of them have input signal transition edge counter

– 16-bit A counter and 16-bit B counter with auto-reload function every channel

– Support interrupt generation when the A counter underflow

4

T31ZX Smart Video Application Processor Data Sheet

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc