嵌入式系统课程设计

查表式硬件运算器

�

1、任务与要求

基于嵌入式技术利用VHDL 等硬件语言描述4x4bit 查表式乘法

器的系统组成。

(1)基本要求:

a.设计一个4x4bit 查表式乘法器。

b.利用查表完成算法的原理,进行下式计算,并通过时序分析

得到其运算速度。

c.在DE2 开发板上用数码管显示。

(2)发挥部分:

a.在Signal Tap 中显示查表式乘法器的输出结果仿真波形图。

b. 计算精度和数据区域根据设定的ROM 的大小自行设定。

2、系统原理

对于高速嵌入式测控系统,影响测控速度最大的因素是在测得必

要的数据并

经过复杂的运算后,才能发出控制指令。数据的运算速度决定了

该嵌入式系统的

工作速度。具体实施方案是预先将可能出现的,且需要计算的数

据都计算好,装

入ROM 中,然后将ROM 的地址线作为测得的数据的输入口。测控

系统一旦得到

所测得的数据,并将数据作为地址信号输入ROM 后,即可得到结

�

果。

3.设计步骤

(一)各个单元模块的定制

数码管译码显示模块

7 段数码显示译码器程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DecL7s IS

PORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );

END ENTITY DecL7s;

ARCHITECTURE one OF DecL7S IS

BEGIN

PROCESS(A)

BEGIN

CASE A(3 DOWNTO 0) IS

WHEN "0000" => LED7S <= "1000000";

WHEN "0001" => LED7S <= "1111001";

WHEN "0010" => LED7S <= "0100100";

WHEN "0011" => LED7S <= "0110000";

WHEN "0100" => LED7S <= "0011001";

WHEN "0101" => LED7S <= "0010010";

WHEN "0110" => LED7S <= "0000010";

WHEN "0111" => LED7S <= "1111000";

WHEN "1000" => LED7S <= "0000000";

WHEN "1001" => LED7S <= "0010000";

WHEN "1010" => LED7S <= "0001000";

WHEN "1011" => LED7S <= "0000011";

WHEN "1100" => LED7S <= "1000110";

WHEN "1101" => LED7S <= "0100001";

WHEN "1110" => LED7S <= "0000110";

WHEN "1111" => LED7S <= "0001110";

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

END ARCHITECTURE one;

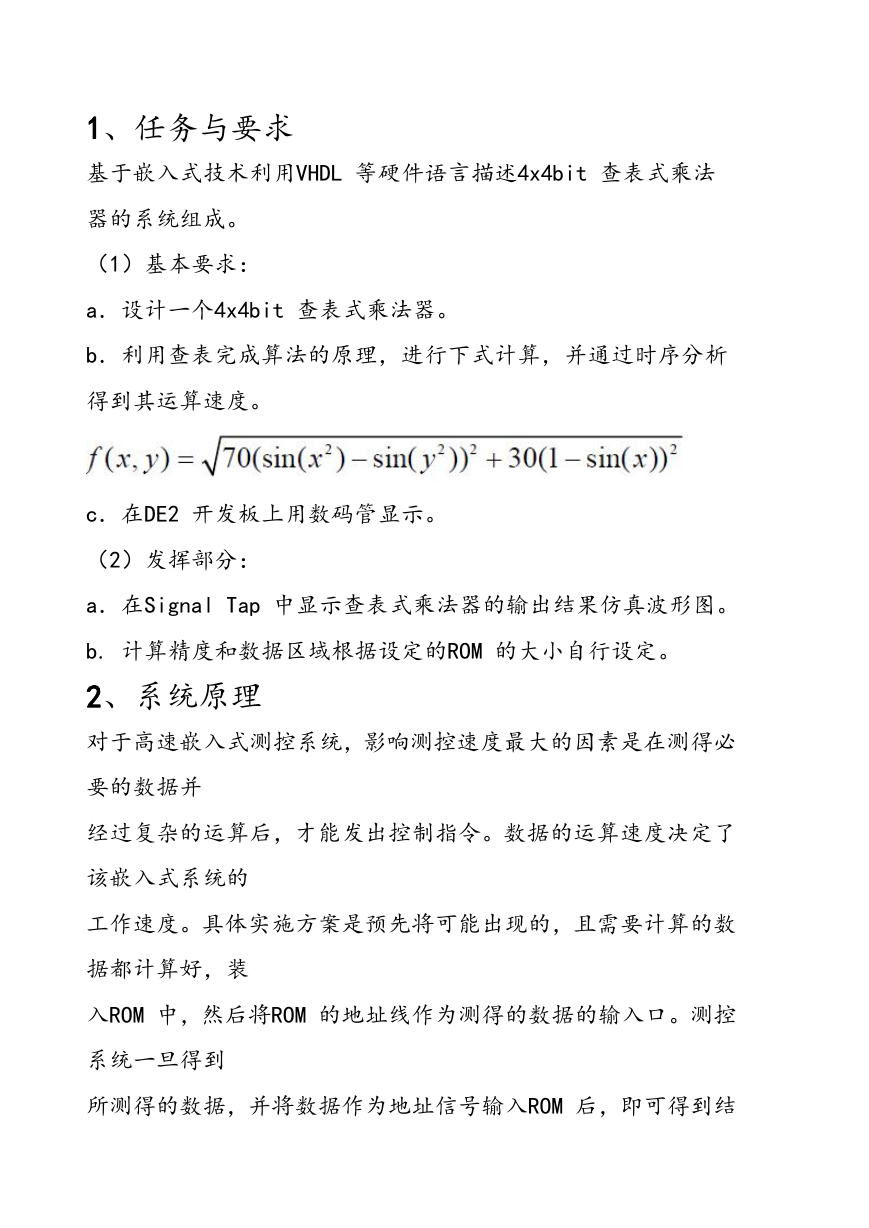

生成的器件为:

�

DecL7s

A[3..0]

LED7S[6..0]

inst2

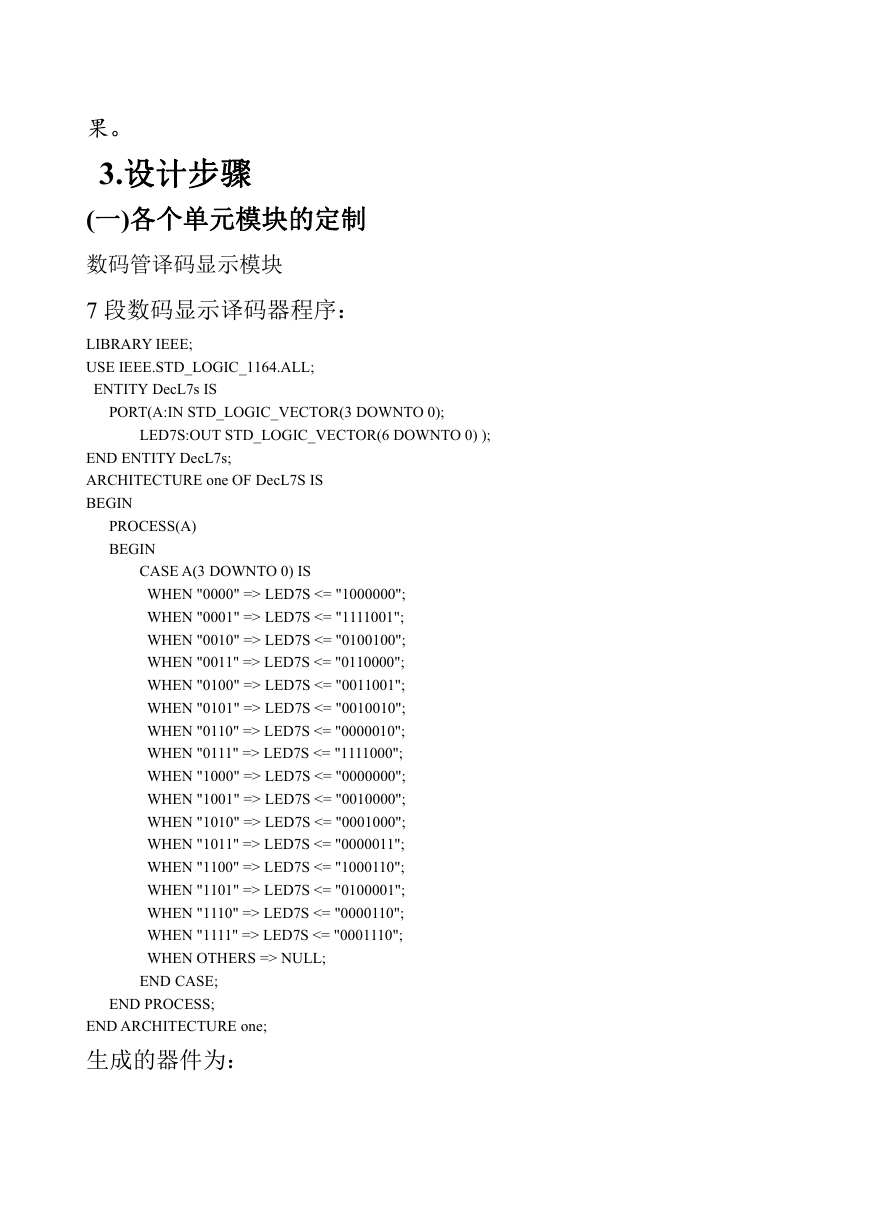

数码管译码显示仿真波形:

由波形图知,数码管可以正确的显示数字。

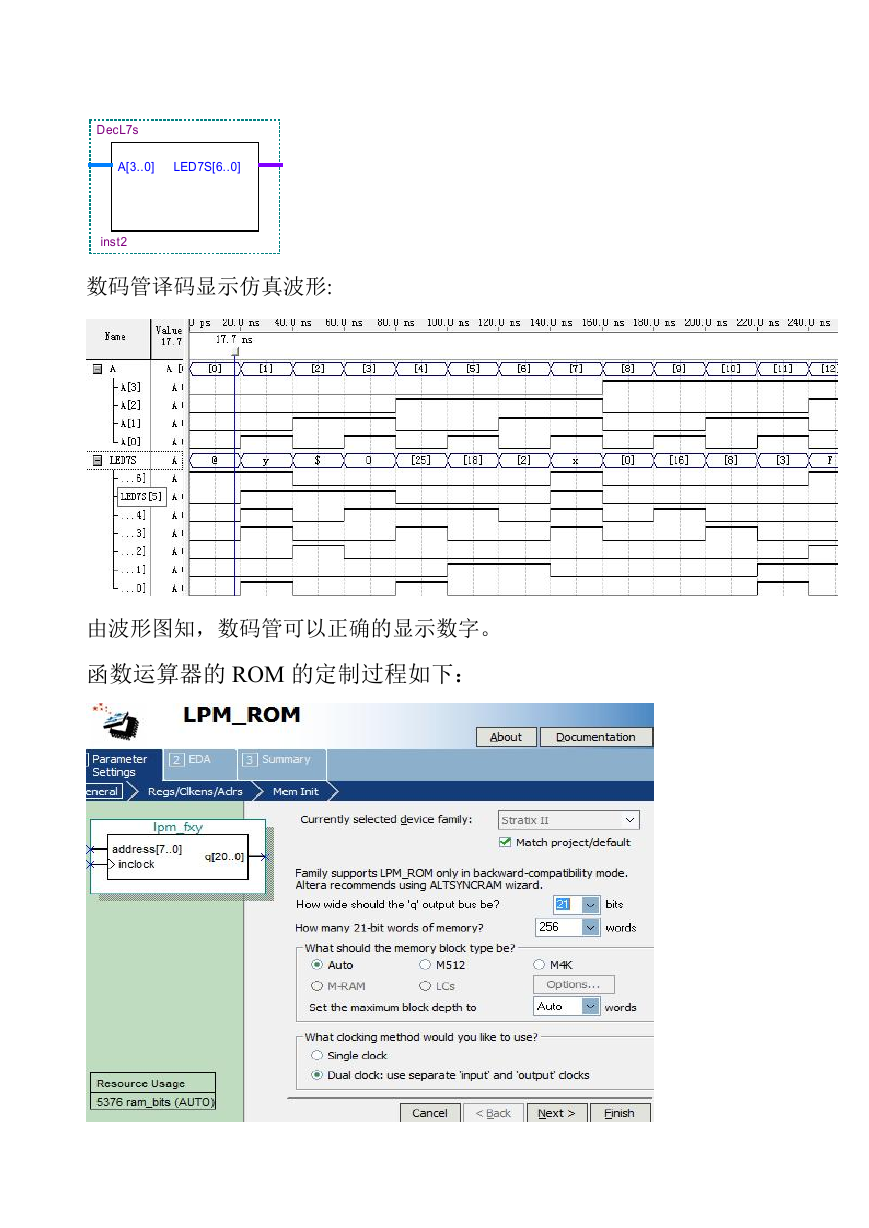

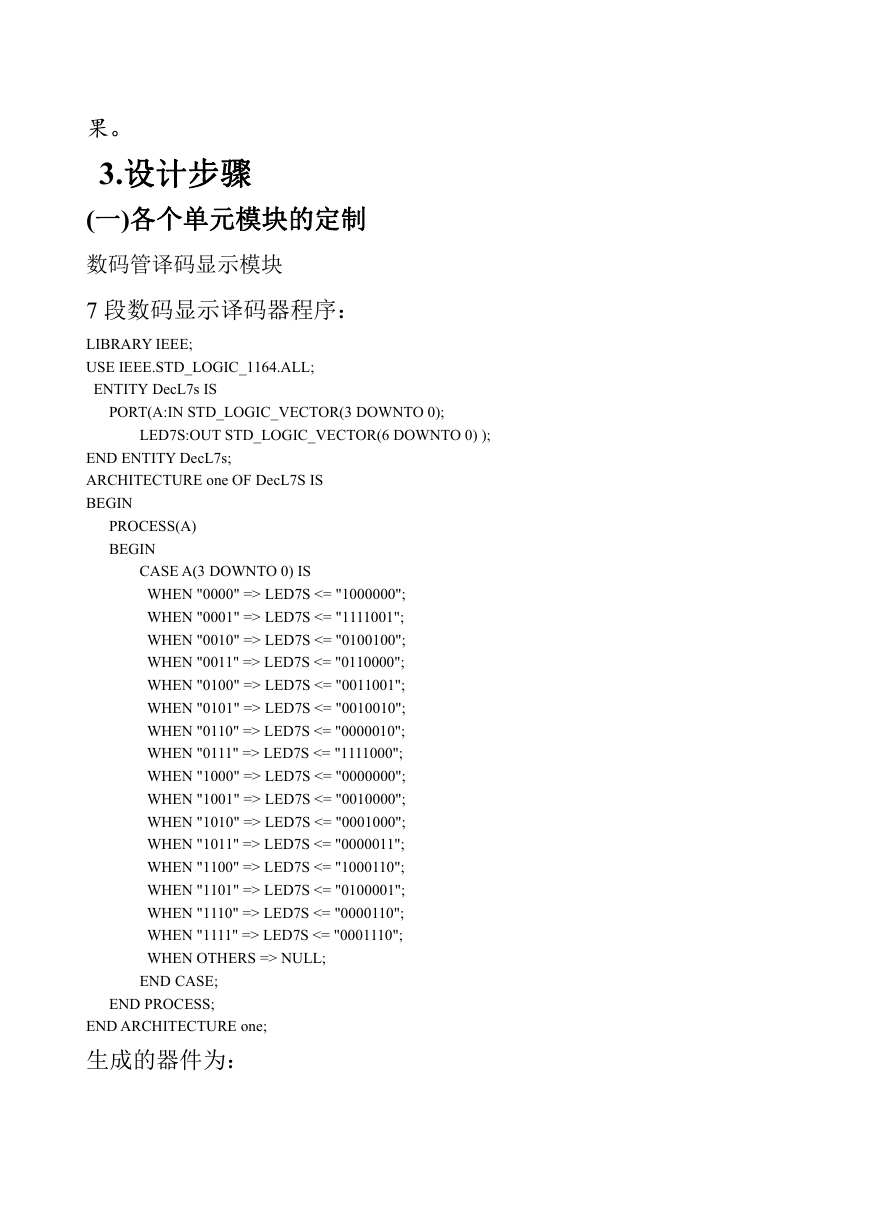

函数运算器的 ROM 的定制过程如下:

�

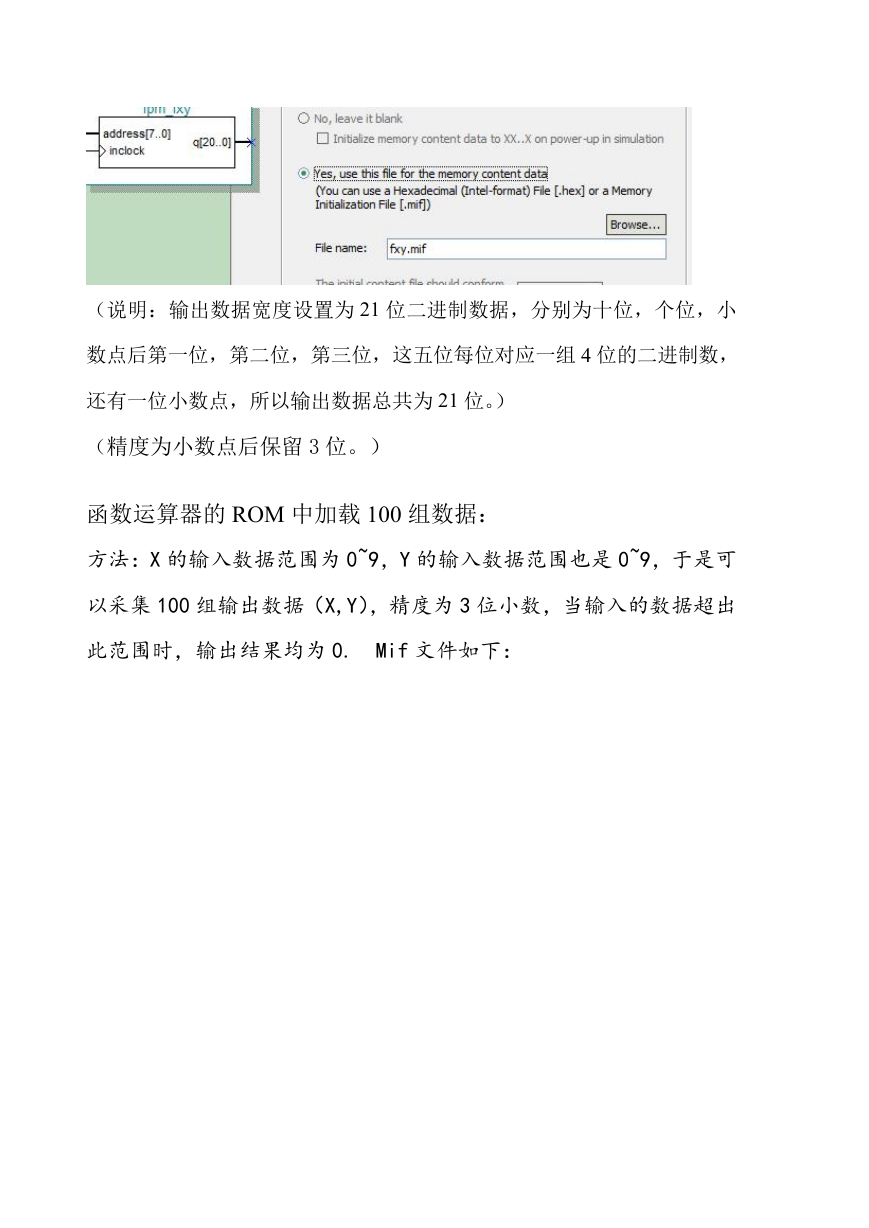

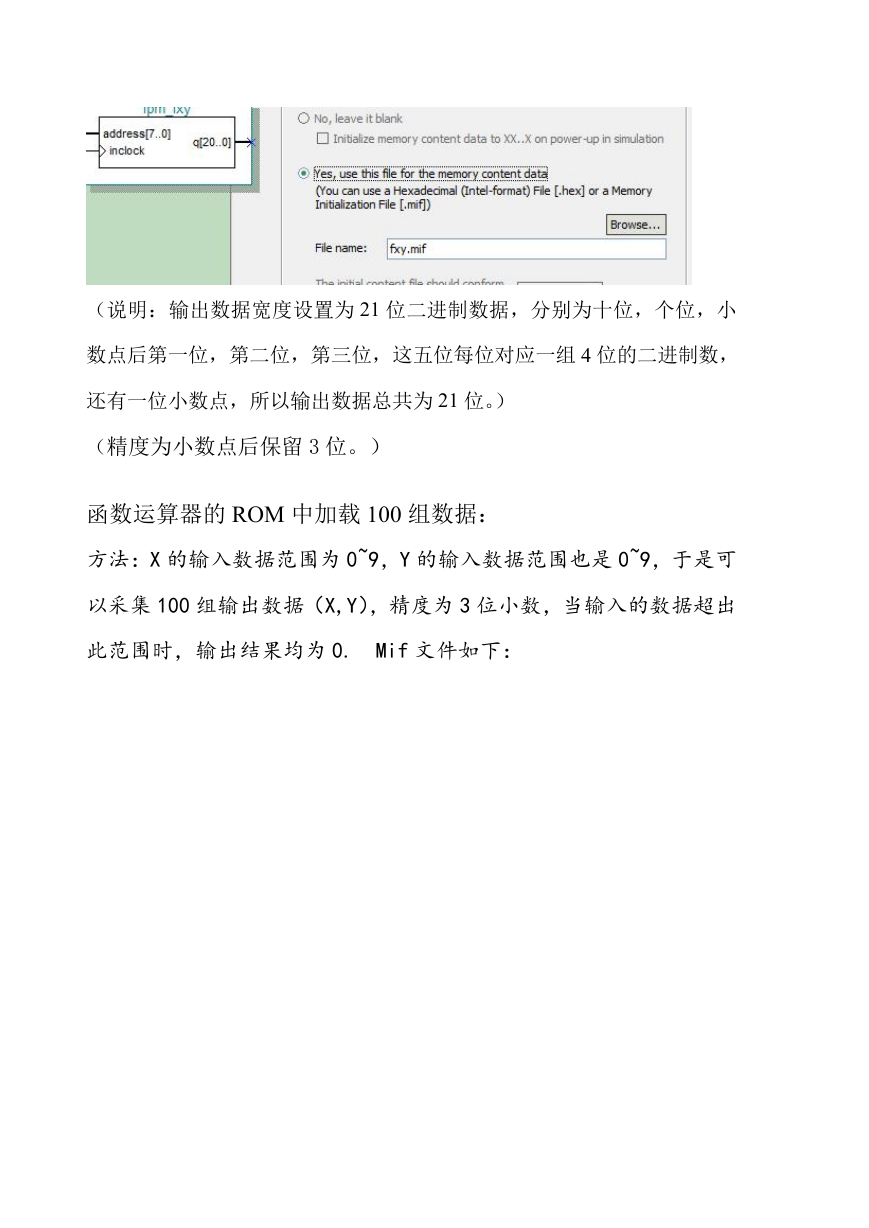

(说明:输出数据宽度设置为 21 位二进制数据,分别为十位,个位,小

数点后第一位,第二位,第三位,这五位每位对应一组 4 位的二进制数,

还有一位小数点,所以输出数据总共为 21 位。)

(精度为小数点后保留 3 位。)

函数运算器的 ROM 中加载 100 组数据:

方法:X 的输入数据范围为 0~9,Y 的输入数据范围也是 0~9,于是可

以采集 100 组输出数据(X,Y),精度为 3 位小数,当输入的数据超出

此范围时,输出结果均为 0. Mif 文件如下:

�

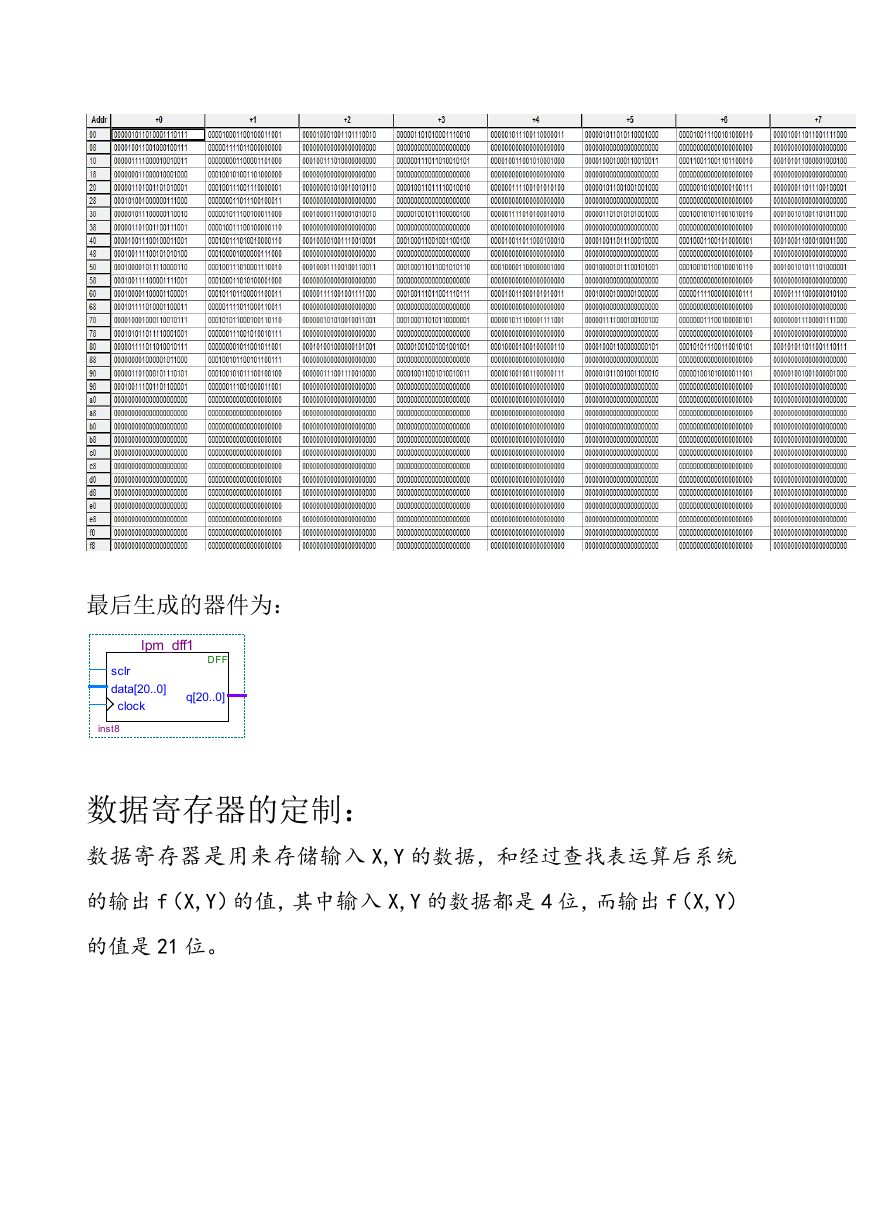

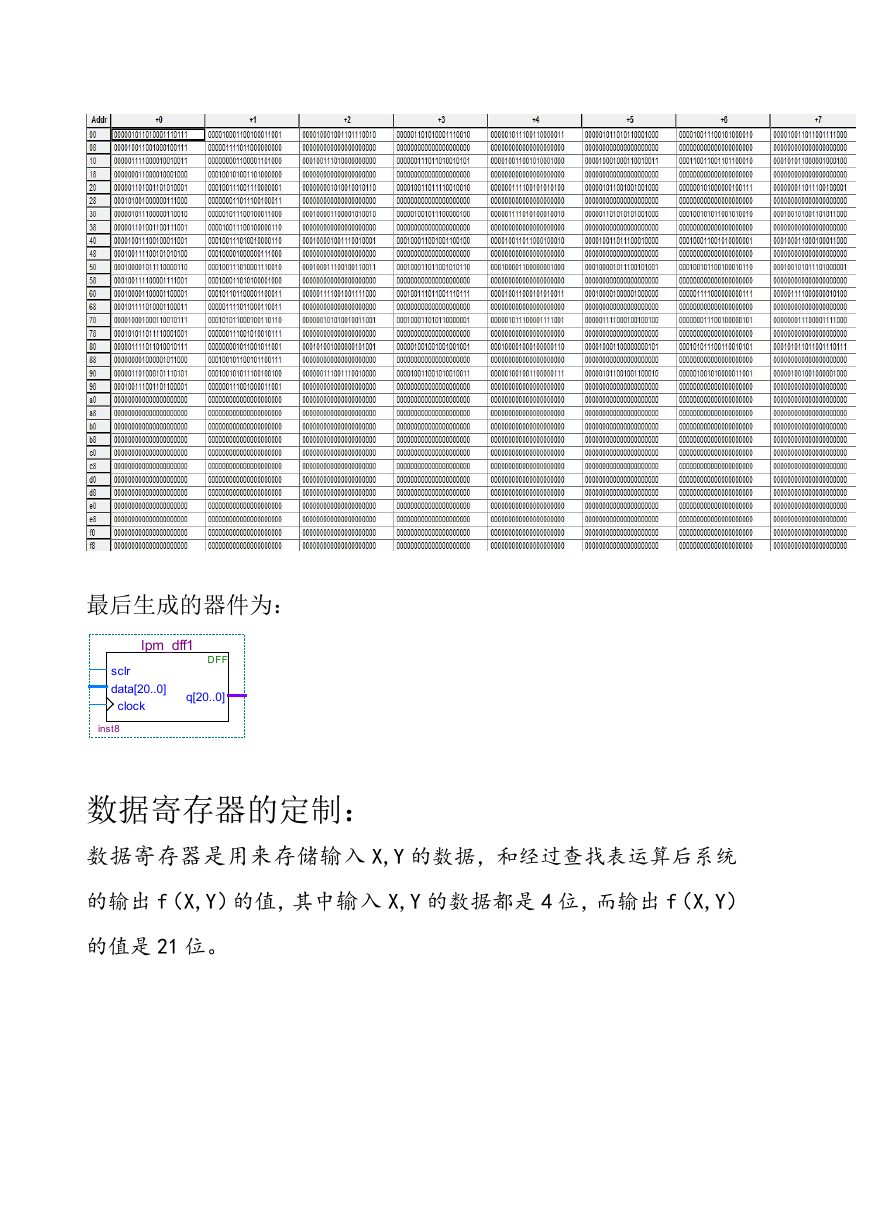

最后生成的器件为:

lpm_dff1

sclr

data[20..0]

clock

inst8

DFF

q[20..0]

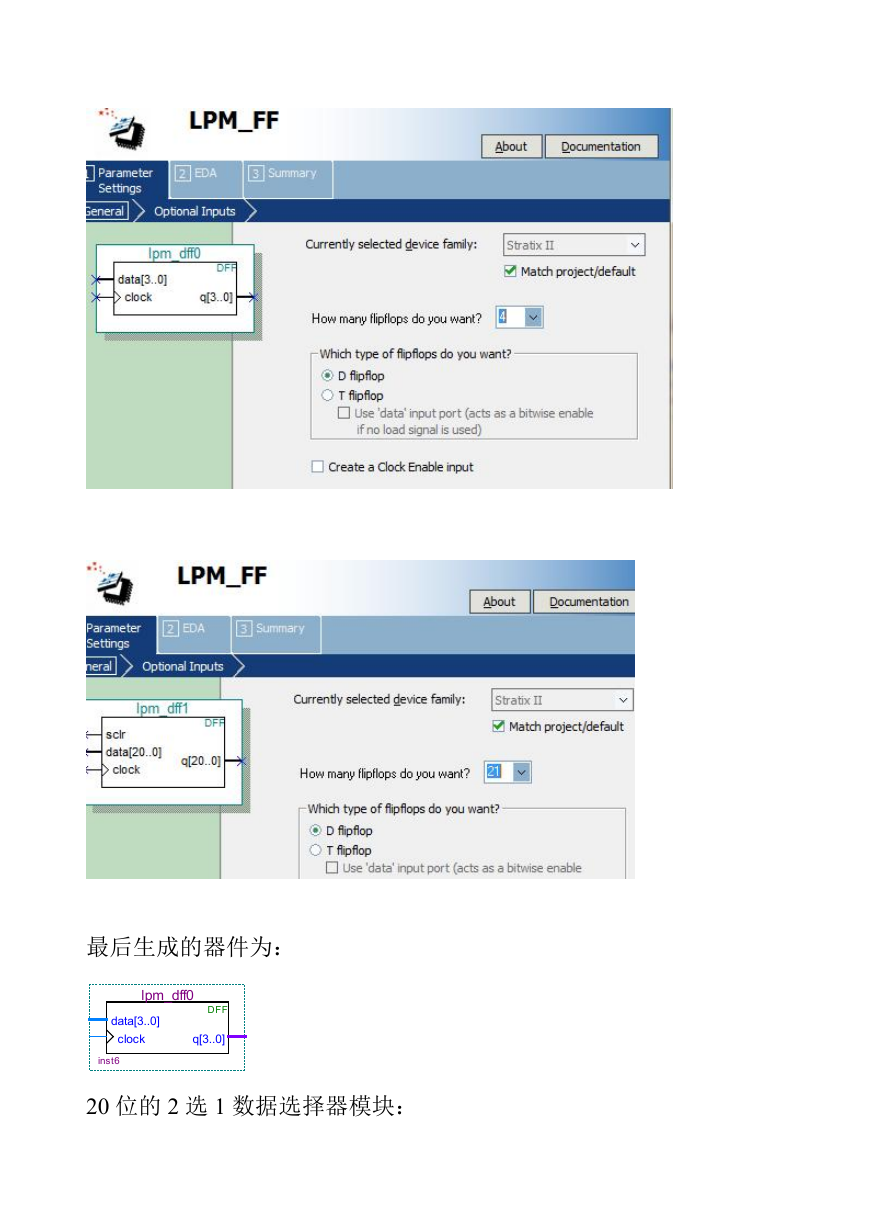

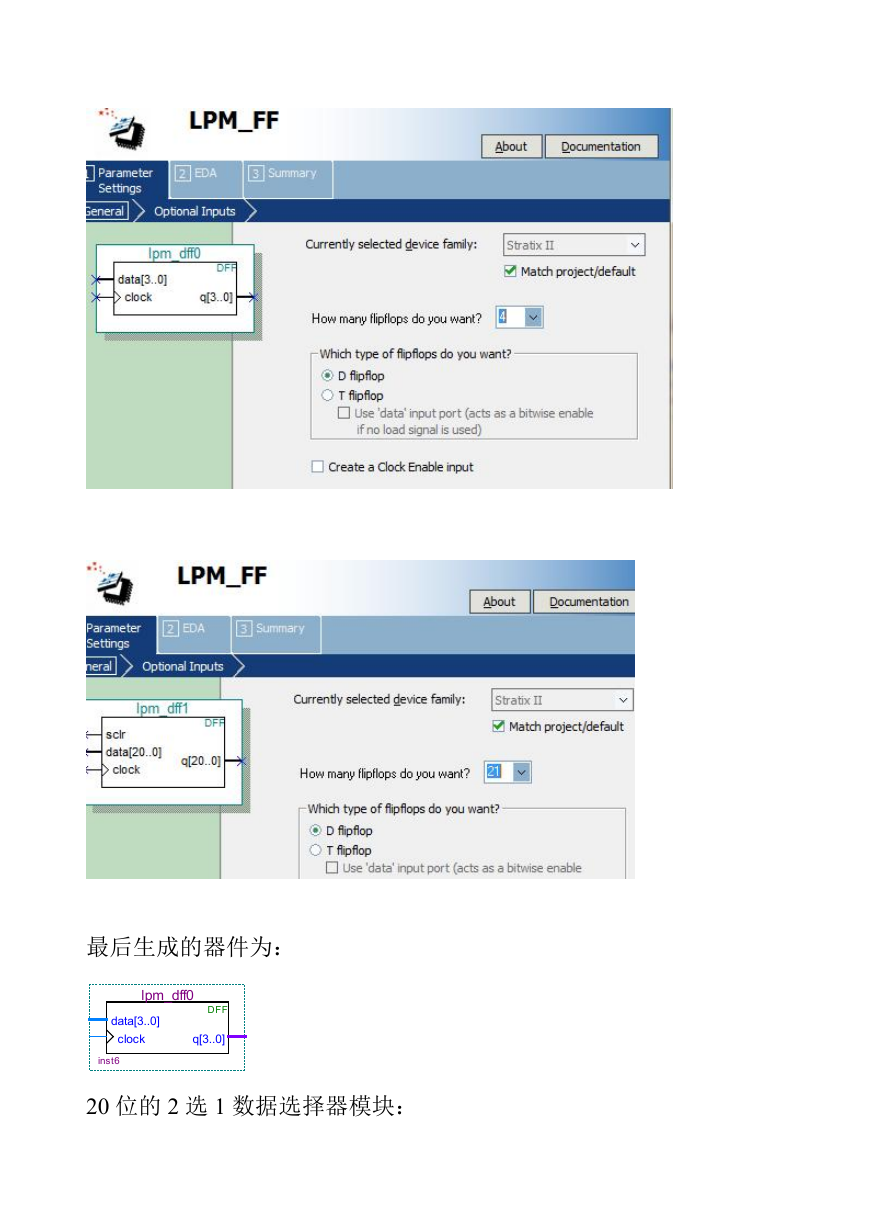

数据寄存器的定制:

数据寄存器是用来存储输入 X,Y 的数据,和经过查找表运算后系统

的输出 f(X,Y)的值,其中输入 X,Y 的数据都是 4 位,而输出 f(X,Y)

的值是 21 位。

�

最后生成的器件为:

lpm_dff0

data[3..0]

clock

inst6

DFF

q[3..0]

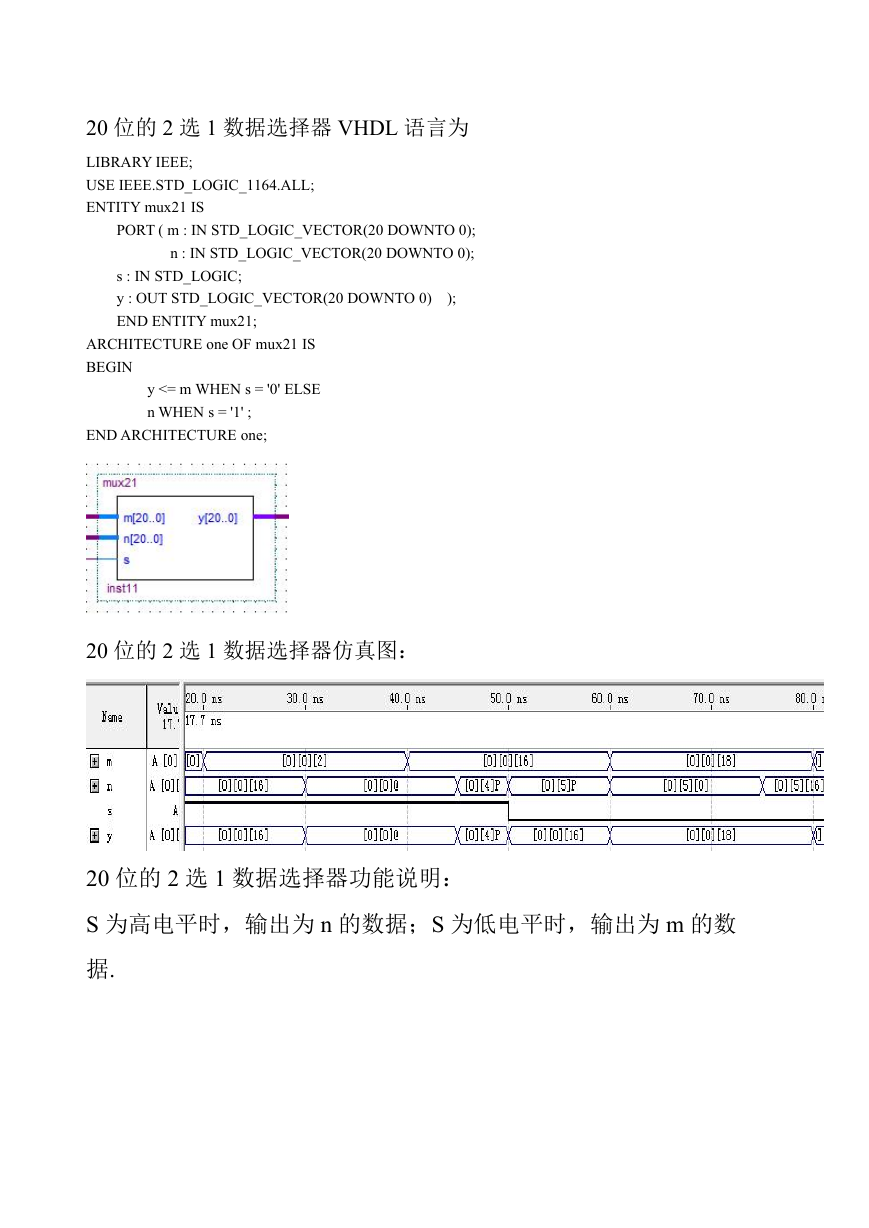

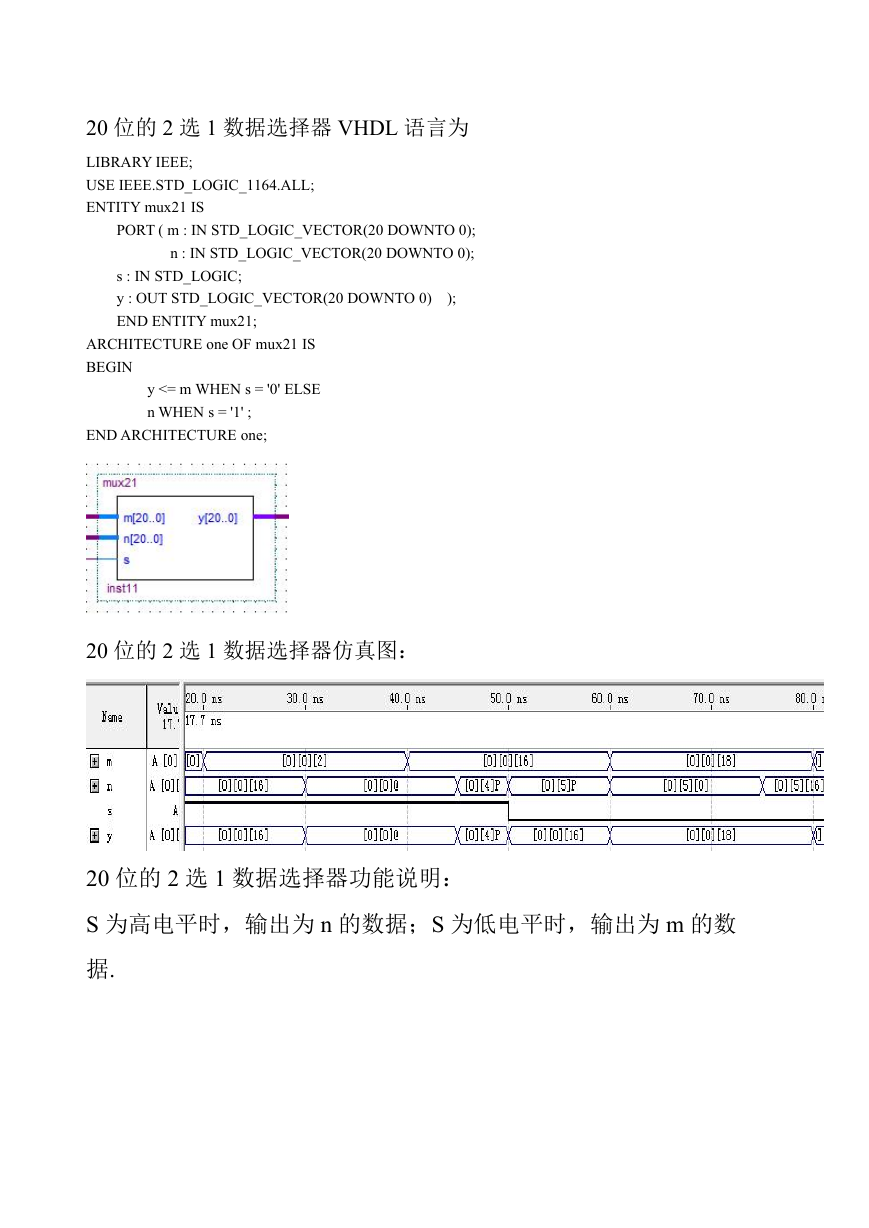

20 位的 2 选 1 数据选择器模块:

�

20 位的 2 选 1 数据选择器 VHDL 语言为

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux21 IS

PORT ( m : IN STD_LOGIC_VECTOR(20 DOWNTO 0);

n : IN STD_LOGIC_VECTOR(20 DOWNTO 0);

s : IN STD_LOGIC;

y : OUT STD_LOGIC_VECTOR(20 DOWNTO 0)

END ENTITY mux21;

);

ARCHITECTURE one OF mux21 IS

BEGIN

y <= m WHEN s = '0' ELSE

n WHEN s = '1' ;

END ARCHITECTURE one;

20 位的 2 选 1 数据选择器仿真图:

20 位的 2 选 1 数据选择器功能说明:

S 为高电平时,输出为 n 的数据;S 为低电平时,输出为 m 的数

据.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc