JEDEC

STANDARD

Cycled Temperature-Humidity-Bias

Life Test

JESD22-A100C

(Revision of JESD22-A100-B, April 2000)

OCTOBER 2007

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

�

NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and

approved through the JEDEC Board of Directors level and subsequently reviewed and approved

by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating

misunderstandings between manufacturers and purchasers, facilitating interchangeability and

improvement of products, and assisting the purchaser in selecting and obtaining with minimum

delay the proper product for use by those other than JEDEC members, whether the standard is to

be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption

may involve patents or articles, materials, or processes. By such action JEDEC does not assume

any liability to any patent owner, nor does it assume any obligation whatever to parties adopting

the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to

product specification and application, principally from the solid state device manufacturer

viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or

publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in

the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or

publication should be addressed to JEDEC at the address below, or call (703) 907-7559 or

www.jedec.org

Published by

©JEDEC Solid State Technology Association 2007

2500 Wilson Boulevard

Arlington, VA 22201-3834

This document may be downloaded free of charge; however JEDEC retains the

copyright on this material. By downloading this file the individual agrees not to

charge for or resell the resulting material.

PRICE: Please refer to the current

Catalog of JEDEC Engineering Standards and Publications online at

http://www.jedec.org/Catalog/catalog.cfm

Printed in the U.S.A.

All rights reserved

�

PLEASE!

DON’T VIOLATE

THE

LAW!

This document is copyrighted by JEDEC and may not be

reproduced without permission.

Organizations may obtain permission to reproduce a limited number of copies

through entering into a license agreement. For information, contact:

JEDEC Solid State Technology Association

2500 Wilson Boulevard

Arlington, Virginia 22201-3834

or call (703) 907-7559

�

�

Scope

Apparatus

TEST METHOD A100-B

CYCLED TEMPERATURE-HUMIDITY-BIAS LIFE TEST

(From JEDEC Board Ballot JCB-99-80 and JCB-07-77, formulated under the cognizance of JC-14.1

Committee on Reliability Test Methods for Packaged Devices.)

1

The Cycled Temperature-Humidity-Bias Life Test is typically performed on cavity packages (e.g.

MQUADs, lidded ceramic pin grid arrays, etc.) as an alternative to JESD22-A101 or JESD22-A110.

The Cycled Temperature-humidity –Biased Life Test is performed for the purpose of evaluating the

reliability of non-hermetic, packaged solid state devices in humidity environments when surface

condensation is likely. It employs conditions of bias, temperature cycling and high humidity that will

cause condensation to occur on the device surface. It is useful to determine device surface susceptibility

to corrosion and/or dendritic growth.

For most applications test method JESD22-A110 “Highly Accelerated Temperature and Humidity Stress

Test (HAST)” or JESD22-A101 “Steady State Temperature, Humidity, Biased Life Test” is preferred.

2

The test requires a temperature-humidity test chamber capable of maintaining a specified temperature and

relative humidity profile continuously, while providing electrical connections to the devices under test in

a specified biasing configuration.

2.1

The chamber must be capable of providing controlled conditions of temperature and relative humidity as

described in clause 3, Test Conditions.

2.2

A recording device (e.g. a chart recorder or a computer) with an interface to suitable chamber monitoring

instrumentation shall be provided for continuous recording of chamber temperature and relative humidity.

2.3

Devices under stress must be physically located to minimize temperature gradients.

2.4 Minimize release of contamination

Care must be exercised in the choice of board and socket materials, to minimize release of contamination,

and to minimize degradation due to corrosion and other mechanisms.

Temperature and relative humidity

Devices under stress

Recording device

JEDEC Standard No. 22-A100C

Page 1

Test Method A100C

(Revision of A100-B)

�

Apparatus (cont’d)

Ionic contamination

JEDEC Standard No. 22-A100C

Page 2

2

2.5

Ionic contamination of the test apparatus (card cage, test boards, sockets, wiring, storage containers, etc.)

shall be controlled to avoid test artifacts.

2.6

Deionized water with a minimum resistivity of 1 megohm-cm at room temperature shall be used.

3

The test condition consists of a temperature, relative humidity, and duration used in conjunction with an

electrical bias configuration specific to the device.

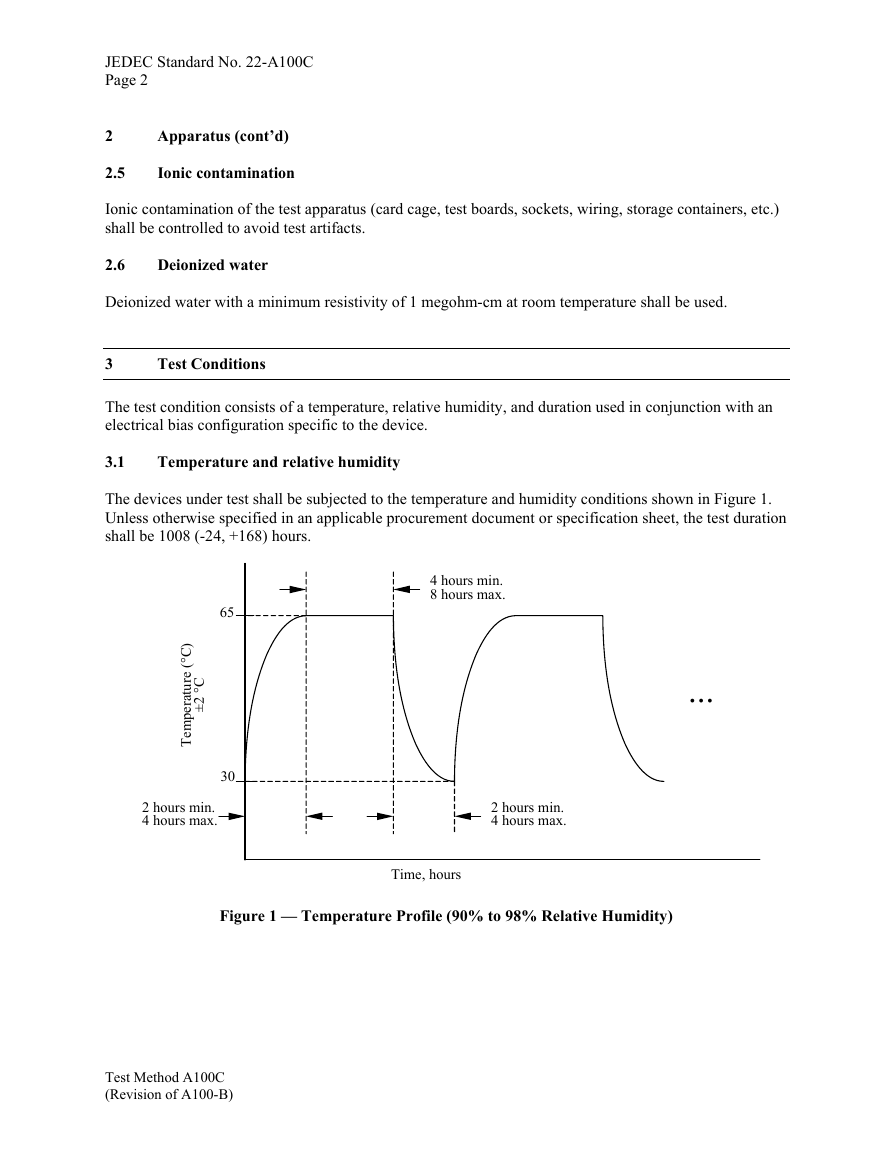

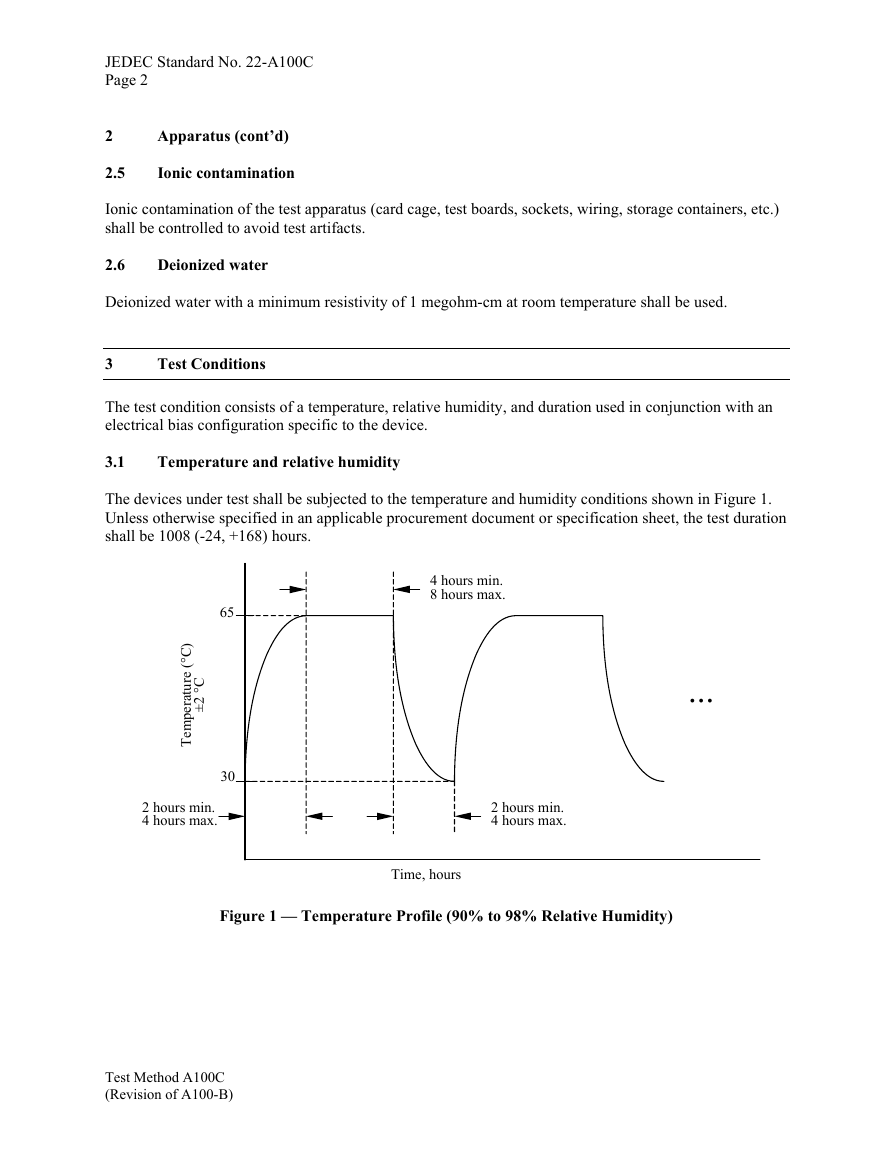

3.1

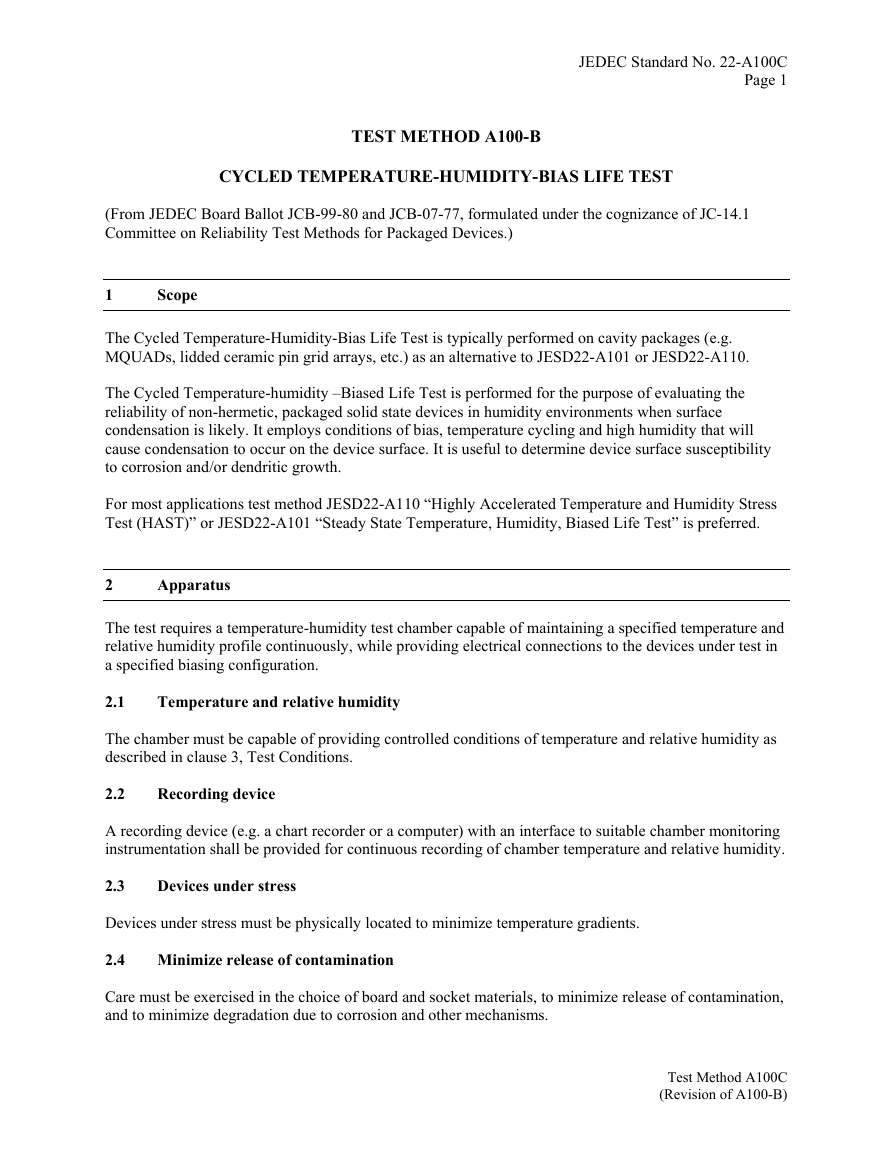

The devices under test shall be subjected to the temperature and humidity conditions shown in Figure 1.

Unless otherwise specified in an applicable procurement document or specification sheet, the test duration

shall be 1008 (-24, +168) hours.

Temperature and relative humidity

Deionized water

Test Conditions

4 hours min.

8 hours max.

...

65

30

)

C

°

(

e

r

u

t

a

r

e

p

m

e

T

C

°

2

±

2 hours min.

4 hours max.

2 hours min.

4 hours max.

Time, hours

Figure 1 — Temperature Profile (90% to 98% Relative Humidity)

Test Method A100C

(Revision of A100-B)

�

JEDEC Standard No. 22-A100C

Page 3

Biasing guidelines

Test Conditions (cont’d)

3

3.2

3.2.1 Apply bias according to the following guidelines:

a) Minimize power dissipation.

b) Alternate pin bias as much as possible.

c) Distribute potential differences across chip metallization as much as possible.

d) Maximize voltage within operating range.

NOTE The priority of the above guidelines depends on the mechanism and specific device characteristics.

3.2.2 Either of two kinds of bias may be used to satisfy these guidelines, whichever is more

severe:

a) Continuous bias – the dc bias shall be applied continuously. Continuous bias is more severe than

cycled bias when the die temperature is less than or equal to 10 °C higher than the chamber ambient

temperature, or if the die temperature is not known when the heat dissipation of the device under test

(DUT) is less than 200 mW. If the heat dissipation of the DUT exceeds 200 mW, then the die

temperature should be calculated. If the die temperature exceeds the chamber ambient temperature by

more than 5 °C, then the die temperature rise above the chamber ambient should be included in

reports of test results since the acceleration of failure mechanisms will be affected.

b) Cycled bias – the dc voltage applied to the devices under test shall be periodically interrupted with an

appropriate frequency and duty cycle. If the biasing configuration results in a temperature rise above

the chamber ambient , ΔTja, exceeding 10 °C, then cycled bias, when optimized for a specific device

type, will be more severe than continuous bias. Heating as a result of power dissipation tends to drive

moisture away from the die and thereby hinders moisture-related failure mechanisms. Cycled bias

permits moisture collection on the die during the off periods when the device power dissipation does

not occur. Cycling the DUT bias with one hour on and one hour off is optimal for most plastic

encapsulated microcircuits. The die temperature, as calculated on the basis of the known thermal

impedance and dissipation, should be quoted with the results whenever it exceeds the chamber

ambient by 5 °C or more.

Test Method A100C

(Revision of A100-B)

�

Test Conditions (cont’d)

Biasing guidelines (cont’d)

JEDEC Standard No. 22-A100C

Page 4

3

3.2

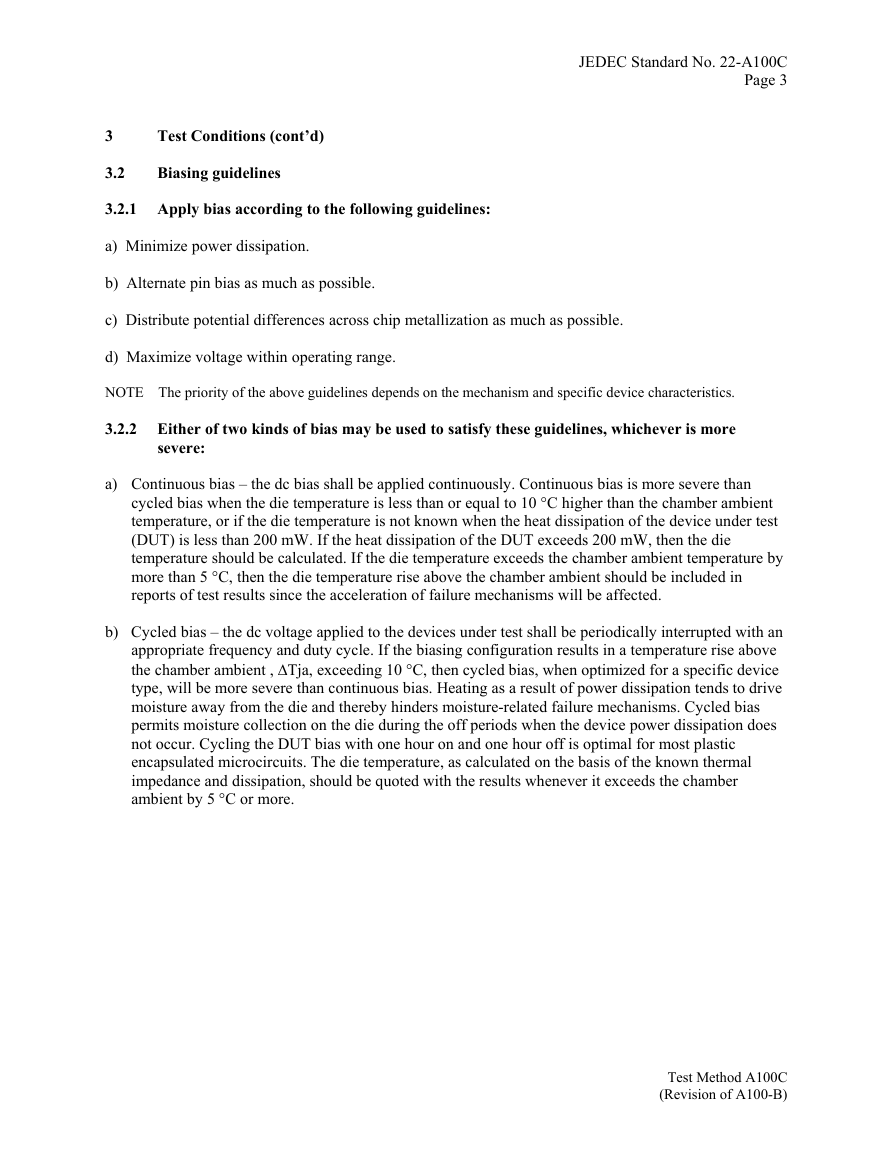

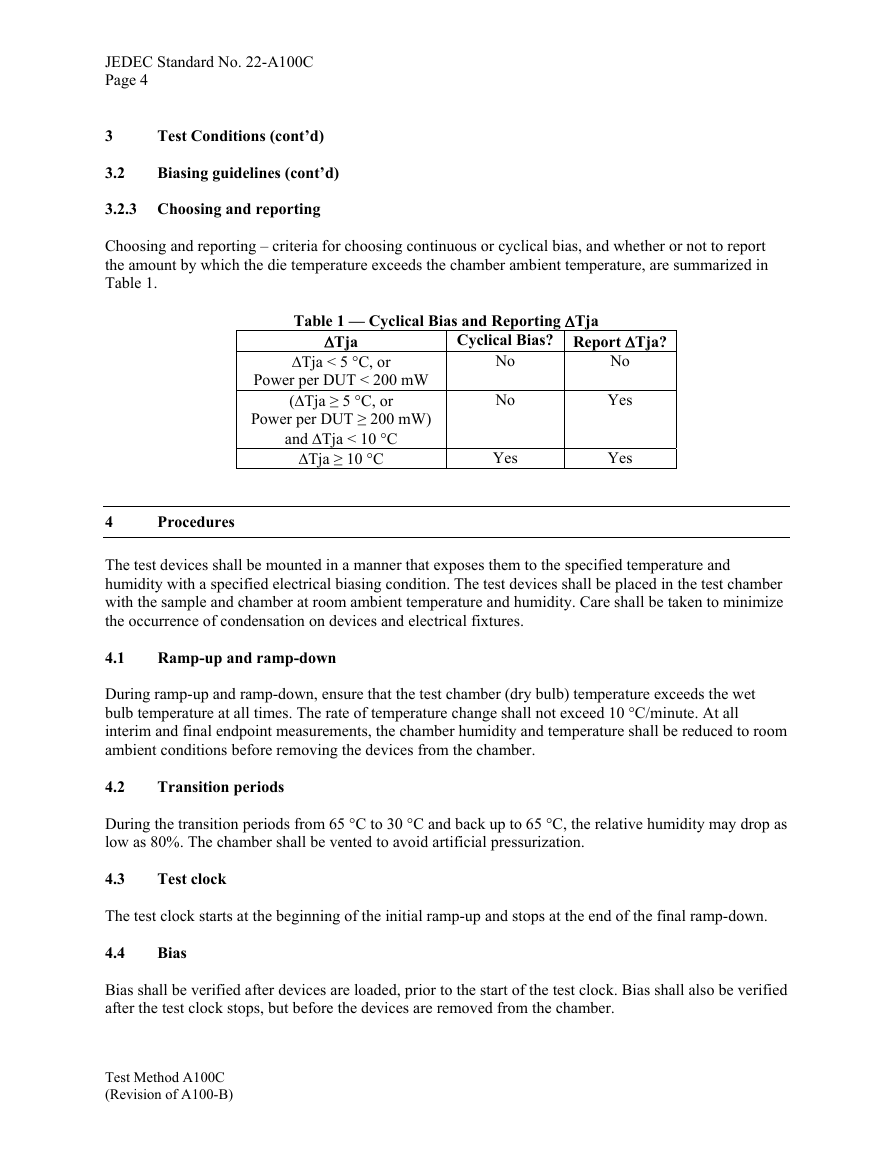

3.2.3 Choosing and reporting

Choosing and reporting – criteria for choosing continuous or cyclical bias, and whether or not to report

the amount by which the die temperature exceeds the chamber ambient temperature, are summarized in

Table 1.

Table 1 — Cyclical Bias and Reporting ΔTja

ΔTja

Cyclical Bias? Report ΔTja?

ΔTja < 5 °C, or

Power per DUT < 200 mW

(ΔTja ≥ 5 °C, or

Power per DUT ≥ 200 mW)

and ΔTja < 10 °C

ΔTja ≥ 10 °C

No

No

No

Yes

Yes

Yes

Procedures

Ramp-up and ramp-down

4

The test devices shall be mounted in a manner that exposes them to the specified temperature and

humidity with a specified electrical biasing condition. The test devices shall be placed in the test chamber

with the sample and chamber at room ambient temperature and humidity. Care shall be taken to minimize

the occurrence of condensation on devices and electrical fixtures.

4.1

During ramp-up and ramp-down, ensure that the test chamber (dry bulb) temperature exceeds the wet

bulb temperature at all times. The rate of temperature change shall not exceed 10 °C/minute. At all

interim and final endpoint measurements, the chamber humidity and temperature shall be reduced to room

ambient conditions before removing the devices from the chamber.

4.2

During the transition periods from 65 °C to 30 °C and back up to 65 °C, the relative humidity may drop as

low as 80%. The chamber shall be vented to avoid artificial pressurization.

4.3

The test clock starts at the beginning of the initial ramp-up and stops at the end of the final ramp-down.

4.4

Bias shall be verified after devices are loaded, prior to the start of the test clock. Bias shall also be verified

after the test clock stops, but before the devices are removed from the chamber.

Transition periods

Test clock

Bias

Test Method A100C

(Revision of A100-B)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc