芯驿电子科技(上海)有限公司

021-67676997

www.alinx.cn

www.heijin.org

PCIE 速度测试

黑金动力社区 2018-10-30

1 实验简介

PCIE(PCI Express)采用了目前业内流行的点对点串行连接,比起 PCI 以及更早期的计算机总

线的共享并行架构,每个设备都有自己的专用连接,不需要向整个总线请求带宽,而且可以把数

据传输率提高到一个很高的频率,达到 PCI 所不能提供的高带宽。AX7325 开发板中的 FPGA

XC7K325TFFG900 单通道通信速率可高达 5G bit 带宽,可配置成 X1、X2、X4、X8 模式。该例程中

通过利用 XILINX 的 XDMA IP 来实现 PCIE 的发送和接收速度测试。

2 实验原理

2.1 例程简介

Xilinx 的 XC7K325TFFG900 FPGA 集成了 1 个 PCIe 硬核,可配置成 X1、X2、x4、x8 来实现不同

速率的高速串行数据通信。在 AX7325 开发板上 PCIe 例程中,FPGA 端程序采用 XILINX 的 PCIe

Core 进行设计,例中配置成 x8 进行 PCIe 通信,具体见 XILINX 官方 Vivado 文档的 PG195。PCIe 的

相关基础知识可参考提供的《PCIe 概述》或查阅其它进行整体了解,对于已有基础的大虾来说,

可忽略。

PCIe 通信例程由三部分组成:FPGA 端程序、PCIe 卡驱动、PCIe 上位机测试程序。

FPGA 端程序:负责建立与 PCIe 通信需具备的 FPGA 框架,PCIe 通信协议的构建;

PCIe 卡驱动:负责上位机测试程序与 PCIe 卡的数据交换;

PCIe 上位机测试程序:PCIe 测速(如 linux 下开发,请参考实验教程《ALINX 黑金 PCIe 板卡

Linux 使用教程》)。

在进行 PCIe 测速例程之前,确保计算机为 WIN7(64 位)或 WIN10(64 位)系统。

黑金 FPGA

版权所有

1 / 29

�

www.heijin.org

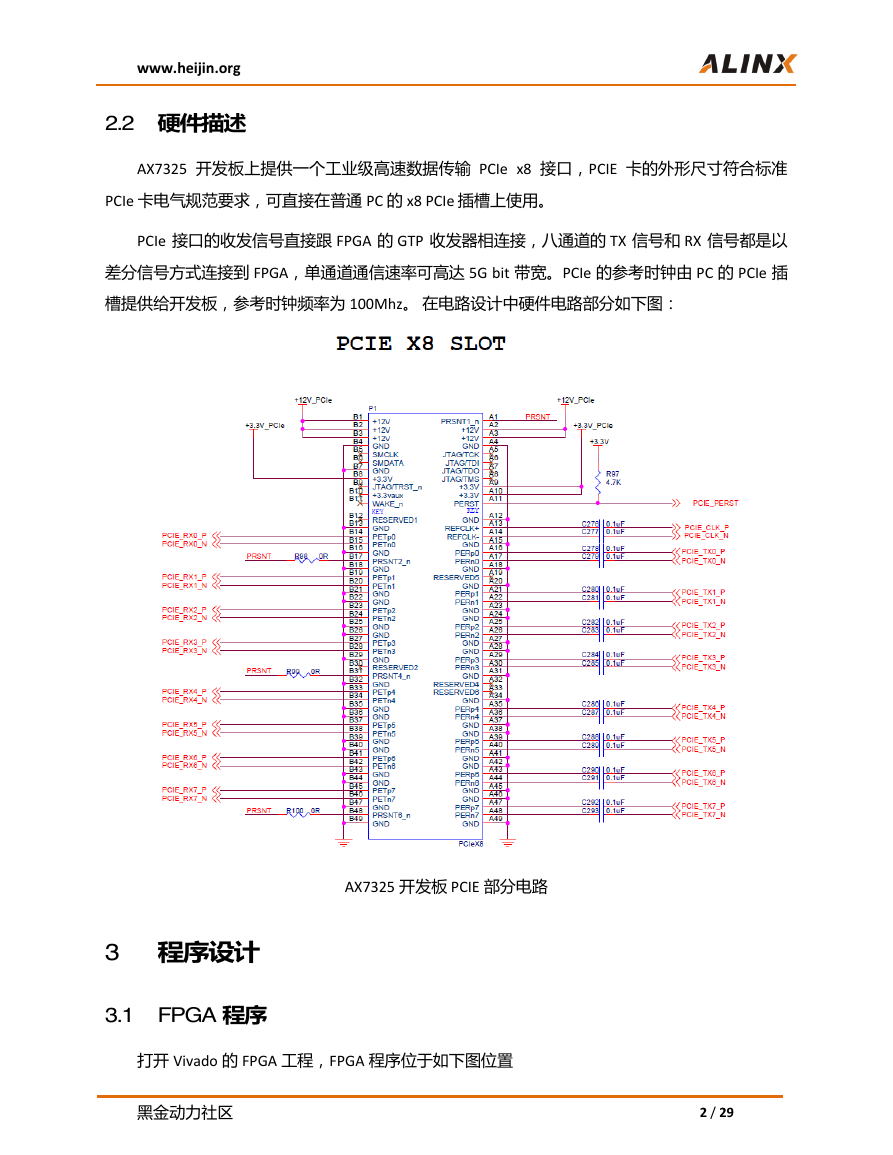

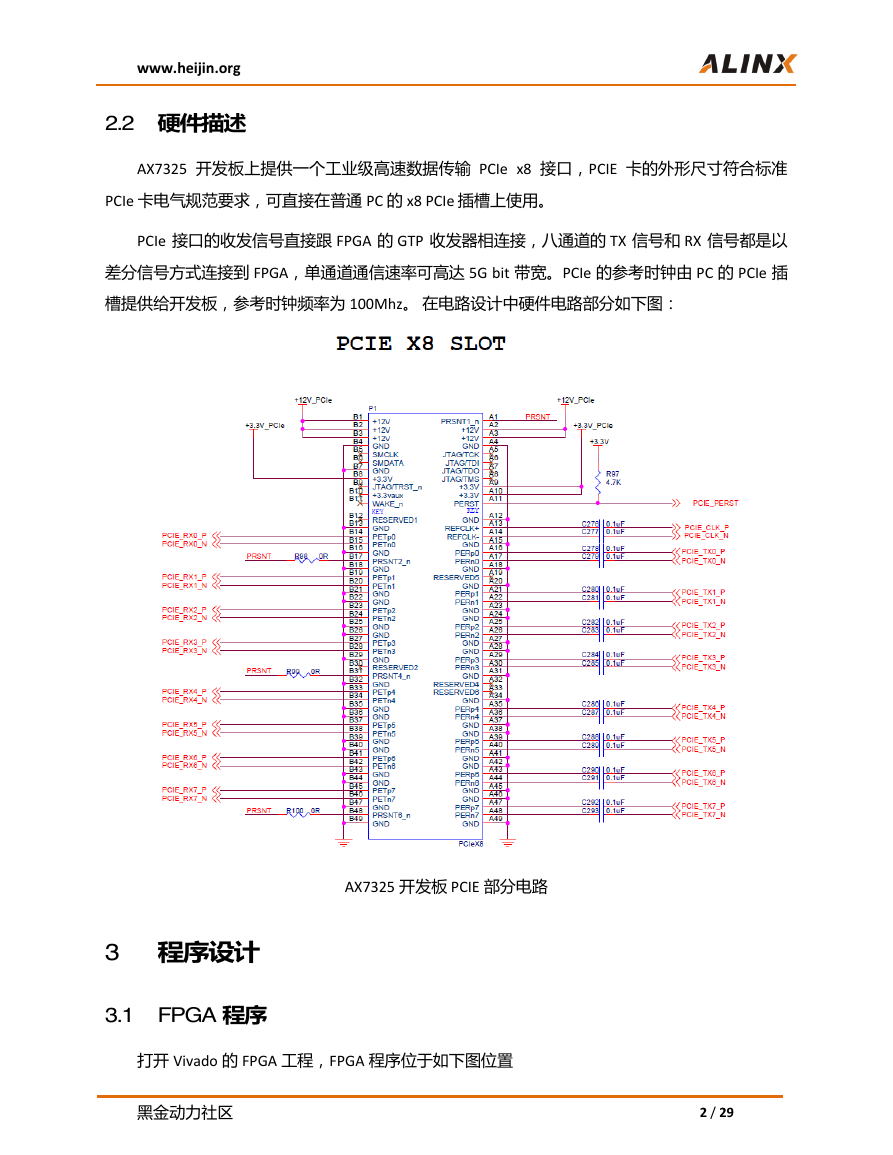

2.2 硬件描述

AX7325 开发板上提供一个工业级高速数据传输 PCIe x8 接口,PCIE 卡的外形尺寸符合标准

PCIe 卡电气规范要求,可直接在普通 PC 的 x8 PCIe 插槽上使用。

PCIe 接口的收发信号直接跟 FPGA 的 GTP 收发器相连接,八通道的 TX 信号和 RX 信号都是以

差分信号方式连接到 FPGA,单通道通信速率可高达 5G bit 带宽。PCIe 的参考时钟由 PC 的 PCIe 插

槽提供给开发板,参考时钟频率为 100Mhz。 在电路设计中硬件电路部分如下图:

AX7325 开发板 PCIE 部分电路

3 程序设计

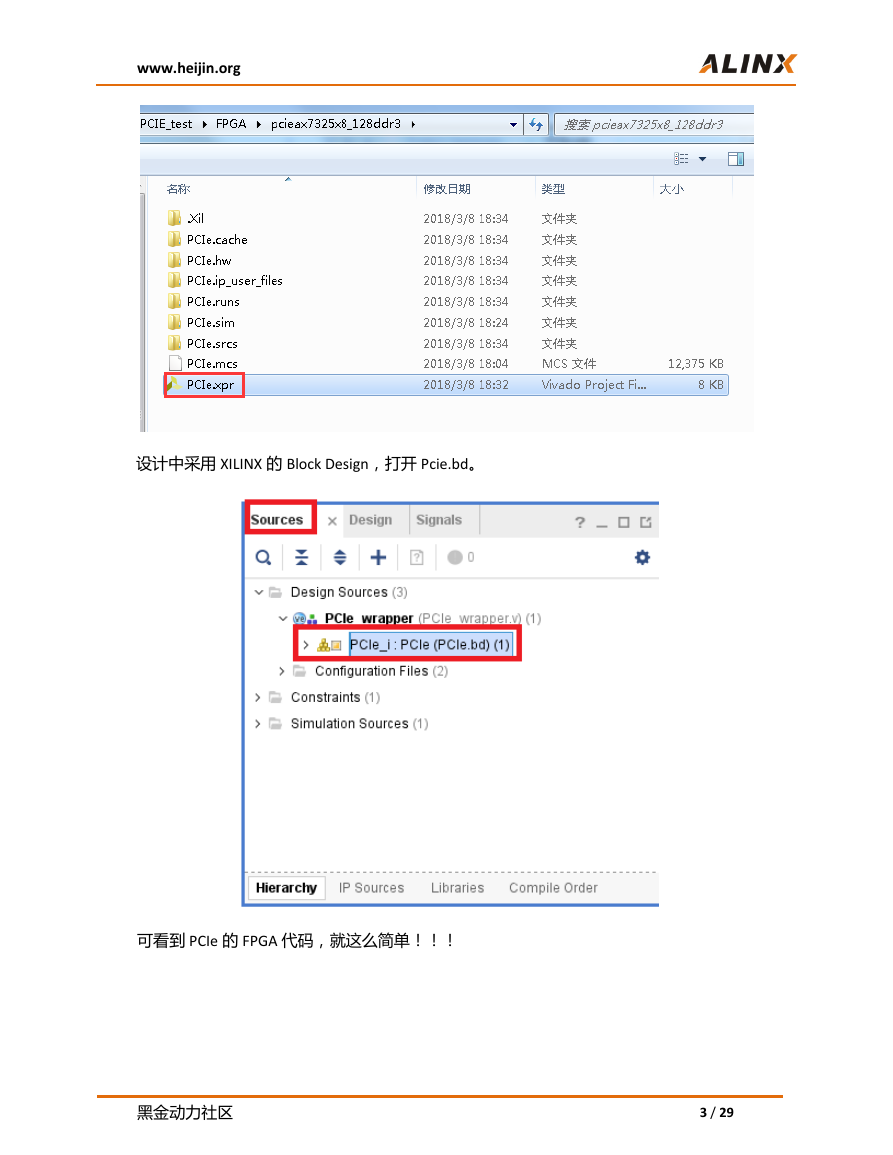

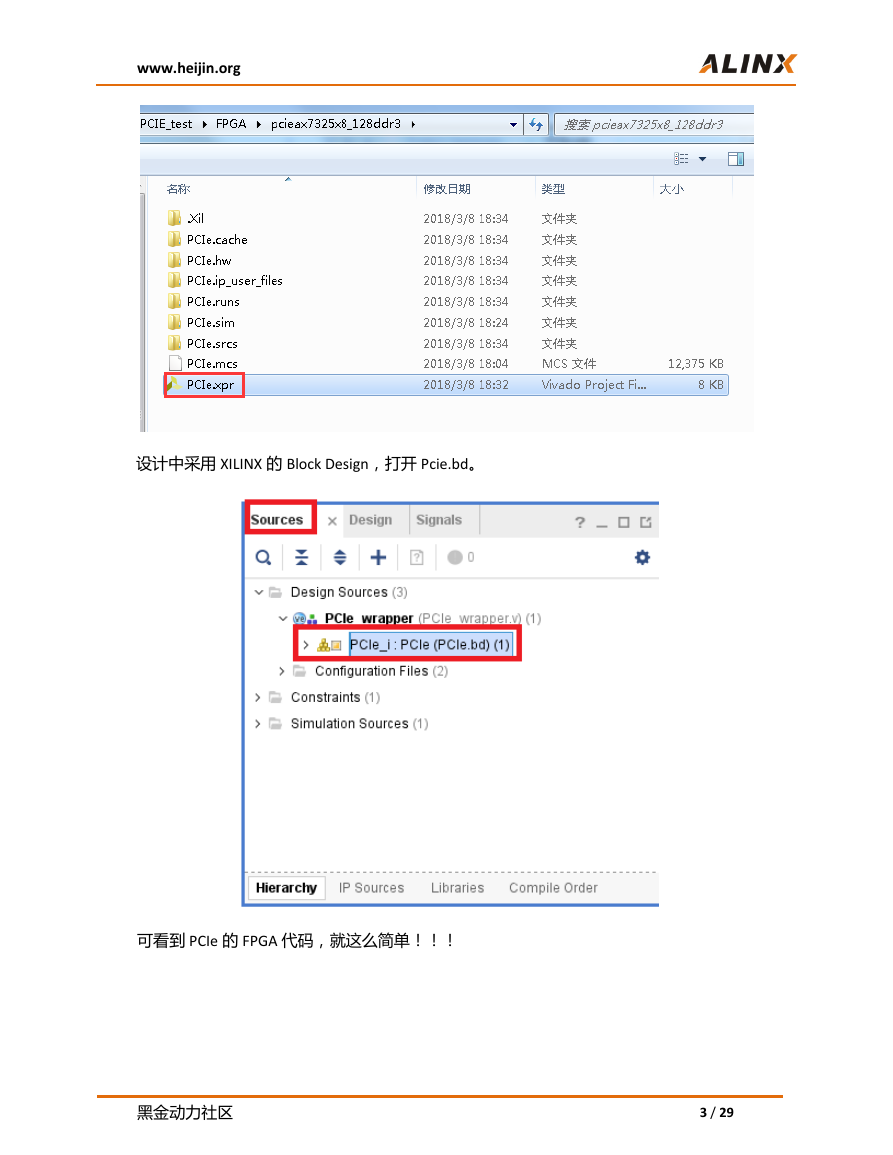

3.1 FPGA 程序

打开 Vivado 的 FPGA 工程,FPGA 程序位于如下图位置

黑金动力社区

2 / 29

�

www.heijin.org

设计中采用 XILINX 的 Block Design,打开 Pcie.bd。

可看到 PCIe 的 FPGA 代码,就这么简单!!!

黑金动力社区

3 / 29

�

www.heijin.org

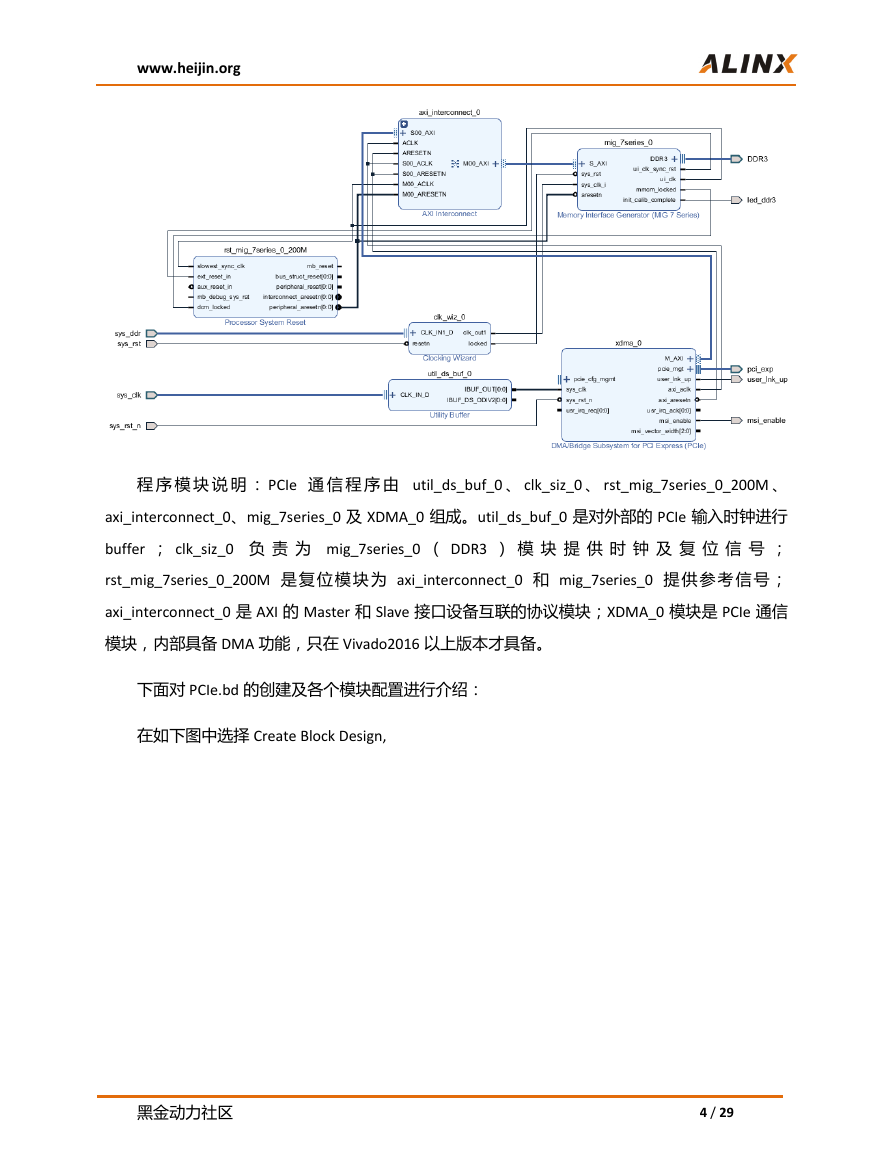

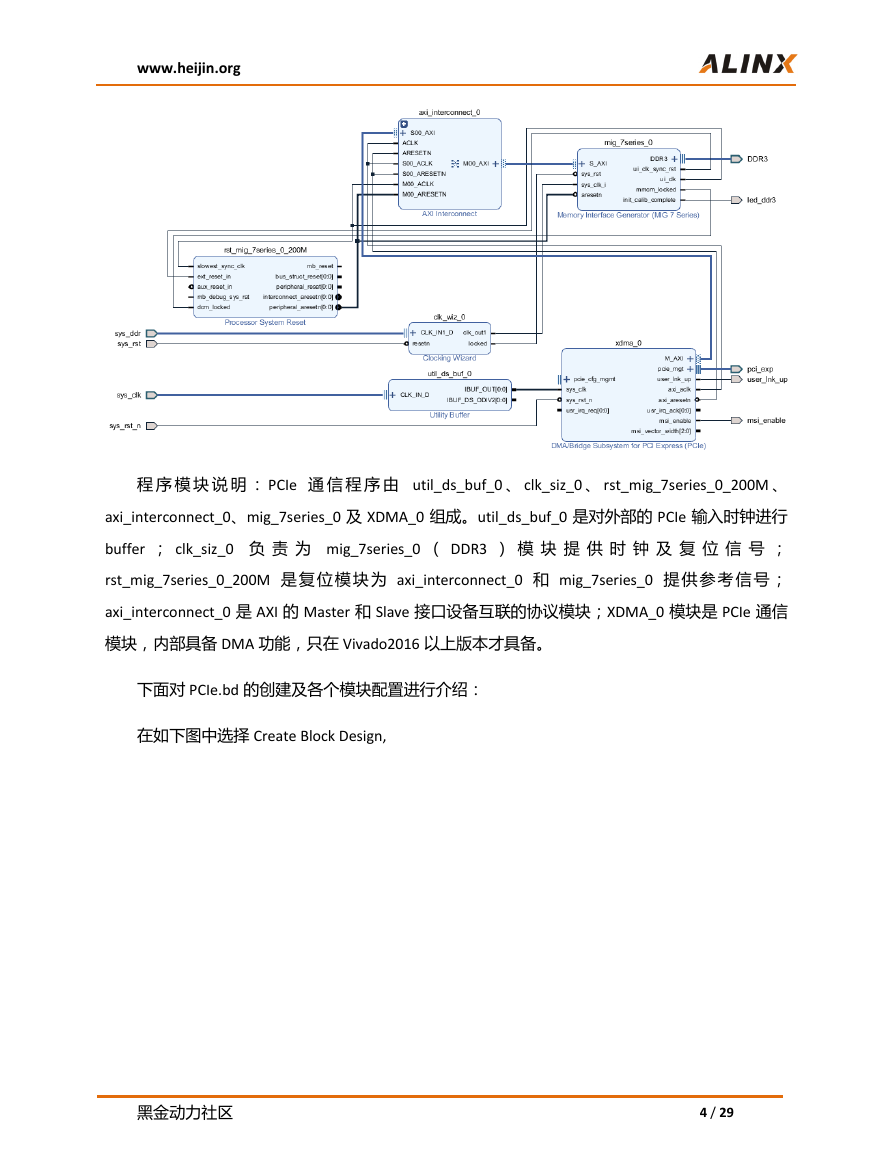

程 序 模 块 说 明 : PCIe 通 信 程 序 由 util_ds_buf_0 、 clk_siz_0 、 rst_mig_7series_0_200M 、

axi_interconnect_0、mig_7series_0 及 XDMA_0 组成。util_ds_buf_0 是对外部的 PCIe 输入时钟进行

buffer ; clk_siz_0 负 责 为 mig_7series_0 ( DDR3 ) 模 块 提 供 时 钟 及 复 位 信 号 ;

rst_mig_7series_0_200M 是 复 位 模 块 为 axi_interconnect_0 和 mig_7series_0 提 供 参 考 信 号 ;

axi_interconnect_0 是 AXI 的 Master 和 Slave 接口设备互联的协议模块;XDMA_0 模块是 PCIe 通信

模块,内部具备 DMA 功能,只在 Vivado2016 以上版本才具备。

下面对 PCIe.bd 的创建及各个模块配置进行介绍:

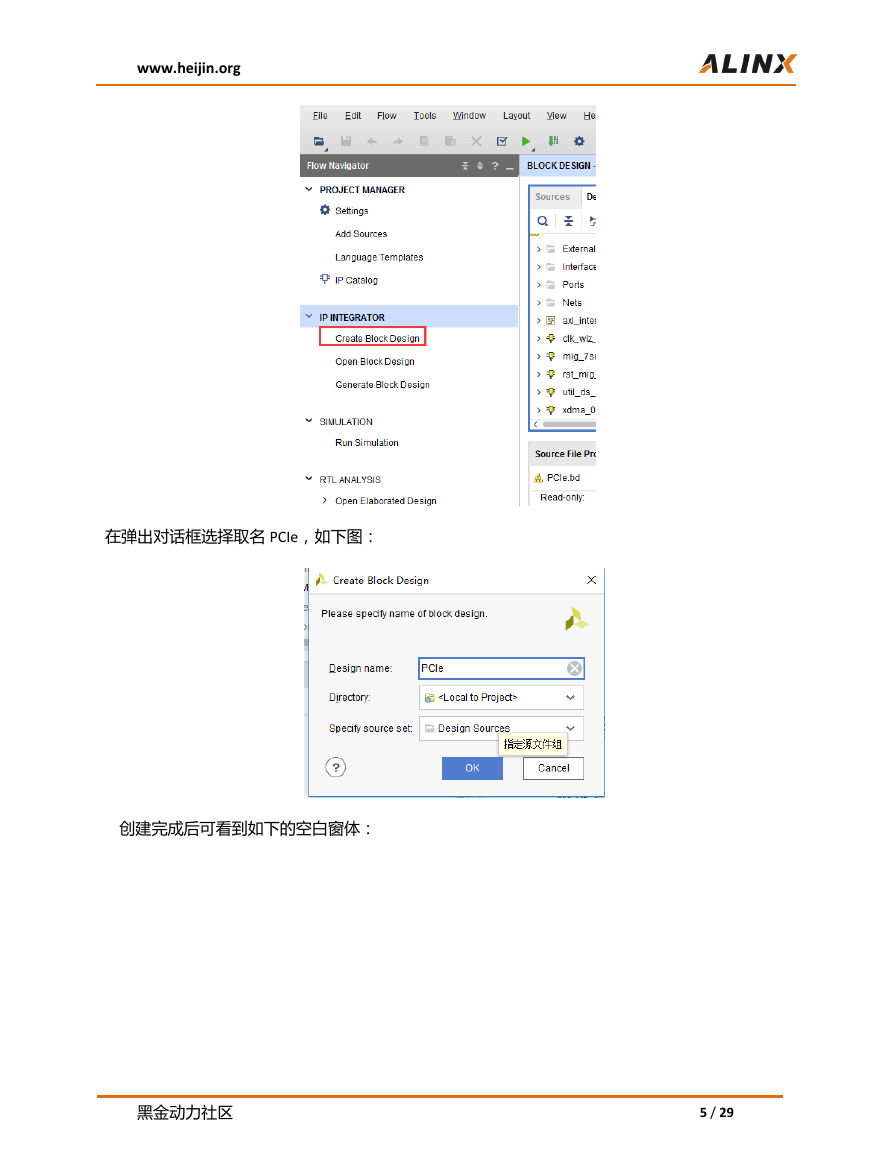

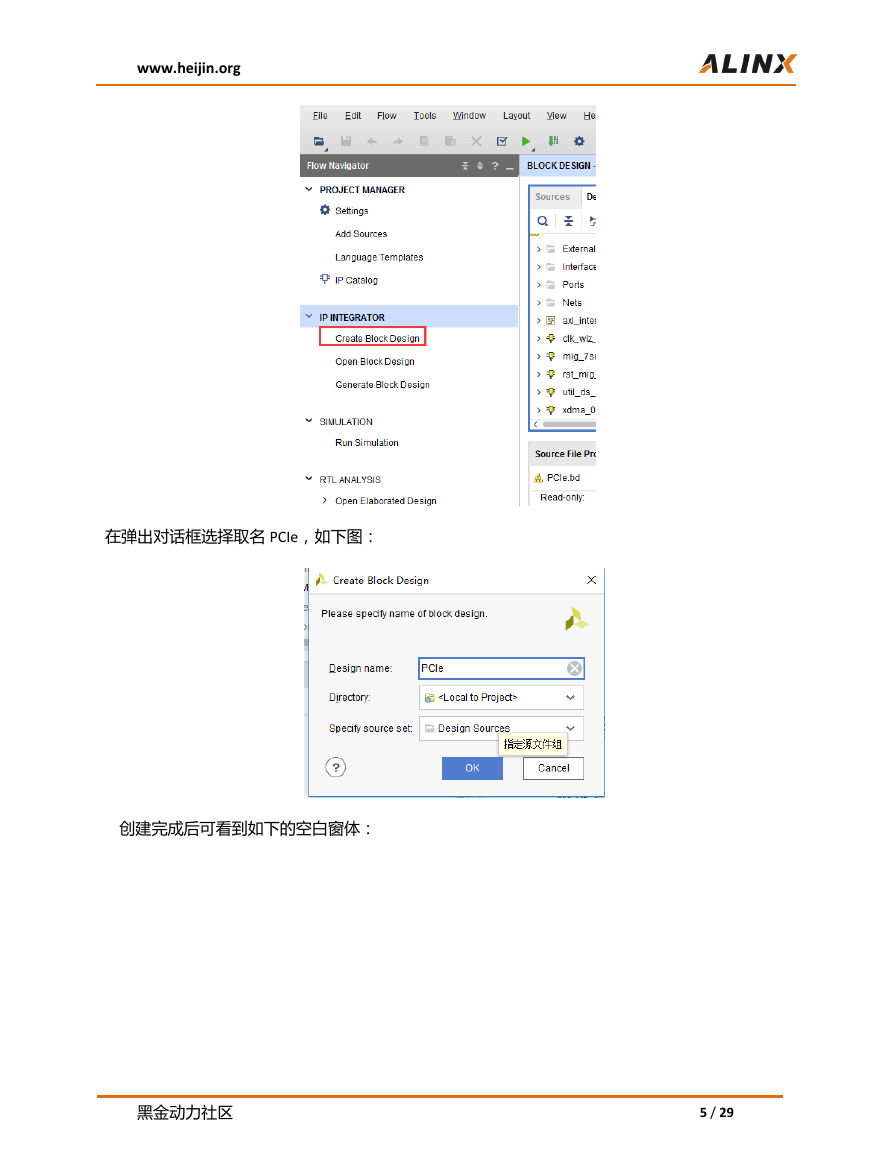

在如下图中选择 Create Block Design,

黑金动力社区

4 / 29

�

www.heijin.org

在弹出对话框选择取名 PCIe,如下图:

创建完成后可看到如下的空白窗体:

黑金动力社区

5 / 29

�

www.heijin.org

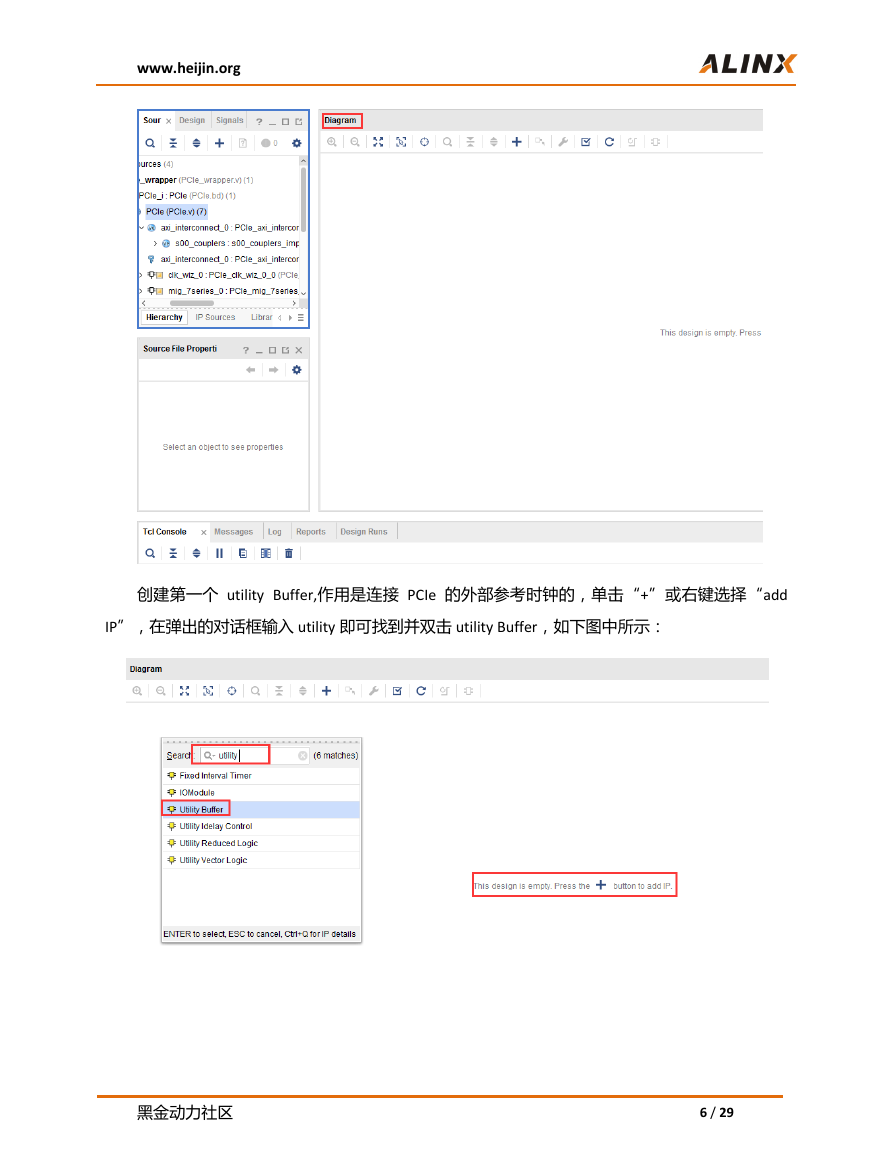

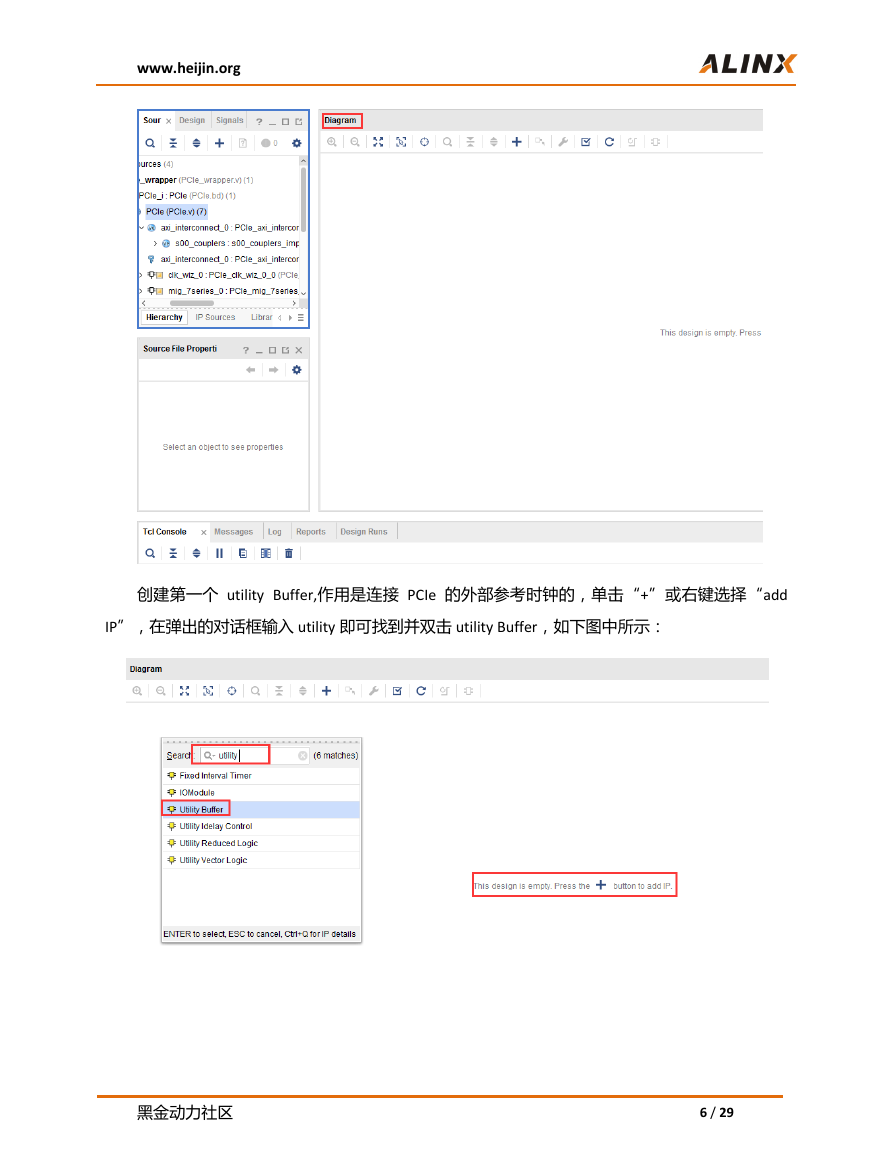

创建第一个 utility Buffer,作用是连接 PCIe 的外部参考时钟的,单击“+”或右键选择“add

IP”,在弹出的对话框输入 utility 即可找到并双击 utility Buffer,如下图中所示:

黑金动力社区

6 / 29

�

www.heijin.org

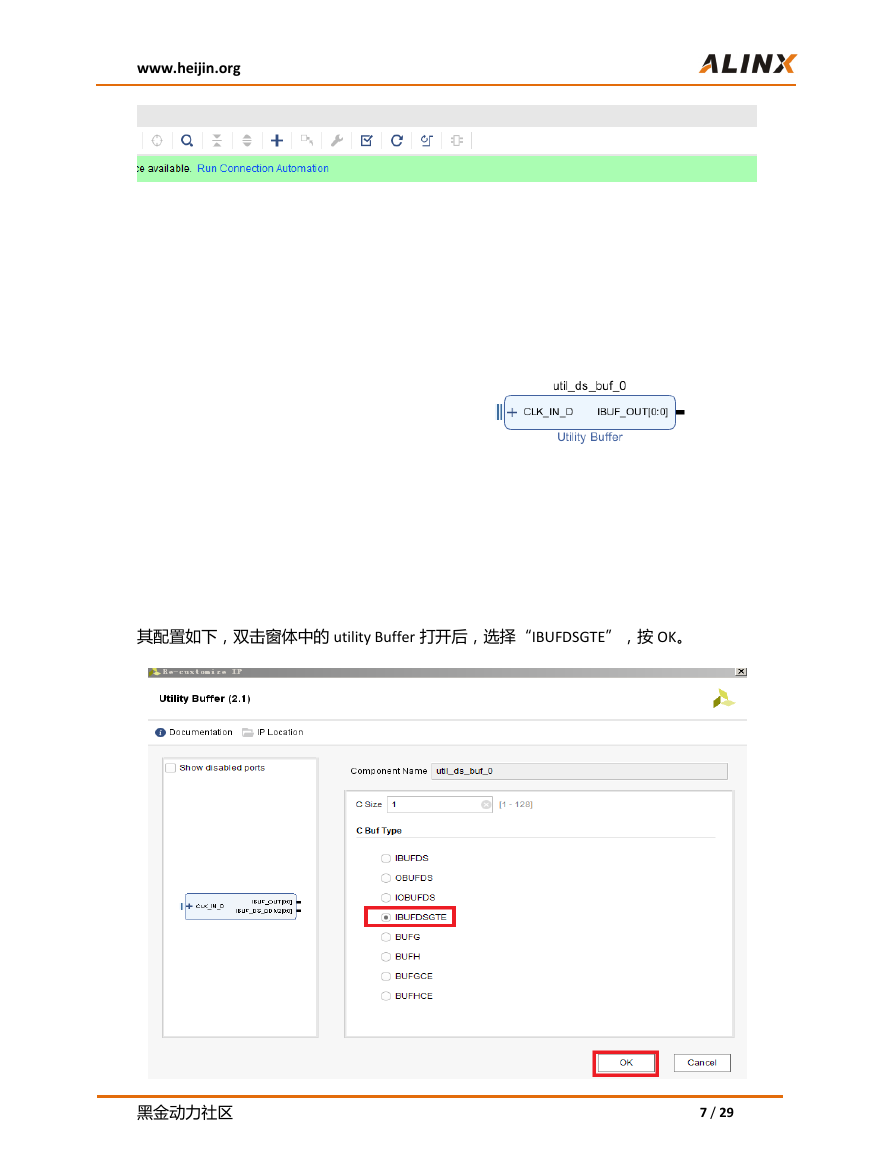

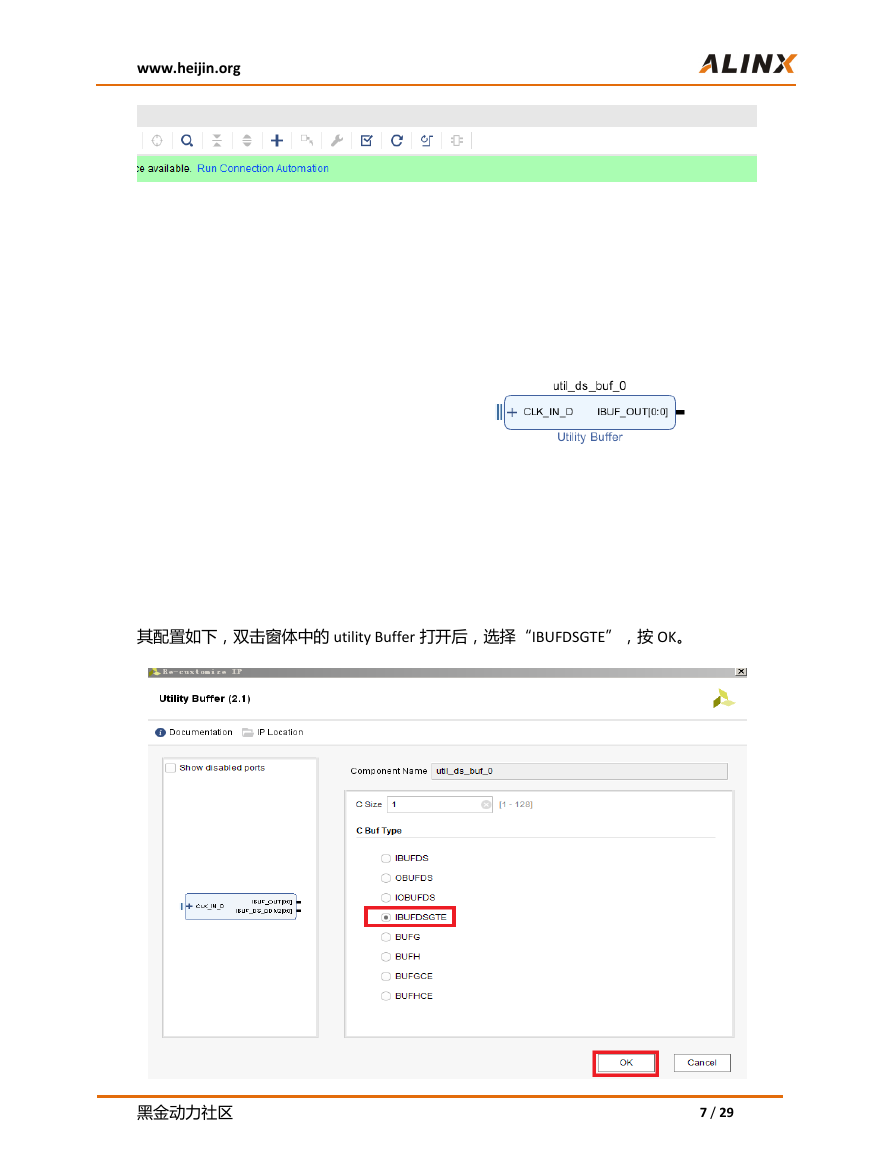

其配置如下,双击窗体中的 utility Buffer 打开后,选择“IBUFDSGTE”,按 OK。

黑金动力社区

7 / 29

�

www.heijin.org

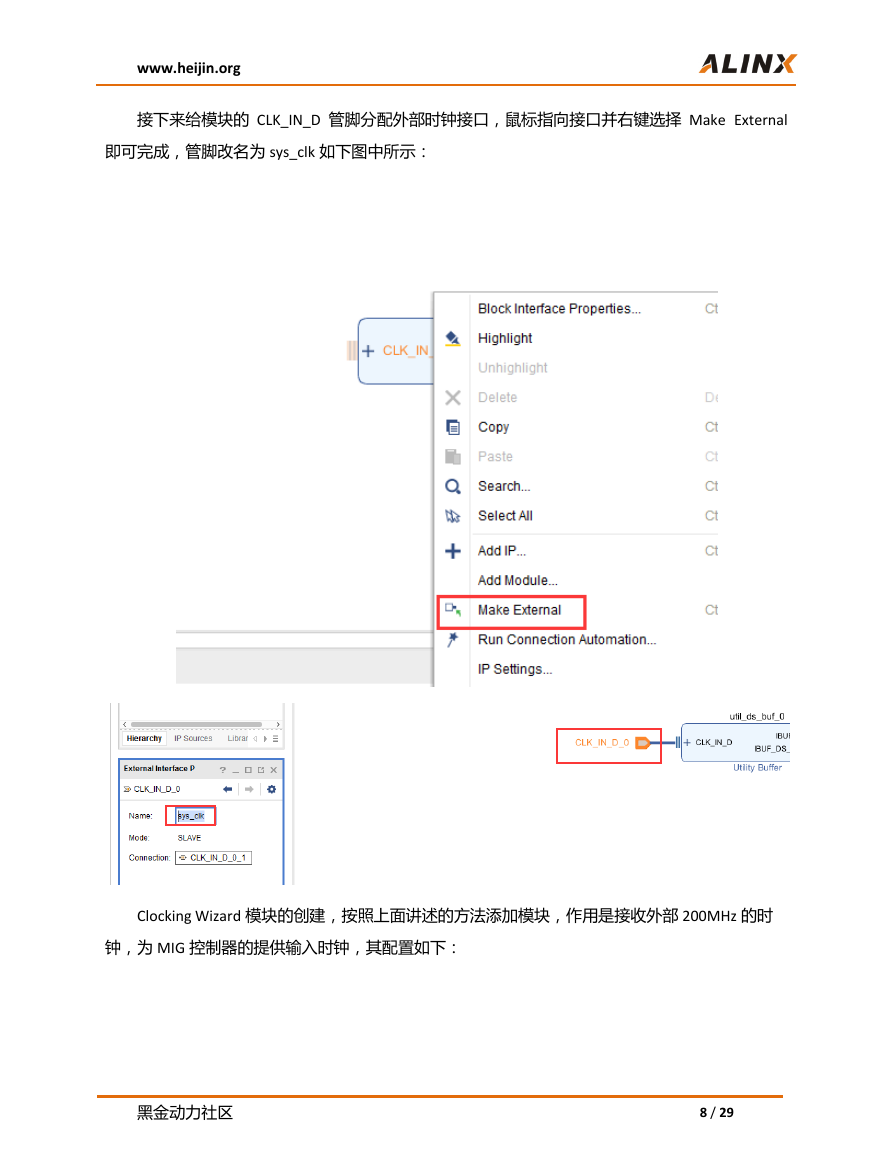

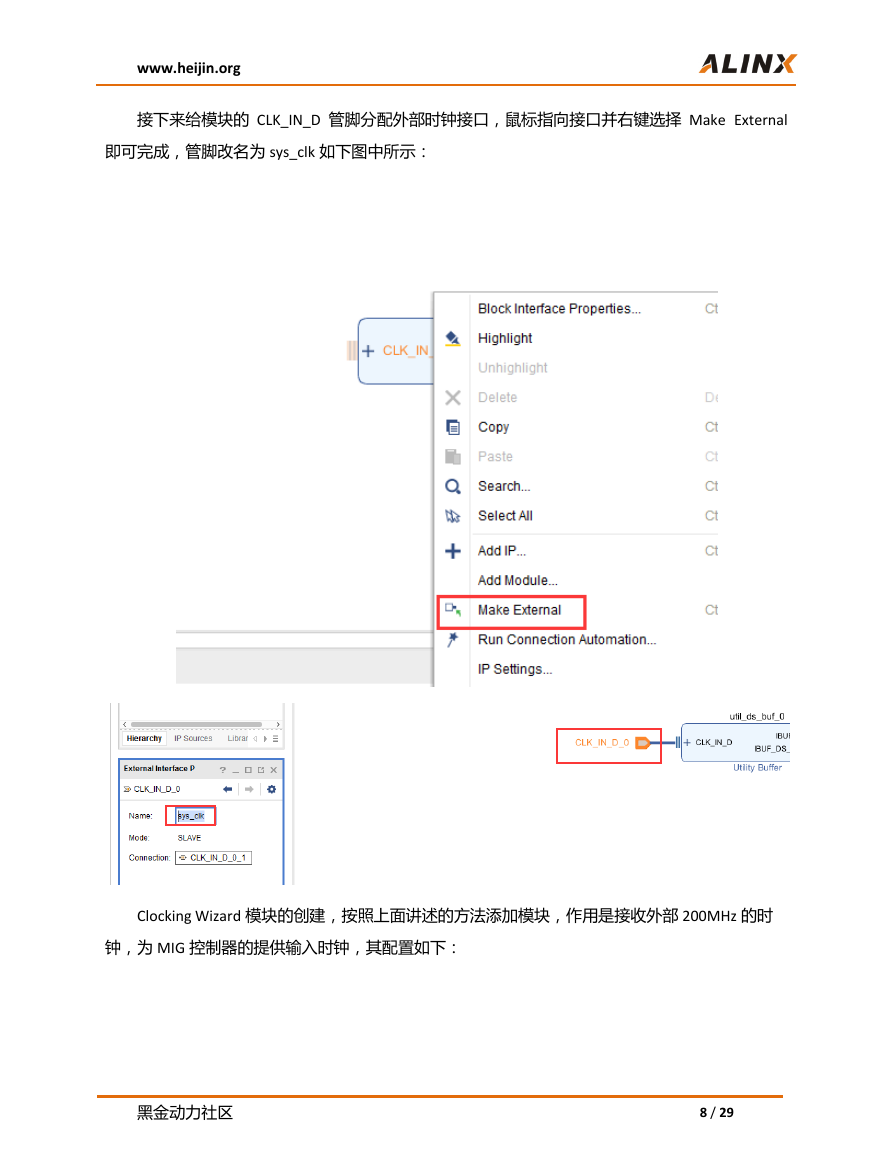

接下来给模块的 CLK_IN_D 管脚分配外部时钟接口,鼠标指向接口并右键选择 Make External

即可完成,管脚改名为 sys_clk 如下图中所示:

Clocking Wizard 模块的创建,按照上面讲述的方法添加模块,作用是接收外部 200MHz 的时

钟,为 MIG 控制器的提供输入时钟,其配置如下:

黑金动力社区

8 / 29

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc