81BCopyright Notice

82BTrademark Acknowledgment

83BFurther Information

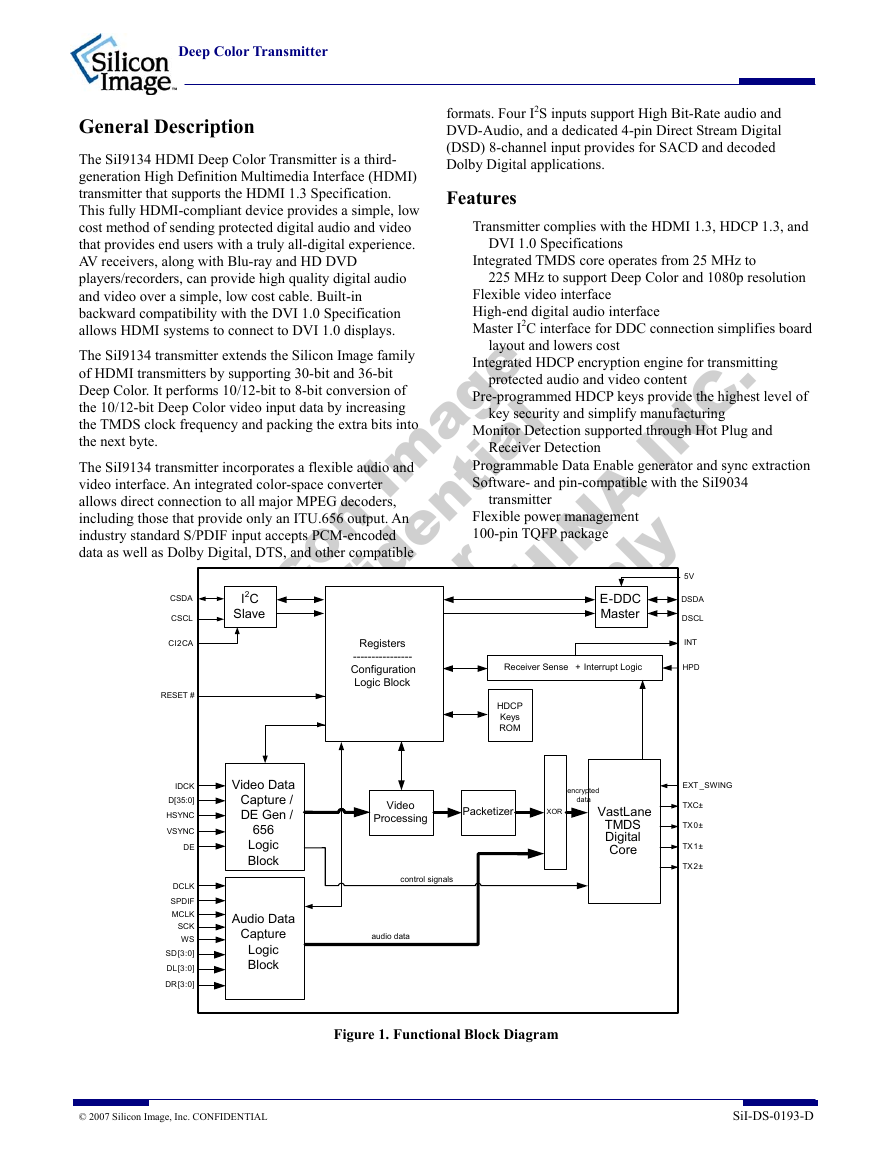

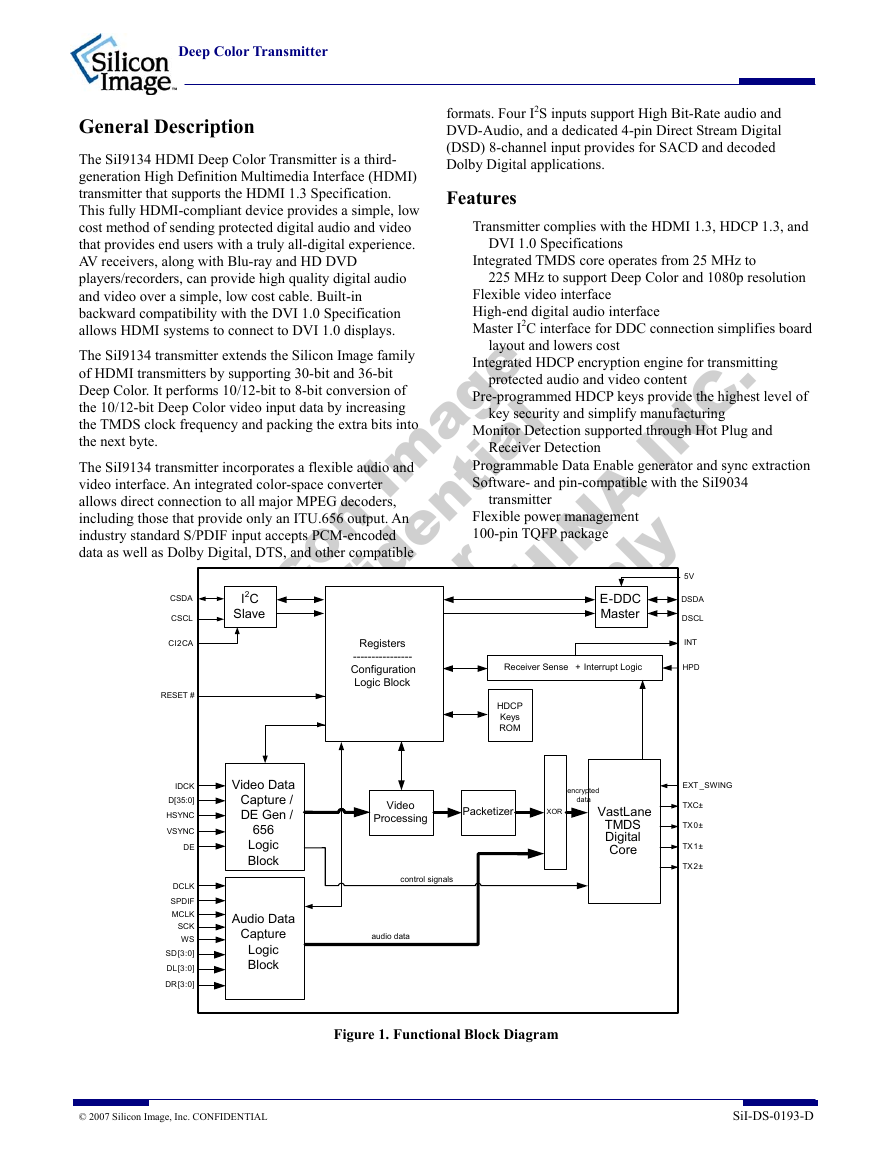

0BGeneral Description

9BFeatures

1BSiI9134 Transmitter Pin Diagram

2BFunctional Description

10BSiI9134 HDMI Deep Color Transmitter Compared with SiI9030/9034 devices

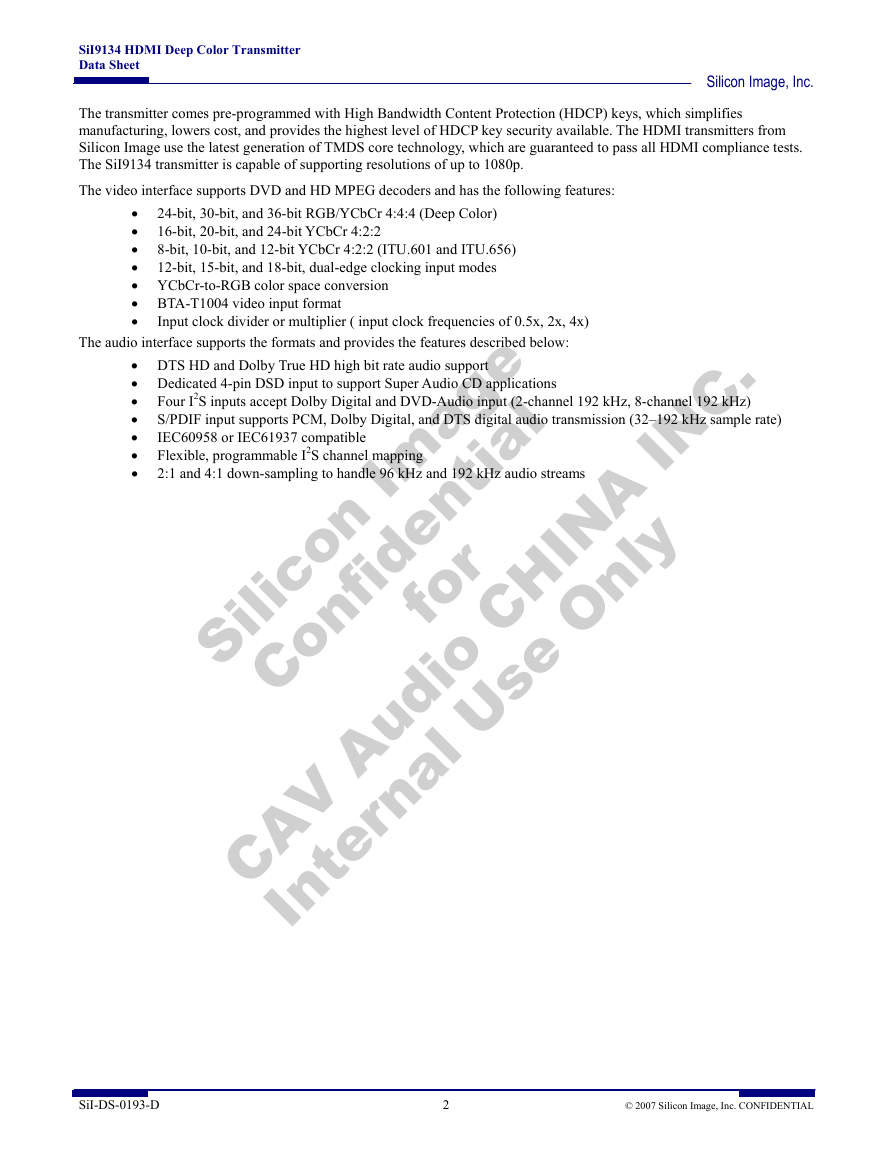

11BVideo Data Input and Conversion

35BVideo Processing Pipeline

36BInput Clock Multiplier/Divider

37BVideo Data Capture Logic

38BConfiguration to Support Deep-color

39BCommon Video Input Formats

40BEmbedded Sync Decoding

41BData Enable Generator

42BRe-sampling

43BColor Space Converters (CSC)

44B14-to-8/10/12-Dither

45BColor Range Scaling

46BClipping

47BHDCP Encryption Engine/XOR Mask

48BTMDS Digital Core

12BAudio Data Capture Logic

49BS/PDIF

50BI2S

51BOne-Bit Audio Input (DSD/SACD)

52BHigh-Bit Rate Audio on HDMI

13BAudio DownSampler Limitations

14BHDCP Key ROM

15BInterrupt Out

16BControl and Configuration

53BRegisters/Configuration Logic

54BMicrocontroller Slave I2C Interface

55BDDC Master I2C Interface

3BElectrical Specifications

17BAbsolute Maximum Conditions

18BNormal Operating Conditions

19BDC Specifications

56BDigital I/O Specifications1

57BDC Power Supply Pin Specifications

20BAC Specifications

58BTMDS AC Timing Specifications

59BAudio AC Timing Specifications

84BS/PDIF Input Port Timings

85BI2S Input Port Timings

86BDSD Input Port Timings

60BVideo AC Timing Specifications

61BControl Timing Specifications

21BTiming Diagrams

62BInput Timing Diagrams

63BAudio Timing Diagrams

64BPower Supply Sequencing

65BOutput Timing Diagrams

4BPin Descriptions

22BVideo and Audio Input Pins

23BConfiguration/Programming Pins

24BControl Pins

25BDifferential Signal Data Pins

26BPower and Ground Pins

5BData Bus Mappings

66BRGB and YCbCr 4:4:4 Formats with Separate Syncs

67BYC 4:2:2 Formats with Separate Syncs

68BYC 4:2:2 Formats with Embedded Sync

69BYC Mux 4:2:2 Formats with Separate Syncs

70BYC Mux 4:2:2 Embedded Sync Formats

71B12/15/18-Bit DMO RGB and YCbCr Formats

6BDesign Guidelines

27BPower Supplies

72BVoltage Ripple Regulation

73BDecoupling

28BHigh-Speed TMDS Signals

74BESD Protection

75BTransmitter Layout Guidelines

29BProtection for I2C Port

30BHot Plug Signal Conditioning

31BHDMI Design Considerations

76BHDMI CTS Test ID 7-4: TMDS Differential Rise and Fall Time

77BRecommendation to pass Test ID 7-4

32BEMI Considerations

33BTypical Circuit

78BPower Supply Decoupling

79BHDMI Port TMDS Connections

80BControl Signal Connections

7BPackaging

34B100-pin TQFP Package Dimensions and Marking Specification

8BOrdering Information

87B Disclaimers

88BProducts and Services

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc