Verilog HDL & VHDL

高级设计与实践

李凡

�

目录

第一章 阅读指南 ............................................................................................................................. 6

第二章 现代数字硬件设计导论 ..................................................................................................... 7

2.1 数字系统设计过程 .......................................................................................................... 10

2.2 早期的人工图纸作业 ...................................................................................................... 10

2.3 ASIC 器件和现场定制需求 .............................................................................................. 10

2.4 基于 ROM 器件的组合逻辑(ROM-Based Combinational Logic) ............................... 10

2.5 PAL 和 PLA 的出现及其工作原理 .................................................................................... 10

2.6 PLD 器件 ........................................................................................................................... 10

2.7 GAL 器件的出现和特点 ................................................................................................... 10

2.8 FPGA 诞生的前夜—CPLD ................................................................................................. 10

2.9 硅谷传奇—Altera 和 Xilinx 的成立 ................................................................................ 10

2.10 Altera 的产品和发展历程 .............................................................................................. 10

2.11 Xilinx 的产品和发展历程 ............................................................................................... 10

2.12 Actel 的产品和发展历程................................................................................................ 10

2.13 FPGA 的结构(Altera) ................................................................................................. 10

2.13.1 FPGA 与 CPLD 的比较 .......................................................................................... 10

2.13.2 FPGA 的资源和平面布置 .................................................................................... 10

2.13.3 FPGA 的查找表 LUT 及其工作原理 .................................................................... 10

2.13.4 FPGA 的 LE 单元 .................................................................................................. 10

2.13.5 FPGA 的锁相环 .................................................................................................... 10

2.13.6 FPGA 对 DDR2/DDR3 的支持 .............................................................................. 10

2.13.7 FPGA 的存储器资源和使用 ................................................................................ 10

2.13.8 FPGA 的基于 RAM 的配置 .................................................................................. 10

2.13.9 FPGA 的在线编程和 JTAG ................................................................................... 10

2.14 FPGA 的应用方向 ........................................................................................................... 10

2.14.1 替代 ASIC 和 ASSP .............................................................................................. 10

2.14.2 高速图像应用 ..................................................................................................... 10

2.14.3 高速 DSP 应用 .................................................................................................... 10

2.14.4 加速器应用 ......................................................................................................... 10

2.14.5 在片系统 SoPC 应用(替代 ASIC 的 ARM 和单片机) .................................... 10

2.14.6 高速串行通信应用 ............................................................................................. 10

2.14.7 先有“芯”后有“片”的转变(现代数字技术标准的应用) ..................... 10

2.14.8 作为 ASIC 器件的准备和过渡 ........................................................................... 10

第三章 现代数字电路基础 ........................................................................................................... 11

3.1 基本逻辑门和 CMOS 电路 .............................................................................................. 11

3.1.1 反相器和 CMOS 电路 ........................................................................................... 13

3.1.2 基本逻辑单元 ....................................................................................................... 15

3.2 输入和输出...................................................................................................................... 19

3.2.1 端口 I/O 标准 ....................................................................................................... 19

3.2.2 逻辑值和噪声容限 ............................................................................................... 25

3.2.3 漏极开路输出(OD)或集电极开路输出(OC) ............................................. 27

3.2.4 端口的上拉(Pull-Up)和下拉() ................................................................... 28

3.2.5 三态输出 ............................................................................................................... 28

�

3.2.6 端口的扇入和扇出 ............................................................................................... 28

3.3 布尔代数.......................................................................................................................... 28

3.4 德摩根变换...................................................................................................................... 28

3.5 维恩图.............................................................................................................................. 28

3.6 卡诺图和真值表 .............................................................................................................. 28

3.7 二元决策图...................................................................................................................... 28

3.8 组合逻辑设计.................................................................................................................. 28

3.8.1 积之和(SOP)及其表达式 ................................................................................ 28

3.8.2 和之积(POS)及其表达式 ................................................................................ 28

3.8.3 布尔表达式的化简 ............................................................................................... 28

3.9 毛刺和竞争冒险 .............................................................................................................. 28

3.10 时序逻辑设计................................................................................................................ 28

3.10.1 锁存器(Latch)和传输门 ................................................................................ 28

3.10.2 触发器(Flip-Flop) ........................................................................................... 28

3.11 数值类型........................................................................................................................ 28

3.11.1 布尔类型............................................................................................................. 28

3.11.2 有符合数和无符号数 ......................................................................................... 28

3.12 浮点数 ........................................................................................................................... 28

第四章 HDL 基础知识 ................................................................................................................... 28

4.1 数字电路设计概述 .......................................................................................................... 29

4.2 硬件描述语言基础 .......................................................................................................... 32

4.2.1 三种建模方式 ....................................................................................................... 35

4.2.2 数据流建模 ........................................................................................................... 36

4.2.3 行为建模 ............................................................................................................... 36

4.2.4 结构化建模 ........................................................................................................... 36

4.2.5 显示建模和隐式建模 ........................................................................................... 36

4.2.6 信号延迟与中间信号 ........................................................................................... 36

4.2.7 可定参设计 ........................................................................................................... 38

4.2.8 并发-顺序-循环-控制 ........................................................................................... 38

4.2.9 组合逻辑设计例子 ............................................................................................... 38

4.2.10 时序逻辑设计例子 ............................................................................................. 38

4.3 有限状态机设计 .............................................................................................................. 39

4.3.1 有限状态机理论(Mealy ,Moore) ................................................................ 39

4.3.2 有限状态机的三段式编码 ................................................................................... 39

4.3.3 线性序列机 LSM ................................................................................................... 39

4.3.4 状态转移图 STG ................................................................................................... 39

4.3.5 算法机 ASM 和算法流程图 ASMc ....................................................................... 39

4.3.6 显示状态机和隐式状态机 ................................................................................... 39

4.3.7 摩尔机设计例子:LPM 分频器 ........................................................................... 39

4.3.8 米利机设计例子:自动售货机 ........................................................................... 39

4.4 验证 ................................................................................................................................. 39

4.4.1 验证的理论和方法 ............................................................................................... 39

4.4.2 运行仿真的人工方式 ........................................................................................... 39

4.4.3 运行仿真的自动方式(NativeLink) .................................................................. 39

�

4.5 同步设计.......................................................................................................................... 39

4.5.1 同步设计的概念 ................................................................................................... 39

4.5.2 激励和响应 ........................................................................................................... 39

4.5.3 同步机制 ............................................................................................................... 39

4.5.4 同步翻转噪声(SSN)和功耗............................................................................. 39

4.5.5 时钟节点(Pipeline Node)和时钟域(Clock Domain) .................................. 39

4.5.6 时钟偏斜 Skew 和时钟抖动 Jitter ....................................................................... 39

4.5.7 同步设计中的 One-Clock 原则和时钟流分析(TP 图) ................................... 39

4.5.8 基于时钟节点的时序约束和时序分析 ............................................................... 39

第五章 可综合编码(Coding Style for Synthesis, CSS)........................................................... 40

5.1 编写综合优化的代码 ...................................................................................................... 40

5.2 组合电路的 CSS ............................................................................................................... 49

5.3 优先结构的 CSS ............................................................................................................... 49

5.4 锁存器电路的 CSS ........................................................................................................... 49

5.5 三态门的 CSS ................................................................................................................... 49

5.6 总线接口的 CSS ............................................................................................................... 49

5.7 显示状态机的 CSS ........................................................................................................... 49

5.8 寄存器和计数器的 CSS ................................................................................................... 49

5.9 复位电路的 CSS ............................................................................................................... 49

5.10 层次化和打平................................................................................................................ 49

第六章 不可综合编码(Coding Style for Dis-Synthesis, CSDS) .............................................. 49

6.1 何时需要不可综合代码 .................................................................................................. 49

6.2 时钟信号的 CSDS ............................................................................................................ 49

6.3 顺序信号的 CSDS ............................................................................................................ 49

6.4 状态机的 CSDS ................................................................................................................ 49

6.5 CSDS 用于构建电路模型 ................................................................................................. 49

6.6 CSDS 用于 Testbench ........................................................................................................ 49

第七章 数字系统设计例子 ........................................................................................................... 50

7.1 图像处理.......................................................................................................................... 50

7.2 数字滤波器...................................................................................................................... 50

7.3 流水线架构例子 .............................................................................................................. 50

7.4 环形缓冲器...................................................................................................................... 50

7.5 同步和异步 FIFO ............................................................................................................. 50

7.6 行波进位加法器 .............................................................................................................. 50

7.7 超前进位加法器 .............................................................................................................. 50

7.8 无符号乘法器.................................................................................................................. 50

7.9 有符号乘法器.................................................................................................................. 50

7.10 浮点数乘法器................................................................................................................ 50

第八章 FPGA 和边界扫描 JTAG .................................................................................................... 50

8.1 边界扫描和可测试技术 .................................................................................................. 50

8.2 FPGA 的 JTAG 操作模式 ................................................................................................... 50

8.3 JTAG 寄存器 ...................................................................................................................... 50

8.4 JTAG 指令 .......................................................................................................................... 50

8.5 TAP 寄存器架构 ................................................................................................................ 50

�

8.6 TAP 控制器 ........................................................................................................................ 50

8.7 使用 JTAG 进行测试的例子 ............................................................................................ 50

8.8 Altera 的 JTAG 应用 .......................................................................................................... 50

第九章 时序分析 ........................................................................................................................... 50

9.1 时序分析基础.................................................................................................................. 50

9.2 管脚至管脚延迟 tPD 和寄存器的时钟输出延迟 tCO ................................................... 50

9.3 由 tPD 和 tCO 得到的时序约束 ...................................................................................... 50

9.4 插入流水线...................................................................................................................... 50

9.5 建立时间 tSU 和保持时间 tH ......................................................................................... 50

9.6 由 tSU 和 tH 得到的时序约束 ........................................................................................ 50

9.7 时序违规分析.................................................................................................................. 50

9.8 时序约束脚本.................................................................................................................. 50

9.9 时序分析工具 timeQuest ................................................................................................ 50

9.10 时序分析应用实例:引信控制器 ................................................................................ 50

第十章 复杂系统设计例子 ........................................................................................................... 50

10.1 UART 收发器设计 ........................................................................................................... 50

10.2 MCS51 单片机设计 ........................................................................................................ 50

10.3 图像加速器设计............................................................................................................ 50

10.4 Huffman 编码器设计...................................................................................................... 50

�

第一章 阅读指南

�

第二章 现代数字硬件设计导论

本书讨论的 HDL,与现代数字硬件设计方法有关。数字硬件设计方法的进步与数字电子设备

的进步密不可分。而现代的数字电子设备则直接体现了现代人类的文明进步。从早上的牛奶

-汉堡,iphone5,高速公路,GPS 导航到晚上的 HDTV,这种体现现代文明的电子设备无处不

在。这个时代竟然出现这样的奇迹:10 年前生活的人,比 100 年前的生活的人享受到更多

地技术文明;18 个月前生活的人,显然会比 10 年前的那个人更美好;而生活在当下这一刻

的人们,完全可能会比 18 个月前的人,甚至比 6 个月前的人具有更多的技术特权。没有必

要也不可能了解所有这些人类进步的细节,但我们必须清楚地知道这些人类进步来自何处:

好像并非完全来自达尔文的物种进化历程,并非来自征服者的强权统治。确确实实地,它来

自人类高级智慧活动本身,这种高级智慧活动,并不完全适用达尔文物竞天泽,适者生存所

述的自然淘汰的进化原则,在数千万年生物进化的历程中,没有看到过如此惊奇的进化方式:

物种中的某个个体的发现或知识,可以迅速地传播至整个物种,并可以将这些知识迅速地进

行积淀。自然界中不存在的这些人类的高级智慧行为(姑且称为超自然行为)包括:知识的

传播和研究(大学),民主政治(议会制度),体育和文艺活动(艺术家)等等。当然,达尔

文物种进化的自然原则在人类中也普遍存在,例如:军队和战争(非洲蚂蚁),领土争端(狼

的领地),领袖和统治(狮子社会)等等。人类世界的未来,究竟是由上帝决定,还是我们

自己,这的确是一个未知数。

好在本书并不是一本讨论物种进化的书,而是一本论述现代硬件设计技术的书,这样,我们

就可以比较客观地从历史和物理两个角度来叙述它。

从 17 世纪到 19 世纪,物理学领域的发生的四个重要事件开启了现代人类文明的进程,它们

是:牛顿的经典物理学,麦克斯韦的电磁方程组,爱因斯坦的相对论以及普朗克的量子力学。

虽然现代物理学的重大进展促进了人类进步,但技术(technology)领域的发展速度却十分

惊人,典型的例子就是美国硅谷的摩尔周期:18 个月诞生一代新技术(注:Gordon Moore

在 1965 年预言集成电路的密度将每年翻一倍,但实际速度是每 18~20 个月翻一倍,并保持

这个速度近 40 年)。

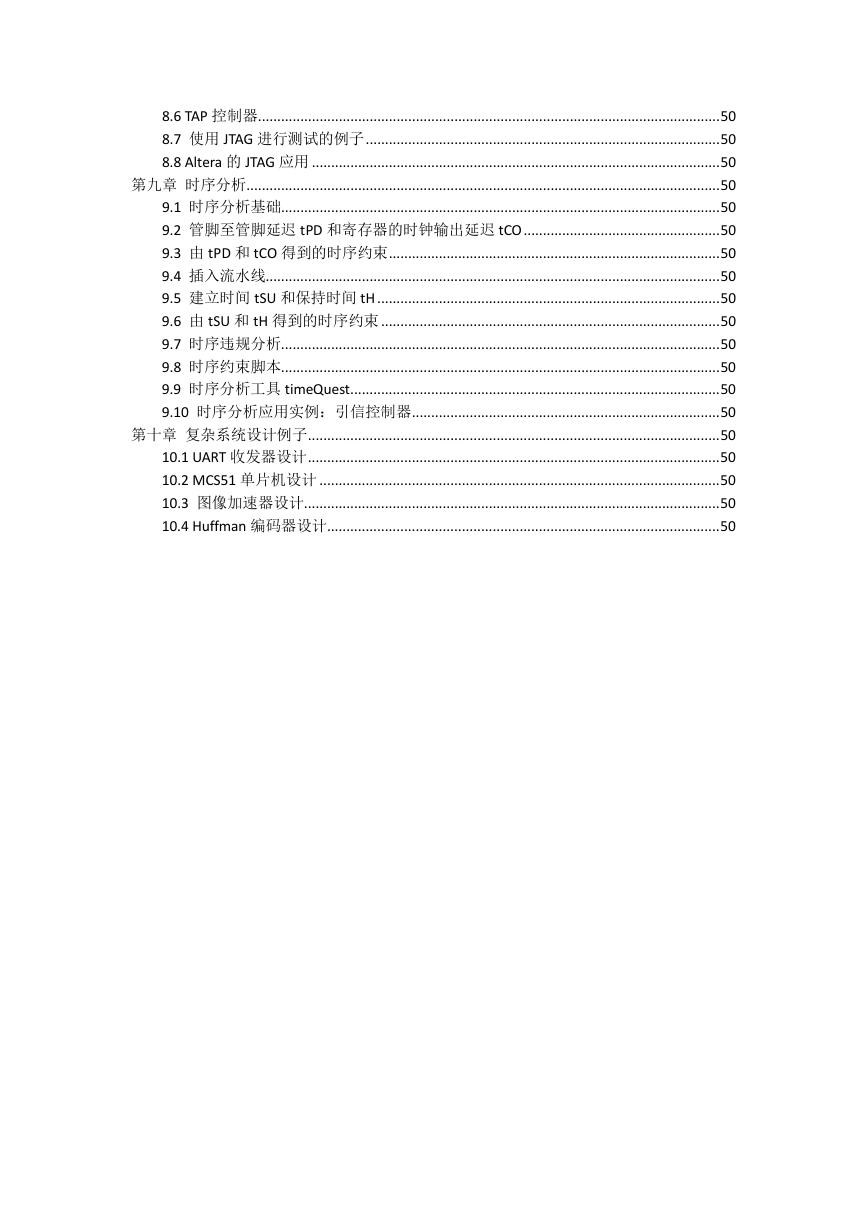

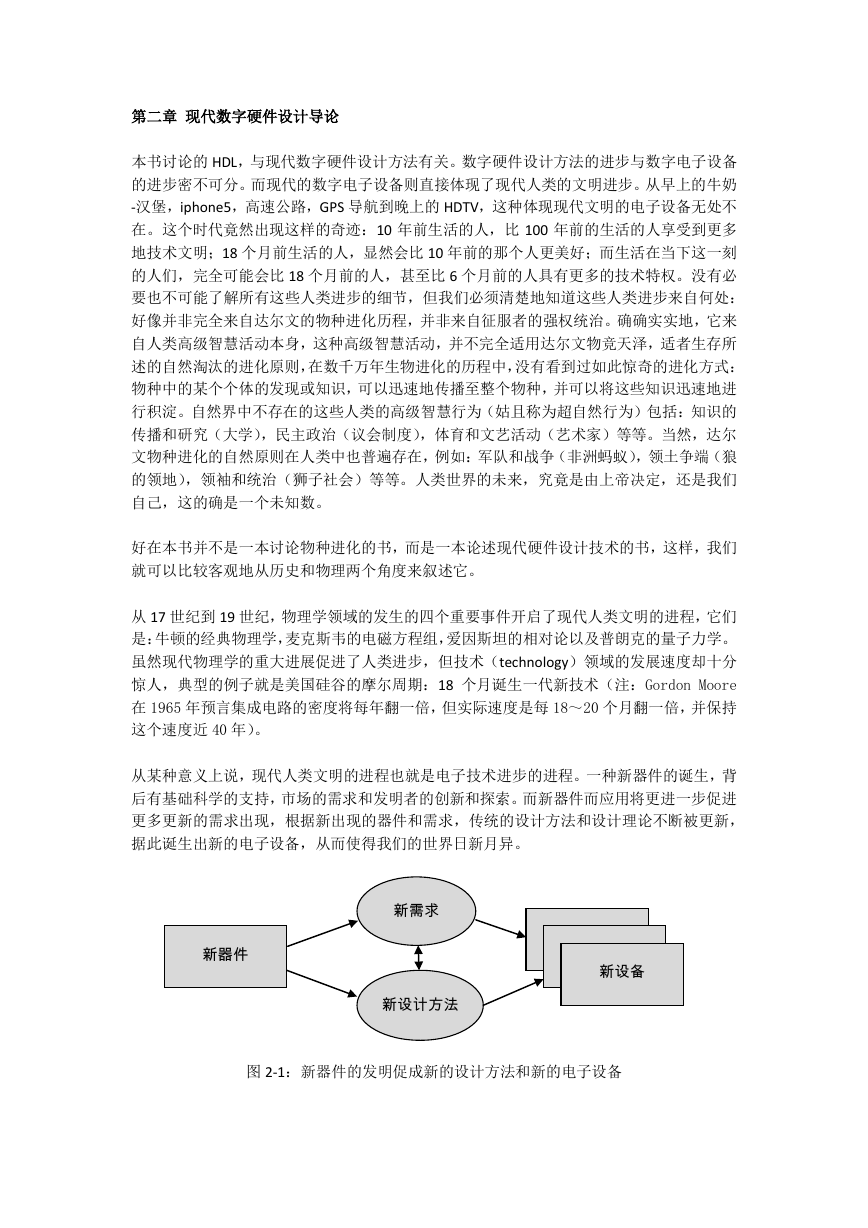

从某种意义上说,现代人类文明的进程也就是电子技术进步的进程。一种新器件的诞生,背

后有基础科学的支持,市场的需求和发明者的创新和探索。而新器件而应用将更进一步促进

更多更新的需求出现,根据新出现的器件和需求,传统的设计方法和设计理论不断被更新,

据此诞生出新的电子设备,从而使得我们的世界日新月异。

新设计方法

新器件

新需求

新设备

新设备

新设备

图 2-1:新器件的发明促成新的设计方法和新的电子设备

�

1904 年,英国物理学家英国物理学家约翰.弗莱明(John Fleming)发明世界上第一个电子管,

图 2-2:电子管的发明和 ENIAC 计算机

人类有了电子管之后,1909 年马克尼(Guglielmo Marconi)使用它制作出世界上第一台无线

电收发报机,从此人类具有了无线远距离通信的技术特权。之后诞生的无线电收音机,使得

几乎整整一代人为之受益,人们可以迅速获知最新的消息,收听音乐,这使得 20 世纪的人

类比之前的人类更幸福。1946 年 2 月 14,美国宾夕法尼亚大学诞生了世界上第一台计算机

埃尼阿克(ENIAC:The Electronic Numerical Integrator And Calculator),ENIAC 则使用电子管

作为其主要工作器件。

1947 年 12 月,美国贝尔实验室的肖克利(Shockley,William Bradford)团队研发出基于固体

物理技术的锗半导体三极管,较之电子管,它小型化,低功耗的特性立刻引起世界的关注,

从而引发一场新的技术革命。几乎原先电子管的所有设备都可以被晶体管取代,晶体管不仅

用于通信和计算机,还用于许多控制领域。

图 2-3:贝尔实验室和肖克利的晶体管

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc