正点原子 静态时序分析与时序约束

ALIENTEK FPGA 开发板教程

FPGA 静态时序分析

与时序约束

−ALIENTEK 开拓者/新起点 FPGA开发板教程

I

�

正点原子 静态时序分析与时序约束

ALIENTEK FPGA 开发板教程

广州市星翼电子科技有限公司

淘宝店铺 1: http://eboard.taobao.com

淘宝店铺 2: http://openedv.taobao.com

技术支持论坛 (开源电子网 ):www.openedv.com

官方网站: www.alientek.com

最新资料下载链接: http://www.openedv.com/posts/list/13912.htm

E-mail: 389063473@qq.com QQ: 389063473

咨询电话: 020-38271790

传真号码 :020-36773971

团队: 正点原子团队

正点原子,做最全面 、最 优秀的嵌入式开发平台软硬件供应商。

友 情 提 示

如果您想及时免费获取“正点原子”最新资料,敬请关注正点原子

微信公众平台 ,我们将及时给您发布最新消息和重要资料。

关注方法:

(1)微信“扫一扫”,扫描右侧二维码,添加关注

(2)微信添加朋友公众号输入“正点原子”关注

(3)微信添加朋友输入“alientek_stm32”关注

II

�

第一章

正点原子 静态时序分析与时序约束

ALIENTEK FPGA 开发板教程

静态时序分析与时序约束 ............................................... 1

1.1 静态时序分析简介.................................................. 2

1.2

FPGA设计流程...................................................... 4

1.3

TimeQuest的使用................................................... 7

1.4 常用时序约束..................................................... 23

1.5 时序分析的基本概念............................................... 26

III

�

正点原子 静态时序分析与时序约束

ALIENTEK FPGA 开发板教程

第一章 静态时序分析与时序约束

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否

符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯

片的时序进行约束,然后通过时序分析工具给出时序分析结果,并根据设计者的修复使设计

完全满足时序约束的要求。

本章包括以下几个部分:

1.1 静态时序分析简介

1.2 FPGA 设计流程

1.3 TimeQuest 的使用

1.4 常用时序约束

1.5 时序分析的基本概念

1

�

正点原子 静态时序分析与时序约束

1.1 静态时序分析简介

ALIENTEK FPGA 开发板教程

静态时序分析(Static Timing Analasis,STA)用来验证电路的性能,找到时序违规路

径,并指导EDA工具对设计进行布局布线,以满足时序要求。静态时序分析的速度很快,但是

它并不对电路的功能进行验证。

时序约束(Timing Constraints)用来描述设计人员对时序的要求,比如时钟频率,输入

输出的延时等。比如,对时钟频率的约束最简单的理解就是,设计者需要告诉EDA工具设计

中所使用的时钟的频率是多少;然后工具才能按照所要求的时钟频率去优化布局布线,使设

计能够在要求的时钟频率下正常工作。

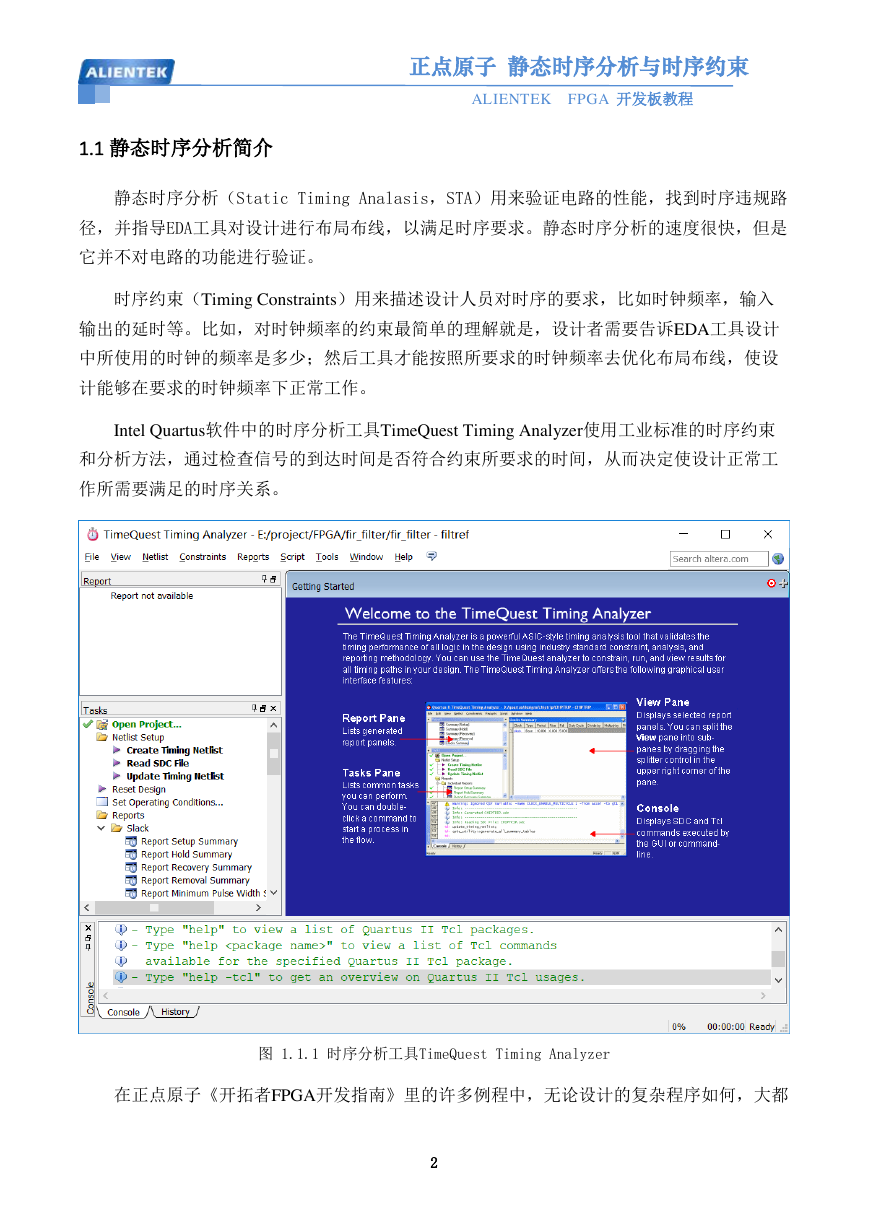

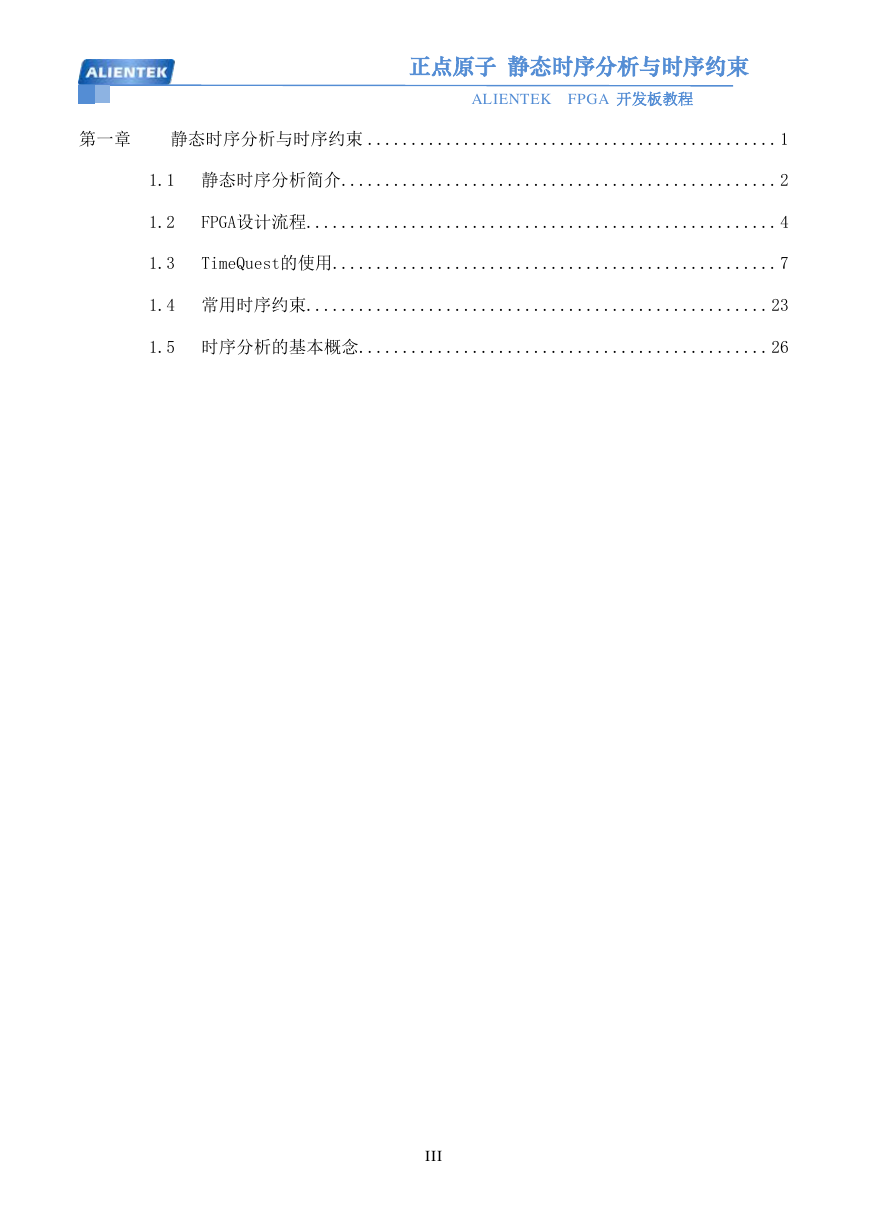

Intel Quartus软件中的时序分析工具TimeQuest Timing Analyzer使用工业标准的时序约束

和分析方法,通过检查信号的到达时间是否符合约束所要求的时间,从而决定使设计正常工

作所需要满足的时序关系。

图 1.1.1 时序分析工具TimeQuest Timing Analyzer

在正点原子《开拓者FPGA开发指南》里的许多例程中,无论设计的复杂程序如何,大都

2

�

正点原子 静态时序分析与时序约束

用到了时序约束以实现功能。如果没有给设计添加时序约束,则有可能会影响到最终的功

ALIENTEK FPGA 开发板教程

能,而且问题不容易排查。例如,在第四十八章《基于以太网的板对板音频互传实验》,未

添加时序约束之前,通过以太网传输的音频有噪声,添加时序约束后噪声消失。

在上面的例子中,由于未添加时序约束,设计所实现的功能受到了一些影响。而更为严

重的情况是,在一些设计中由于没有进行时序约束,而导致设计的功能根本无法实现。比如

第五十二章《FIR滤波器实验》中,在没进行时序约束之前,设计的低通滤波器根本无法工

作。

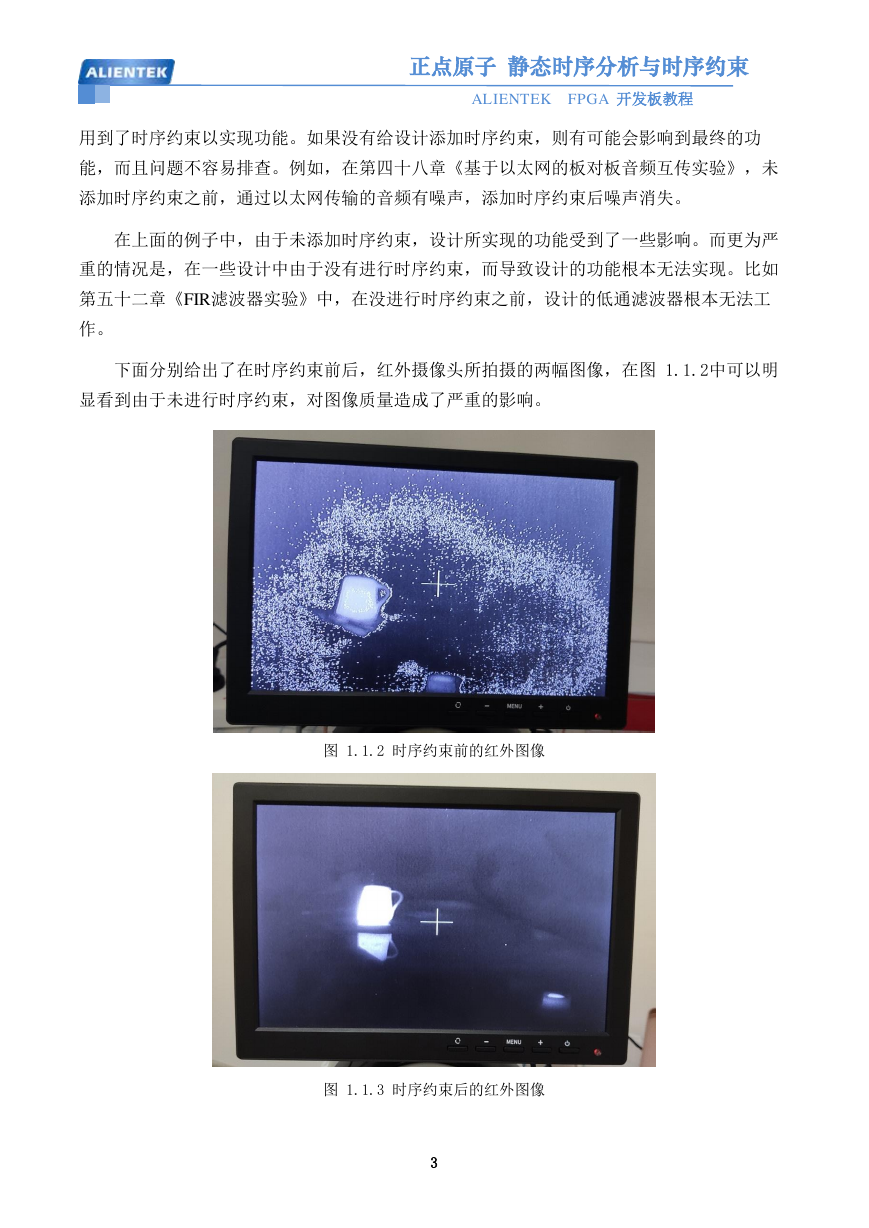

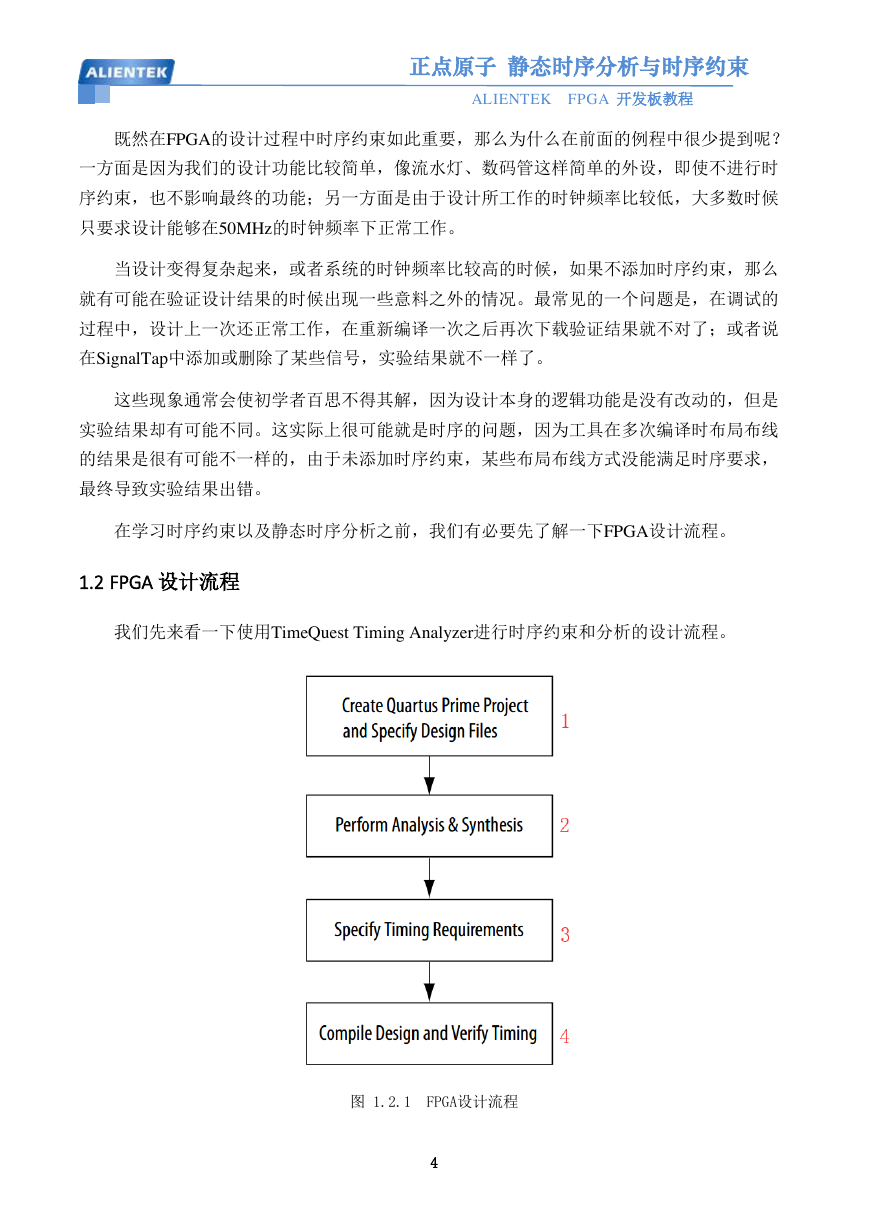

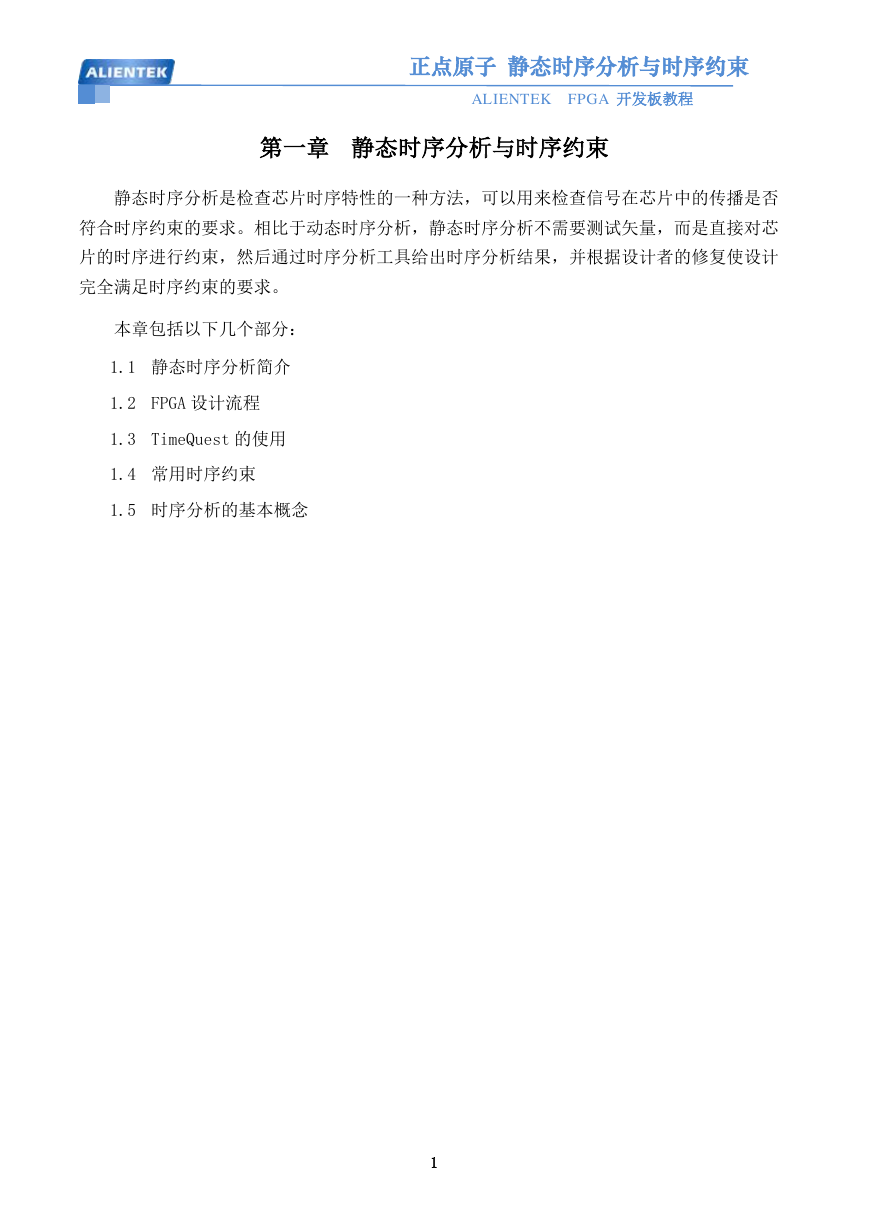

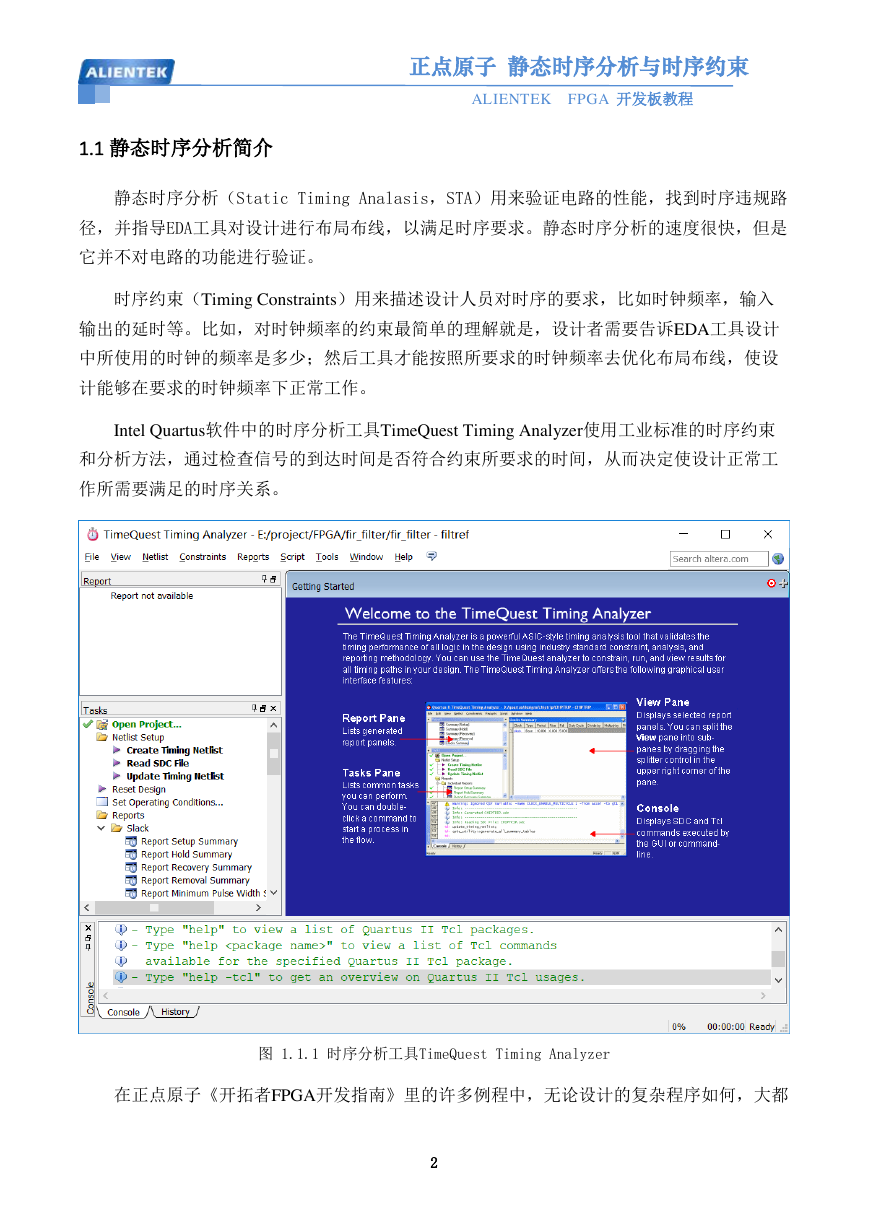

下面分别给出了在时序约束前后,红外摄像头所拍摄的两幅图像,在图 1.1.2中可以明

显看到由于未进行时序约束,对图像质量造成了严重的影响。

图 1.1.2 时序约束前的红外图像

图 1.1.3 时序约束后的红外图像

3

�

正点原子 静态时序分析与时序约束

ALIENTEK FPGA 开发板教程

既然在FPGA的设计过程中时序约束如此重要,那么为什么在前面的例程中很少提到呢?

一方面是因为我们的设计功能比较简单,像流水灯、数码管这样简单的外设,即使不进行时

序约束,也不影响最终的功能;另一方面是由于设计所工作的时钟频率比较低,大多数时候

只要求设计能够在50MHz的时钟频率下正常工作。

当设计变得复杂起来,或者系统的时钟频率比较高的时候,如果不添加时序约束,那么

就有可能在验证设计结果的时候出现一些意料之外的情况。最常见的一个问题是,在调试的

过程中,设计上一次还正常工作,在重新编译一次之后再次下载验证结果就不对了;或者说

在SignalTap中添加或删除了某些信号,实验结果就不一样了。

这些现象通常会使初学者百思不得其解,因为设计本身的逻辑功能是没有改动的,但是

实验结果却有可能不同。这实际上很可能就是时序的问题,因为工具在多次编译时布局布线

的结果是很有可能不一样的,由于未添加时序约束,某些布局布线方式没能满足时序要求,

最终导致实验结果出错。

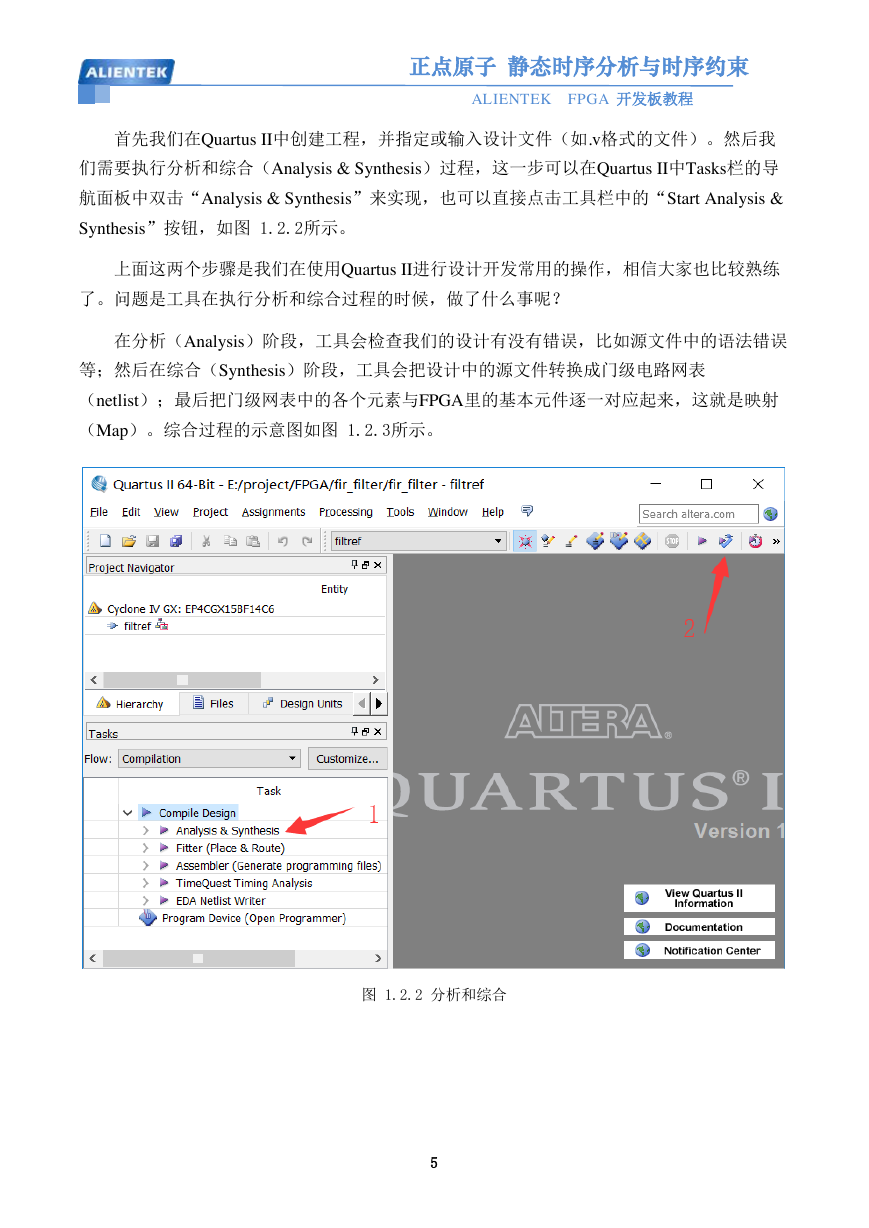

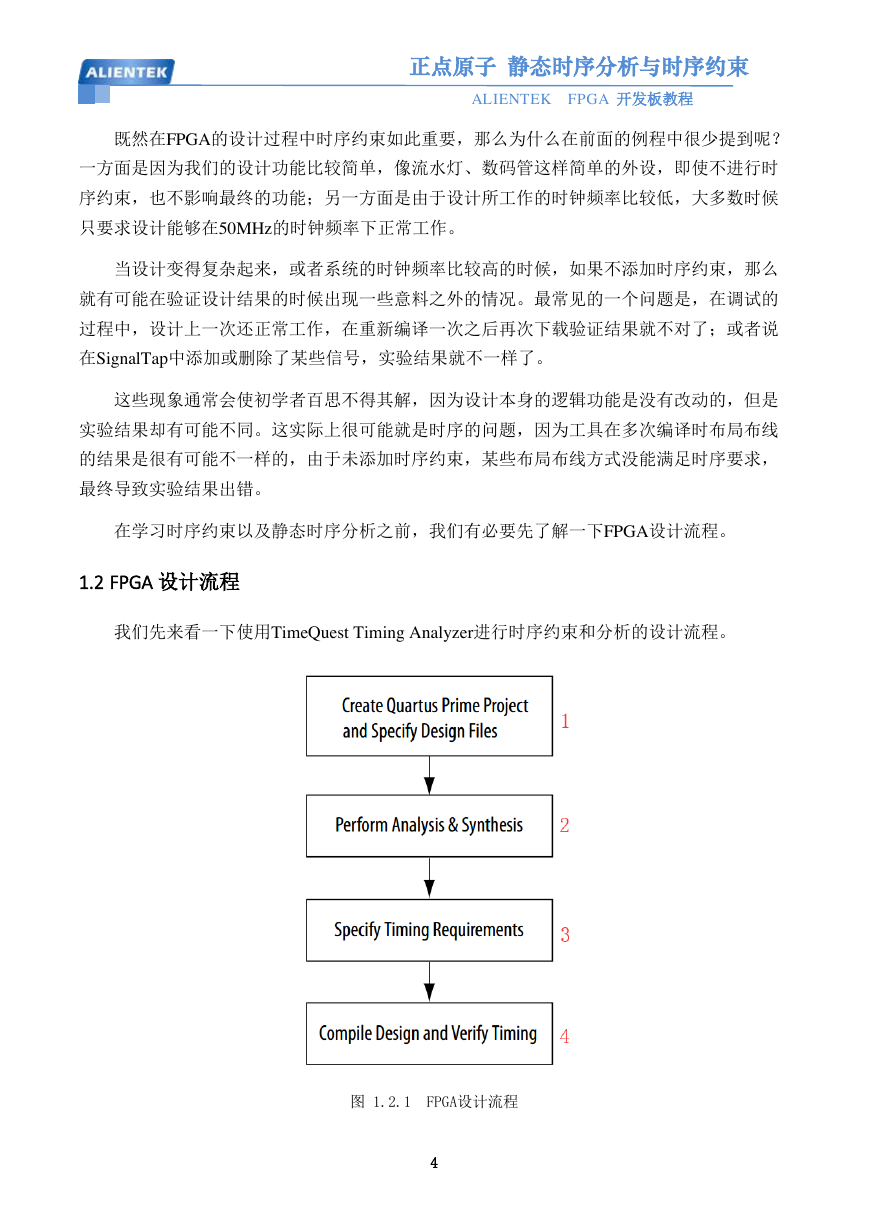

在学习时序约束以及静态时序分析之前,我们有必要先了解一下FPGA设计流程。

1.2 FPGA 设计流程

我们先来看一下使用TimeQuest Timing Analyzer进行时序约束和分析的设计流程。

图 1.2.1 FPGA设计流程

4

�

正点原子 静态时序分析与时序约束

ALIENTEK FPGA 开发板教程

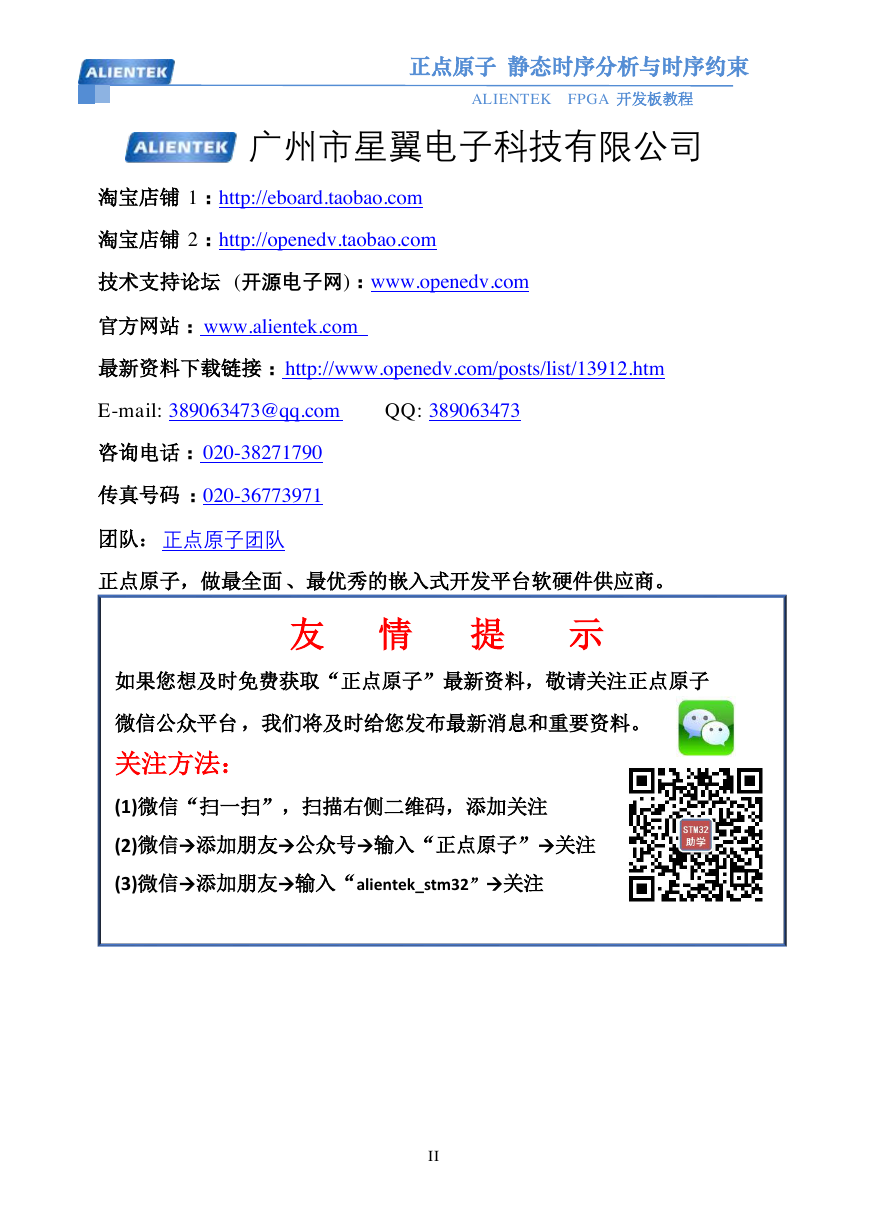

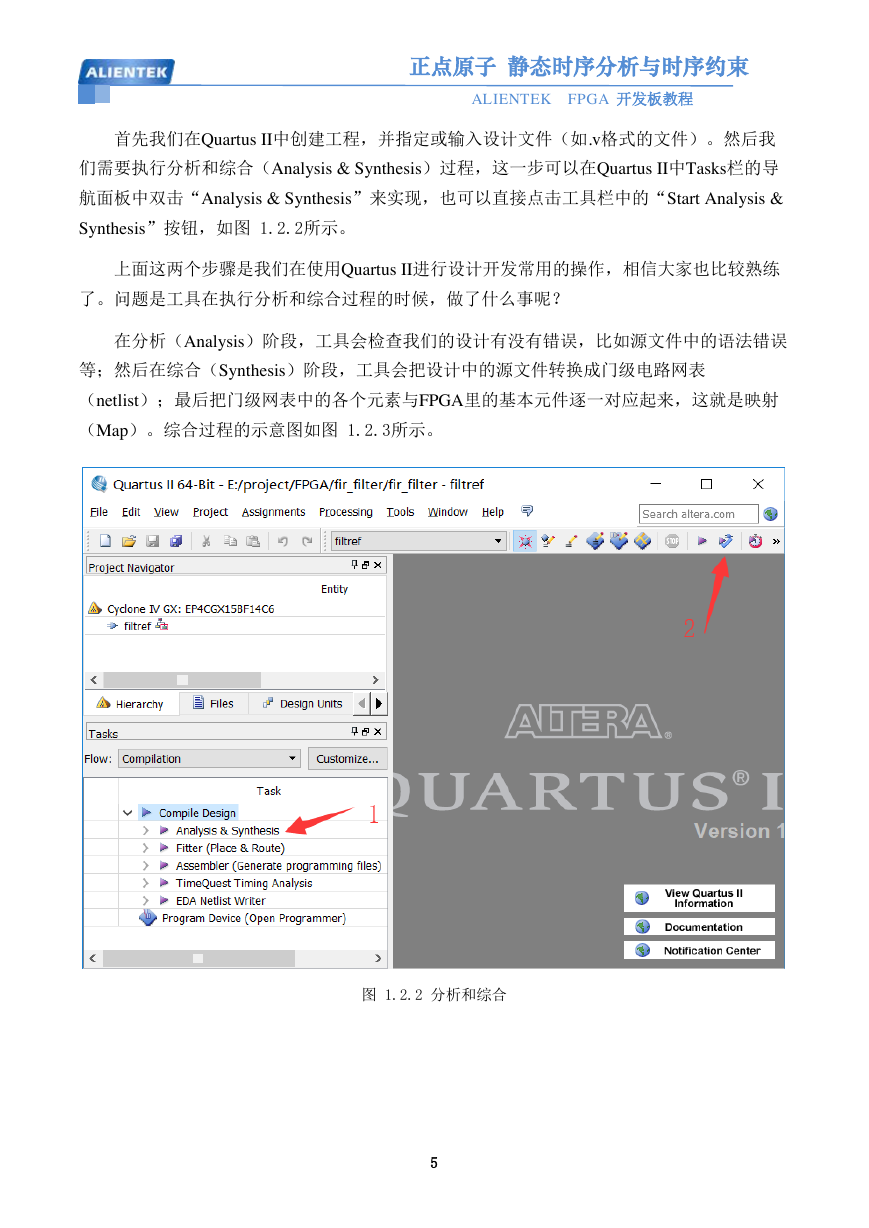

首先我们在Quartus II中创建工程,并指定或输入设计文件(如.v格式的文件)。然后我

们需要执行分析和综合(Analysis & Synthesis)过程,这一步可以在Quartus II中Tasks栏的导

航面板中双击“Analysis & Synthesis”来实现,也可以直接点击工具栏中的“Start Analysis &

Synthesis”按钮,如图 1.2.2所示。

上面这两个步骤是我们在使用Quartus II进行设计开发常用的操作,相信大家也比较熟练

了。问题是工具在执行分析和综合过程的时候,做了什么事呢?

在分析(Analysis)阶段,工具会检查我们的设计有没有错误,比如源文件中的语法错误

等;然后在综合(Synthesis)阶段,工具会把设计中的源文件转换成门级电路网表

(netlist);最后把门级网表中的各个元素与FPGA里的基本元件逐一对应起来,这就是映射

(Map)。综合过程的示意图如图 1.2.3所示。

图 1.2.2 分析和综合

5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc