网络与通信工程

Camera Link 协议和 FPGA 的数字图像信号源设计

Camer a Link 协议和 FPGA 的数字图像信号源设计

王小艳, 张会新, 孙永生, 杨 倩

( 中北大学, 山西 太原 030051)

摘要: 介绍一种基于 Camera Link 协议和 FPGA 设计数字图像信号源的方法。该设计将图像数据和接口信号转换成与

Camera Link 协议 相 匹配 的 低 压差 分 信 号( LVDS) 进 行 传 输。提 高 了 信号 的 传 输距 离 和 精度, 为 图 像数 据 采 集装 置 的

测试提供了可靠的信号源。阐述了图像信号源的设计思想与电路结构, 最后简述了在实际中的应用。该信号源已经成

功应用于某弹载地面测试系统中。

关 键 词: 图像信号源; Camera Link; FPGA

中图分类号: TN911

文献标识码: A

文章编号: 1006- 6977(2008)07- 0059- 03

Design of numer al pictur e signal sour ce based on Camer a Link

standar d and FPGA

WANG Xiao- yan, ZHANG Hui- xin, SUN Yong- sheng, YANG Qian

(North University, Taiyuan 030051, China)

Abstr act:This paper introduces a kind of method to design the numeral picture signal source,that is based on Camera Link

protocol and FPGA.The picture data and interface signal are converted to low voltage differential signaling(LVDS) matching

the Camera Link standard to transmit.This method can enhance the signal transfers distance,precision and offer the trusti-

ness signal source to picture data acquisition system.It elaborates the design and circuit structure of picture signal source.In

the end,it elaborates its actual application.This signal source has already been applied to a ground testing system.

Key wor ds: picture signal source; Camera Link; FPGA; LVDS

1 引言

目前, 各种图像设备已 广 泛 应用 到 航 空航 天 、军 事、医 疗

等领域。图像信号源作为地面图像采集装置测试系统中的一

部 分 , 其 传 输 方 式 及 信 号 精 度 都 是 影 响 系 统 性 能 的 重 要 因

素。由于图像信号的传输速率高, 数 据 量大, 在 传 输过 程 中,

其精度和传输距离易受影响。为了提高信号传输距离和精度

设计 了 由 FPGA 内 部 发 出图 像 数 据, 并 通 过 FPGA 进 行 整 体

时序控制; 输出接口信号转换成符合 Camera Link 标 准的 低

电 压差 分 信 号( LVDS) 进 行 传 输。该 图 像 信号 源 已 成 功 应 用

于某弹载记录器的地面测试台系统中。

2 Camer a Link 接口及图像数据接口信号

Camera Link 标准 是 由国 家 半 导 体 实 验 室(National Semi-

conductor)提出的一种 Channel Link 技 术 标准 发 展 而来 的, 该

接口具有开放式的接口协议, 使得 不 同 厂家 既 能 保持 产 品 的

差异 性, 又能 互 相 兼容 。它 在 传统 LVDS 传 输 数 据 的 基 础 上

又加载了并转串发送器和串转并 接收 器, 可 在并 行 组 合的 单

向 链 路 、串 行 链 路 和 点 对 点 链 路 上 , 利 用 SER/DES( 串 行 化/

解 串 行 化 ) 技 术 以 高 达 4.8 Gb/s 的 速 度 发 送 数 据 。Camera

Link 标准 使 用 每条 链 路 需两 根 导 线的 LVDS 传 输 技 术 [1]。 驱

动器接收 28 个单端 数 据 信号 和 1 个 时钟 信 号, 这些 信 号 以

7: 1 的比例被串行发送, 也就是 5 对 LVDS 信 号 通 道上 分 别

传输 4 组 LVDS 数 据流 和 1 组 LVDS 时钟 信 号,即完 成 28 位

数据的同步传输只需 5 对线, 而且在多通道 66 MHz 像素时

钟频率下传输距离可达 6 m。

Camera Link 是 在 Channel Link 的 基 础 上 增 加 了 一 些 相

机控制信号和串行通信信号, 定 义 出 标准 的 接 头也 就 是 标准

化信号线, 让 Camera 及 影 像卡 的 信 号传 输 更 简单 化, 同 时提

供 基 本 架 构(Base Configuration)、中 阶 架 构(Medium Configura-

tion)及 完 整 架 构(Full Configuration) 三 种 [2]: 基 本 架 构 属 单 一

Camera Link 元件, 为单一接头; 中阶架构属双组 Camera Link

元 件 , 为 双 组 接 头 ; 完 整 架 构 属 三 组 Camera Link 元 件 , 为 三

组接头。

传输数据时使用的视频同步信号固定不变, 分别为:

帧 同 步 信 号 FVAL:当 FVAL 为 高 电 平 时 , 正 输 出 一 帧 有

效 数 据 ; 行 同 步 信 号 LVAL:当 LVAL 为 高 电 平 时 , 正 输 出 一

个有效像元行( 在两个有效像元行中间, LVAL 会跳过几 个无

收稿日期: 2008- 05- 19

作者简介: 王小艳( 1983- ) , 女, 硕士研究生。研究方向: 微系统及集成技术。

稿件编号: 200805014

- 59-

�

《国外电子元器件》2008 年第 7 期

效的 像 素 点, 可 在 实 际应 用 时 设定 跳 过 的像 素 点 数 [3]) ; 数 据

有效信号 DVAL:当 FVAL 和 LVAL 为 高 时, DVAL 为高 电 平,

正输出有效的数据; SPARE 为备用信号。

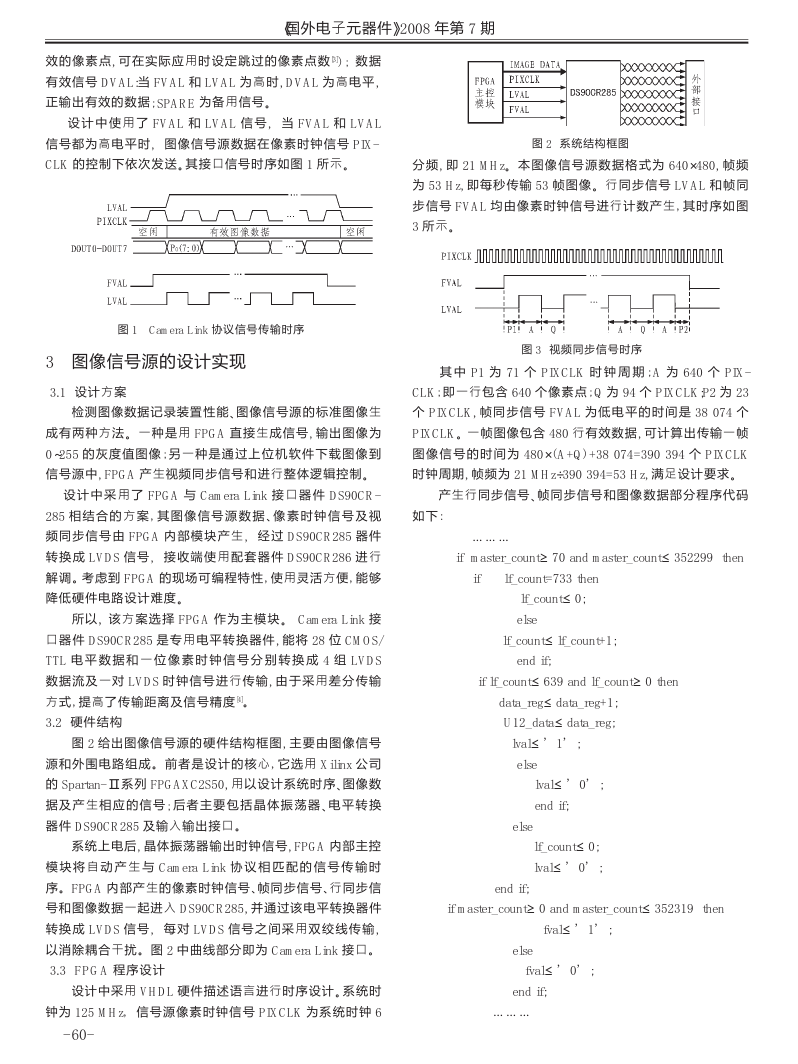

设 计 中 使 用 了 FVAL 和 LVAL 信 号 , 当 FVAL 和 LVAL

信号都为高 电平 时, 图 像信 号 源 数据 在 像 素时 钟 信 号 PIX-

CLK 的控制下依次发送。其接口信号时序如图 1 所示。

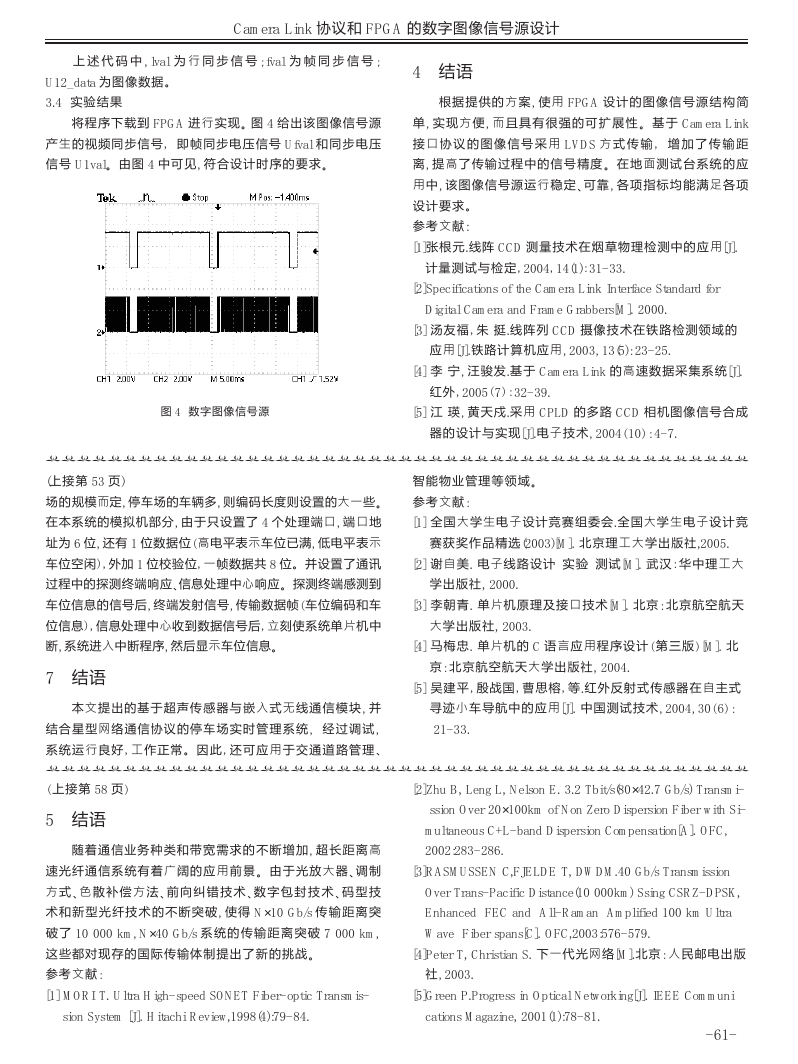

图 2 系统结构框图

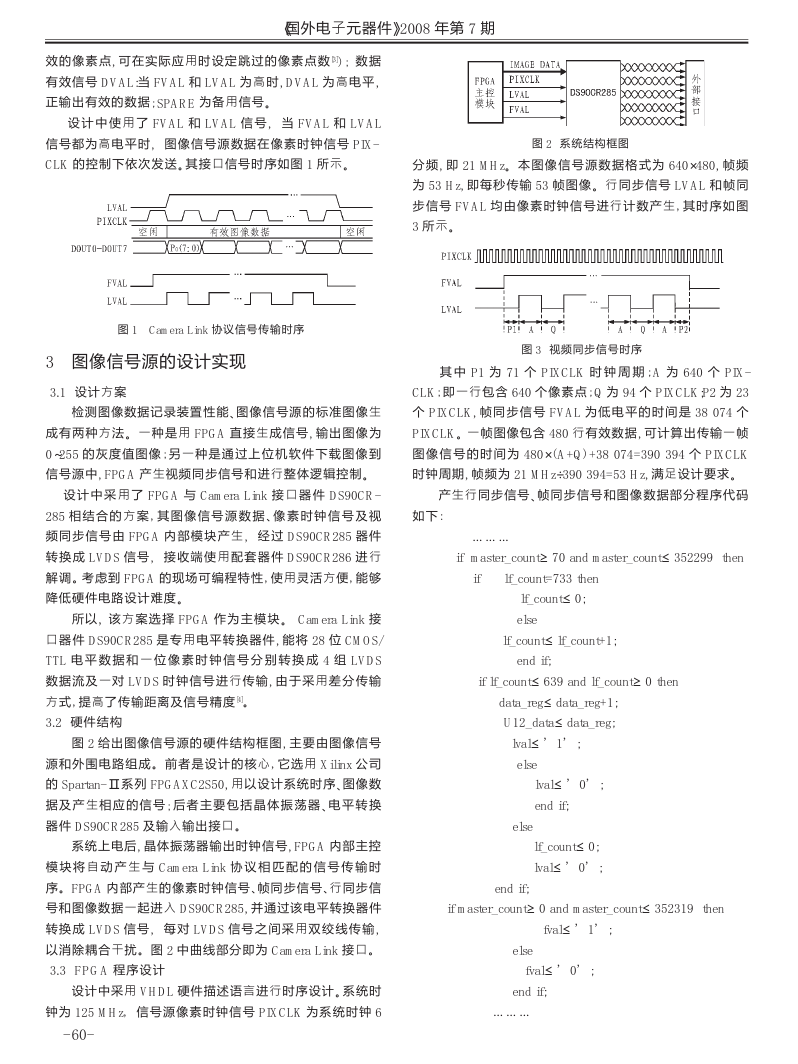

分 频 , 即 21 MHz。 本 图 像 信 号 源 数 据 格 式 为 640×480, 帧 频

为 53 Hz, 即每秒传输 53 帧 图 像。行 同 步 信号 LVAL 和 帧 同

步 信 号 FVAL 均由 像 素 时钟 信 号 进行 计 数 产生, 其 时 序 如 图

3 所示。

图 1 Camera Link 协议信号传输时序

3 图像信号源的设计实现

3.1 设计方案

检测图像数据记录装置 性 能、图 像 信 号源 的 标 准图 像 生

成有 两 种 方法 。一 种 是用 FPGA 直 接 生成 信 号, 输出 图 像 为

0~255 的 灰 度 值图 像; 另 一种 是 通 过上 位 机 软 件 下 载 图 像 到

信号源中, FPGA 产生视频同步信号和进行整体逻辑控制。

设 计 中 采 用 了 FPGA 与 Camera Link 接 口 器 件 DS90CR-

285 相 结 合 的 方 案 , 其 图 像 信 号 源 数 据 、像 素 时 钟 信 号 及 视

频 同 步信 号 由 FPGA 内 部 模 块 产 生 , 经 过 DS90CR285 器 件

转 换 成 LVDS 信 号 , 接 收 端 使 用 配 套 器 件 DS90CR286 进 行

解调。考虑到 FPGA 的现场可编程特性, 使用灵活方便, 能够

降低硬件电路设计难度。

所以, 该 方 案 选 择 FPGA 作 为 主 模 块 。 Camera Link 接

口 器 件 DS90CR285 是 专 用 电平 转 换 器件, 能 将 28 位 CMOS/

TTL 电 平 数 据 和 一 位 像 素 时 钟 信 号 分 别 转 换 成 4 组 LVDS

数据 流 及 一对 LVDS 时 钟 信号 进 行 传输, 由 于 采用 差 分 传 输

方式, 提高了传输距离及信号精度[4]。

3.2 硬件结构

图 2 给出图像信号源的 硬 件 结构 框 图, 主要 由 图 像信 号

源和外 围 电 路组 成 。前 者是 设 计 的核 心, 它 选用 Xilinx 公 司

的 Spartan- Ⅱ系列 FPGAXC2S50, 用以设计系统时序、图像数

据 及 产 生 相 应 的 信 号 ; 后 者 主 要 包 括 晶 体 振 荡 器 、电 平 转 换

器件 DS90CR285 及输入输出接口。

系统上电后, 晶体振荡器输出时钟信号, FPGA 内部主控

模 块 将 自 动 产 生 与 Camera Link 协 议 相 匹 配 的 信 号 传 输 时

序。FPGA 内部产生的像素时钟信号、帧同步信号、行同步信

号和图像数据一起进入 DS90CR285, 并通过该电平转换器件

转 换 成 LVDS 信 号 , 每 对 LVDS 信 号 之 间 采 用 双 绞 线 传 输 ,

以消除耦合干扰。图 2 中曲线部分即为 Camera Link 接口。

3.3 FPGA 程序设计

设计中采用 VHDL 硬件描述语言进行时序设计。系统时

钟为 125 MHz, 信 号源 像 素 时钟 信 号 PIXCLK 为系 统 时 钟 6

- 60-

图 3 视频同步信号时序

其 中 P1 为 71 个 PIXCLK 时 钟 周 期 ; A 为 640 个 PIX-

CLK; 即一行包 含 640 个 像素 点; Q 为 94 个 PIXCLK;P2 为 23

个 PIXCLK, 帧 同 步 信 号 FVAL 为 低 电 平 的 时 间 是 38 074 个

PIXCLK。一帧图像包含 480 行有效数据, 可计算出传输一帧

图 像 信 号 的 时 间 为 480×( A+Q) +38 074=390 394 个 PIXCLK

时钟周期, 帧频为 21 MHz÷390 394=53 Hz, 满足设计要求。

产生行同步信号 、帧 同步 信 号 和图 像 数 据部 分 程 序代 码

如下:

………

if master_count≥70 and master_count≤352299 then

if

lf_count=733 then

lf_count≤0;

else

lf_count≤lf_count+1;

end if;

if lf_count≤639 and lf_count≥0 then

data_reg≤data_reg+1;

U12_data≤data_reg;

lval≤' 1'

else

;

else

lval≤' 0'

end if;

;

lf_count≤0;

lval≤' 0'

;

end if;

if master_count≥0 and master_count≤352319 then

fval≤' 1'

;

else

fval≤' 0'

;

end if;

………

�

Camera Link 协议和 FPGA 的数字图像信号源设计

上 述 代 码 中 , lval 为 行 同 步 信 号 ; fval 为 帧 同 步 信 号 ;

U12_data 为图像数据。

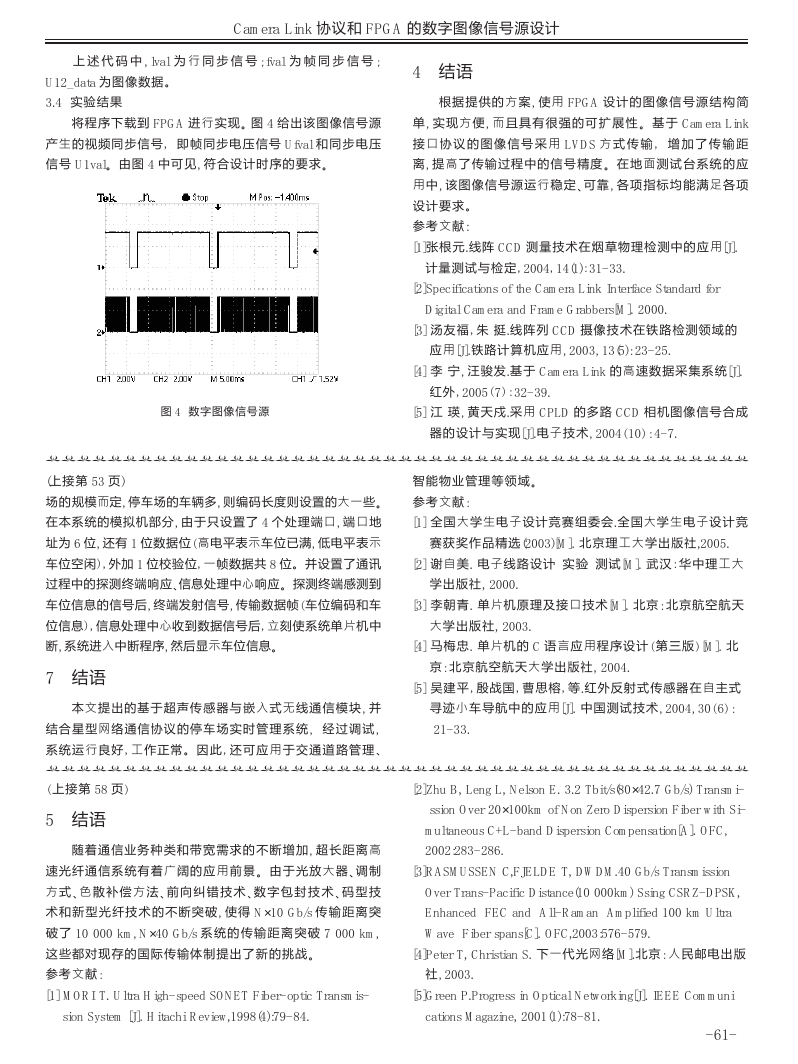

3.4 实验结果

将程序下载到 FPGA 进行实现。图 4 给出该图像信号源

产生的视频同步信号, 即帧同步电压信号 Ufval 和 同 步 电压

信号 U1val。由图 4 中可见, 符合设计时序的要求。

4 结语

根据 提 供的 方 案, 使用 FPGA 设 计 的图 像 信 号 源 结 构 简

单, 实 现 方便, 而 且 具有 很 强 的可 扩 展 性 。 基 于 Camera Link

接 口 协 议 的 图 像 信 号 采 用 LVDS 方 式 传 输 , 增 加 了 传 输 距

离, 提高了传输过程中的 信 号 精度 。在 地 面测 试 台 系统 的 应

用中, 该图像信号源运行稳 定 、可靠, 各 项 指标 均 能 满足 各 项

设计要求。

参考文献:

[1]张根元.线阵 CCD 测量技术在烟草物理检测中的应用[J].

计量测试与检定, 2004, 14(1): 31- 33.

[2]Specifications of the Camera Link Interface Standard for

Digital Camera and Frame Grabbers[M]. 2000.

[3] 汤友福, 朱 挺.线阵列 CCD 摄像技术在铁路检测领域的

应用[J].铁路计算机应用, 2003, 13(5): 23- 25.

[4] 李 宁, 汪骏发.基于 Camera Link 的高速数据采集系统[J].

红外, 2005( 7) : 32- 39.

图 4 数字图像信号源

[5] 江 瑛, 黄天戍.采用 CPLD 的多路 CCD 相机图像信号合成

器的设计与实现[J].电子技术, 2004( 10) : 4- 7.

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

(上接第 53 页)

场的规模而定, 停车场的车辆多, 则编码长度则设置的大一些。

在本系统的模拟机部分, 由于只设置了 4 个处理端口, 端口地

址为 6 位, 还有 1 位数据位( 高电平表示车位已满, 低电平表示

车位空闲) , 外加 1 位校验位, 一帧数据共 8 位。并设置了通讯

智能物业管理等领域。

参考文献:

[1] 全国大学生电子设计竞赛组委会.全国大学生电子设计竞

[2] 谢自美. 电子线路设计·实验·测试[M]. 武汉: 华中理工大

赛获奖作品精选(2003)[M]. 北京理工大学出版社,2005.

过程中的探测终端响应、信息处理中心响应。探测终端感测到

车位信息的信号后, 终端发射信号, 传输数据帧( 车位编码和车

学出版社, 2000.

[3] 李朝青. 单片机原理及接口技术[M]. 北京: 北京航空航天

位信息) , 信息处理中心收到数据信号后, 立刻使系统单片机中

大学出版社, 2003.

断, 系统进入中断程序, 然后显示车位信息。

[4] 马梅忠. 单片机的 C 语言应用程序设计( 第三版) [M]. 北

7 结语

本文提出的基于超声传 感 器与 嵌 入 式无 线 通 信模 块, 并

结合星型网络通信协议的停车场 实 时 管理 系 统, 经过 调 试,

系统运行良好, 工作正常。因 此, 还可 应 用 于交 通 道 路管 理 、

京: 北京航空航天大学出版社, 2004.

[5] 吴建平, 殷战国, 曹思榕, 等.红外反射式传感器在自主式

寻迹小车导航中的应用[J]. 中国测试技术, 2004, 30( 6) :

21- 33.

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

[2]Zhu B, Leng L, Nelson E. 3.2 Tbit/s(80×42.7 Gb/s) Transmi-

( 上接第 58 页)

ssion Over 20×100km of Non Zero Dispersion Fiber with Si-

multaneous C+L- band Dispersion Compensation[A]. OFC,

2002:283- 286.

随着通信业务种类和带 宽 需求 的 不 断增 加, 超 长距 离 高

5 结语

速光纤通信系统有着广阔的应用 前 景 。由于 光 放 大器 、调 制

[3]RASMUSSEN C,FJELDE T, DWDM.40 Gb/s Transmission

方 式 、色 散 补 偿 方 法 、前 向 纠 错 技 术 、数 字 包 封 技 术 、码 型 技

术 和新 型 光 纤技 术 的 不断 突 破, 使得 N×10 Gb/s 传 输 距 离 突

破 了 10 000 km, N×40 Gb/s 系 统 的 传 输 距 离 突 破 7 000 km,

这些都对现存的国际传输体制提出了新的挑战。

参考文献:

[1] MORI T. Ultra High- speed SONET Fiber- optic Transmis-

Over Trans- Pacific Distance(10 000km) Ssing CSRZ- DPSK,

Enhanced FEC and All- Raman Amplified 100 km Ultra

Wave Fiber spans[C]. OFC,2003:576- 579.

[4]Peter T, Christian S. 下一代光网络[M].北京: 人民邮电出版

社, 2003.

[5]Green P.Progress in Optical Networking[J]. IEEE Communi

sion System [J]. Hitachi Review,1998(4):79- 84.

cations Magazine, 2001(1):78- 81.

- 61-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc