Verilog 作业

姓名:zzz

班級: zzzz

學號:zzzz

報告日期:2010年10月30日

�

作业

题目要求:实现 8 位的并行数据转换为串行的数据。

题目分析:并行转串行,只要把每个输入按从高到低的顺序输出即可。即每个时

钟脉冲输出一个数据。但是下面的代码有一个的问题,不能解决在 8 为数据串行

输出的过程当中如果又有一个并行的输入数据输入,没有做到缓冲处理。也许这

个缓冲处理可以在调用此模块时在外部实现吧。

功能代码:

module para_to_serial_8bit(para_in,clock,reset,ser_out);

para_in;

input [7:0]

input reset,clock;

output

ser_out;

reg ser_out;

reg [7:0] data;

always@(posedge clock or negedge reset) begin

if(~reset)

begin

ser_out <= 1'b0;

data <= para_in;

begin

end

else

data <= {data[6:0],data[7]};

ser_out <= data[7];

end

end

endmodule

测试代码:

module test_para_to_ser;

reg [7:0] para_in;

reg clock,reset;

wire out;

para_to_serial_8bit f1(.para_in(para_in),.clock(clock),.reset(reset),.ser_out(out));

initial

$monitor($time,"in_8bit = %b,reset= %b,ser_out= %b,data=%b",para_in,reset,out,f1.data);

initial begin

clock = 1'b0;

reset = 1'b0;

#3 reset = 1'b1;

#300 $stop;

end

�

initial

para_in = 8'b1010_0100;

always

#5clock = ~clock;

endmodule

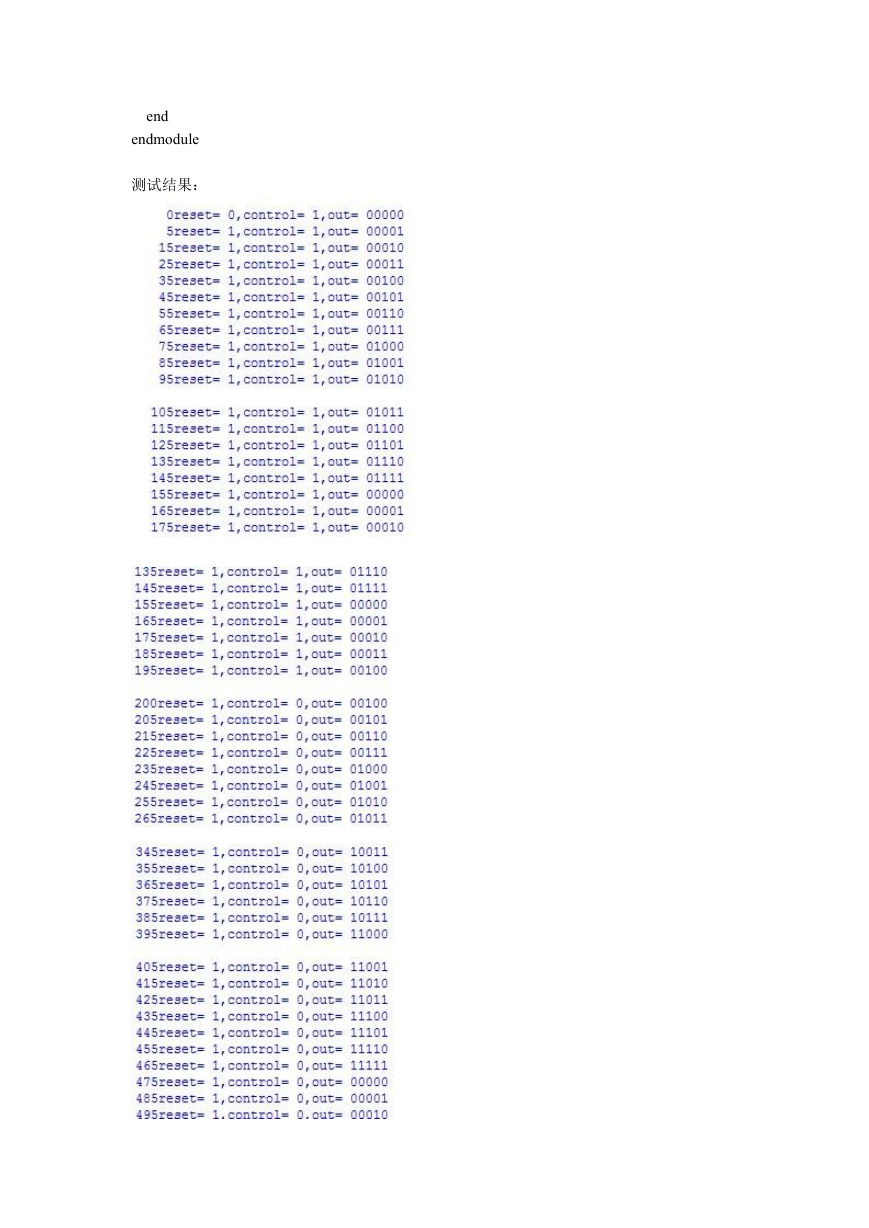

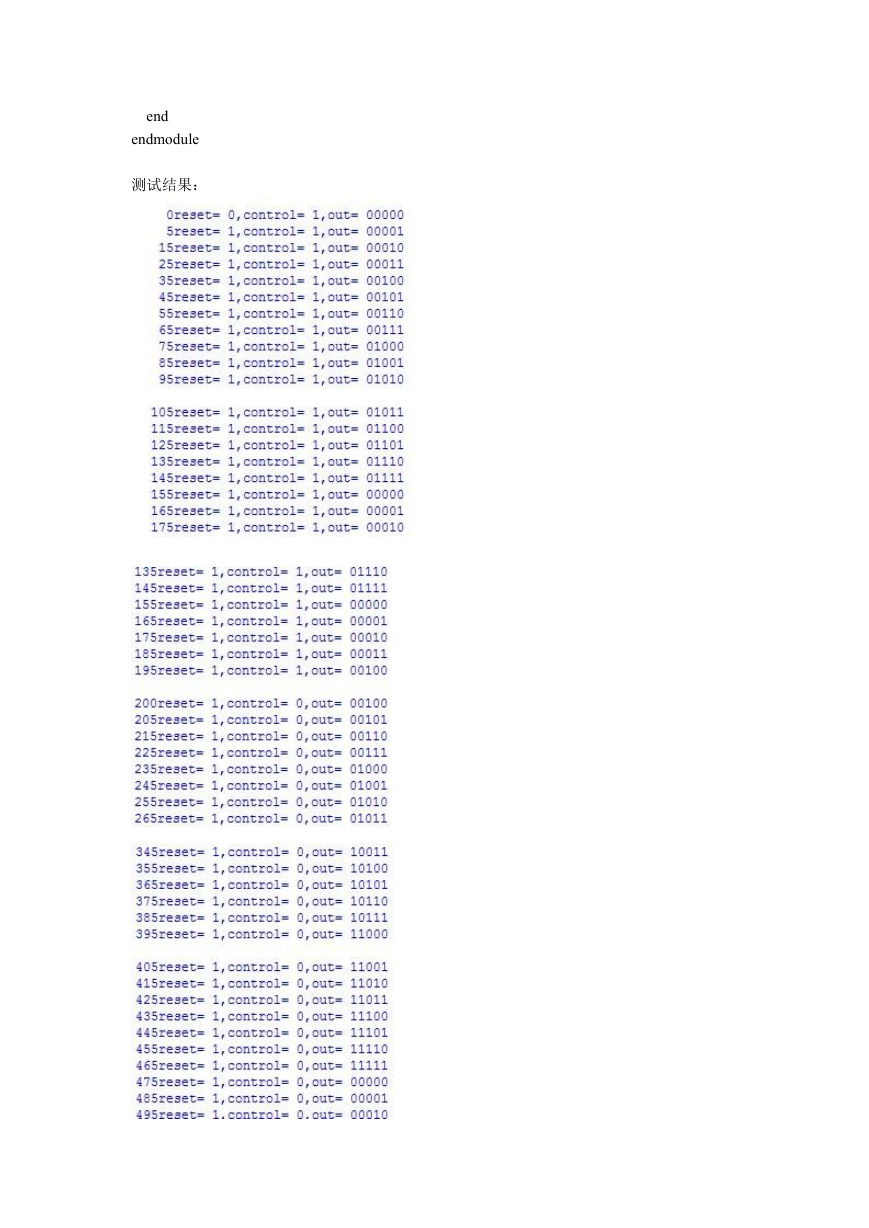

测试结果:

测试波形如下:

�

题目要求:实现 8 位的串行数据转换为并行的数据。

作业二

题目分析:8 位串行数据转换为并行数据,需要一个模为 8 的计数器,当计到 8

个时钟脉冲时,把之前的 8 个数据全部输出,然后从新接收。

功能模块代码:

模 8 计数器:

module counter_mod_8(clock,reset,Q);

//posedge effective

input clock;

input reset; // negedge effective

output [2:0] Q;

reg [2:0] Q;

always@(posedge clock or negedge reset) begin

if(~reset)

Q <= 3'd0;

else

Q <= Q + 1;

end

endmodule

串转并模块:

module ser_to_par_8bit(ser_in,clk,rst,out);

input ser_in,clk,rst;

output [7:0] out;

wire [7:0]

reg

[7:0]

wire [2:0]

out;

par_out;

count;

counter_mod_8 f1(.clock(clk),.reset(rst),.Q(count));

always@(posedge clk or negedge rst) begin

if(~rst)

par_out <= 8'b0000_0000;

else begin

par_out <= {par_out[6:0],ser_in};

end

end

assign out = (count == 7)? par_out : 8'b0000_0000;

endmodule

�

测试模块代码:

module test_ser_par;

reg [7:0] data;

wire data_in;

reg clock, reset;

wire [7:0] out;

initial begin

clock = 1'b0;

reset = 1'b0;

#3 reset = 1'b1;

data = 8'b1001_1101;

#300 $stop;

end

always

#5clock = ~clock;

always@(posedge clock)

data ={data[6:0],data[7]};

assign data_in = data[7];

ser_to_par_8bit a(.ser_in(data_in),.clk(clock),.rst(reset),.out(out));

initial

$monitor($time,"reset= %b,data= %b,data_in= %b,out= %b",reset,data,data_in,out);

endmodule

�

测试结果:

测试波形:

�

作业三

题目:可变模计数器,当控制信号为 1 时,模值为 16,当控制信号为 0 是模值

为 32。

功能模块代码:

// contr = 1 mod =16; contr =0 mod =32

module count_mod_chg(clk,reset,contr,Q);

input clk,reset,contr;

output [4:0] Q;

reg

wire

[4:0] Q;

[4:0] last;

last =(contr ? 5'b01111:5'b11111);

assign

always@(posedge clk or negedge reset) begin

if(~reset || Q == last)

Q <= 5'b00000;

else

Q = Q + 1;

end

endmodule

测试模块代码:

module test_count_mod_chg;

clock,reset;

reg

control;

reg

wire [4:0] out;

count_mod_chg counter1(.clk(clock),.reset(reset),.contr(control),.Q(out));

initial

$monitor($time,"reset= %b,control= %b,out= %b",reset,control,out);

initial

begin

clock = 1'b0;

forever #5 clock = ~clock;

end

initial begin

reset = 1'b0;

#5reset = 1'b1;

end

initial begin

control = 1;

#200 control = 0;

�

end

endmodule

测试结果:

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc