Cortex‐M3 权威指南

初稿

前置

Cortex-M3 权威指南

Joseph Yiu 著

宋岩 译

‐ 1 ‐

�

Cortex‐M3 权威指南

初稿

前置

译序

我接触 ARM 的历史约 4 年,早期是很欣赏这类处理器,到了后来切身使用它们的机会

越来越多,慢慢地有了感觉,也更加喜欢了。在偶然听说 Cortex‐M3 后,我就冥冥地感到它

不寻常。只是因为其它工作一直没有去了解它,直到今年初才进一步学习,很快就觉得相知

恨晚。当时只能看 ARM 官方的重量级资料,在看到这本书的英文原稿后,更感觉被电到了

一样,于是突然有了把它翻译成中文的冲动。经过累计约 150 个小时的奋战,终于有了此译

稿。在翻译过程中,我始终采用下列指导思想:

1. 尽量使用短句,并且把句子口语化。我认为高深的道理不一定要用高级的语法句型才能

表达。想想看,即使是几位博士互相聊天讨论一个课题,也还是使用口语吧,而且火花

往往就是在这种讨论中产生呢!

2. 多用修辞方法,并且常常引用表现力强的词汇——甚至包括网络用语和脍炙人口的歌词。

另外,有时会加工句子,使得风格像是对话。这样做的目的是整个文风更鲜活——有点

像为写出高分作文而努力的样子。这点可能与很多学术著作的“严肃、平实”文风不同,

也是一次大胆的尝试。还希望读者不吝给予反馈。

3. 在“宏观”上直译,在“微观”上意译。英语不仅单一句子的语法和汉语不同,并且句

子的连贯方式也与汉语不同。因此在十几个到几十个单词的范围内,我先把它们翻译成

脑子里的“中间语言”,再把中间语言翻译成汉语。这样,就最大地避免了贻笑大方的

“英式汉语”。

4. 有些术语名词不方便翻译成汉语,或者目前的翻译方式不统一,或者与其它术语翻译的

结果很接近,如 error 和 fault,就只能用英语意会。此时我就保留英文单词,相信这样

比硬生生地翻译成汉语还好。这些词汇主要是:retarget, fault, region 等。另外,英文中有

一个很能精练表达“两者都”意思的单词及其用法:”both”,我也常常保留之。

5. 图表对颜色的使用比较丰满,尤其是比较大型的插图,相信这样能帮助读者分析和理解。

插图是从原图直接复制的,因此矢量图变成了位图,无法再适应任何比例的缩放。不过,

我在复制原图时,把原图以 200%的比例放大,从而提高了图片的质量。

6. 我在很多地方加了译注。比较短的译注就直接以“()”加在文字后面。比较长的译注则

为它开出一个“文字池”,放到相应的“.text”后面并与之相临。早期的译注多用于解释

一些不是很广为人知的术语,后期的译注则更多是我认为有必要补充的内容,包括读者

在阅读过程中可能会产生的问题,容易混淆的概念,深入理解等。

7. 我对少量自然段作了改编。也有个别部分译自 ARM 提供的权威文档。

本书的翻译工作在 40%进度的时候是最困难的时期,有一种好像长跑中遇到了所谓“极

限”的感觉。望着距离掉下去还有那么高的滚动条,甚至都有停住的自我暗示了。那天刚好

是哀悼日的第一天,我本来情绪很低沉,但在我看到默哀完毕,天安门广场上排山倒海般地

呐喊“中国加油”时,我突然有了强烈的共振感觉,那是一种热泪盈眶的激动和感叹,甚至

觉得他们就是在鼓励我!让我一下子振作起来,找回了比刚开始还要强烈的干劲,并且更加

信心满满。这种精神力量一直推动我翻译完最后一个字,并且还有“余勇可贾”的快感^_^

整个翻译的时间跨度是在 2008.05.10‐2008.06.07,共计 28 天。不知这是否算得上很“仓

促”。想必有很多句式还能改得更好,甚至还有错别字等低级错误。我使用了五笔输入法,

可能错别字会错得很离奇,不过肯定逃不过读者雪亮的双眼的。希望读者在发现错误后批评

指正。反馈地址是:rock.song@hotmail.com,也可以通过QQ:9471202/9312500。

本译稿草稿完成后,我交给几位好友去试读和审校,得以揪出了很多大大小小的 bugs。

他们是:浮云,土豆波,美眉 Y 和小胖,在这里以点名表示感谢!

宋 岩 2008.07.02

‐ 2 ‐

�

Cortex‐M3 权威指南

初稿

前置

原作序

谁是最节能,最擅长把好钢用在刀刃上的人?要让我说,我一定得表一表单片机

的开发者。他们使出浑身解术,写出精妙玲珑的代码,把单片机点点滴滴的力量汇集起

来,让它如同涌泉一般尽情地迸发,灌溉滋养着各行各业。是什么灵丹妙药赐予了他们

这么神奇力量?除了好的处理器之外,还要配合好的开发环境和工具链。也正出于此,

在设计ARM7TDMI处理器时,ARM的工具链工程师们和CPU设计师们强强联手,为了

让它的内部结构更优化、更精练、更到位而并肩奋战了很多日日夜夜,终于有了

ARM7TDMI的无限辉煌,并且久经岁月的洗礼依旧光芒绽放。

珠联璧合的最新果实,是破茧而出的ARM Cortex-M3处理器。这个小尤物,处处

闪耀着ARM体系结构激动人心的新突破。它基于最新最好的32位ARMv7架构——这个

架构支持高度成功的Thumb-2指令集,还有很多时尚、前卫甚至崭新的特性,充满了

新生代的气息。它在很好、很强大的同时,编程模型却变得更加清新爽洁了。不管你是

祖国的花朵、是人民教师、还是精明的商人,也无所谓是新手还是骨灰级玩家,

Cortex-M3都将尽情展现它的秀外慧中,带给你喜出望外的收获和“激活”!

ARM嵌入式解决方案主任

Wayne Lyons

‐ 3 ‐

�

Cortex‐M3 权威指南

初稿

前置

前 言

不管你是做软件的还是做硬件的,只要相中了ARM的Cortex‐M3处理器,这本

书就是为你而写。以前Cortex‐M3的资料只有两个大部头,分别是:

《Cortex‐M3技术参考手册》(Cortex‐M3 Technical Reference Manual, 简

称Cortex‐M3 TRM)

《ARMv7‐M应用程序级架构参考手册》(ARMv7‐M Application Level

Architecture Reference Manual)

虽然这它俩差不多是权威到“古文观止”级的,但实在是太深入了,以致于对

新手来说那简直就是天书。本书则是一个精简版,并且叙述的前后更有条理。目

标读者包括:一线程序员,嵌入式产品设计师,片上系统(SoC)工程师,嵌入

式系统发烧友,学院研究员,还包括所有涉猎过单片机和微处理器领域,慧眼识

珍看中了Cortex‐M3的人民大众们。

本书要给Cortex‐M3的架构做一个简介,浏览一下指令系统,写几个段代码练

练手,说一些硬件特性,再表一表该处理器精深的调试系统。本书还给出了应用

程序范例,手把手地教你使用开发工具,包括ARM的工具和GNU的工具链。如果

你以前是ARM7TDMI的玩家,正准备着升级装备到Cortex‐M3,本书也非常解渴,

里面讲述了两者的不同,以及鸟枪换炮的升级过程。

‐ 4 ‐

�

Cortex‐M3 权威指南

初稿

前置

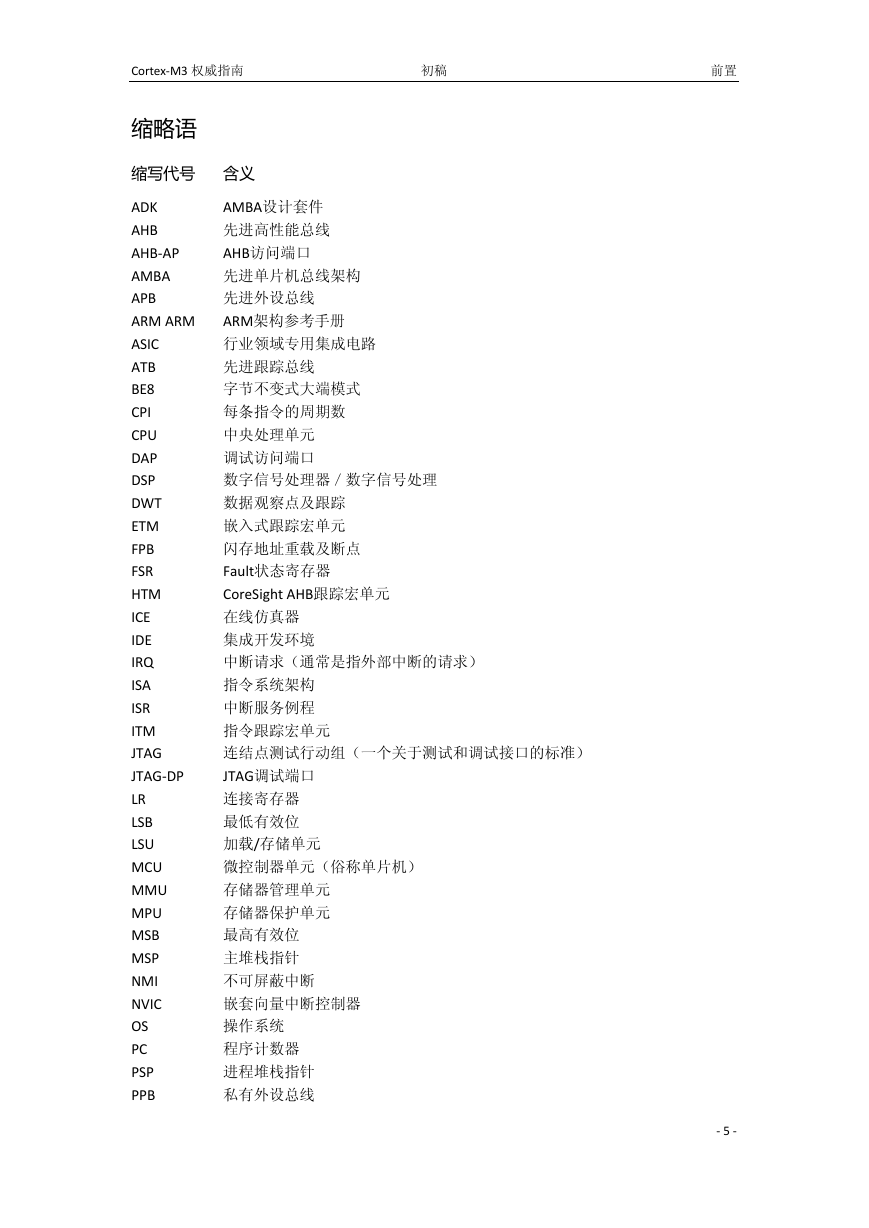

缩略语

缩写代号 含义

行业领域专用集成电路

先进跟踪总线

字节不变式大端模式

每条指令的周期数

中央处理单元

调试访问端口

数字信号处理器/数字信号处理

数据观察点及跟踪

嵌入式跟踪宏单元

闪存地址重载及断点

在线仿真器

集成开发环境

中断请求(通常是指外部中断的请求)

指令系统架构

中断服务例程

指令跟踪宏单元

连结点测试行动组(一个关于测试和调试接口的标准)

Fault状态寄存器

CoreSight AHB跟踪宏单元

JTAG调试端口

AHB访问端口

先进单片机总线架构

先进外设总线

AMBA设计套件

先进高性能总线

ADK

AHB

AHB‐AP

AMBA

APB

ARM ARM ARM架构参考手册

ASIC

ATB

BE8

CPI

CPU

DAP

DSP

DWT

ETM

FPB

FSR

HTM

ICE

IDE

IRQ

ISA

ISR

ITM

JTAG

JTAG‐DP

LR

LSB

LSU

MCU

MMU

MPU

MSB

MSP

NMI

NVIC

OS

PC

PSP

PPB

连接寄存器

最低有效位

加载/存储单元

微控制器单元(俗称单片机)

存储器管理单元

存储器保护单元

最高有效位

主堆栈指针

不可屏蔽中断

嵌套向量中断控制器

操作系统

程序计数器

进程堆栈指针

私有外设总线

‐ 5 ‐

�

Cortex‐M3 权威指南

初稿

前置

; 把寄存器R1中的数据移至R0

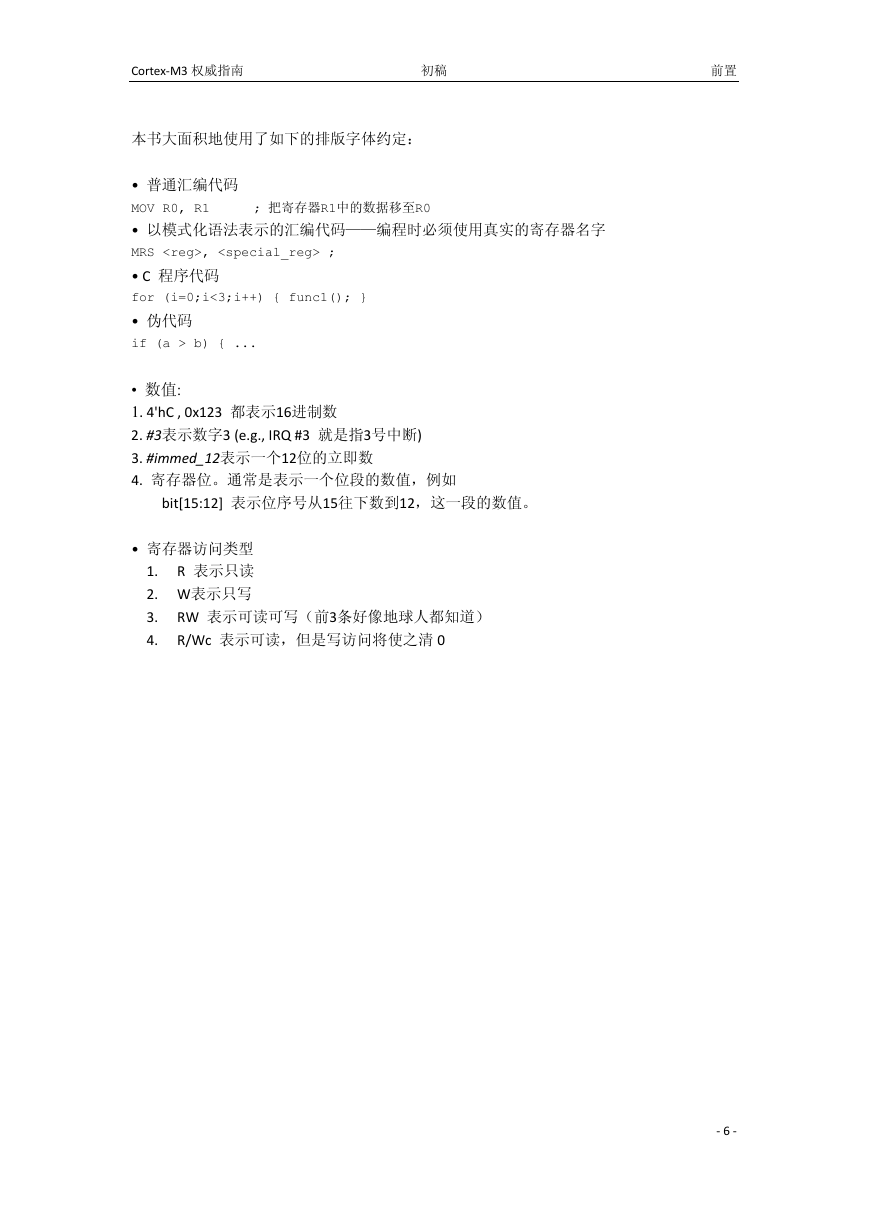

本书大面积地使用了如下的排版字体约定:

• 普通汇编代码

MOV R0, R1

• 以模式化语法表示的汇编代码——编程时必须使用真实的寄存器名字

MRS , ;

• C 程序代码

for (i=0;i<3;i++) { func1(); }

• 伪代码

if (a > b) { ...

• 数值:

1. 4'hC , 0x123 都表示16进制数

2. #3表示数字3 (e.g., IRQ #3 就是指3号中断)

3. #immed_12表示一个12位的立即数

4. 寄存器位。通常是表示一个位段的数值,例如

bit[15:12] 表示位序号从15往下数到12,这一段的数值。

• 寄存器访问类型

1. R 表示只读

2. W表示只写

3. RW 表示可读可写(前3条好像地球人都知道)

4. R/Wc 表示可读,但是写访问将使之清 0

‐ 6 ‐

�

Cortex‐M3 权威指南

初稿

前置

其它参考资料

1. Cortex-M3 Technical Reference Manual (TRM) (Cortex-M3技术参考手册)

请从www.arm.com/documentation/ARMProcessor_Cores/index.html下载

2. ARMv7-M Architecture Application Level Reference Manual(ARMv7-M应用级架构参考

手册)

请从www.arm.com/products/CPUs/ARM_Cortex-M3_v7.html下载

3.CoreSight Technology System Design Guide(CoreSight技术系统设计指导)

请从www.arm.com/documentation/Trace_Debug/index.html下载

4. AMBA Specification (AMBA规格书)

请从www.arm.com/products/solutions/AMBA_Spec.html下载

5. AAPCS Procedure Call Standard for the ARM Architecture(AAPCS ARM架构过程调用

标准)

请从www.arm.com/pdfs/aapcs.pdf下载

6. RVCT 3.0 Compiler and Library Guide(RVCT 3.0编译器及库向导)

请从www.arm.com/pdfs/DUI0205G_rvct_compiler_and_libraries_guide.pdf下载

7. ARM Application Note 179: Cortex-M3 Embedded Software Development(ARM应用笔记

179:Cortex-M3嵌入式软件开发)

请从www.arm.com/documentation/Application_Notes/index.html下载

‐ 7 ‐

�

Cortex‐M3 权威指南

初稿

前置

占位符 1,为目录保留

‐ 8 ‐

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc