Application Report

SWRA606–May 2018

CAN Node on AWR1642

RaghunandanKamath

ABSTRACT

AWR1642 has two CAN interfaces: one DCAN controller supporting bit rates of up to 1 Mbit/s, and

compliant to the controller area network (CAN) 2.0B protocol specification, and one MCAN controller

supporting bit rates of up to 10 Mbit/s. compliant to the controller area network (CAN) 2.0 part A, B

protocol specification and ISO 11898-1, and the CAN FD V1.0 specification with up to 64 data bytes

support.

This application report describes the procedure to configure a CAN node on AWR1642 and perform CAN

communication over the network.

1

2

3

Appendix A

Introduction ................................................................................................................... 2

Initializing the CAN Peripheral ............................................................................................. 5

Configuring Message Objects ............................................................................................ 11

ECO’s on AWR1642BOOST .................................................................................... 18

Contents

List of Figures

CAN Transceiver Interface ................................................................................................. 3

DCAN Module Block Diagram ............................................................................................. 4

MCAN Module Block Diagram ............................................................................................. 5

MCAN Rx Buffer/Rx FIFO Element...................................................................................... 10

ECO[1] on AWR1642BOOST ............................................................................................ 20

ECO[2] on AWR1642BOOST ............................................................................................ 21

ECO on MMWAVE-DEVPACK ........................................................................................... 21

Nominal Bit-Timing 500KBit/s ............................................................................................ 22

Nominal Bit-Timing for 1MBit/s ........................................................................................... 23

Dataphase Bit-Timing for 5Mbit/s ........................................................................................ 24

Structure of Message Object............................................................................................... 9

List of Tables

1

2

3

4

5

6

7

8

9

10

1

Trademarks

All trademarks are the property of their respective owners.

SWRA606–May 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

CAN Node on AWR1642

1

�

Introduction

1

Introduction

1.1 Controller Area Network (DCAN)

www.ti.com

The Controller Area Network is a high-integrity, serial, multi-master communication protocol for distributed

real-time applications. This CAN module is implemented according to ISO 11898-1 and is suitable for

industrial, automotive and general embedded communications.

1.1.1

Features

• Protocol

– Supports CAN protocol version 2.0 part A, B

• Speed

– Bit rates up to 1 MBit/s

• MailBox

– Configurable Message objects

– Individual identifier masks for each message object

– Programmable FIFO mode for message objects

• High Speed MailBox Access

– DMA access to Message RAM

• Debug

– Suspend mode for debug support

– Programmable loop-back modes for self-test operation

– Direct access to Message RAM in test mode

– Supports two interrupt lines - Level 0 and Level 1

• Others

– Automatic message RAM initialization

– Automatic bus on after bus-off state by a programmable 32-bit timer

– CAN Rx/Tx pins configurable as general purpose IO pins

– Software module reset

1.2 Modular Controller Area Network (MCAN)

The MCAN module supports both classic CAN with Flexible Data-Rate (CAN and CAN FD) specifications.

CAN FD feature allow high throughput and increased payload per data frame. The classic CAN and

CANFD devices can coexist on the same network without any conflict.

1.2.1

Features

• Conforms with CAN protocol 2.0 A, B and ISO 11898-1

• Full CAN FD support (up to 64 data bytes)

• AUTOSAR and SAE J1939 support

• Up to 32 dedicated transmit buffers

• Configurable transmit FIFO, up to 32 elements

• Configurable transmit queue, up to 32 elements

• Configurable transmit event FIFO, up to 32 elements

• Up to 64 dedicated receive buffers

• Two configurable receive FIFOs, up to 64 elements each

• Up to 128 filter elements

•

• Maskable interrupts, two interrupt lines

Internal loopback mode for self-test

2

CAN Node on AWR1642

Copyright © 2018, Texas Instruments Incorporated

SWRA606–May 2018

Submit Documentation Feedback

�

www.ti.com

Introduction

• Two clock domains: CAN clock and Host clock

• Parity/ECC support - message RAM single error correction and double error detection (SECDED)

• Mechanism

•

• Timestamp counter

Local power-down and wakeup support

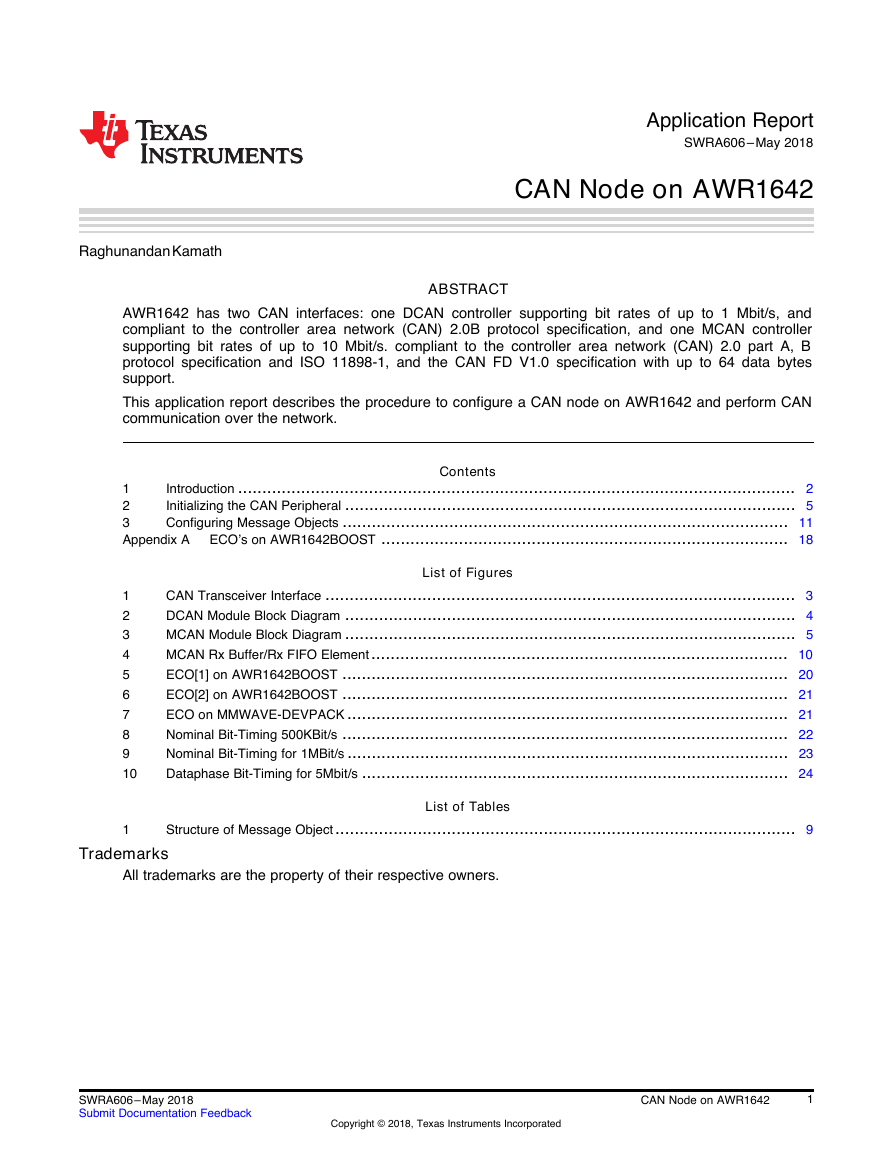

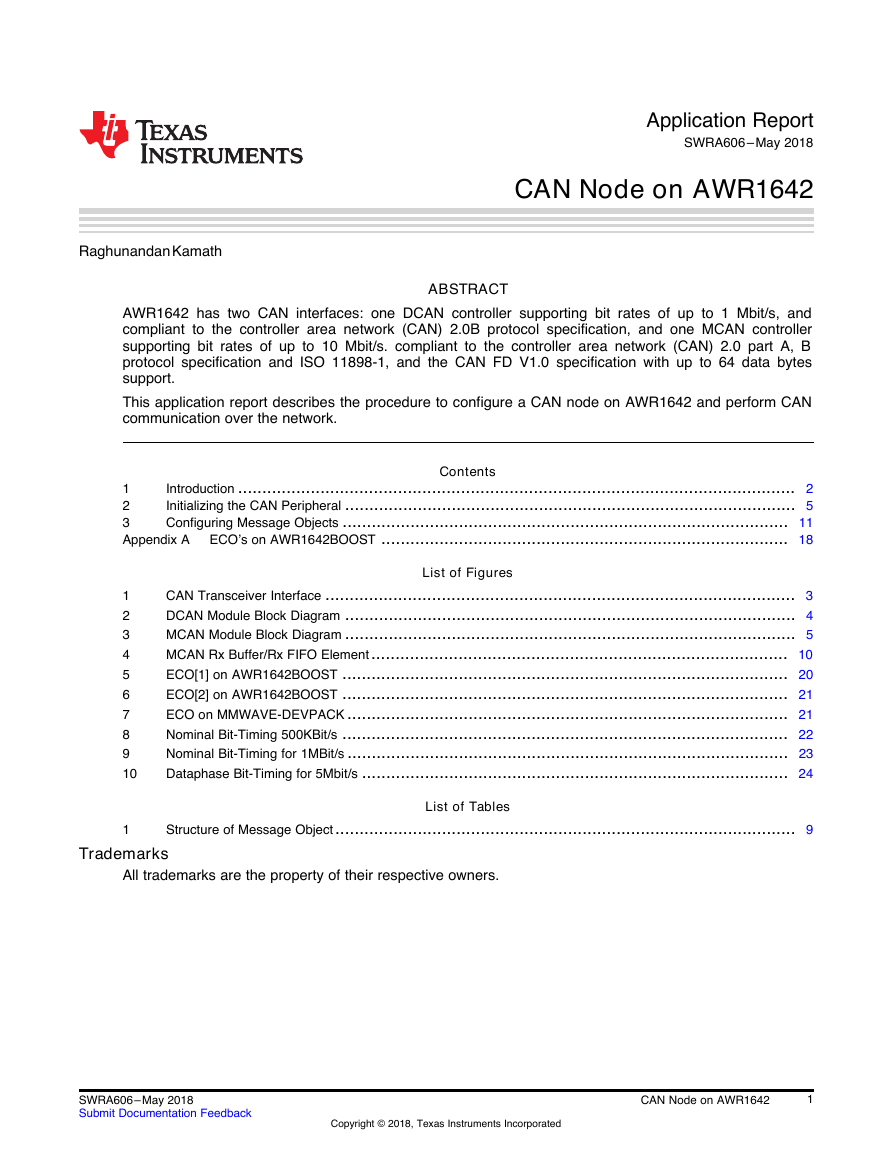

1.3 CAN Transceiver Interface Diagram

Figure 1 shows a typical CAN transceiver interface.

Figure 1. CAN Transceiver Interface

SWRA606–May 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

CAN Node on AWR1642

3

AWR1642DCANMCANMCAN RxCANTxMCANTxCANTransceiverCAN_HCANTransceiverCAN RxCAN_LCAN_HCAN_L�

Introduction

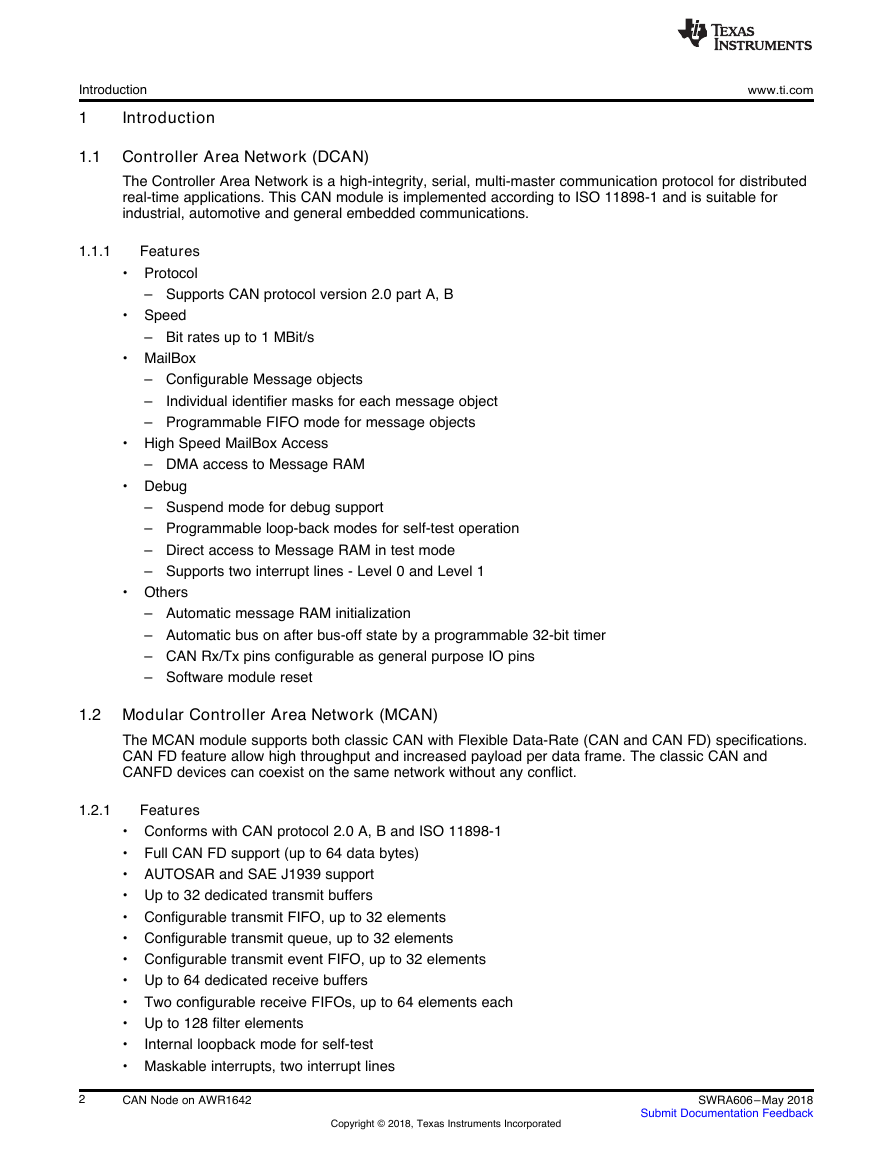

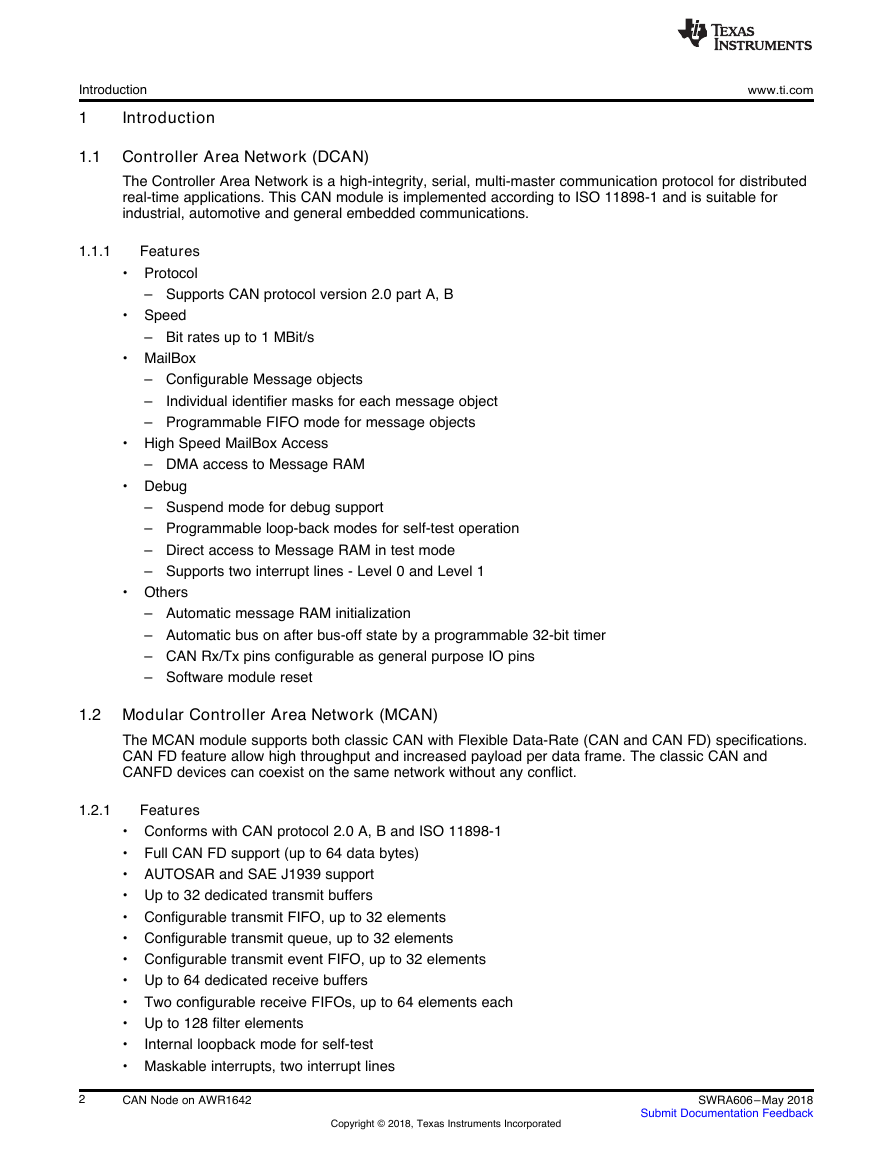

1.4 Block Diagram

1.4.1

DCAN Block Diagram

Figure 2 shows a typical DCAN module block diagram

www.ti.com

Figure 2. DCAN Module Block Diagram

4

CAN Node on AWR1642

Copyright © 2018, Texas Instruments Incorporated

SWRA606–May 2018

Submit Documentation Feedback

MessageRAMMessageObjectsMessageRAMInterfaceCPUVCLKVCLKACAN_RXCAN_TXCAN CoreCAN_CLKMessage HandlerRegisters andMessage ObjectAccessModule Interface�

www.ti.com

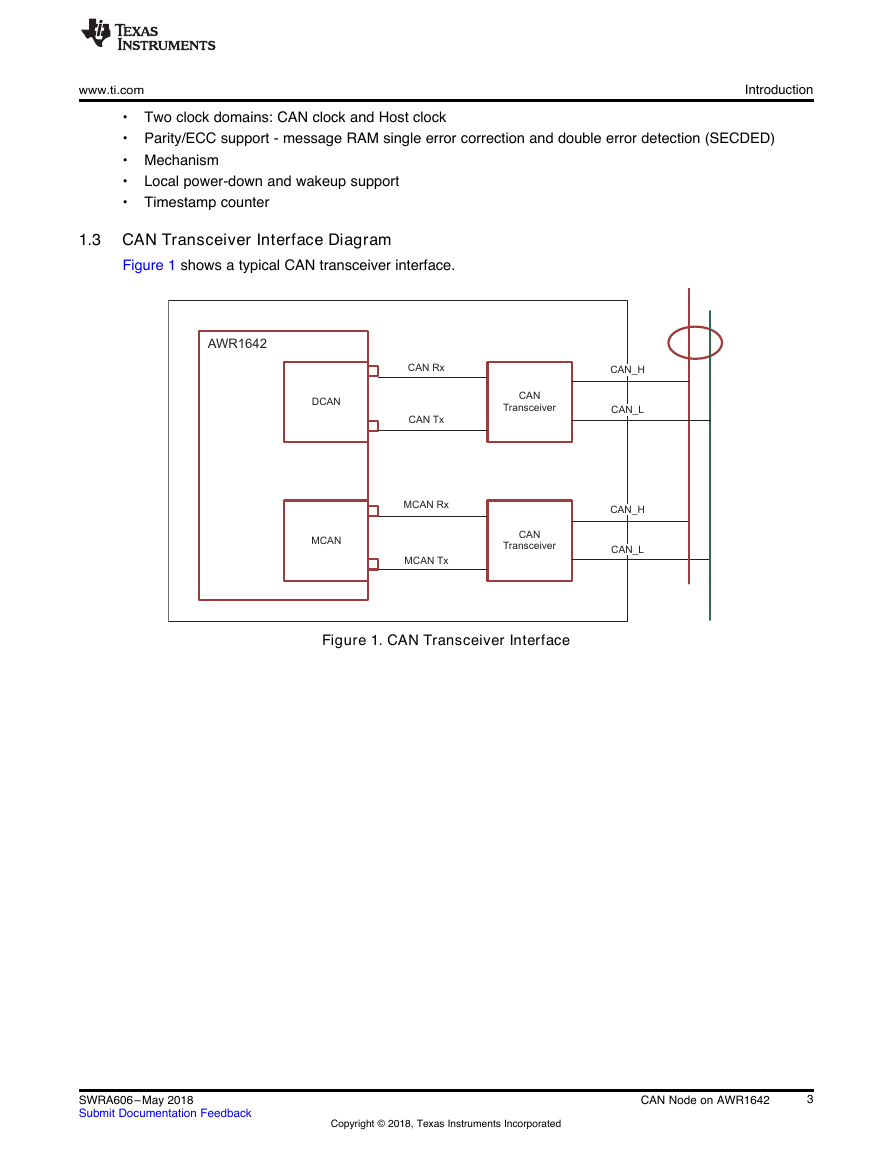

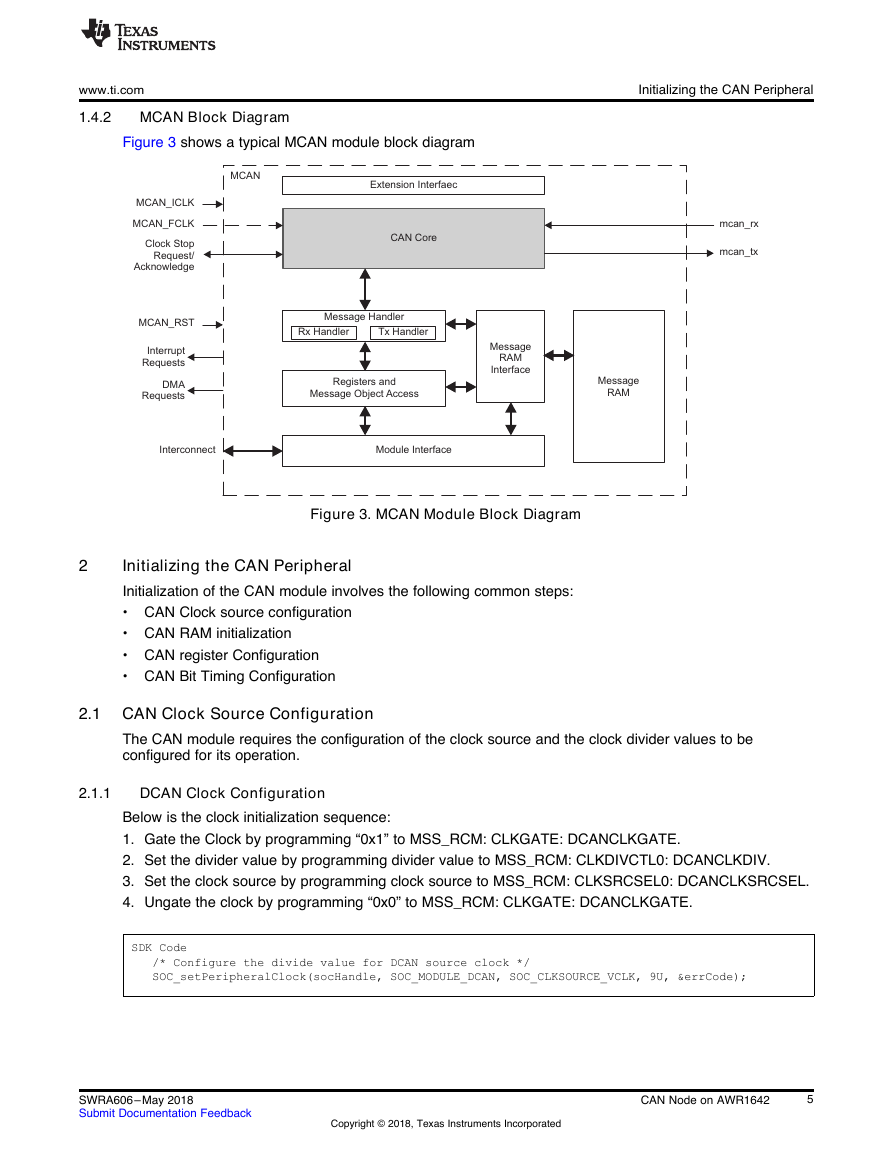

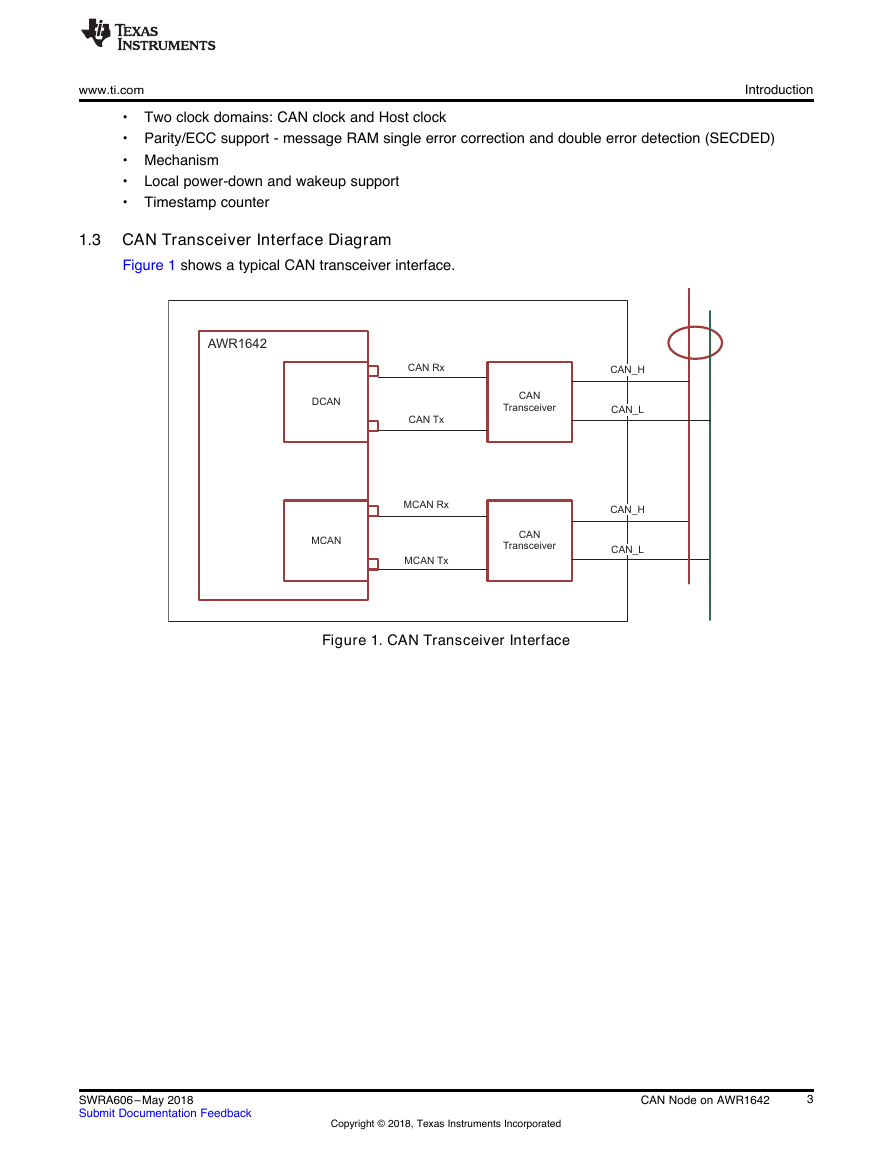

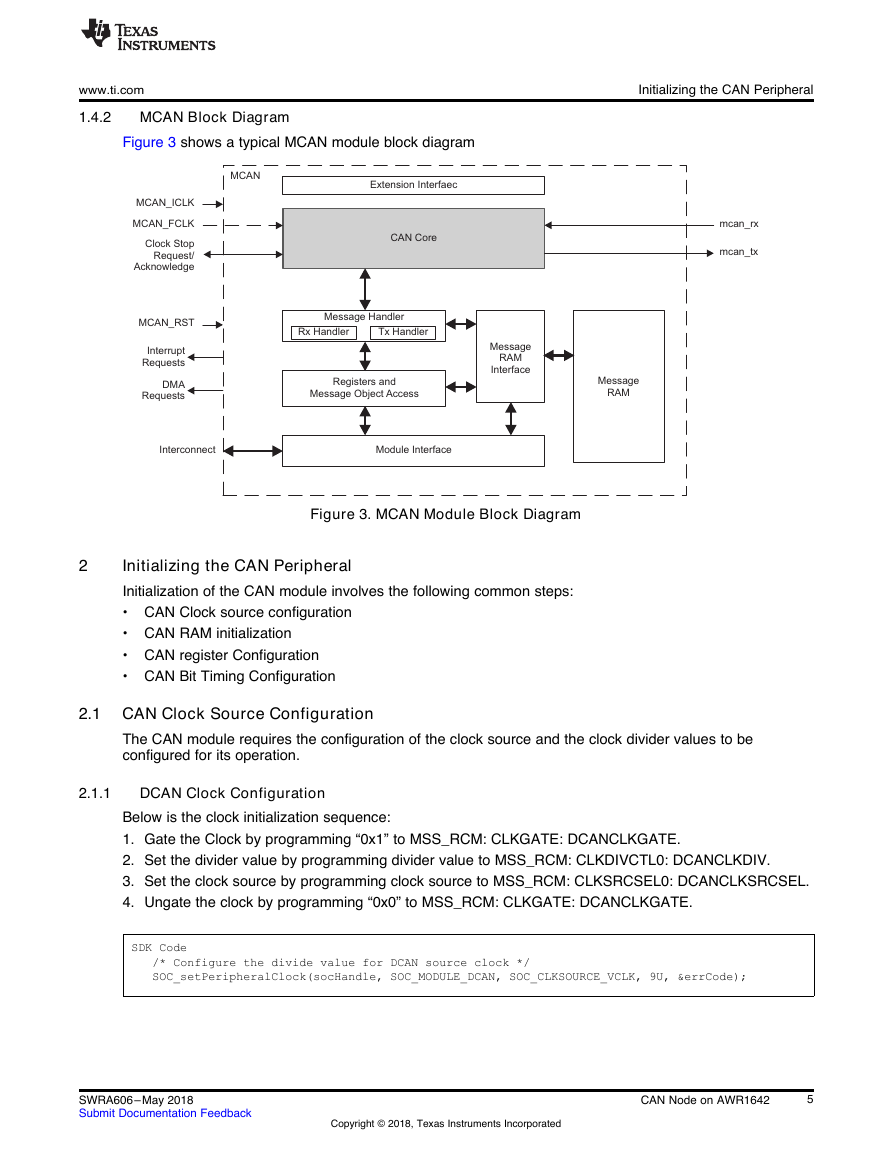

1.4.2

MCAN Block Diagram

Figure 3 shows a typical MCAN module block diagram

Initializing the CAN Peripheral

Figure 3. MCAN Module Block Diagram

2

Initializing the CAN Peripheral

Initialization of the CAN module involves the following common steps:

• CAN Clock source configuration

• CAN RAM initialization

• CAN register Configuration

• CAN Bit Timing Configuration

2.1 CAN Clock Source Configuration

The CAN module requires the configuration of the clock source and the clock divider values to be

configured for its operation.

2.1.1

DCAN Clock Configuration

Below is the clock initialization sequence:

1. Gate the Clock by programming “0x1” to MSS_RCM: CLKGATE: DCANCLKGATE.

2. Set the divider value by programming divider value to MSS_RCM: CLKDIVCTL0: DCANCLKDIV.

3. Set the clock source by programming clock source to MSS_RCM: CLKSRCSEL0: DCANCLKSRCSEL.

4. Ungate the clock by programming “0x0” to MSS_RCM: CLKGATE: DCANCLKGATE.

SDK Code

/* Configure the divide value for DCAN source clock */

SOC_setPeripheralClock(socHandle, SOC_MODULE_DCAN, SOC_CLKSOURCE_VCLK, 9U, &errCode);

SWRA606–May 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

CAN Node on AWR1642

5

Module InterfaceInterconnectDMARequestsInterruptRequestsMCAN_RSTClock StopRequest/AcknowledgeMCAN_FCLKMCAN_ICLKMCANRx HandlerTx HandlerMessage HandlerRegisters andMessage ObjectAccessMessageRAMInterfaceMessageRAMmcan_rxmcan_txCAN CoreExtension Interfaec�

Initializing the CAN Peripheral

2.1.2

MCAN Clock Configuration

www.ti.com

Below is the clock initialization sequence:

1. Gate the Clock by programming “0x1” to MSS_RCM: CLKGATE: FDCANCLKGATE.

2. Set the divider value by programming divider value to MSS_RCM: CLKDIVCTL0: FDCANCLKDIV.

3. Set the clock source by programming clock source to MSS_RCM: CLKSRCSEL0:

FDCANCLKSRCSEL.

4. Ungate the clock by programming “0x0” to MSS_RCM: CLKGATE: FDCANCLKGATE.

SDK Code

/* Configure the divide value for MCAN source clock */

SOC_setPeripheralClock(socHandle, SOC_MODULE_MCAN, SOC_CLKSOURCE_VCLK, 4U, &errCode);

2.2 CAN RAM Initialization

The CAN RAM holds the CAN message objects (also called mail box). To begin, the RAM space should

be initialized to zeros through the hardware by configuring the system registers.

2.2.1

DCAN RAM Initialization

Below is the sequence for RAM initialization:

1. Switch to memory initialization mode by programming the key “0xAD” to MSS_RCM: MEMINITSTART:

MEMINITKEY.

2. Start the memory initialization for the DCAN memories by programming ‘0x1’ to MSS_RCM:

MEMINITSTART: DCANMEM,

3. Wait on the confirmation of the memory initialization complete. Wait until MSS_RCM: MEMINITDONE:

DCANMEM to become “0x1”.

SDK Code

/* Initialize peripheral memory */

SOC_initPeripheralRam(socHandle, SOC_MODULE_DCAN, &errCode);

2.3 CAN Register Configuration

2.3.1

DCAN Register Configuration

The following steps are involved in the DCAN configuration:

1. Enable the “Normal” operation by programming ‘0x1’ to DCAN_CTL: INIT.

2. Enable the “Configuration Change Enable” by programming ‘0x1’ to DCAN_CTL: CCE.

3. Enable the “Interrupt line 0” by programming ‘0x1’ to DCAN_CTL:IE0.

4. Enable the “Status Change Interrupt Enable” by programming ‘0x1’ to DCAN_CTL:SIE.

5. Enable the “Error Interrupt Enable” by programming ‘0x1’ to DCAN_CTL:EIE.

6. Enable the “Disable automatic retransmission” by programming ‘0x1’ to DCAN_CTL:DAR.

7. Enable the “Test mode enable” by programming ‘0x1’ to DCAN_CTL:TEST.

8. Enable the “Interruption debug support enable” by programming ‘0x1’ to DCAN_CTL:IDS.

9. Enable the “Auto-Bus-On enable” by programming ‘0x1’ to DCAN_CTL:ABO.

10. Enable the “Parity On/Off bit” by programming ‘0xF’ to DCAN_CTL:PMD.

11. Enable the “Internal init state while debug access” by programming ‘0xF’ to DCAN_CTL: INITDBG.

12. Enable the “Interrupt line 1” by programming ‘0x1’ to DCAN_CTL:IE1.

6

CAN Node on AWR1642

Copyright © 2018, Texas Instruments Incorporated

SWRA606–May 2018

Submit Documentation Feedback

�

www.ti.com

Initializing the CAN Peripheral

13. Enable the “Enable DMA request line for IF1” by programming ‘0x1’ to DCAN_CTL:DE1.

14. Enable the “Enable DMA request line for IF2” by programming ‘0x1’ to DCAN_CTL:DE2.

15. Enable the “Enable DMA request line for IF3” by programming ‘0x1’ to DCAN_CTL:DE3.

16. Program the “Auto BUS on Timer register ” with the timer value in DCAN_ABOTR:ABO_TIME .

SDK Code

/* Initialize the DCAN parameters that need to be specified by the application */

DCANAppInitParams(&appDcanCfgParams,

&appDcanTxCfgParams,

&appDcanRxCfgParams,

&appDcanTxData);

/* Initialize the CAN driver */

canHandle = CAN_init(&appDcanCfgParams, &errCode);

2.3.2

MCAN Register Configuration

The following steps are involved in the MCAN configuration:

1. Check whether or not the memory initialization is complete. Check if the value of MCANSS_STAT:

MMI_DONE is set to 0x1.

Initiate a soft reset by programming value “0x1” to MCANSS_CTRL: RESET.

2.

3. Put the MCAN in “Software Initialization Mode” by programming ‘0x1’ to MCAN_CCCR: INIT.

4. Configure MCAN wakeup and clock stop controls.

a. Enable “Wakeup Request Enable” programming value “0x1” to MCANSS_CTRL:WAKEUPREGEN.

b. Enable “Automatic Wakeup Enable” programming value “0x1” to MCANSS_CTRL:

AUTOWAKEUP.

c. Disable “Emulation Enable” programming value “0x0” to MCANSS_CTRL: EMUEN.

d. Disable “Emulation Fast Ack” programming value “0x0” to MCANSS_CTRL: EMUFACK.

e. Disable “Clock Fast Ack” programming value “0x0” to MCANSS_CTRL: CLKFACK.

5. Configure MCAN mode (FD vs Classic CAN operation) and controls.

a. Enable the “FD Operation Enable” by programming value ‘0x1’ to MCAN_CCCR: FDOE.

b. Enable the “Bit Rate Switch Enable” by programming value ‘0x1’ to MCAN_CCCR: BRSE.

c. Disable the “Transmit Pause” by programming value ‘0x0’ to MCAN_CCCR: TXP.

d. Disable the “Edge Filtering during Bus Integration” by programming value ‘0x0’ to MCAN_CCCR:

EFBI.

e. Disable the “Protocol Exception Handling Disable” by programming value ‘0x0’ to MCAN_CCCR:

PXHD.

f. Enable the “Disable Automatic Retransmission” by programming value ‘0x1’ to MCAN_CCCR:

DAR.

6. Configure transceiver delay compensation.

a. Configure the “Transmitter Delay Compensation Filter Window Length” by programming the length

to MCAN_TDCR: TDCF.

b. Configure the “Transmitter Delay Compensation Offset” by programming the length to

MCAN_TDCR: TDCO.

7. Configure MSG RAM watchdog counter preload value by programming the preload value to

MCAN_RWD: WDC.

SWRA606–May 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

CAN Node on AWR1642

7

�

Initializing the CAN Peripheral

www.ti.com

8. Enable the “Transceiver Delay Compensation” by programming the MCAN_DBTP: TDC.

SDK Code

MCANAppInitParams (&mcanCfgParams);

/* Initialize the CANFD driver */

canHandle = CANFD_init(&mcanCfgParams, &errCode);

2.4 CAN Bit Timing Configuration

2.4.1

DCAN Bit Timing Configuration

The following steps are used for the DCAN bit timing configuration:

1. Enable the “Init” operation by programming ‘0x1’ to DCAN_CTL: INIT.

2. Enable the “Configuration Change Enable” by programming ‘0x1’ to DCAN_CTL: CCE.

3. Program the DCAN bit time value by programming the BRP Extension Register DCAN_BTR with BRP

value.

4. Disable the “Configuration Change Enable” by programming ‘0x0’ to DCAN_CTL: CCE.

5. Enable the “Normal” operation by programming ‘0x0’ to DCAN_CTL: INIT.

SDK Code

/* Set the desired bit rate based on input clock */

retVal = DCANAppCalcBitTimeParams(DCAN_APP_INPUT_CLK / 1000000,

DCAN_APP_BIT_RATE / 1000,

DCAN_APP_SAMP_PT,

DCAN_APP_PROP_DELAY,

&appDcanBitTimeParams);

2.4.2

MCAN Bit Timing Configuration

The following steps are used for the MCAN bit timing configuration:

1. Enable the “Configuration Change Enable” by programming ‘0x1’ to MCAN_CCCR: CCE.

2. Configure the nominal bitrate values.

a. Program the “Nominal Resynchronization Jump Width” with value to MCAN_NBTP: NSJW.

b. Program the “Nominal Baud Rate Prescaler” with value to MCAN_NBTP: NBRP.

c. Program the “Nominal Time segment before sample point” with value to MCAN_NBTP: NTSEG1.

d. Program the “Nominal Time segment after sample point” with value to MCAN_NBTP: NTSEG2.

3. Configure the dataphase bitrate values.

a. Program the “Data Resynchronization Jump Width” with value to MCAN_ MCAN_DBTP: DSJW.

b. Program the “Data time segment after sample point” with value to MCAN_ MCAN_DBTP:

DTSEG2.

c. Program the “Data time segment before sample point” with value to MCAN_ MCAN_DBTP:

DTSEG1.

d. Program the “Data Baud Rate Prescaler” with value to MCAN_ MCAN_DBTP: DBRP.

e. Program the “Data Baud Rate Prescaler” with value to MCAN_ MCAN_DBTP: DBRP.

8

CAN Node on AWR1642

Copyright © 2018, Texas Instruments Incorporated

SWRA606–May 2018

Submit Documentation Feedback

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc