描述

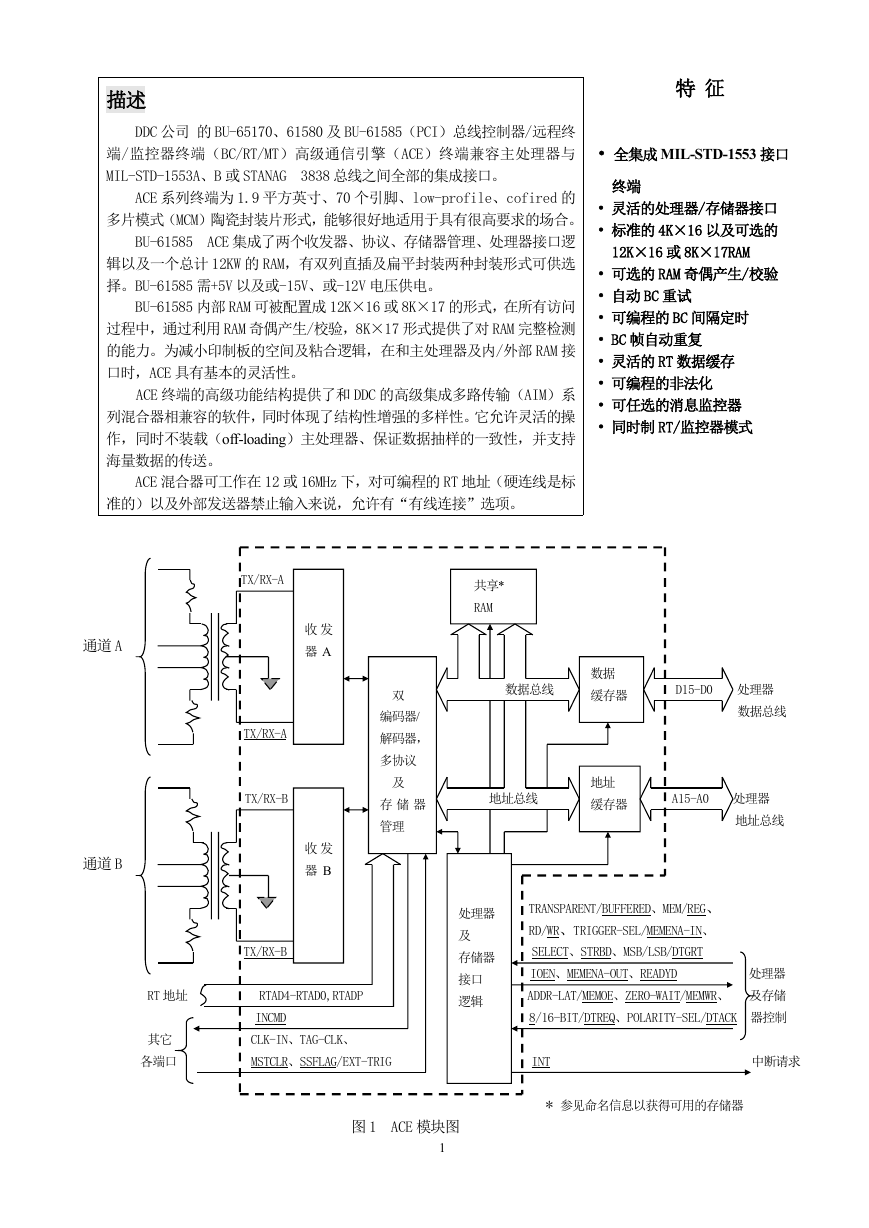

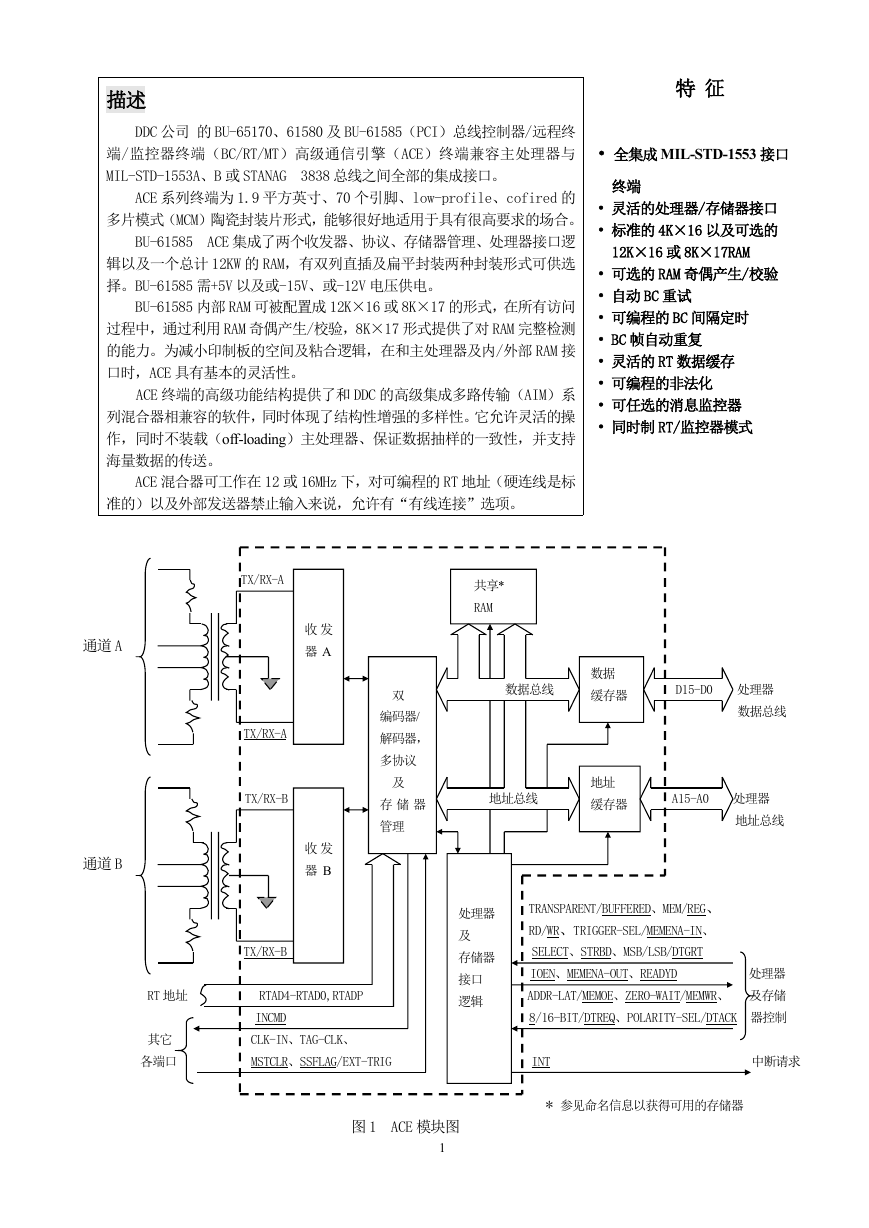

DDC 公司 的 BU-65170、61580 及 BU-61585(PCI)总线控制器/远程终

端/监控器终端(BC/RT/MT)高级通信引擎(ACE)终端兼容主处理器与

MIL-STD-1553A、B 或 STANAG 3838 总线之间全部的集成接口。

ACE 系列终端为 1.9 平方英寸、70 个引脚、low-profile、cofired 的

多片模式(MCM)陶瓷封装片形式,能够很好地适用于具有很高要求的场合。

BU-61585 ACE 集成了两个收发器、协议、存储器管理、处理器接口逻

辑以及一个总计 12KW 的 RAM,有双列直插及扁平封装两种封装形式可供选

择。BU-61585 需+5V 以及或-15V、或-12V 电压供电。

BU-61585 内部 RAM 可被配置成 12K×16 或 8K×17 的形式,在所有访问

过程中,通过利用 RAM 奇偶产生/校验,8K×17 形式提供了对 RAM 完整检测

的能力。为减小印制板的空间及粘合逻辑,在和主处理器及内/外部 RAM 接

口时,ACE 具有基本的灵活性。

ACE 终端的高级功能结构提供了和 DDC 的高级集成多路传输(AIM)系

列混合器相兼容的软件,同时体现了结构性增强的多样性。它允许灵活的操

作,同时不装载(off-loading)主处理器、保证数据抽样的一致性,并支持

海量数据的传送。

ACE 混合器可工作在 12 或 16MHz 下,对可编程的 RT 地址(硬连线是标

准的)以及外部发送器禁止输入来说,允许有“有线连接”选项。

特 征

• 全集成 MIL-STD-1553 接口

终端

• 灵活的处理器/存储器接口

• 标准的 4K×16 以及可选的

12K×16 或 8K×17RAM

• 可选的 RAM 奇偶产生/校验

• 自动 BC 重试

• 可编程的 BC 间隔定时

• BC 帧自动重复

• 灵活的 RT 数据缓存

• 可编程的非法化

• 可任选的消息监控器

• 同时制 RT/监控器模式

通道 A

通道 B

收 发

器 A

收 发

器 B

TX/RX-A

TX/RX-A

TX/RX-B

TX/RX-B

RT 地址

RTAD4-RTAD0,RTADP

INCMD

其它

各端口

CLK-IN、TAG-CLK、

MSTCLR、SSFLAG/EXT-TRIG

图 1 ACE 模块图

1

共享*

RAM

双

编码器/

解码器,

多协议

及

存 储 器

管理

数据总线

数据

缓存器

D15-D0 处理器

数据总线

地址总线

地址

缓存器

A15-A0 处理器

地址总线

处理器

及

存储器

接口

逻辑

TRANSPARENT/BUFFERED、MEM/REG、

RD/WR、TRIGGER-SEL/MEMENA-IN、

SELECT、STRBD、MSB/LSB/DTGRT

IOEN、MEMENA-OUT、READYD

处理器

ADDR-LAT/MEMOE、ZERO-WAIT/MEMWR、 及存储

8/16-BIT/DTREQ、POLARITY-SEL/DTACK 器控制

INT

中断请求

* 参见命名信息以获得可用的存储器

�

表 1 “ACE”系列详细说明

参数

最小

典型

最大

单位

绝对最大值

电源电压

■ 逻辑+5V

■ 收发器+5V

■ –15V

■ –12V

逻辑

■ 电压输入范围

接收器

差分输入电阻

■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2)(注 1-7)

■ (BU-65170/61580/61585×3、BU-65170/61580/61585×6)(注 1-7)

差分输入电容

■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2)(注 1-7)

■ (BU-65170/61580/61585×3、BU-65170/61580/61585×6)(注 1-7)

门限电压(变压器耦合、短截线上测得)

共模电压(注 7)

发送器

差分输出电压

■ 跨接 35Ω直接耦合、在总线上测得

■ 跨接 70Ω变压器耦合、在总线上测得

■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2、×3、×6)

输出噪音(差分、直接耦合)

输出偏移电压(变压器耦合、短截线上测得)

上升/下降时间

逻辑

VIH

VIL

IIH(VCC=5.5V,VIN=VCC)

IIH(VCC=5.5V,VIN=2.7V)

■ SSFLAG/EXT-TRIG

■ 所有其它输入

IIL(VCC=5.5V,VIN=0.4V)

■ SSFLAG/EXT-TRIG

■ 所有其它输入

VOH(VCC=4.5V,VIH=2.7V、VIL=0.2V、IOH=最大)

VOL(VCC=4.5V,VIH=2.7V、VIL=0.2V、IOL=最大)

IOL

■ DB15-DB0、A15-A0、MEMOE/ADDR-LAT、MEMWR/ZERO-WAIT、

DTREQ/16/8、DTACK/POLARITY-SEL

■ INCMD、INT、MEMENA-OUT、READYD、IOEN、TXA、TXA、

TXB、TXB、TX-INH-OUT-A、TX-INH-OUT-B

2

-0.3

-0.3

-18.0

-18.0

-0.3

11

2.5

0.200

6

-250

100

2.0

-10

-692

-346

-794

-397

2.4

6.4

3.2

7.0

7.0

0.3

0.3

VCC+0.3

10

5

0.860

10

9

27

27

10

250

300

0.8

10

-84

-42

-100

-50

0.4

V

V

V

V

V

KΩ

KΩ

pF

pF

Vp-p

Vpeak

Vp-p

Vp-p

Vp-p

mVp-p,diff

mV

nsec

V

V

uA

uA

uA

uA

uA

V

V

mA

mA

7

20

18

150

�

表 1 “ACE”系列详细说明(续 1)

最小

参数

典型

最大

单位

逻辑(续)

IOH

■ DB15-DB0、A15-A0、MEMOE/ADDR-LAT、MEMWR/ZERO-WAIT、

DTREQ/16/8、DTACK/POLARITY-SEL

■ INCMD、INT、MEMENA-OUT、READYD、IOEN、TXA、TXA、

TXB、TXB、TX-INH-OUT-A、TX-INH-OUT-B

CI(输入电容)

CIO(双向信号输入电容)

电源要求

差分输入电阻

■ BU-65170/61580/61585×1

· +5V(逻辑)

· +5V(通道 A、通道 B)

· -15V(通道 A、通道 B)

■ BU-65170/61580/61585×2

· +5V(逻辑)

· +5V(通道 A、通道 B)

· -12V(通道 A、通道 B)

■ BU-65170/61580/61585×3、BU-65170/61580/61585×6

· +5V(逻辑)

· +5V(通道 A、通道 B)

漏电流

■ BU-65170/61580×1

· +5V(逻辑、通道 A、通道 B)

· -15V(通道 A、通道 B)

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-65170/61580×2

· +5V(逻辑、通道 A、通道 B)

· -12V(通道 A、通道 B)

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-65170/61580×3、BU-65170/61580×6

· +5V(逻辑、通道 A、通道 B)

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

3

4.5

4.5

-15.75

4.5

4.5

-12.6

4.5

4.75

6.4

3.2

50

50

5.5

5.5

-14.25

5.5

5.5

-11.4

5.5

5.25

190

60

108

160

255

190

60

120

185

305

200

350

500

800

5.0

5.0

-15.0

5.0

5.0

-12.0

5.0

5.0

95

30

68

105

180

95

30

80

130

230

95

245

360

590

mA

mA

pF

pF

V

V

V

V

V

V

V

V

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

�

表 1 “ACE”系列详细说明(续 2)

最小

参数

典型

最大

单位

电源要求(续)

漏电流

■ BU-61585×1

· +5V(逻辑、通道 A、通道 B)

· -15V(通道 A、通道 B)

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×2

· +5V(逻辑、通道 A、通道 B)

· -12V(通道 A、通道 B)

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×3、BU-61585×6

· +5V(逻辑、通道 A、通道 B)

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

功耗

全部混合器

■ BU-65170/61580×1

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-65170/61580×2

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-65170/61580×3、BU-65170/61580×6

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×1

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

4

105

30

68

105

180

105

30

80

130

230

105

255

370

600

0.850

1.195

1.450

1.975

0.835

1.135

1.435

2.035

0.475

0.905

1.160

1.670

0.900

1.245

1.500

2.025

240

60

120

185

305

240

250

400

550

850

1.85

2.25

2.72

3.52

1.67

2.10

2.59

3.46

1.00

1.43

1.86

2.72

2.10

2.50

2.97

3.77

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

�

表 1 “ACE”系列详细说明(续 3)

最小

参数

典型

最大

单位

功耗(续)

全部混合器

■ BU-61585×2

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×3、BU-61585×6

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

最热 Die

■ BU-65170/61580×1

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-65170/61580×2

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-65170/61580×3、BU-65170/61580×6

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×1

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×2

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×3、BU-61585×6

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

5

0.885

1.185

1.485

2.085

0.525

0.955

1.210

1.720

0.335

0.600

0.860

1.385

0.290

0.590

0.890

1.490

0.200

0.630

0.885

1.395

0.335

0.600

0.860

1.385

0.290

0.590

0.890

1.490

0.200

0.630

0.885

1.395

1.92

2.35

2.84

3.71

1.25

1.68

2.11

2.97

0.68

1.06

1.45

2.23

0.59

0.92

1.36

2.16

0.25

0.68

1.11

1.97

0.68

1.06

1.45

2.23

0.59

0.92

1.36

2.16

0.25

0.68

1.11

1.97

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

�

表 1 “ACE”系列详细说明(续 4)

最小

参数

典型

最大

单位

时钟输入

频率

■ 标称值(可编程的)

· 缺省模式

· 软件可编程选项

■ 长期容许量

· 1553A 模式

· 1553B 模式

■ 短期容许量、1 秒

· 1553A 模式

· 1553B 模式

■ 工作周期

· 16MHz

· 12MHz

1553 消息定时

CPU 写操作的完成(BC 开始到下一个消息的开始)

BC 消息间间隔(注 8)

BC/RT/MT 响应暂停(注 9)

■ 18.5 标称值

■ 22.5 标称值

■ 50.5 标称值

■ 128.0 标称值

RT T 响应暂停(注 11)

发送器看门狗暂停

热参数

热电阻、节点- 壳

最热 Die(θJC)

■ BU-65170/61580×1、BU-65170/61580×2

■ BU-65170/61580×3、BU-65170/61580×6

工作节温

储藏温度

引线温度(焊接、10 秒)

物理特征

尺寸

■ BU-65170/61580/61585 S

■ BU-65170/61580/61585 V

重量

■ BU-65170/61580/61585 S/V

16.0

12.0

2.5

9.5

18.5

22.5

50.5

129.5

688

33

40

17.5

21.5

49.5

127

4

-55

-65

0.01

0.1

0.001

0.01

67

60

19.5

23.5

51.5

131

7

6.99

6.8

150

150

+300

MHz

MHZ

%

%

%

%

%

%

us

us

us

us

us

us

us

us

℃/W

℃/W

℃

℃

℃

1.9×1.0×0.165

英寸

(48.3×25.4×4.19)

(毫米)

1.9×1.0×0.150

英寸

(48.3×25.4×3.81)

(毫米)

0.6(17)

盎司(克)

6

�

表 1 注:注 1 到注 6 适用于接收器差分电阻及差分电容的说明

⑴ 该说明包括接收器及发送器(在内部是连在一起的)

⑵ 阻抗的测试是直接在 BU-65170/61580××混合器的管脚 TX/RX A(B)及 TX/RX A(B)之间进行的。

⑶ 假定混合器所有的电源及地输入端都被连接。

⑷ 该说明适用于上电及非上电两种情况

⑸ 该说明假定是 2V rms 的平衡、差分、正旋输入的情况,适用频率范围是 75KHz 到 1MHz。

⑹ 所给的最小电阻及最大电容参数在整个工作范围内都是满足要求的,但未经在整个工作范围内测试。

⑺ 假定共模电压的频率范围是直流到 2MHz,在短截线一侧的隔离变压器的管脚上(直接耦合或变压器耦合)测得,

以混合器的地为参考点。使用的变压器必须是 DDC 推荐的或能提供相同的最小 CMRR(共模抑制比)的其它变压

器。

⑻ 对最小消息间间隔定时来说,其典型值在软件的控制下可以增加到(65535us 减去消息本身的时间),其单位增

量是 1us。

⑼ 是软件可编程的(4 个选项),包括 RT-to-RT 暂停(发送指令的中间奇偶位到发送 RT 状态的中间同步位之间的

时间)。

⑽ 是对+5V 逻辑及收发器而言的,对通道 A 及通道 B 来说,是+5V。

⑾ 是从指令字的中间奇偶位过零点开始到 RT 状态字的中间同步位过零点为止进行测量的。

⑿ 对 BU-65171、BU-61581、及 BU-61586 的说明与对 BU-65170、BU-61580、及 BU-61585 的说明是分别完全相同

的。

1 介绍

DDC 的集成 BC/RT/MT 混合器 ACE 系列在微处理器和 MIL-STD-1553A、B Notice 2、McAir、或 STANAG 3838

总线之间提供了完整的、灵活的接口,可完成 BC、RT 及 MT 模式。封装形式为一个单片 1.9 平方英寸、70 个引脚的

DIP 或表面贴装,或 J-引线封装。ACE 系列含有两个低功耗收发器和编码/解码器、完整的 BC/RT/MT 多协议逻辑、

存储器管理及中断逻辑、共享的 4K×16 静态 RAM 以及一个与主处理器总线可直接相连的缓冲接口。

BU-65170/61580 含内部地址锁存器及双向数据缓存器,可与主处理器总线直接接口。在缓存的共享 RAM 配置方

式下,BU-65170/61580 可与 16 位及 8 位微处理器直接相连。另外,通过直接存储器访问(DMA)接口,ACE 可以和

16 位微处理器总线相连。BU-65170/61580 含有 4KW 的缓存 RAM,非此即彼,无论在共享 RAM,还是在 DMA 配置方式

下,ACE 都可以和多达 64KW 的外部 RAM 相连。

ACE RT 模式是多协议的,支持 MIL-STD-1553A、MIL-STD-1553B Notice 2、STANAG 3838(含 EFA 总线),以

及 McAir A3818、A5232 及 A5690 协议,完全服从 McAir 规则,但需使用正弦收发器(收发器选项 5),参见 BU-61590

数据页以获取 McAir 终端的更多信息。

RT 模式的存储器管理方案提供了一个广播数据分离的选项,与 1553B Notice 2 是一致性的。双缓存器和循环

缓存器选项都可以通过子地址编程。这些功能有助于保证数据的一致性,并且对海量数据传送来说,有助于(off-load)

主处理器。

ACE 系列完成 3 种监控器模式:字监控器、可选择的消息监控器、合并型 RT/可选择监控器。其它功能包括自

动重试及 BC 模式的可编程消息间间隔选项、内部定时标签寄存器、内部中断状态寄存器以及 RT 模式的内部指令非

法化。

2 功能概述

2.1 收发器

BU-65170/61580×3(×6)中的收发器全部都是单片的,只需+5V 电源输入。除取消了对其它电源输入的要求

外,只需+5 电源输入的收发器还需要利用升压,而不是降压的隔离变压器。与 15V 或 12V 的发送器相比,这样做可

能具有的优点是终端输入阻抗较高,因此,输入阻抗的测试就具有更大的余量,被用于对 1553 有效性的测试。这

样,还允许在嵌入式 1553 终端的隔离变压器和 LRU 系统连接器之间使用更长的电缆。

对+5V 和-15V/-12V 前端来说,BU-61580×1(×2)使用低功耗双极性单片及厚片混合技术,收发器只需+5V 和

7

�

-15V/-12V(不需要+15V/+12V),并包括电源发送器。该电源发送器为使用长电缆及总线装载海量数据时提供了超级

线驱动能力。另外,BU-65170/61580×1 中的单块收发器最大限度地减小了变压器耦合的 20V 峰-峰电压的残端电平,

使它们满足 MIL-STD-1760 的要求。

就前端过压保护、门限、共模反射、字的出错率来说,BU-65170/61580 的接收器部分与 MIL-STD-1553B 是完一

致的,另外,接收器滤波器和 J 型芯片的曼彻斯特Ⅱ解码器已经被设计成最佳工作形式。

2.2 J 型数字单片芯片

J 型数字单片芯片是 ACE 终端家族基本成员的代表,开发的 J 型芯片是 DDC 的 1553 协议及接口设计的第五代产

品。最近几年,DDC 的 1553 协议及接口设计的发展历程为:(1)分离元件部分,包括多功能混合器(在单个混合器

的内部具有很多数量的芯片)及可编程逻辑器件。(2)多功能典型的 ASIC,可在单个混合器中完成编码器/解码器

及 RT 协议功能。(3)BUS-61553 高级集成多路传输混合器(AIM-HY)系列,除了一个双单/厚片收发器及分离的 RAM

芯片外,它还包括一个典型的协议芯片和一个分离的典型存储器管理/处理器接口芯片(4)BUS-61559 带有增强 RT

功能的 AIM-HY,er,它带有增强的 RT 功能(AIM-HY,er— 除了 AIM-HY 系列所具有的功能外,AIM-HY,er 系列还具有

存储器管理及处理器接口功能)。(5)全集成的 J 型芯片。

J 型芯片含有一个双编码/解码器、完整的 BC 协议、1553A/B/McAir RT 及 MT 模式、存储器管理及中断逻辑、

与主处理器总线及可任选的外部 RAM 灵活的带缓存的接口、以及 4KW 的片内 RAM。参见图 1 点划线内的部分。除了

能实现早期 AIM-HY,er 系列所有的协议、存储器管理以及接口功能外,J 型芯片还做了大量的改进以方便硬件及软件

的设计,并进一步 off-load 1553 终端的主处理器。

2.3 解码器

BU-65170 RT 和 BU-61580 BC/RT/MT 工作时所需时钟输入的缺省值是 16MHz,如果需要,软件可编程选项允许

该器件工作时的时钟输入为 12MHz。多数流行的 1553 解码器的抽样时钟为 10MHz 或 12MHz。在 16 MHz(硬件或软件

复位时的缺省值)模式下,ACE 解码器对 1553 串行数据的抽样时钟为 16 MHz。在 12MHz 模式下,解码器利用时钟

的两个沿抽样,因此抽样速率可达 24MHz。就位出错率及过零点失真容许量来说,J 型芯片曼彻斯特Ⅱ解码器更快的

抽样速率具有更高的性能。

MIL-STD-1773 要求和光纤收发器接口,这时可以使用无收发器版本的 J 型芯片 BU-65620,这些芯片提供了管

脚可编程选项,以便和光纤接收器的各单端输出口直接相连,不需要外部逻辑。

2.4 时间定标

ACE 内部含有可读写的内部定时标签寄存器,该寄存器是一个 CPU 可读写的 16 位计数器,其分辨度是可编程的,

为 2、4、6、8、16、32、或 64us/LSB。同样,定时标签寄存器的时钟也可以是外部振荡器。另一个选项允许定时标

签寄存器的增量是软件可控的。这样做可以支持定时标签寄存器的自检,对 BC 和 RT 模式来说,每一个被处理的消

息都被装载到相应的描述器堆栈入口的第二个位置(TIME TAG WORD)。

其它选项有:在同步模式指令(不带数据)之后清除定时标签寄存器、或在同步模式指令(带数据)之后装载

定时标签寄存器。当定时标签寄存器从 0000 滚动到 FFFF 时使能中断请求并设置中断状态寄存器中的一位。假如定

时标签寄存器没被装载或已被复位,对 64us/LSB 到 2us/LSB 的分辨率来说,这将产生约 4 秒到 131ms 的时间间隔。

RT 模式的另一个可编程选项是,当 ACE 响应了一个发送矢量字模式指令后,自动清除“服务请求状态字”位。

2.5 中断

ACE 系列器件为中断的产生和处理提供了很多可编程选项,中断输出管脚(INT)具有 3 种软件可编程的工作模

式:脉冲、软件控制下清除的电平输出、读中断状态寄存器后自动清除的电平输出。

各中断都被中断屏蔽寄存器所使能。使用中断状态寄存器,主处理器可轻易地判断中断原因,中断状态寄存器

提供了中断事件的当前状态。中断状态寄存器的更新有两种途径。在标准中断处理模式中,只有当事件存在且中断

屏蔽寄存器中相应的位被使能后,中断状态寄存器中特定的位才会被更新。在增强的中断处理模式中,只要事件存

在,不必考虑中断屏蔽寄存器中相应位的内容,中断状态寄存器中特定的位就会被更新。在任何情况下,对特定的

事件来说,中断屏蔽寄存器中各个位都会使能一次中断。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc