2019

计算机组成原理 ·实验报告·

专 业:

信息安全

班 级:

学 号:

姓 名:

电 话:

邮 件:

完成日期:

计算机科学与技术学院

�

华 中 科 技 大 学 课 程 实 验 报 告

目录

1 CPU 设计实验........................................................................................ 2

1.1

1.2

1.3

1.4

设计要求...............................................................................................................2

方案设计...............................................................................................................2

1.2.1 设计单周期 MIPS CPU 数据通路............................................................ 2

1.2.2 设计单周期 MIPS CPU 硬布线控制器.................................................... 4

1.2.3 设计多周期 MIPS CPU 数据通路............................................................ 7

1.2.4 设计多周期 MIPS CPU 微程序控制器.................................................... 7

1.2.5 设计多周期 MIPS CPU 硬布线控制器.................................................. 10

实验步骤.............................................................................................................10

1.3.1 构建单周期 CPU 数据通路.................................................................... 10

1.3.2 构建单周期 CPU 硬布线控制器............................................................ 10

1.3.3 构建多周期 CPU 数据通路.....................................................................11

1.3.4 构建多周期 CPU 微程序控制器............................................................ 12

1.3.5 构建多周期 CPU 硬布线控制器............................................................ 14

测试与分析.........................................................................................................17

1.4.1 单周期 CPU 执行 sort.hex 测试程序......................................................17

1.4.2 多周期 CPU(微程序)执行 sort.hex 测试程序...................................17

1.4.3 多周期 CPU(硬布线)执行 sort.hex 测试程序...................................18

2 总结与心得..........................................................................................19

2.1

2.2

实验总结.............................................................................................................19

实验心得.............................................................................................................19

参考文献................................................................................................... 20

I

�

华 中 科 技 大 学 课 程 实 验 报 告

1 CPU 设计实验

1.1 设计要求

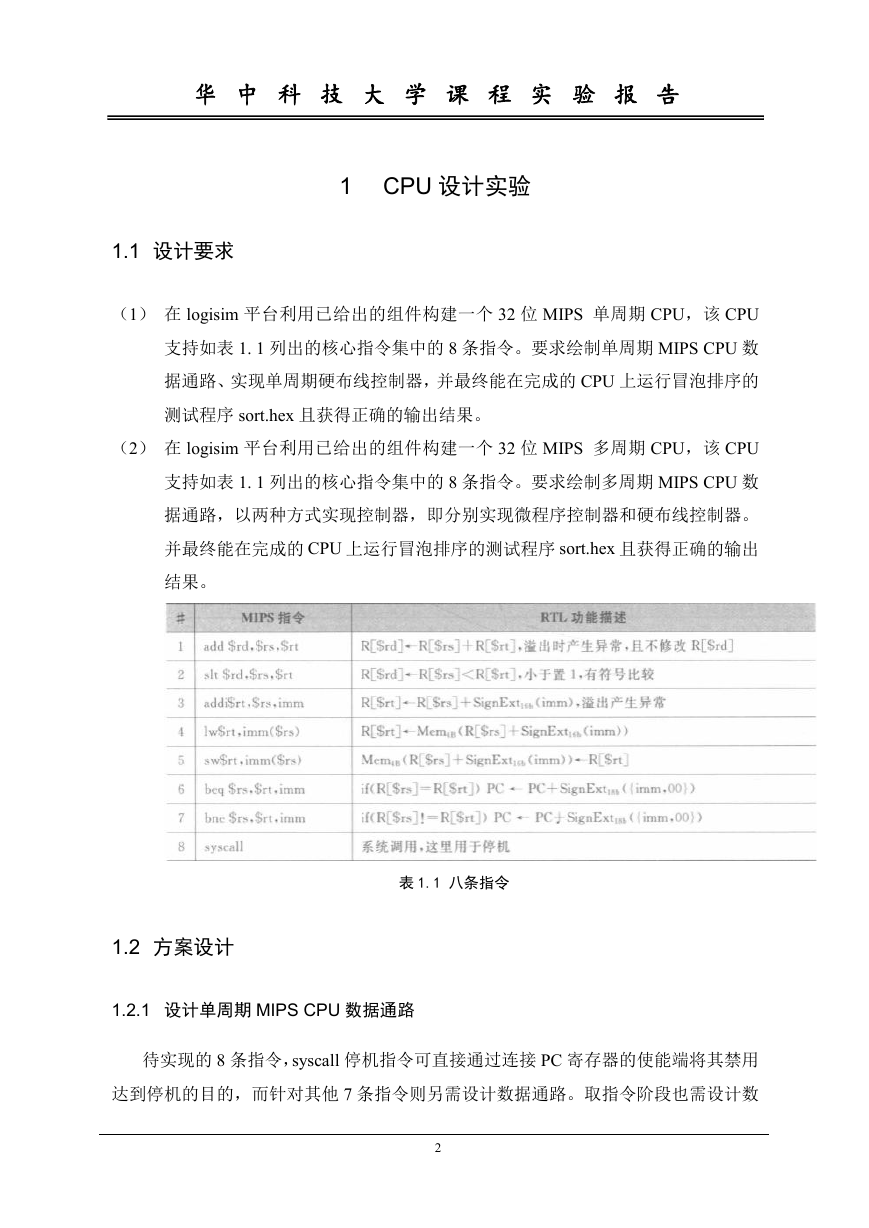

(1) 在 logisim 平台利用已给出的组件构建一个 32 位 MIPS 单周期 CPU,该 CPU

支持如表 1. 1 列出的核心指令集中的 8 条指令。要求绘制单周期 MIPS CPU 数

据通路、实现单周期硬布线控制器,并最终能在完成的 CPU 上运行冒泡排序的

测试程序 sort.hex 且获得正确的输出结果。

(2) 在 logisim 平台利用已给出的组件构建一个 32 位 MIPS 多周期 CPU,该 CPU

支持如表 1. 1 列出的核心指令集中的 8 条指令。要求绘制多周期 MIPS CPU 数

据通路,以两种方式实现控制器,即分别实现微程序控制器和硬布线控制器。

并最终能在完成的 CPU 上运行冒泡排序的测试程序 sort.hex 且获得正确的输出

结果。

表 1.1 八条指令

1.2 方案设计

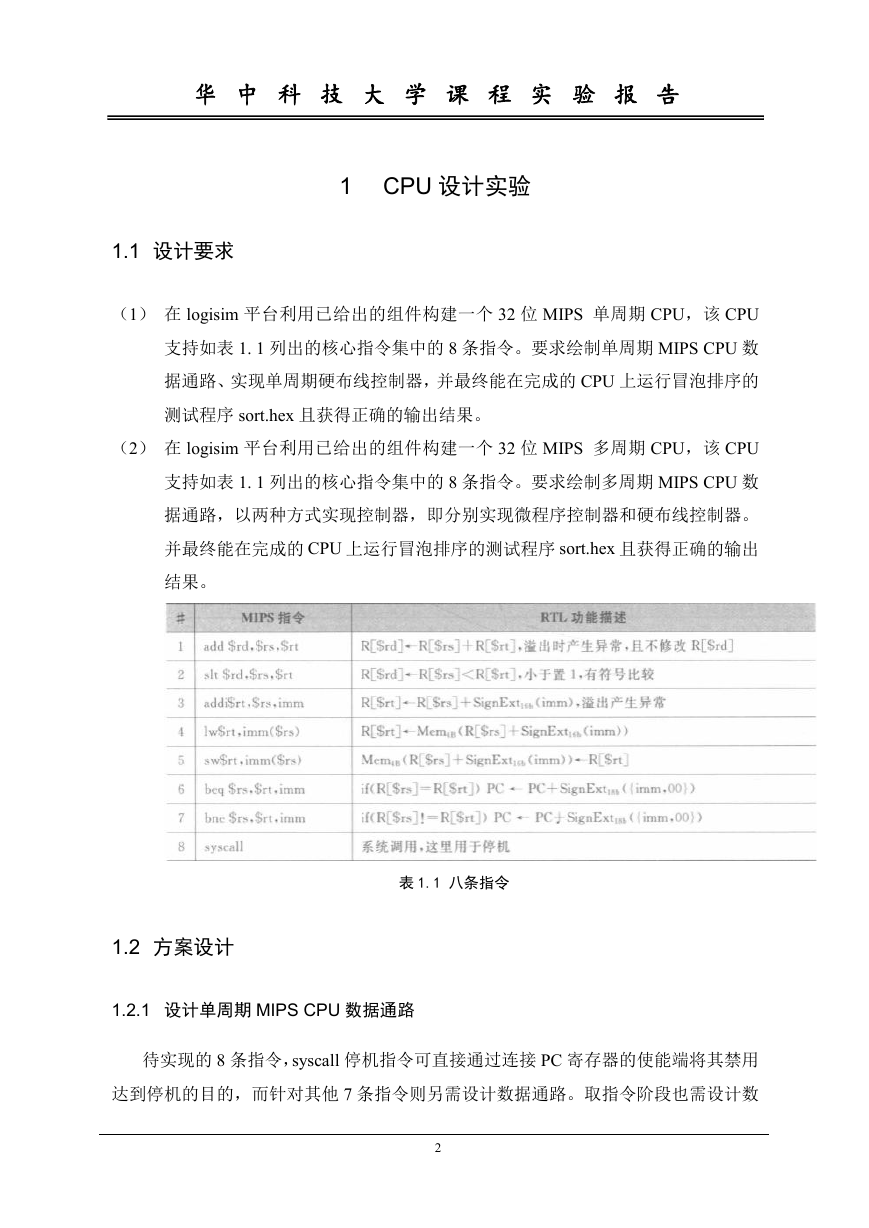

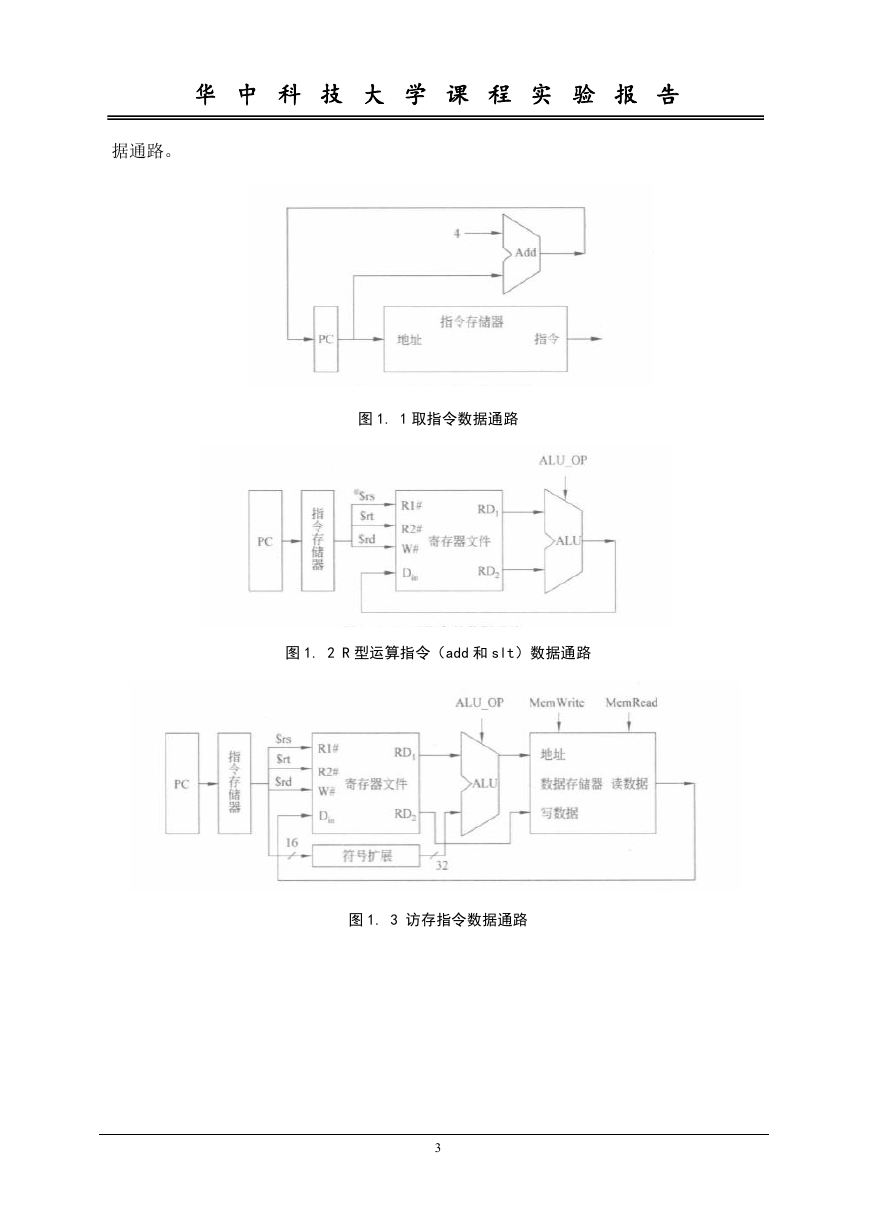

1.2.1 设计单周期 MIPS CPU 数据通路

待实现的 8 条指令,syscall 停机指令可直接通过连接 PC 寄存器的使能端将其禁用

达到停机的目的,而针对其他 7 条指令则另需设计数据通路。取指令阶段也需设计数

2

�

华 中 科 技 大 学 课 程 实 验 报 告

据通路。

图 1. 1 取指令数据通路

图 1. 2 R 型运算指令(add 和 slt)数据通路

图 1. 3 访存指令数据通路

3

�

华 中 科 技 大 学 课 程 实 验 报 告

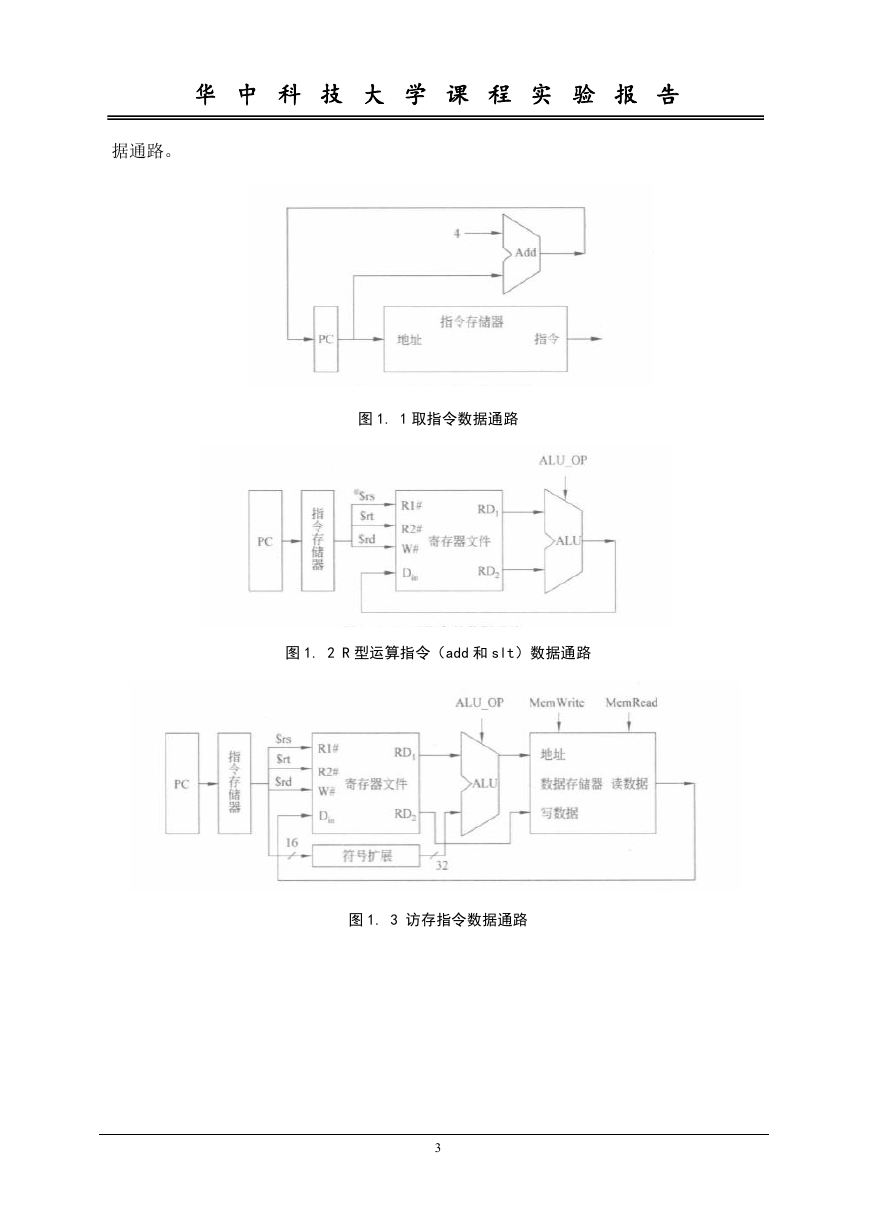

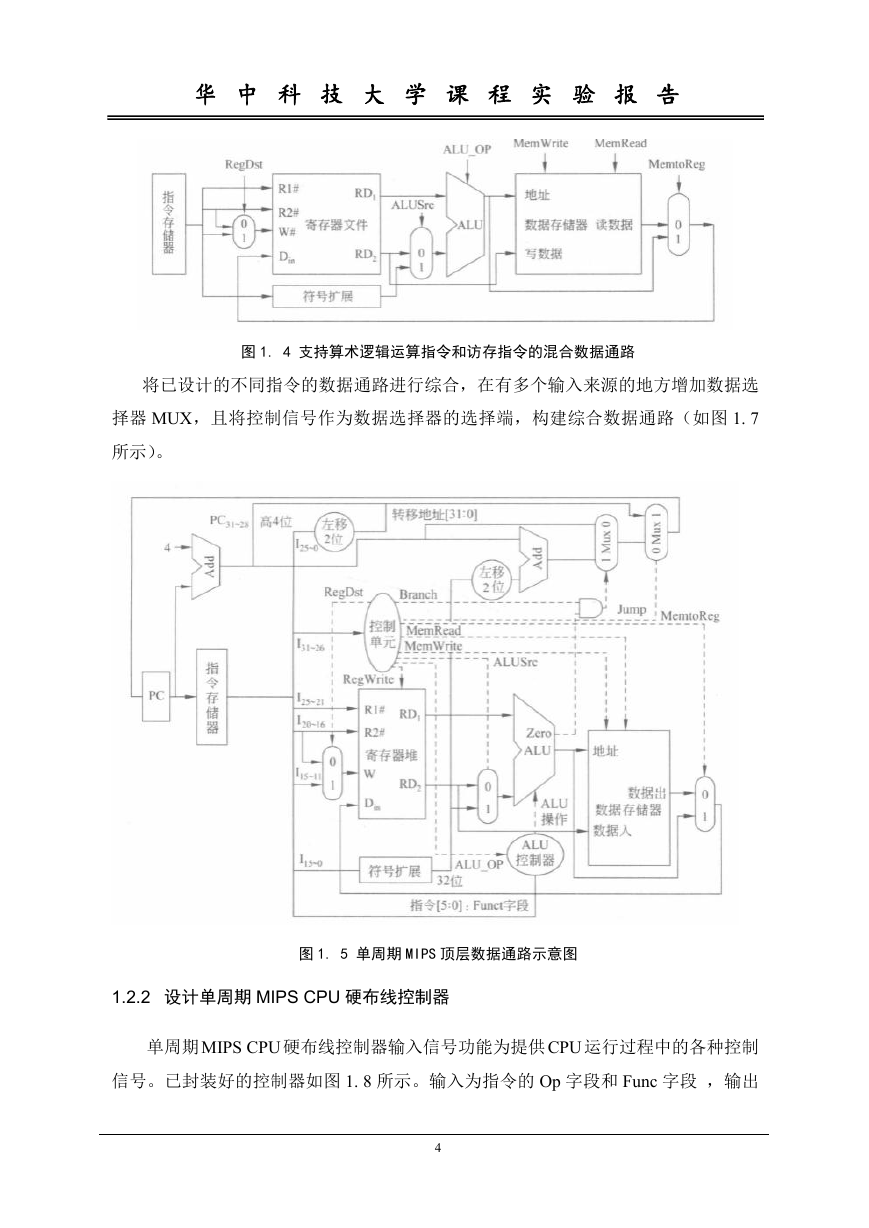

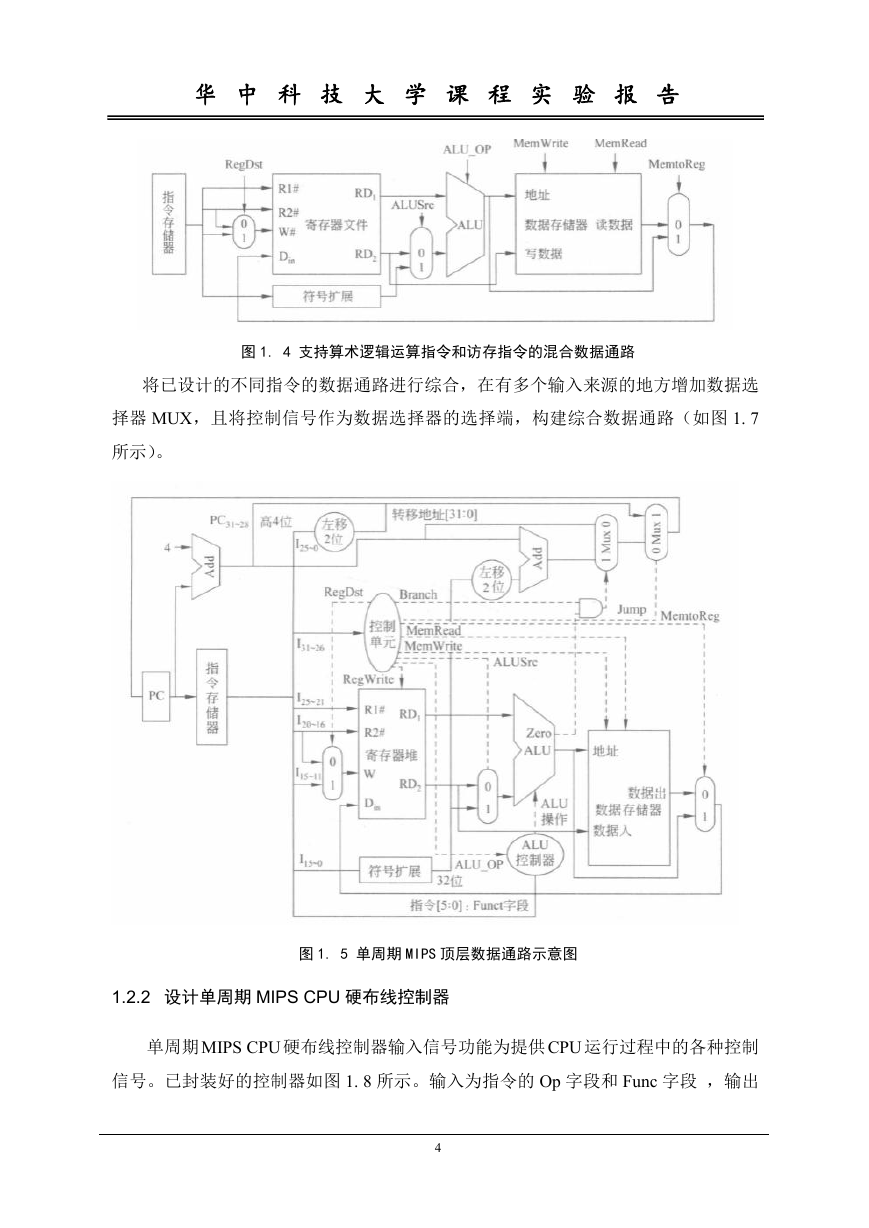

图 1. 4 支持算术逻辑运算指令和访存指令的混合数据通路

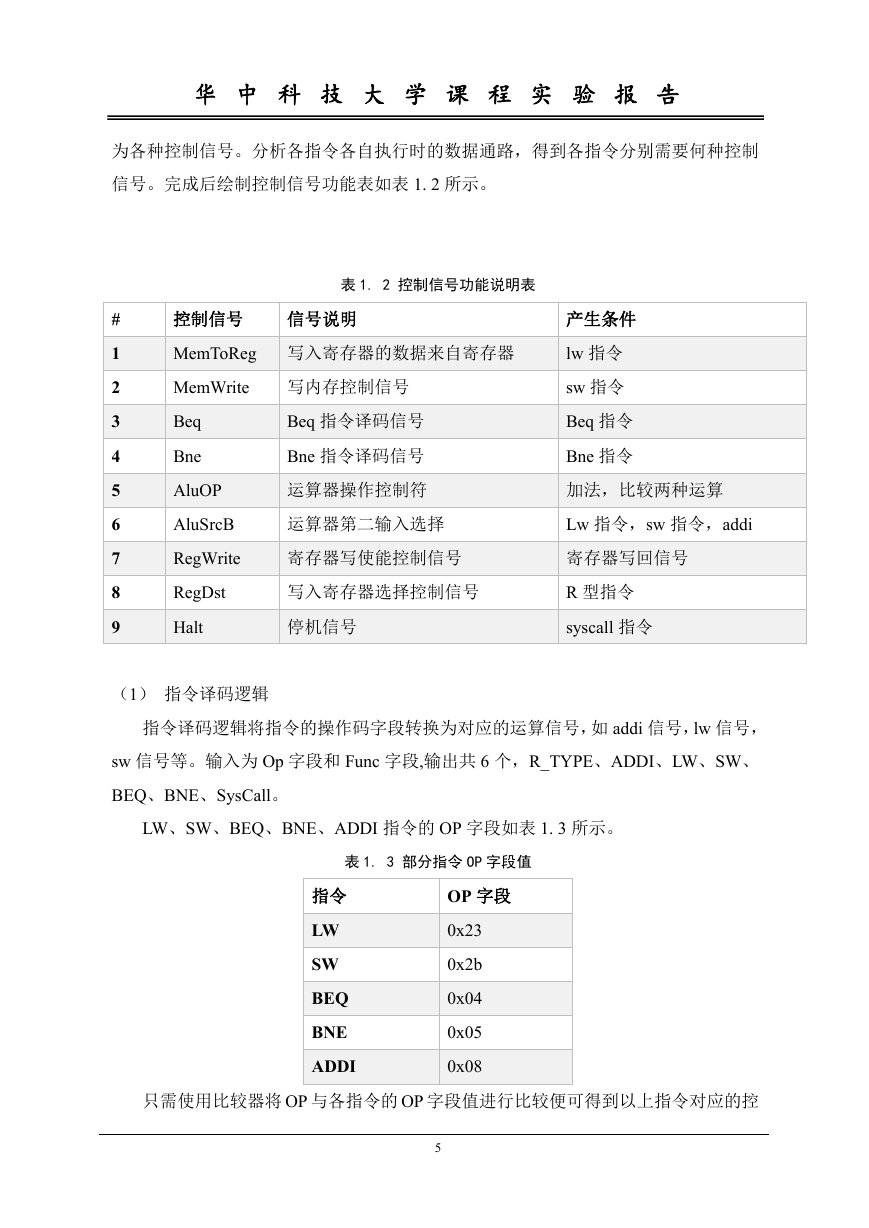

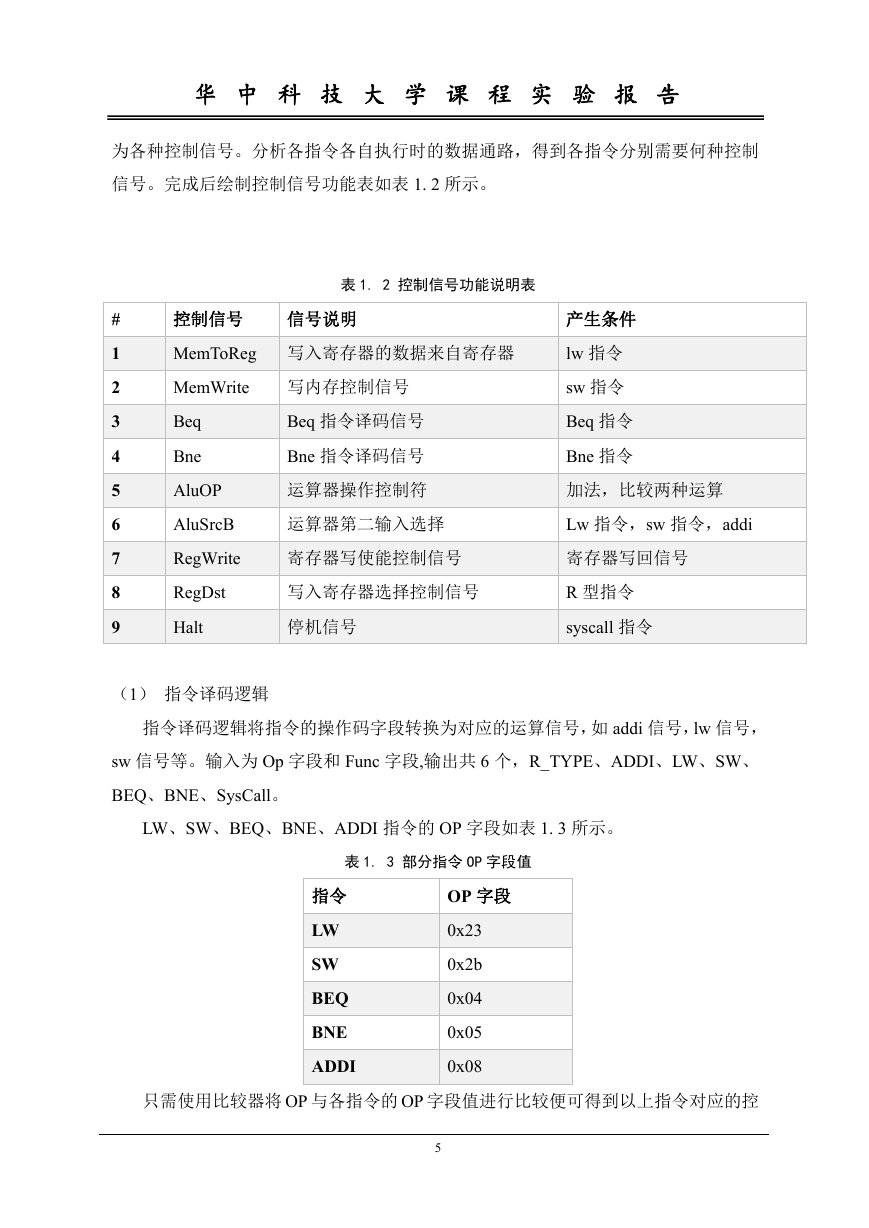

将已设计的不同指令的数据通路进行综合,在有多个输入来源的地方增加数据选

择器 MUX,且将控制信号作为数据选择器的选择端,构建综合数据通路(如图 1. 7

所示)。

图 1. 5 单周期 MIPS 顶层数据通路示意图

1.2.2 设计单周期 MIPS CPU 硬布线控制器

单周期MIPS CPU 硬布线控制器输入信号功能为提供CPU 运行过程中的各种控制

信号。已封装好的控制器如图 1. 8 所示。输入为指令的 Op 字段和 Func 字段 ,输出

4

�

华 中 科 技 大 学 课 程 实 验 报 告

为各种控制信号。分析各指令各自执行时的数据通路,得到各指令分别需要何种控制

信号。完成后绘制控制信号功能表如表 1. 2 所示。

表 1. 2 控制信号功能说明表

控制信号

信号说明

写内存控制信号

Beq 指令译码信号

Bne 指令译码信号

MemToReg 写入寄存器的数据来自寄存器

MemWrite

Beq

Bne

AluOP

AluSrcB

RegWrite

RegDst

Halt

写入寄存器选择控制信号

运算器操作控制符

运算器第二输入选择

寄存器写使能控制信号

停机信号

产生条件

lw 指令

sw 指令

Beq 指令

Bne 指令

加法,比较两种运算

Lw 指令,sw 指令,addi

寄存器写回信号

R 型指令

syscall 指令

#

1

2

3

4

5

6

7

8

9

(1) 指令译码逻辑

指令译码逻辑将指令的操作码字段转换为对应的运算信号,如 addi 信号,lw 信号,

sw 信号等。输入为 Op 字段和 Func 字段,输出共 6 个,R_TYPE、ADDI、LW、SW、

BEQ、BNE、SysCall。

LW、SW、BEQ、BNE、ADDI 指令的 OP 字段如表 1. 3 所示。

表 1. 3 部分指令 OP 字段值

指令

LW

SW

BEQ

BNE

ADDI

OP 字段

0x23

0x2b

0x04

0x05

0x08

只需使用比较器将 OP 与各指令的 OP 字段值进行比较便可得到以上指令对应的控

5

�

华 中 科 技 大 学 课 程 实 验 报 告

制信号。

而对于信号 R_TYPE,它是 R 型运算指令的控制信号,对于本次设计而言,共 3 条

R 型指令,分别为 ADD、SLT、SysCall。其中 ADD 和 SLT 指令为 R 型运算指令。故

R_TYPE 在 SysCall 对应的指令无效,而 ADD 对应的控制信号或 SLT 对应的控制信号

有效时有效。即 R_TYPE = ( ADD + SLT ) & ~SysCall 。故需先得到 ADD、SLT 和

SysCall 信号。R 型指令的 OP 字段为 0,具体功能需看 Func 字段,故需再次查阅实验

包内的《MIPS32 指令手册》得到 ADD、SLT、SysCall 指令的 Func 字段值,如表 1. 4

所示。

表 1. 4 部分 R 型指令 Func 字段值

指令

ADD

SLT

SysCall

Func 字段

0x20

0x2a

0x0c

只需将 FUNC 和各指令对应字段比较相等的信号与 OP 和 0 比较相等的信号作与

运算即可得到相应的控制信号 ADD、SLT 和 SysCall。

这样,我们就得到了 R_TYPE、ADDI、LW、SW、BEQ、BNE、SysCall 这 6 个

指令译码信号。

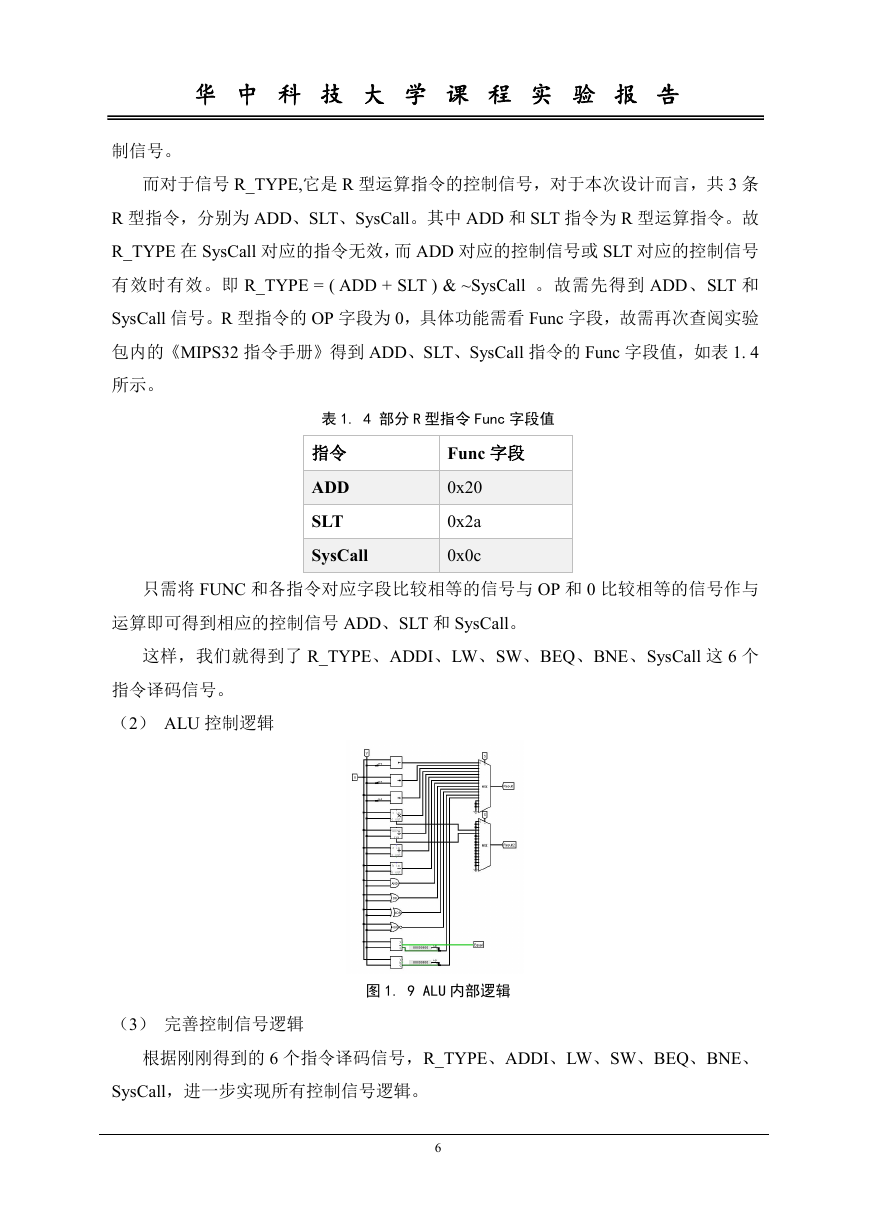

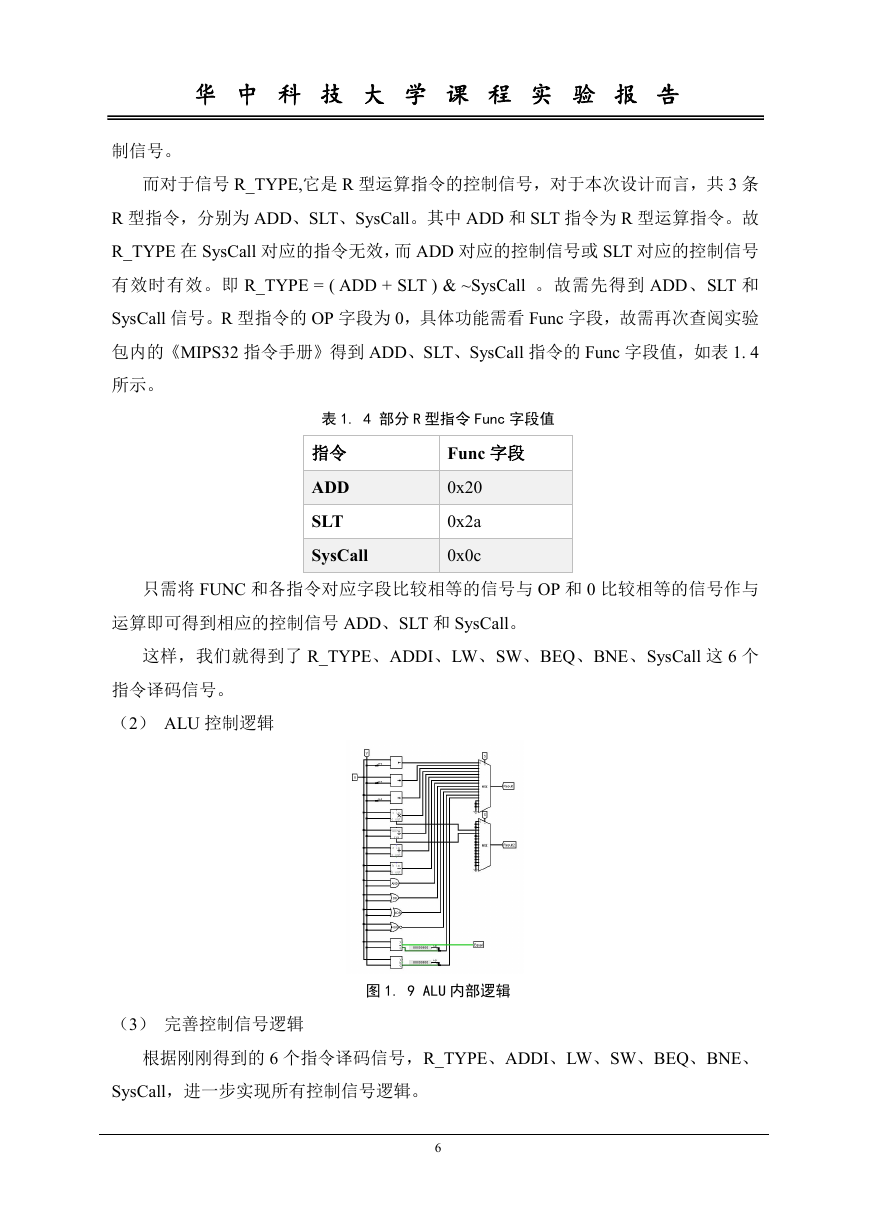

(2) ALU 控制逻辑

(3) 完善控制信号逻辑

图 1. 9 ALU 内部逻辑

根据刚刚得到的 6 个指令译码信号,R_TYPE、ADDI、LW、SW、BEQ、BNE、

SysCall,进一步实现所有控制信号逻辑。

6

�

华 中 科 技 大 学 课 程 实 验 报 告

根据表 1. 2 控制信号功能说明表可知哪些信号在执行哪些指令时起作用,将对应

的指令译码信号进行逻辑或即可得到对应控制信号。

需额外指出的是,寄存器写回操作包括 R_TYPE 指令、ADDI 指令和 LW 指令。

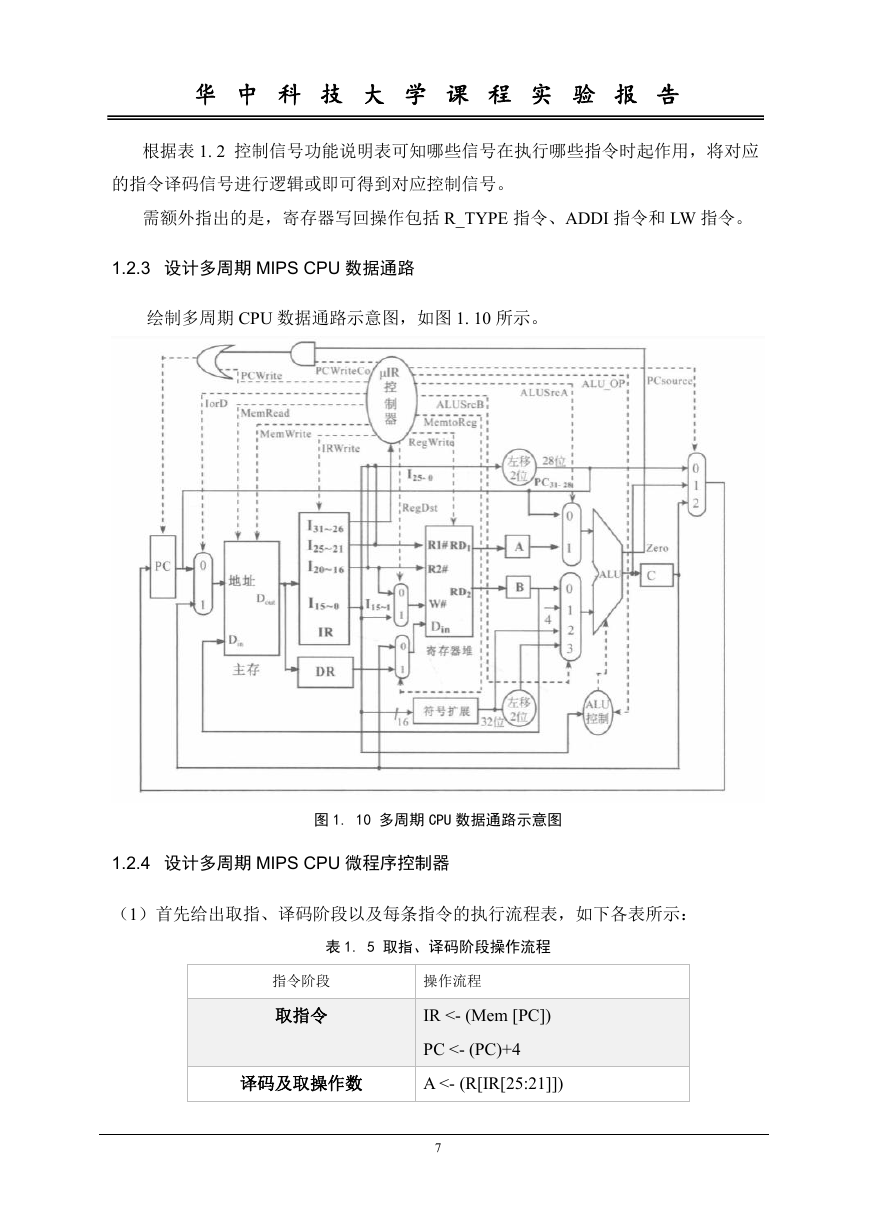

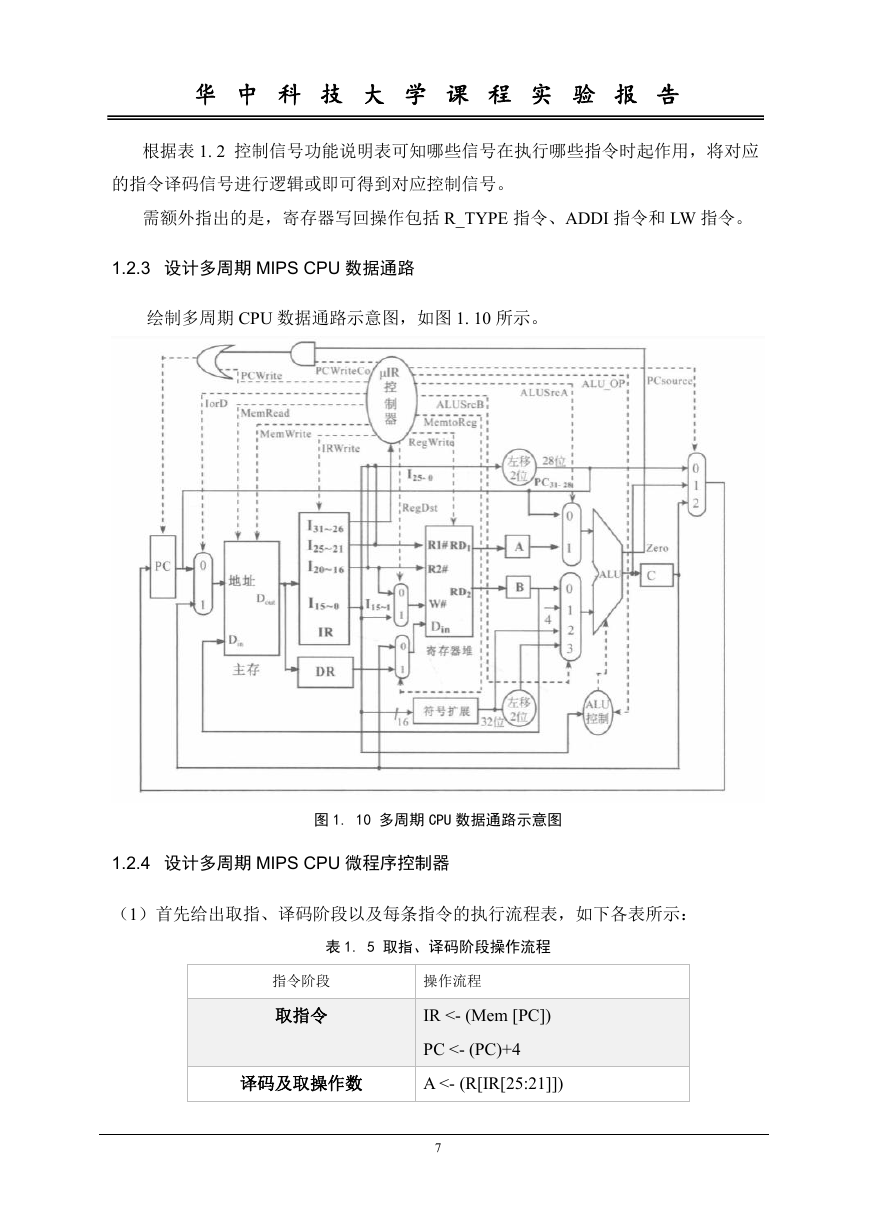

1.2.3 设计多周期 MIPS CPU 数据通路

绘制多周期 CPU 数据通路示意图,如图 1. 10 所示。

图 1. 10 多周期 CPU 数据通路示意图

1.2.4 设计多周期 MIPS CPU 微程序控制器

(1)首先给出取指、译码阶段以及每条指令的执行流程表,如下各表所示:

表 1. 5 取指、译码阶段操作流程

指令阶段

取指令

译码及取操作数

操作流程

IR <- (Mem [PC])

PC <- (PC)+4

A <- (R[IR[25:21]])

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc