Documentation Overview

DW_apb_ssi Release Notes

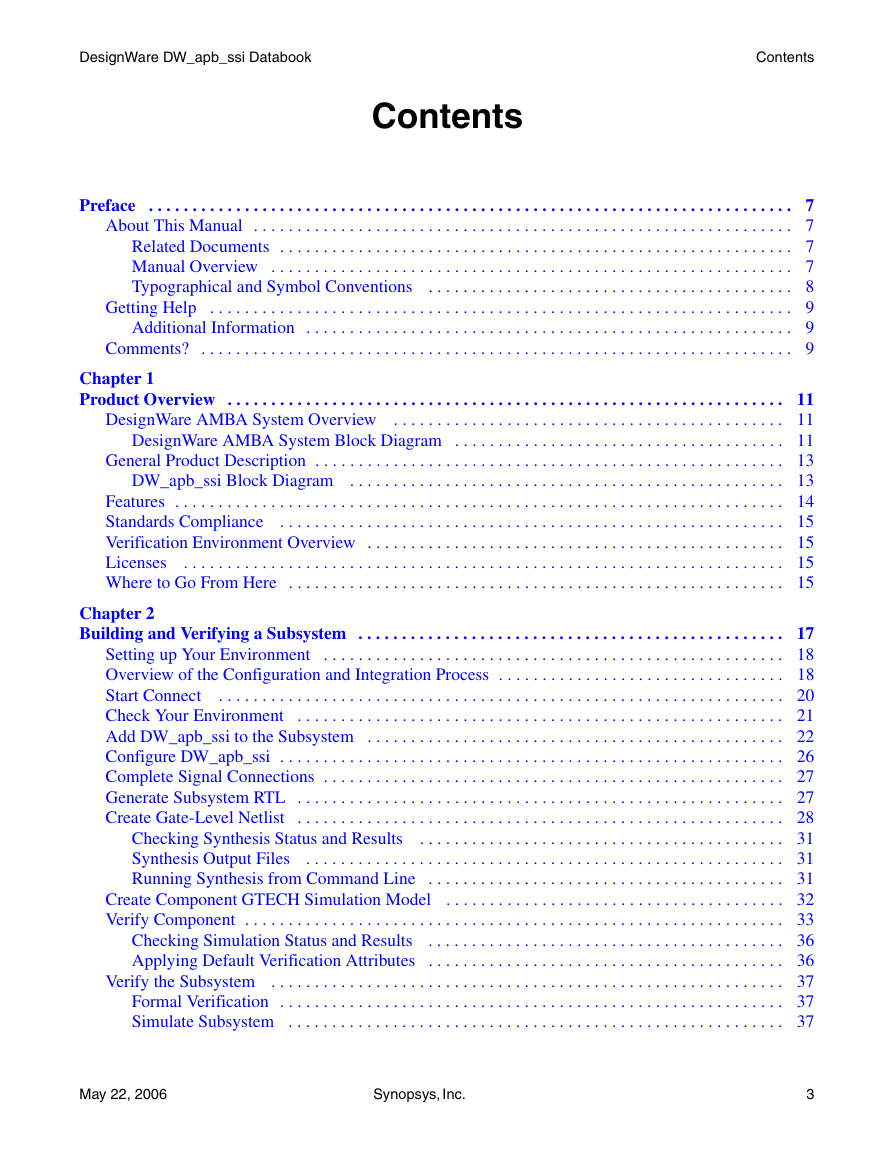

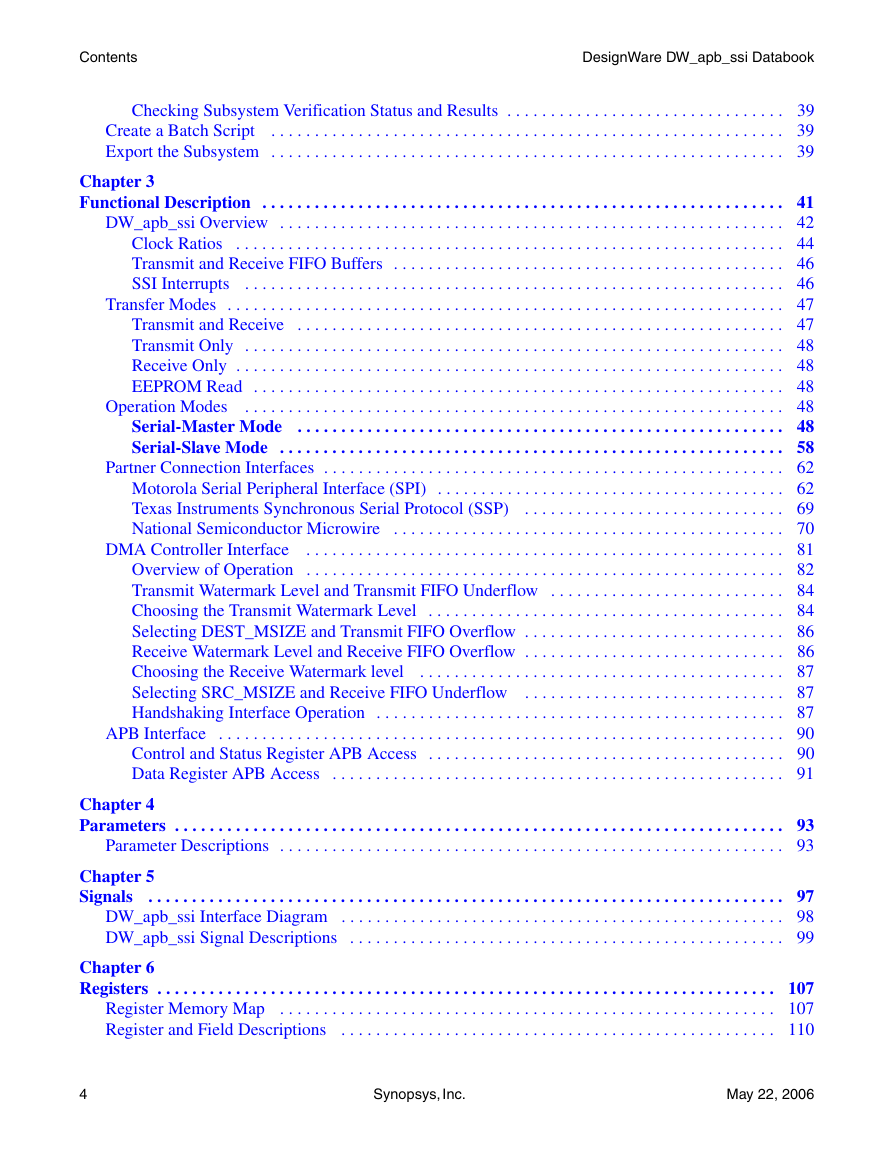

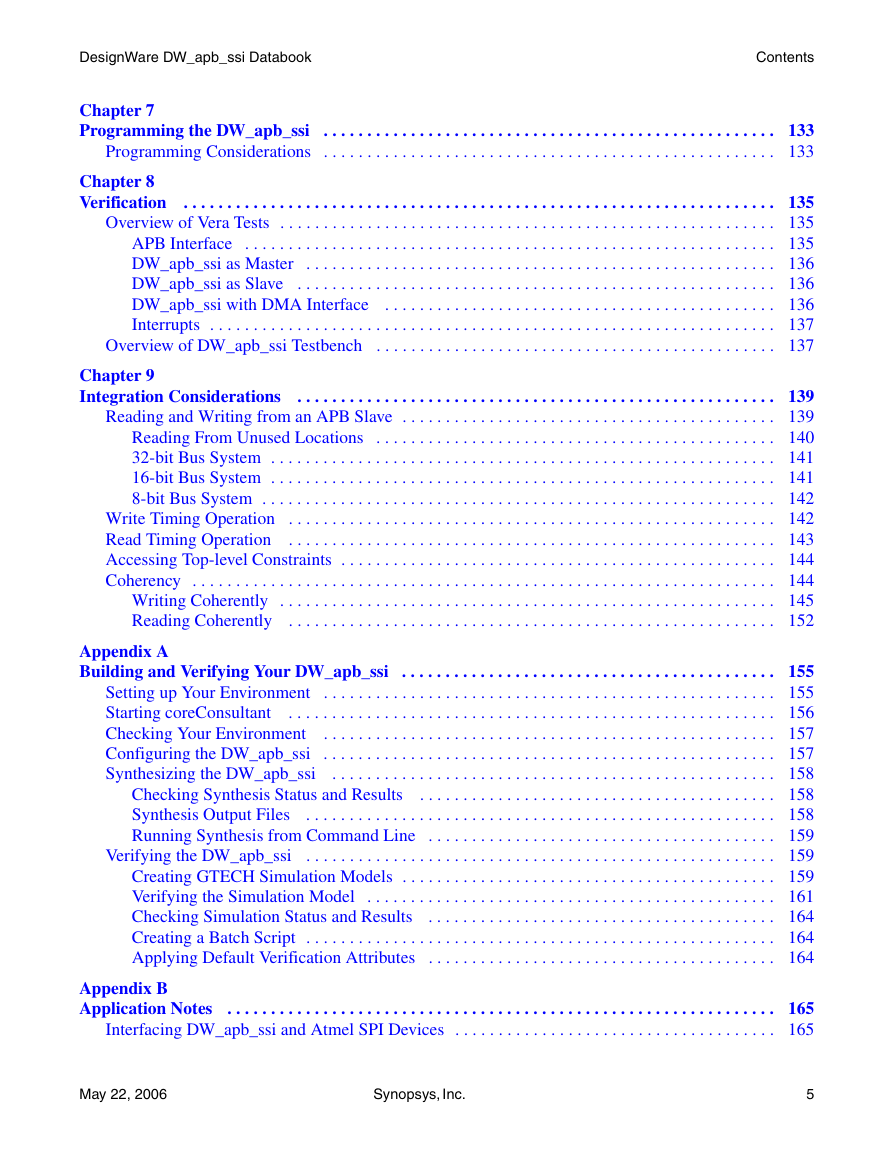

Contents

Preface

About This Manual

Related Documents

Manual Overview

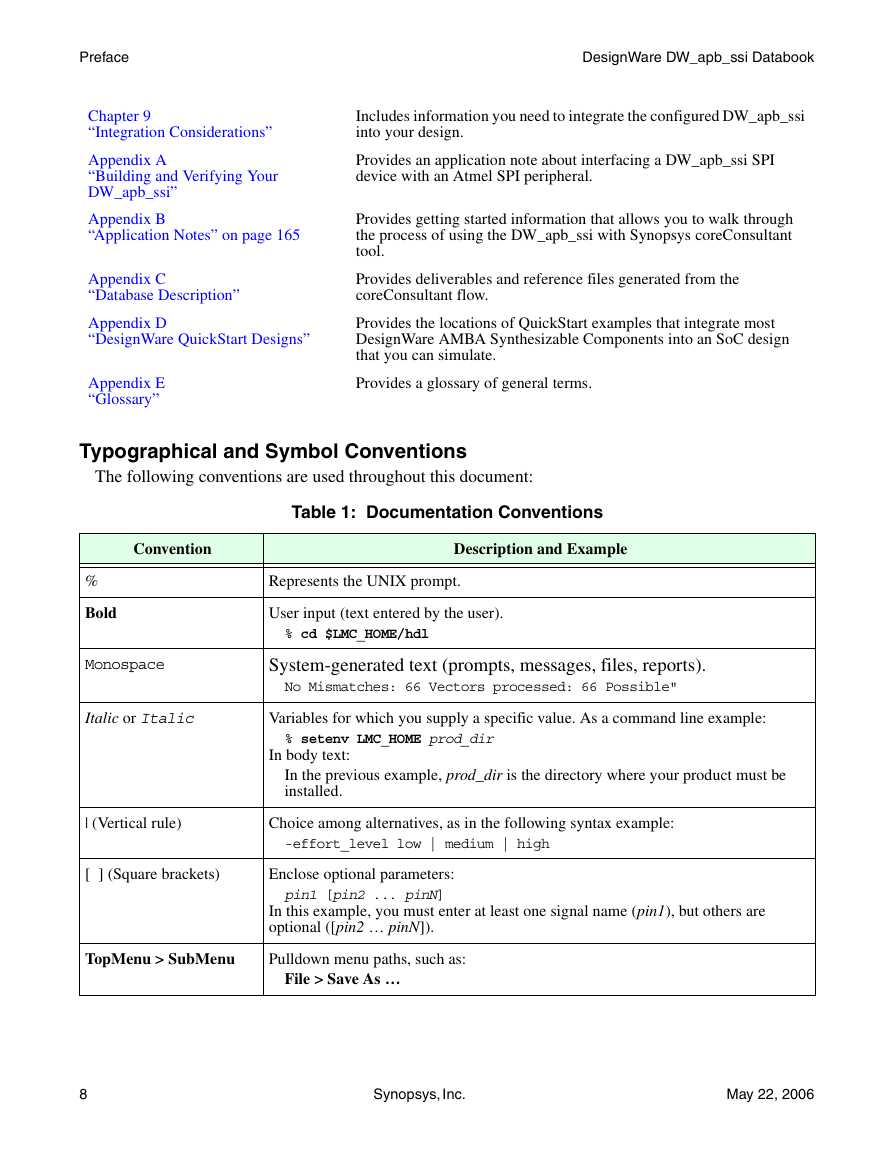

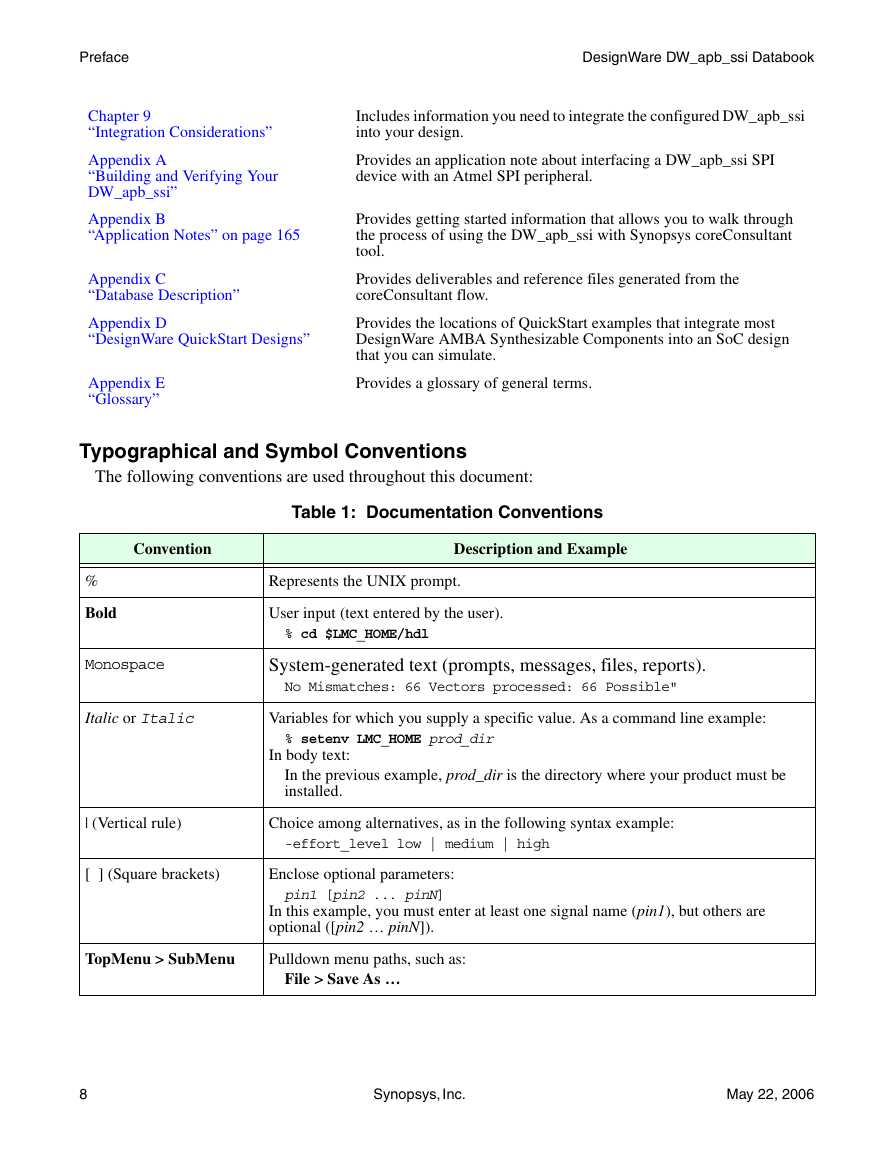

Typographical and Symbol Conventions

Table 1: Documentation Conventions

Getting Help

Additional Information

Comments?

1 Product Overview

DesignWare AMBA System Overview

DesignWare AMBA System Block Diagram

Figure 1: Example of DW_apb_ssi in a Complete System

General Product Description

DW_apb_ssi Block Diagram

Figure 2: DW_apb_ssi Block Diagram

Features

Standards Compliance

Verification Environment Overview

Licenses

Where to Go From Here

Table 2: Tool Comparison

2 Building and Verifying a Subsystem

Setting up Your Environment

Overview of the Configuration and Integration Process

Figure 3: Connect Usage Flow

Table 3: Connect Workspace Directory Contents

Start Connect

Check Your Environment

Add DW_apb_ssi to the Subsystem

Figure 4: DW_apb_ssi in Simple Subsystem

Configure DW_apb_ssi

Complete Signal Connections

Generate Subsystem RTL

Create Gate-Level Netlist

Checking Synthesis Status and Results

Synthesis Output Files

Running Synthesis from Command Line

Create Component GTECH Simulation Model

Verify Component

Checking Simulation Status and Results

Applying Default Verification Attributes

Verify the Subsystem

Formal Verification

Simulate Subsystem

Checking Subsystem Verification Status and Results

Create a Batch Script

Export the Subsystem

3 Functional Description

DW_apb_ssi Overview

Figure 5: Hardware/Software Slave Selection

Clock Ratios

Figure 6: Maximum sclk_out/ssi_clk Ratio

Figure 7: Slave ssi_clk/sclk_in Ratio

Transmit and Receive FIFO Buffers

SSI Interrupts

Transfer Modes

Transmit and Receive

Transmit Only

Receive Only

EEPROM Read

Operation Modes

Serial-Master Mode

Figure 8: DW_apb_ssi Configured as Master Device

Figure 9: Arbitration Between Multiple Serial Masters

Figure 10: Glue Logic for Controlling Logic Level on Master ss_in_n Input

Figure 11: DW_apb_ssi Master SPI/SSP Transfer Flow

Figure 12: DW_apb_ssi Master Microwire Transfer Flow

Serial-Slave Mode

Figure 13: DW_apb_ssi Configured as Slave Device

Figure 14: DW_apb_ssi Slave SPI/SSP Transfer Flow

Partner Connection Interfaces

Motorola Serial Peripheral Interface (SPI)

Figure 15: SPI Serial Format (SCPH = 0)

Figure 16: SPI Serial Format Continuous Transfers (SCPH = 0)

Figure 17: SPI Serial Format (SCPH = 1)

Figure 18: SPI Serial Format Continuous Transfer (SCPH = 1)

Figure 19: FIFO Status for Transmit & Receive SPI and SSP Transfers

Figure 20: FIFO Status for Transmit Only SPI and SSP Transfers

Figure 21: FIFO Status for Receive Only SPI and SSP Transfers

Figure 22: FIFO Status for EEPROM Read Transfer Mode

Texas Instruments Synchronous Serial Protocol (SSP)

Figure 23: SSP Serial Format

Figure 24: SSP Serial Format Continuous Transfer

National Semiconductor Microwire

Figure 25: Single DW_apb_ssi Master Microwire Serial Transfer (MDD=0)

Figure 26: FIFO Status for Single Microwire Transfer (receiving data frame)

Figure 27: Continuous Nonsequential Microwire Transfer (receiving data frame)

Figure 28: FIFO Status for Nonsequential Microwire Transfer (receiving data frame)

Figure 29: Continuous Sequential Microwire Transfer (receiving data frame)

Figure 30: FIFO Status for Sequential Microwire Transfer (receiving data frame)

Figure 31: Single Microwire Transfer (transmitting data frame)

Figure 32: FIFO Status for Single Microwire Transfer (transmitting data frame)

Figure 33: Continuous Microwire Transfer (transmitting data frame)

Figure 34: FIFO Status for Continuous Microwire Transfer (transmitting data frame)

Figure 35: Continuous Microwire Transfer with Handshaking (transmitting data frame)

Figure 36: FIFO Status for Microwire Control Word Transfer

Figure 37: Microwire Control Word

Figure 38: Single DW_apb_ssi Slave Microwire Serial Transfer (MDD=0)

Figure 39: FIFO Status for Single Microwire Transfer (receiving data frame)

Figure 40: Single DW_apb_ssi Slave Microwire Serial Transfer (MDD=1)

Figure 41: FIFO Status for Single Microwire Transfer (transmitting data frame)

DMA Controller Interface

Overview of Operation

Figure 42: Breakdown of DMA Transfer into Burst Transactions

Figure 43: Breakdown of DMA Transfer into Single and Burst Transactions

Transmit Watermark Level and Transmit FIFO Underflow

Choosing the Transmit Watermark Level

Figure 44: Case 1 Watermark Levels

Figure 45: Case 2 Watermark Levels

Selecting DEST_MSIZE and Transmit FIFO Overflow

Receive Watermark Level and Receive FIFO Overflow

Choosing the Receive Watermark level

Selecting SRC_MSIZE and Receive FIFO Underflow

Figure 46: SSI Receive FIFO

Handshaking Interface Operation

Figure 47: Burst Transaction - pclk = hclk

Figure 48: Back-to-Back Burst Transactions - hclk = 2*pclk

Figure 49: Single Transaction

Figure 50: Burst Transaction + 3 Back-to-Back Singles - hclk = 2*pclk

APB Interface

Control and Status Register APB Access

Data Register APB Access

4 Parameters

Parameter Descriptions

Table 4: Top-Level Parameters

Table 5: Derived Configuration Parameters

5 Signals

DW_apb_ssi Interface Diagram

Figure 51: DW_apb_ssi Interface Diagram

DW_apb_ssi Signal Descriptions

Table 6: DW_apb_ssi Signal Description

6 Registers

Register Memory Map

Table 7: Memory Map of DW_apb_ssi

Register and Field Descriptions

Table 8: DFS Decode

Table 9: CFS Decode

Table 10: TFT Decode

Table 11: RFT

Table 12: DMA Transmit Data Level

Table 13: DMATDL Decode Value

Table 14: DMARDL Decode Value

7 Programming the DW_apb_ssi

Programming Considerations

8 Verification

Overview of Vera Tests

APB Interface

DW_apb_ssi as Master

DW_apb_ssi as Slave

DW_apb_ssi with DMA Interface

Interrupts

Overview of DW_apb_ssi Testbench

Figure 52: DW_apb_ssi Testbench

Figure 53:

9 Integration Considerations

Reading and Writing from an APB Slave

Reading From Unused Locations

Figure 54: Read/Write Locations for Different APB Bus Data Widths

32-bit Bus System

16-bit Bus System

8-bit Bus System

Write Timing Operation

Figure 55: APB Write Transaction

Read Timing Operation

Figure 56: APB Read Transaction

Accessing Top-level Constraints

Coherency

Writing Coherently

Table 15: Upper Byte Generation

Figure 57: Coherent Loading - Identical Synchronous Clocks

Figure 58: Coherent Loading - Identical Synchronous Clocks

Figure 59: Coherent Loading - Synchronous Clocks

Figure 60: Coherent Loading - Synchronous Clocks

Figure 61: Coherent Loading - Asynchronous Clocks

Figure 62: Coherent Loading - Asynchronous Clocks

Reading Coherently

Table 16: Lower Byte Generation

Figure 63: Coherent Registering - Synchronous Clocks

Figure 64: Coherent Registering - Synchronous Clocks

Figure 65: Coherency and Shadow Registering - Asynchronous Clocks

Figure 66: Transfer to Shadowing Registers- Asynchronous Clocks

A Building and Verifying Your DW_apb_ssi

Setting up Your Environment

Starting coreConsultant

Checking Your Environment

Configuring the DW_apb_ssi

Synthesizing the DW_apb_ssi

Checking Synthesis Status and Results

Synthesis Output Files

Running Synthesis from Command Line

Verifying the DW_apb_ssi

Creating GTECH Simulation Models

Verifying the Simulation Model

Checking Simulation Status and Results

Creating a Batch Script

Applying Default Verification Attributes

B Application Notes

Interfacing DW_apb_ssi and Atmel SPI Devices

Synopsys SPI Operation

Figure 67: DW_apb_ssi SPI: Continuous Transfer where SCPH = 0 and SCPOL = 0

Figure 68: DW_apb_ssi SPI: Continuous Transfer where SCPH=1 and SCPOL=1

Atmel SPI Operation

Figure 69: Atmel SPI: Continuous Transfer with SCPH=0 and SCPOL=0

Interoperability between DW_apb_ssi and Atmel Devices

C Database Description

Design/HDL Files

RTL-Level Files

Table 17: RTL-Level Files

Simulation Model Files

Table 18: Simulation Model Files

Register Map Files

Table 19: Header Files

Synthesis Files

Table 20: Synthesis Files

Verification Reference Files

Table 21: Verification Reference Files

D DesignWare QuickStart Designs

QuickStart Example Designs

E Glossary

Index

A

B

C

D

E

F

G

H

I

L

M

N

O

P

R

S

T

U

V

W

Z

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc