1. GENERAL DESCRIPTION

W25X10/20/40/80 支持标准串行外设接口(SPI),以及一个高性能的双输出 SPI,他使用四

个引脚:串行时钟,片选,I / O 和串行数据输出。SPI 时钟频率高达 75MHz 的支持,允许

相当于 150MHz 的时钟速率当使用快速阅读的双输出指令时。这些传输速率可比那些 8 位

和 16 位并行闪存。

保持脚,写保护引脚和可编程 WR ITE 保护,顶部或底部的阵列控制功能,提供进一步的控

制的灵活性。此外,该器件支持 JEDEC 标准的制造商和设备标识

2. FEATURES

- W25X10:1M 位/128K 字节(131,072)

- W25X20:2M 位/256K 字节(262,144)

- W25X40:4M 位/512K 字节(524,288)

- W25X80:8M 位/1M 字节(1,048,576)

- 256 字节每可编程页

- 统一的 4K 字节扇区/64K 字节块

数据传输高达 150 Mbits /秒

- 75 兆赫的时钟操作

- 快速阅读双输出指令

- 自动递增读能力

灵活的架构与 4KB 扇区

- 扇区擦除(4K 字节)

- 块擦除(64K 字节)

- 页编程达 256 字节<2ms

- 高达 100,000 次擦除/写周期

- 保留 20 年

•低功耗,宽

温度范围

- 单 2.7 至 3.6V 电源供电

- 积极 5 毫安目前,1μA 电源下(典型值)

- 40°至+85°C 的工作范围

软件和硬件写保护

- 写保护内存的全部或部分

- 启用/禁用/ WP 引脚保护

- 顶部或底部阵列保护

•空间高效的包装

- 8 引脚 SOIC150-MIL(W25X10/20/40)

- 8 引脚 SOIC208 万(W25X40/80)

�

- 8 引脚 PDIP300-MIL(W25X10/20/40/80)

- 8 针 WSON 的引脚 6x5 毫米(W25X10/20/40/80 的)

封装类型

当时这个数据公布并非所有的封装类型已经定稿。联系华邦确认之前,本规范设计这些软件

包的可用性。 W25X10,W25X20

和 W25X40 提供 8 引脚塑料 150 MIL 无线 DTH 的 SOIC(封装代码 SN)图所示

1A。 W25X40 和 W25X80 则提供 8 引脚塑料宽 208 密耳 SOIC(封装代码 SS)在图 1b 所

示。所有零件将提供 6X5 毫米 WSON 的(封装代码,ZP)和 300-MIL DIP(封装代码,DA)。

在此资料包图和尺寸说明。

7. PIN DESCRIPTION

片选(/ CS)

SPI 片选引脚(/ CS)启用和禁用设备操作。当/ CS 为高的设备被取消和串行数据输出(DO)

引脚为高阻抗。取消时,器件的功耗将是待机时的水平,除非内部的擦除,编程或状态寄存

器的指令实在执行。当/ CS 为低电平的设备将被选择,电力消耗量将增加至活跃水平并且指

示可以写入和从设备读取数据。接通电源后,/ CS 必须从高拉低,这样一个新的指令才会被

接受。 / CS 输入必须跟踪 VCC 电供应水平(见“写保护”和图 20)。如果需要上拉电阻那

么/ CS 拉高可以做到这一点

串行数据输出(DO)

串行输出脚(DO)提供一种方法来串行的读取器件的数据和状态,数据在 CLK(串行时钟

输入引脚)的下降沿被依次输出,

写保护(/WP)

写保护引脚(/WP)可用于防止状态寄存器被改写。在与状态寄存器的块保护(BP2,BP1

和 BP0)位及状态寄存器保护(SRP)位一起使用,可以完成部分或整个存储器阵列的硬件

保障。 / WP 引脚为低电平有效。

HOLD(/HOLD)

/ HOLD 引脚允许器件被暂停,当他被主动的选择。当/HOLD 置低,同时/ CS 为低,/DO 引

脚为高阻态,同时/DIO 和/CLK 引脚上的信号将被忽略(不关心),/HOLD 置高,器件操作

可以继续。/ HOLD 功能可能是有用的,当多个设备共享同一个 SPI 信号。 (“保持功能”)

�

串行时钟(CLK)

SPI 串行时钟输入(CLK)引脚提供串行输入和输出操作的时序。 (“见

SPI 的“行动”)

串行数据输入/输出(DIO)

串行数据输入/输出(DIO)引脚提供一种指令,地址,数据串行的写入到设备的方法。串

行时钟(CLK)输入引脚的上升沿锁存数据。快速阅读双路输出指令(Fast Read Dual Output

instruction)执行时 DIO 引脚也被用作输出

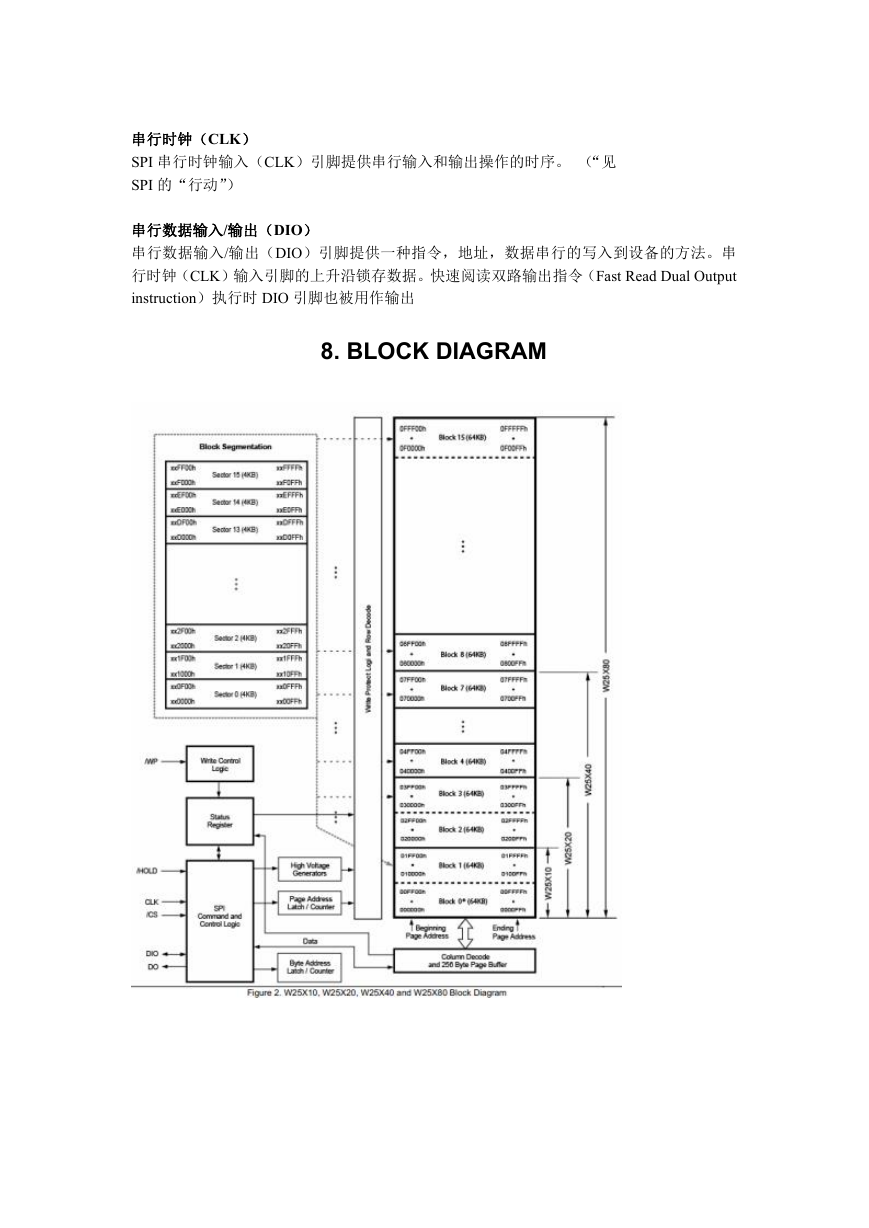

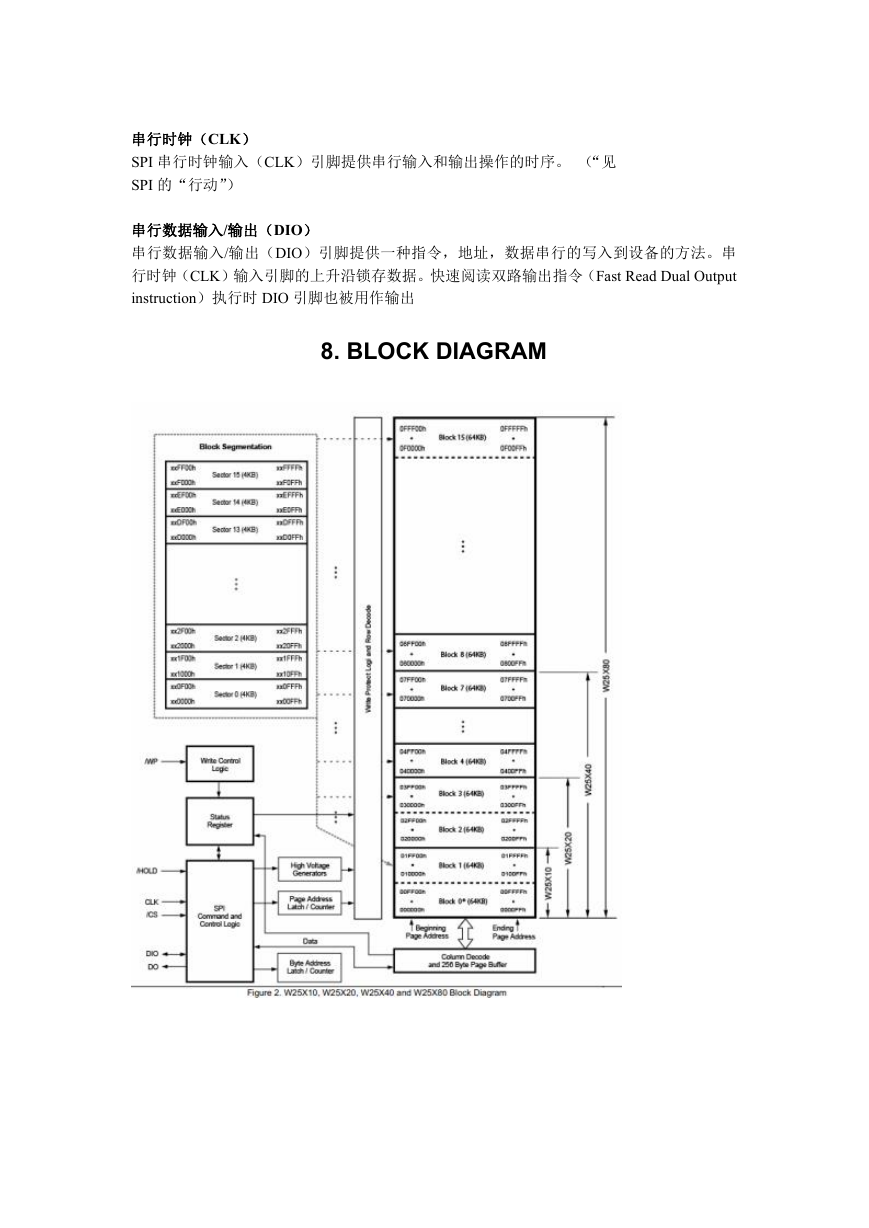

8. BLOCK DIAGRAM

�

9. FUNCTIONAL DESCRIPTION

9.1 SPI 的操作

9.1.1 SPI 的模式

W25X10/20/40/80 通过一个 SPI 兼容总线被访问,总线组成的四个信号:串行时钟(CLK),

芯片选择(/ CS)的访问,串行数据输入/输出(DIO)和串行数据输出(DO)。支持 SPI 总

线操作模式 0(0,0)和 3(1,1)。SPI 总线主模式 0 和模式 3 的主要区别是关于 spi 主机在 standby

模式并且没有传送数据到 flash 时 CLK 的标准状态。为 Mode0 CLK 信号通常是低电平。模

式 3 CLK 信号通常是高电平。在这两种情况下都是 CLK 的上升沿采样 DIO 引脚上的数据。

DO 和 DIO 引脚上的数据在 CLK 的下降沿输出。

9.1.2 双输出的 SPI

W25X10/20/40/80 支持双输出操作,当使用双输出“快速阅读”(3B 十六进制)指令。此功

能允许将数据从 flash 进行传输以两倍与标准的 SPI 的速度。这个指令是为上电时快速从

Flash 上载代码到 RAM 或应用程序缓存代码段到 RAM 中执行。双输出功能,只允许 spi 输

入引脚作为输出在这个指令期间。所有其他操作使用单一输出信号的标准 SPI 接口。

9.1.3 保持功能

/ HOLD 信号允许暂停 W25X10/20/40/80 操作当它被选择时(/ CS 为低)。 / HOLD 功能可

能在 SPI 数据和时钟信号与其他设备共享的情况下非常有用。例如,考虑如果页面缓冲区写

操作还没结束,这时如果被高优先级中断并且他也需要使用 SPI 总线。在这种情况下,/ HOLD

功能可以保存指令和数据的状态到缓冲区中,一旦总线再次可用则可以恢复它离开的时状

态。

启动/HOLD 的条件,设备必须选择/ CS 为低电平。如果 CLK 信号已经是低电平,那么/ HOLD

信号的下降沿来到时将进入/HOLD 模式。如果 CLK 不是低电平,那么下一个 CLK 的下降

边缘/ HOLD 条件将被激活。

/HOLD 模式的终止,如果 CLK 信号已经是低电平那么/ HOLD 信号的上升沿会结束该状态。

如果 CLK 是不是低,那么下一个 CLK 的下降边缘/ HOLD 条件会终止。

在/HOLD 状态下,串行数据输出(DO)是高阻抗,并且串行数据输入/输出(DIO)和串行

时钟(CLK)被忽略。片选(/ CS)信号应保持低电平在整个/ HOLD 操作期间,以避免重

置设备的内部逻辑状态

9.2 写保护

使用非易失性内存的应用程序必须考虑到噪声和其他不利的制度条件下,可能会危及数据的

�

完整性的可能性。为了解决这一问题的 W25X10/20/40/80 提供了几种方法,以防止意外的写

入数据。

9.2.1 写保护功能

•器件复位,当 VCC 低于阈值。

•上电后延迟写禁用,。

•写使能/禁用指令。

•编程和擦除后自动禁止写入。

•软件的写保护使用状态寄存器。

•硬件的写保护使用状态寄存器和/ WP 引脚。

•使用掉电指令写保护。

在电源上电或 掉电或 VCC 低于阈值的 VWI 时 W25X10/20/40/80 将保持复位状态,(见上

电时序和电压等级和图 20)。复位时,所有的操作被禁止,所有的指令也不被识别。上电期

间和 VCC 电压超过 VWI 之后,所有编程和擦除相关的指令,继续禁用一段时间(tPUW)。

这包括写使能,页编程,扇区擦除,块擦除,芯片擦除和写状态寄存器指令。注意的芯片选

择引脚(/ CS)必须跟踪电源 VCC 供电水平从上电直到 VC-min 的水平同事 tVSL 时间延迟

到达。如果需要在/CS 脚上拉电阻那么打开/CS 能实现这一点

上电后设备自动进入写禁用状态,将状态寄存器写使能锁存器 Status Register Write Enable

Latch(WEL)设置为 0。写启用指令必须发出在扇区擦除,芯片擦除或写状态寄存器指令

之前,那么他才将被接受。在完成程序,擦除或写指令后写使能锁存器(WEL)自动清零

进入到写禁用的状态。

软件控制的写入保护是方便使用写状态寄存器指令和设置状态寄存器保护(SRP)和块保护

(TB, BP2, BP1, and BP0)位。这些状态寄存器位允许部分或所有的内存配置为只读。结合

用于写保护(/ WP)管脚,状态寄存器的变化,可以启用或禁用硬件控制下的。进一步信息,

请参阅状态寄存器。

此外,掉电指令提供了一个额外的写保护级别,所有指令都被忽略,除非释放掉电指令。

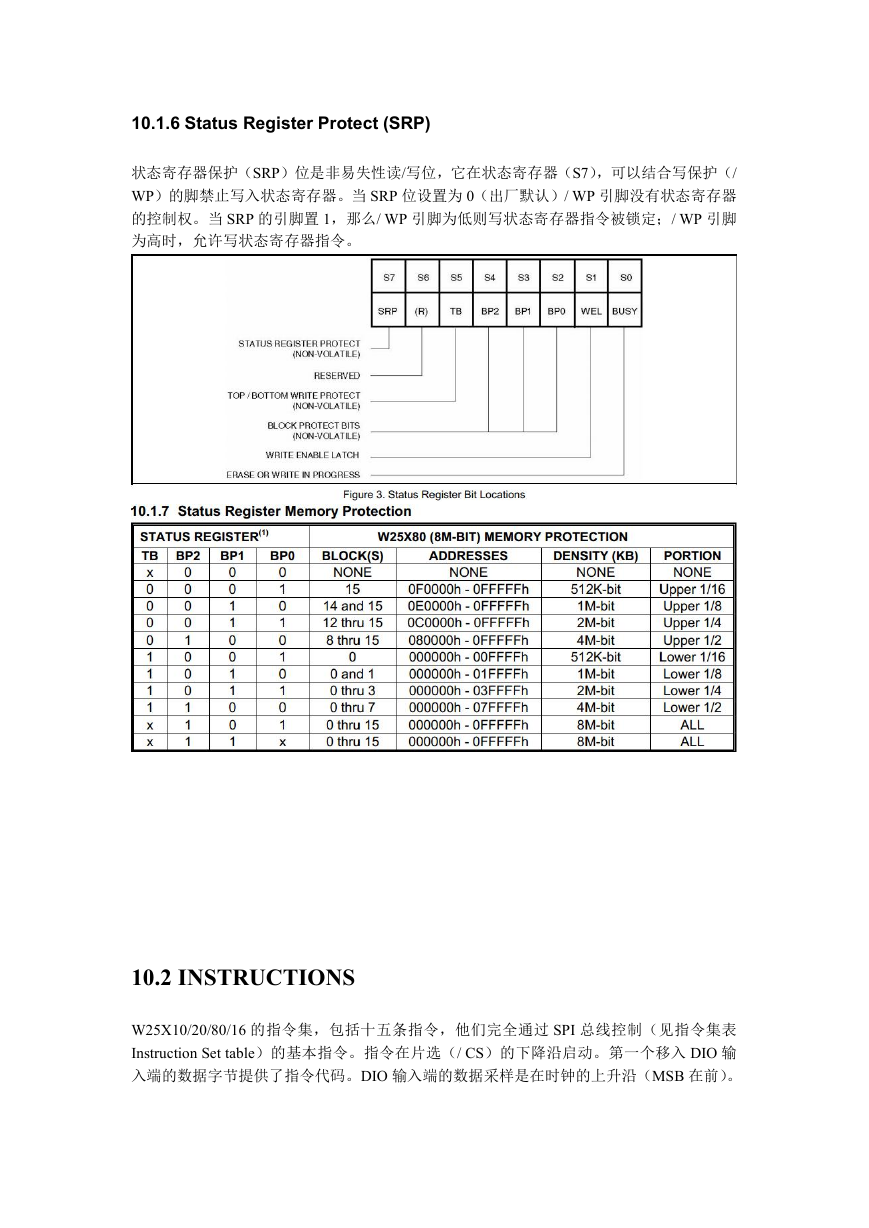

10。控制和状态寄存器

读状态寄存器指令可以用来提供 flash 的可用性状态,如果该设备是写启用或禁用或写保护

状态。写状态寄存器指令可用于配置设备的写保护功能。见 figure3。

�

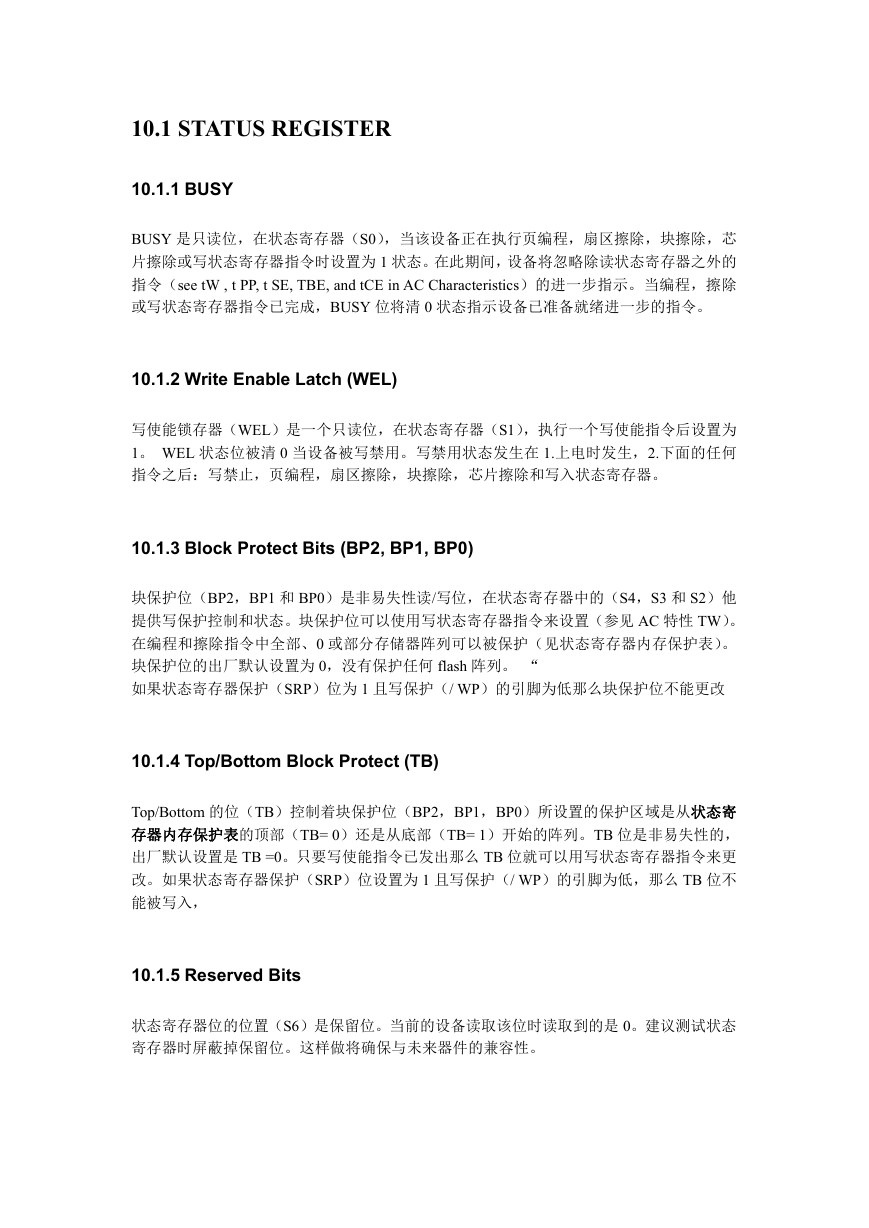

10.1 STATUS REGISTER

10.1.1 BUSY

BUSY 是只读位,在状态寄存器(S0),当该设备正在执行页编程,扇区擦除,块擦除,芯

片擦除或写状态寄存器指令时设置为 1 状态。在此期间,设备将忽略除读状态寄存器之外的

指令(see tW , t PP, t SE, TBE, and tCE in AC Characteristics)的进一步指示。当编程,擦除

或写状态寄存器指令已完成,BUSY 位将清 0 状态指示设备已准备就绪进一步的指令。

10.1.2 Write Enable Latch (WEL)

写使能锁存器(WEL)是一个只读位,在状态寄存器(S1),执行一个写使能指令后设置为

1。 WEL 状态位被清 0 当设备被写禁用。写禁用状态发生在 1.上电时发生,2.下面的任何

指令之后:写禁止,页编程,扇区擦除,块擦除,芯片擦除和写入状态寄存器。

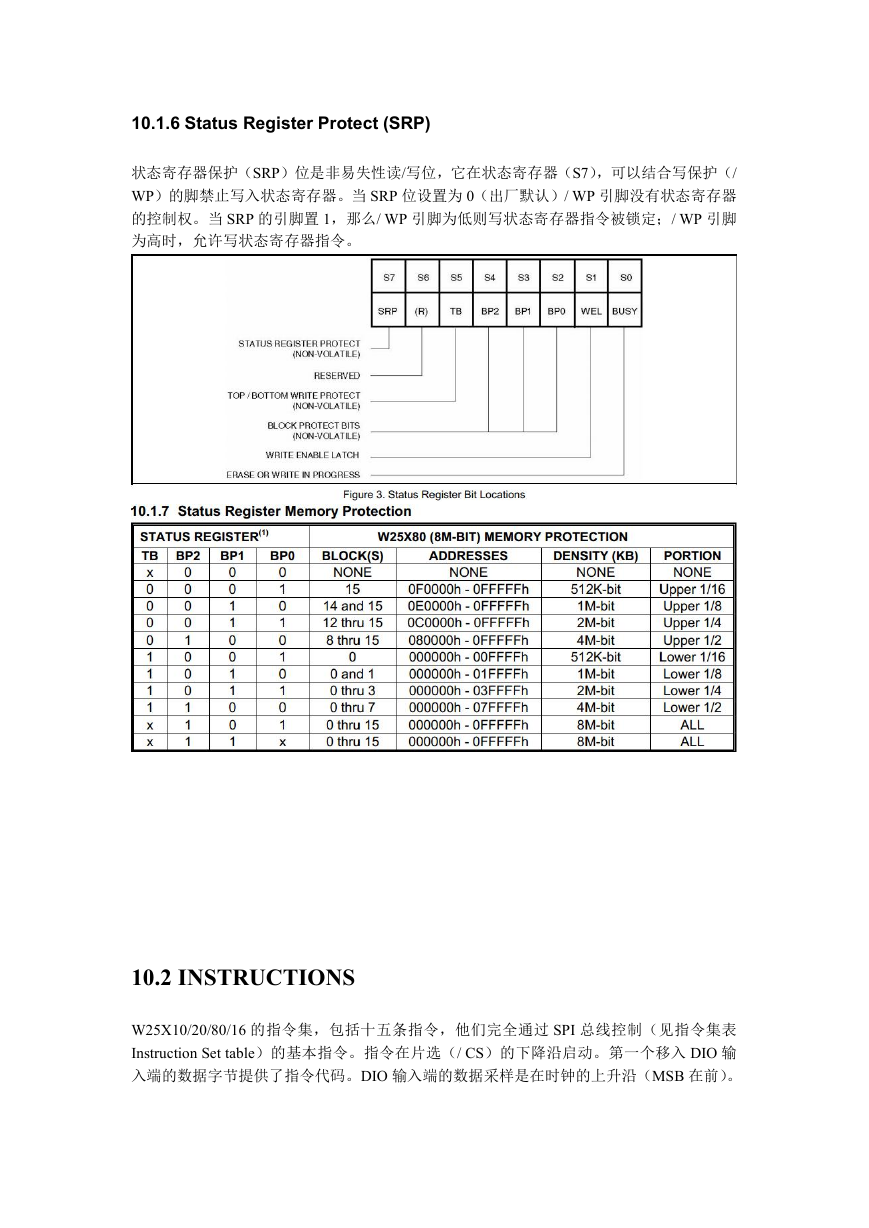

10.1.3 Block Protect Bits (BP2, BP1, BP0)

块保护位(BP2,BP1 和 BP0)是非易失性读/写位,在状态寄存器中的(S4,S3 和 S2)他

提供写保护控制和状态。块保护位可以使用写状态寄存器指令来设置(参见 AC 特性 TW)。

在编程和擦除指令中全部、0 或部分存储器阵列可以被保护(见状态寄存器内存保护表)。

块保护位的出厂默认设置为 0,没有保护任何 flash 阵列。 “

如果状态寄存器保护(SRP)位为 1 且写保护(/ WP)的引脚为低那么块保护位不能更改

10.1.4 Top/Bottom Block Protect (TB)

Top/Bottom 的位(TB)控制着块保护位(BP2,BP1,BP0)所设置的保护区域是从状态寄

存器内存保护表的顶部(TB= 0)还是从底部(TB= 1)开始的阵列。TB 位是非易失性的,

出厂默认设置是 TB =0。只要写使能指令已发出那么 TB 位就可以用写状态寄存器指令来更

改。如果状态寄存器保护(SRP)位设置为 1 且写保护(/ WP)的引脚为低,那么 TB 位不

能被写入,

10.1.5 Reserved Bits

状态寄存器位的位置(S6)是保留位。当前的设备读取该位时读取到的是 0。建议测试状态

寄存器时屏蔽掉保留位。这样做将确保与未来器件的兼容性。

�

10.1.6 Status Register Protect (SRP)

状态寄存器保护(SRP)位是非易失性读/写位,它在状态寄存器(S7),可以结合写保护(/

WP)的脚禁止写入状态寄存器。当 SRP 位设置为 0(出厂默认)/ WP 引脚没有状态寄存器

的控制权。当 SRP 的引脚置 1,那么/ WP 引脚为低则写状态寄存器指令被锁定;/ WP 引脚

为高时,允许写状态寄存器指令。

10.2 INSTRUCTIONS

W25X10/20/80/16 的指令集,包括十五条指令,他们完全通过 SPI 总线控制(见指令集表

Instruction Set table)的基本指令。指令在片选(/ CS)的下降沿启动。第一个移入 DIO 输

入端的数据字节提供了指令代码。DIO 输入端的数据采样是在时钟的上升沿(MSB 在前)。

�

指示长短不一,从单字节到几个字节也有可能跟随着地址字节,数据字节,空字节(不必在

乎),并在某些情况下结合起来。指令在边缘/ CS 的上升沿完成。每个指令的时序图如图 4

至 19。所有读指令能在任意时钟位后完成。然而,所有指令写入,编程或擦除必须完成一

个字节边界(驱动一个完整的 8 位后,CS 拉高),否则指令将被终止。这一功能进一步防止

意外的写入。此外,内存正在编程或擦除,或状态寄存器被写入时,除了读状态寄存器的所

有指令都将被忽略,直到编程或擦除周期已经完成。

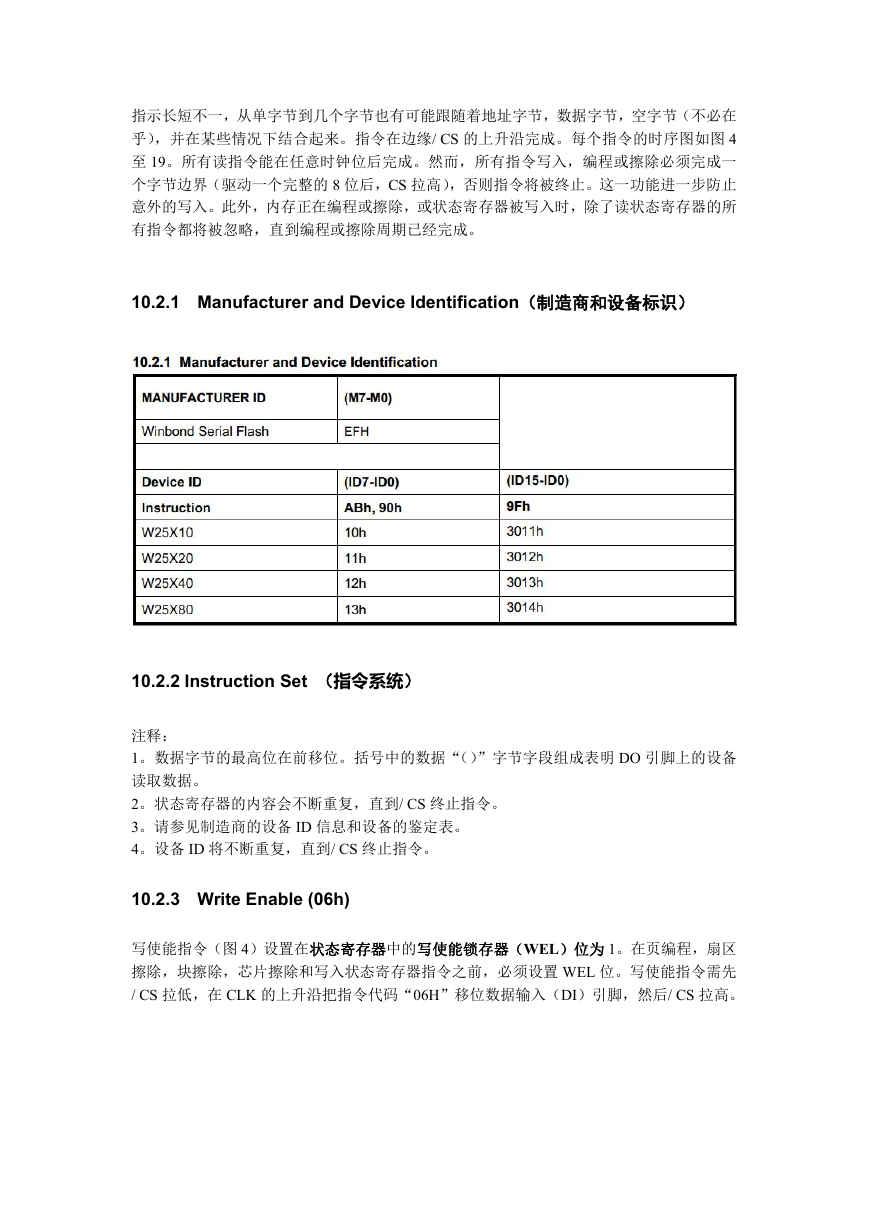

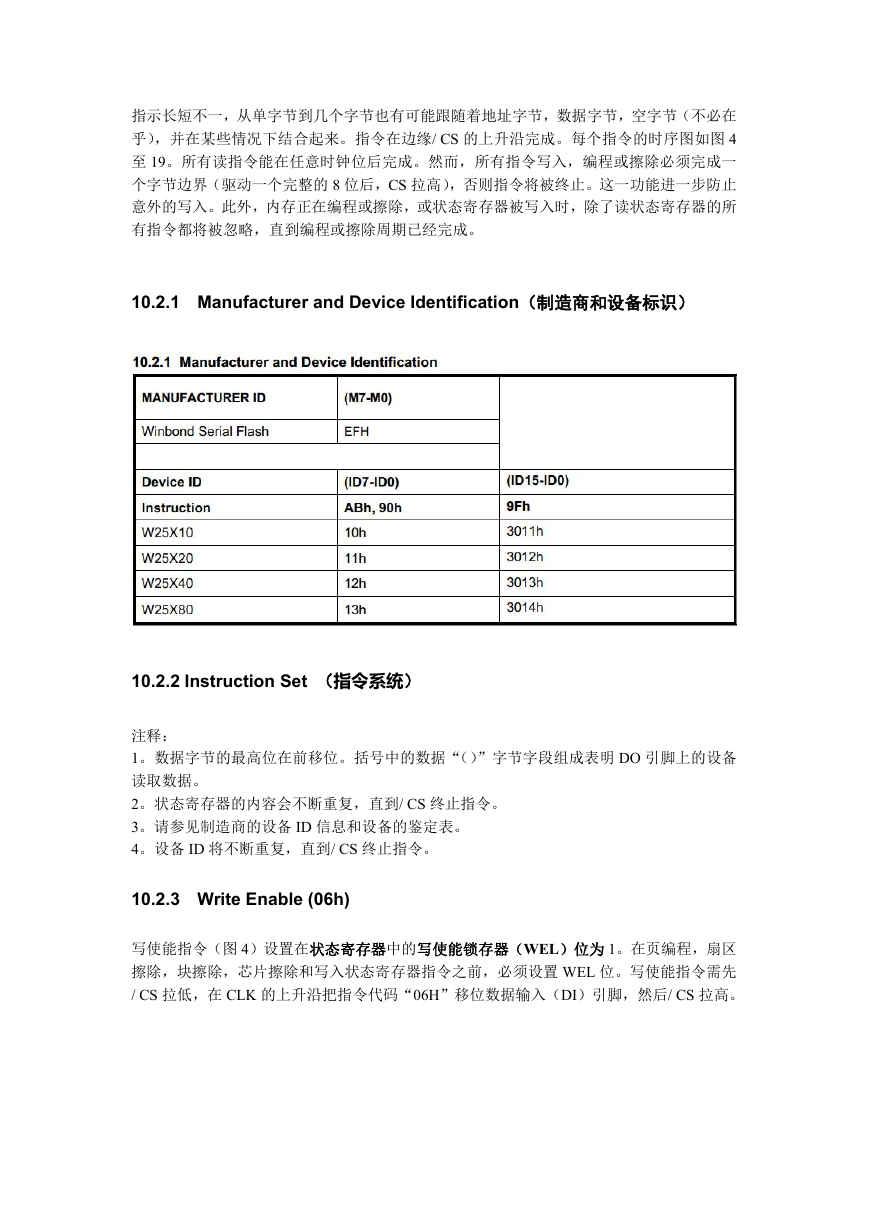

10.2.1 Manufacturer and Device Identification(制造商和设备标识)

10.2.2 Instruction Set (指令系统)

注释:

1。数据字节的最高位在前移位。括号中的数据“()”字节字段组成表明 DO 引脚上的设备

读取数据。

2。状态寄存器的内容会不断重复,直到/ CS 终止指令。

3。请参见制造商的设备 ID 信息和设备的鉴定表。

4。设备 ID 将不断重复,直到/ CS 终止指令。

10.2.3 Write Enable (06h)

写使能指令(图 4)设置在状态寄存器中的写使能锁存器(WEL)位为 1。在页编程,扇区

擦除,块擦除,芯片擦除和写入状态寄存器指令之前,必须设置 WEL 位。写使能指令需先

/ CS 拉低,在 CLK 的上升沿把指令代码“06H”移位数据输入(DI)引脚,然后/ CS 拉高。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc