实验要求

比赛计时器

4 个数码管,其中 2 个用于记录 A、B 队的分数,每队 1 个数码管,

记分范围 0~9 分,另外 2 个数码管用来记录赛程时间,单位为秒。

采用倒计时方式。即比赛前将时间设置好,比赛开始时启动计时,直

至计时到零为止。计时范围为 0~99 秒,倒计时时间由按键设置。

要求:

1.有设置时间、启动、暂停、交换场地等功能。

2.能记录整个赛程的比赛时间,并能修改比赛时间

3.能随时刷新甲、乙两队在整个过程中的比分

4.中场交换比赛场地时,能交换甲、乙两队比分的位置

5.比赛结束时,能发出报警声

本机地址为 04H,当接到上位机发的 04H 时,则回发 04H

当接到上位机发的 AAH 时,则将比分发出

1

�

总体设计方案及论证

一、AT89C51 简介

VCC:供电电压。 GND:接地。

P0 口:P0 口为一个 8 位漏级开路双向 I/O 口,每脚可吸收 8TTL

门电流。当 P1 口的管脚第一次写 1 时,被定义为高阻输入。P0 能

够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

P1 口:P1 口是一个内部提供上拉电阻的 8 位双向 I/O 口,P1 口缓

冲器能接收输出 4TTL 门电流。P1 口管脚写入 1 后,被内部上拉

为高,可用作输入,P1 口被外部下拉为低电平时,将输出电流,

这是由于内部上拉的缘故。

P2 口:P2 口为一个内部上拉电阻的 8 位双向 I/O 口,P2 口缓冲器

可接收,输出 4 个 TTL 门电流,当 P2 口被写“1”时,其管脚被内

部上拉电阻拉高,且作为输入。P2 口当用于外部程序存储器或 16

位地址外部数据存储器进行存取时,P2 口输出地址的高八位。

P3 口:P3 口管脚是 8 个带内部上拉电阻的双向 I/O 口,可接收输

出 4 个 TTL 门电流。当 P3 口写入“1”后,它们被内部上拉为高电

平,并用作输入。作为输入,由于外部下拉为低电平,P3 口将输

出电流(ILL)这是由于上拉的缘故。P3 口同时为闪烁编程和编程

校验接收一些控制信号。

RST:复位输入。当振荡器复位器件时,要保持 RST 脚两个机器

周期的高电平时间。

ALE/PROG:当访问外部存储器时,地址锁存允许的输出电平用于

2

�

锁存地址的地位字节。在平时,ALE 端以不变的频率周期输出正

脉冲信号,此频率为振荡器频率的 1/6。因此它可用作对外部输出

的脉冲或用于定时目的。

/PSEN:外部程序存储器的选通信号。在由外部程序存储器取指期

间,每个机器周期两次/PSEN 有效。但在访问外部数据存储器时,

这两次有效的/PSEN 信号将不出现。

/EA/VPP:当/EA 保持低电平时,则在此期间外部程序存储器,不

管是否有内部程序存储器。

XTAL1:反向振荡放大器的输入及内部时钟工作电路的输入。

XTAL2:来自反向振荡器的输出。

二、数码管显示原理

数码管是由 8 个发光二极管组成,并显示为“8”字型,并记作为

a, b,c,d ,e,f,g dp 按发光二极管单元连接方式分为共阳极数码管和共阴

极数码管。共阳数码管是指将所有发光二极管的阳极接到一起形成公

共阳极(COM)的数码管。共阳数码管在应用时应将公共极 COM 接到

+5V,当某一字段发光二极管的阴极为低电平时,相应字段就点亮。

当某一字段的阴极为高电平时,相应字段就不亮。。共阴数码管是指

将所有发光二极管的阴极接到一起形成公共阴极(COM)的数码管。共

阴数码管在应用时应将公共极 COM 接到地线 GND 上,当某一字段

发光二极管的阳极为高电平时,相应字段就点亮。当某一字段的阳极

为低电平时,相应字段就不亮.

3

�

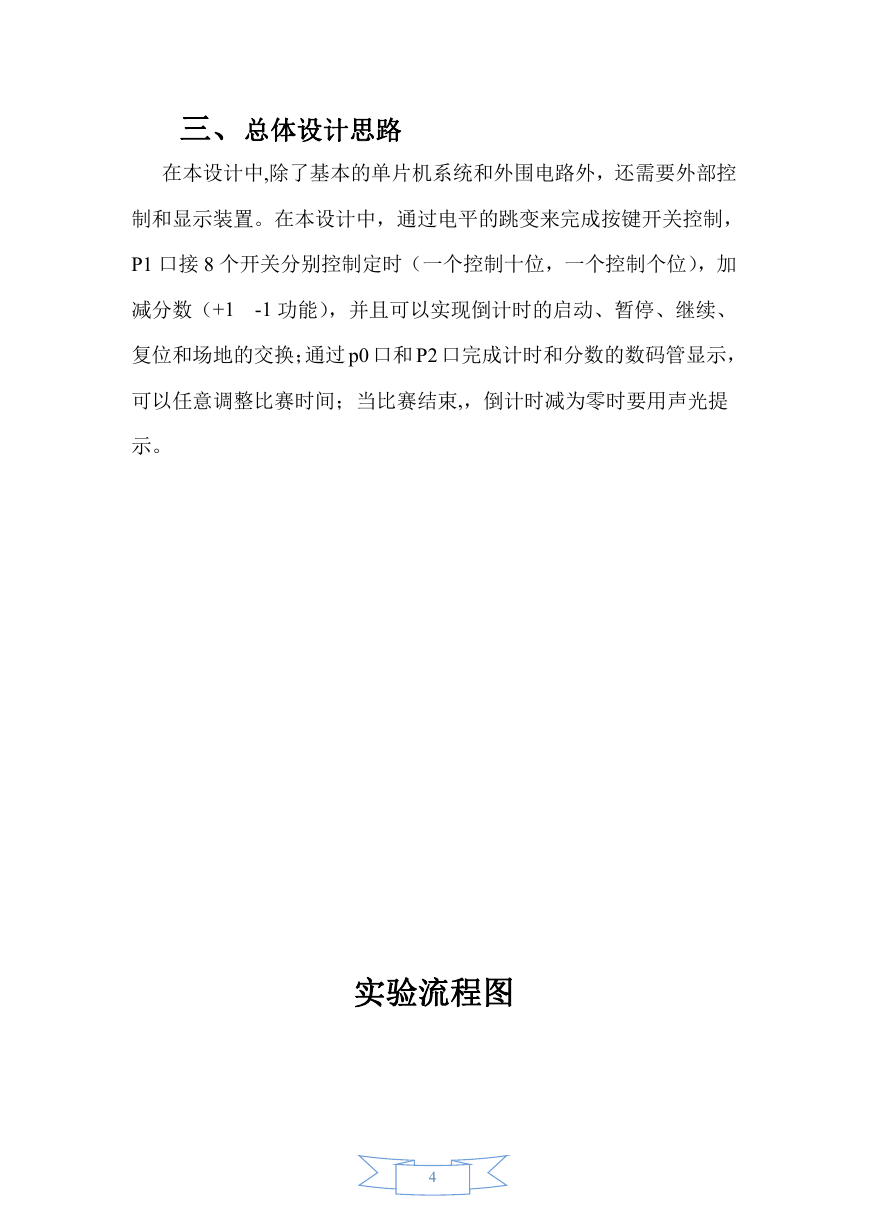

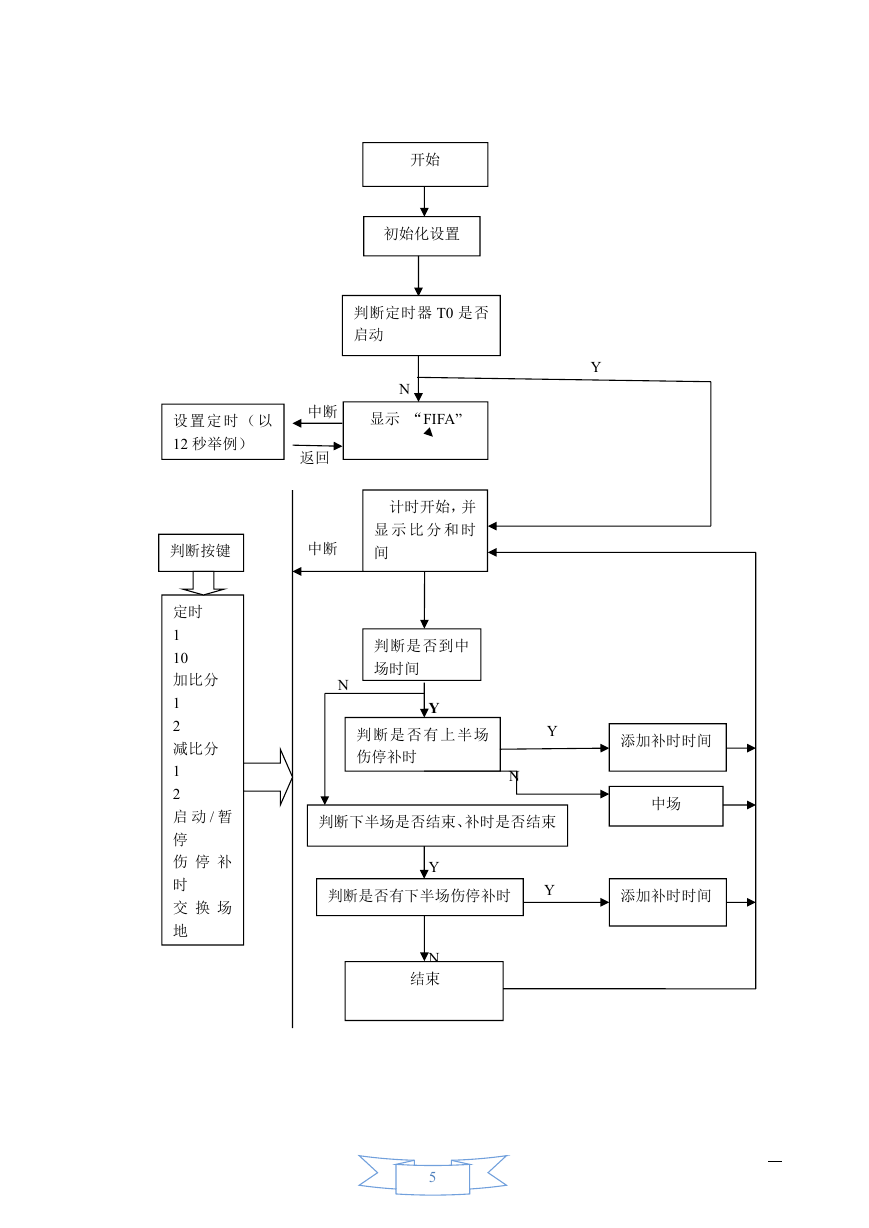

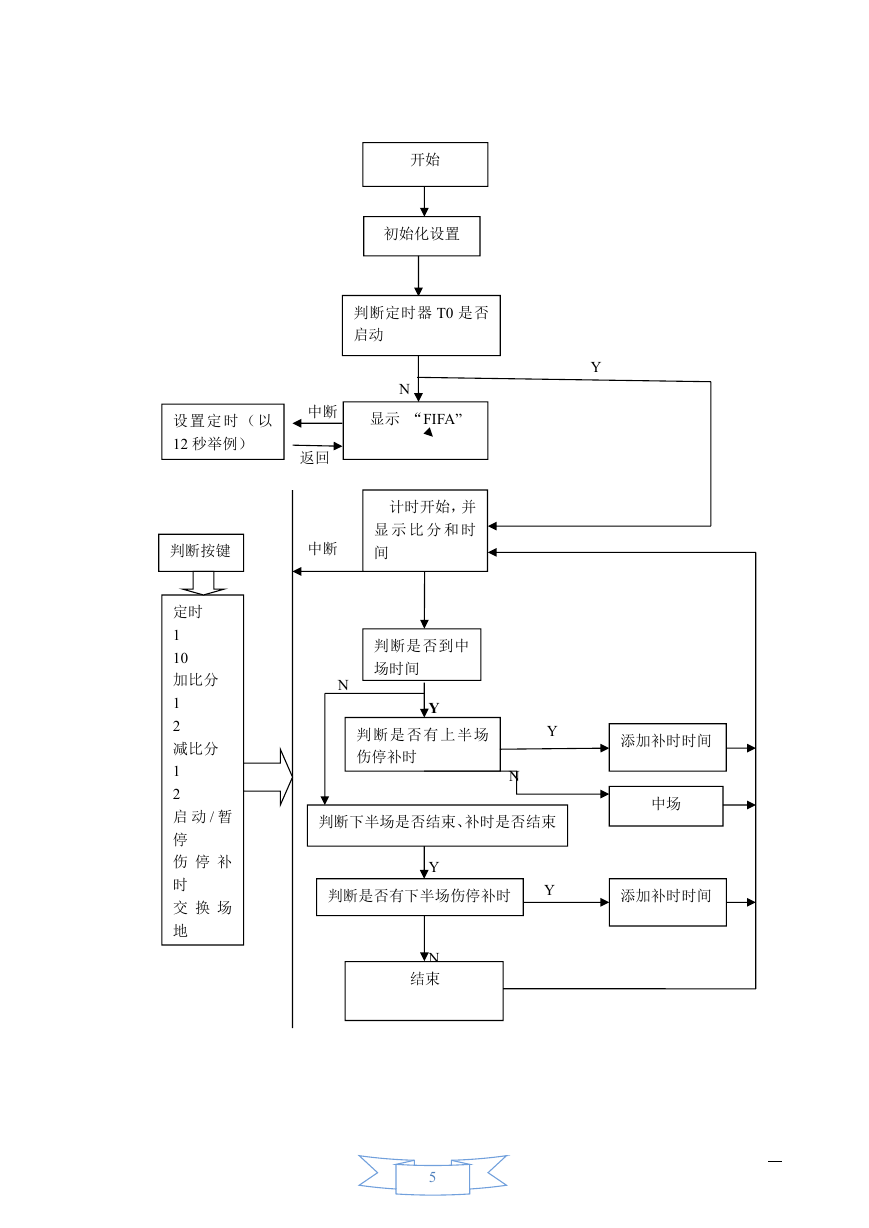

三、总体设计思路

在本设计中,除了基本的单片机系统和外围电路外,还需要外部控

制和显示装置。在本设计中,通过电平的跳变来完成按键开关控制,

P1 口接 8 个开关分别控制定时(一个控制十位,一个控制个位),加

减分数(+1 -1 功能),并且可以实现倒计时的启动、暂停、继续、

复位和场地的交换;通过 p0 口和 P2 口完成计时和分数的数码管显示,

可以任意调整比赛时间;当比赛结束,,倒计时减为零时要用声光提

示。

实验流程图

4

�

开始

初始化设置

判断定时器 T0 是否

启动

N

显示 “FIFA”

Y

设 置 定 时 ( 以

12 秒举例)

中断

返回

判断按键

中断

计时开始,并

显 示 比 分 和 时

间

定时

1

10

加比分

1

2

减比分

1

2

启 动 / 暂

停

伤 停 补

时

交 换 场

地

判断是否到中

场时间

N

Y

判 断 是 否 有 上 半 场

伤停补时

Y

N

添加补时时间

中场

判断下半场是否结束、补时是否结束

Y

判断是否有下半场伤停补时

Y

添加补时时间

N

结束

5

�

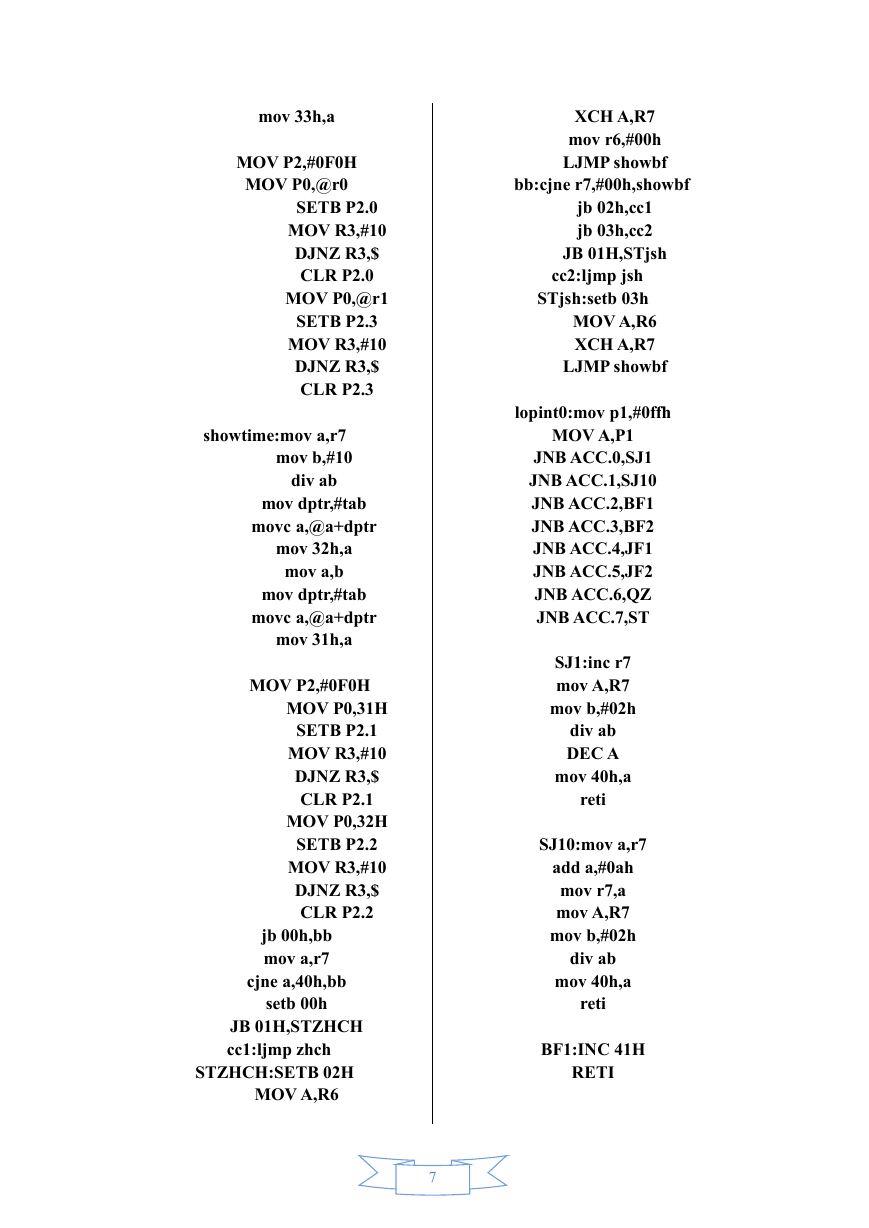

系统软件设计

main:mov tmod,#21h

org 0000h

ajmp main

org 0003h

ljmp lopint0

org 000bh

ljmp lopt0

org 0013h

ljmp lopint1

org 0030h

setb IT0

setb IT1

setb EX0

setb EX1

SETB ET0

setb EA

CLR TR0

mov th0,#3ch

mov tl0,#0b0h

mov tl1,#0fah

mov th1,#0fah

setb tr1

mov pcon,#0

mov scon,#50h

MOV 20H,#00H

mov p1,#0ffh

mov r2,#0ah

MOV R7,#00H

MOV R6,#00H

mov r0,#30h

mov r1,#33h

MOV 41H,#00H

MOV 42H,#00H

showfifa:JB TR0,showbf

lcall wait0

MOV P2,#0F0H

MOV P0,#77H

SETB P2.0

MOV R3,#10

DJNZ R3,$

CLR P2.0

6

MOV P0,#71H

SETB P2.1

MOV R3,#10

DJNZ R3,$

CLR P2.1

MOV P0,#30H

SETB P2.2

MOV R3,#10

DJNZ R3,$

CLR P2.2

MOV P0,#71H

SETB P2.3

MOV R3,#10

DJNZ R3,$

CLR P2.3

ajmp showfifa

wait0:jnb ri,ret1

clr ri

mov a,sbuf

cjne a,#04h,wait1

mov a,#04h

mov sbuf,a

wait1:cjne a,#0aah,ret1

jnb ti,$

clr ti

reti

mov a,41h

swap a

add a,42h

mov sbuf,a

jnb ti,$

clr ti

ret1:reti

showbf:lcall wait0

mov a,41H

mov dptr,#tab

movc a,@a+dptr

mov 30h,a

mov a,42H

mov dptr,#tab

movc a,@a+dptr

�

mov 33h,a

MOV P2,#0F0H

MOV P0,@r0

SETB P2.0

MOV R3,#10

DJNZ R3,$

CLR P2.0

MOV P0,@r1

SETB P2.3

MOV R3,#10

DJNZ R3,$

CLR P2.3

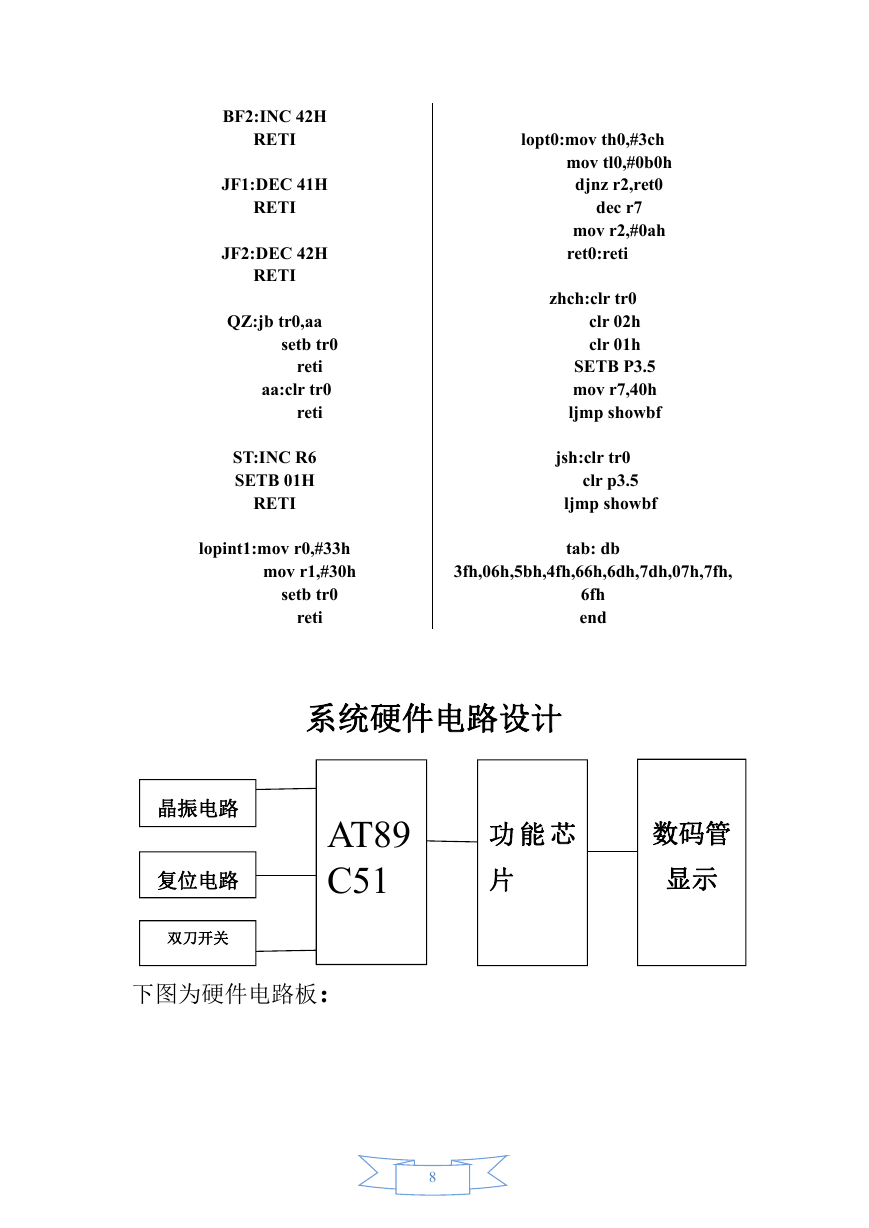

showtime:mov a,r7

mov b,#10

div ab

mov dptr,#tab

movc a,@a+dptr

mov 32h,a

mov a,b

mov dptr,#tab

movc a,@a+dptr

mov 31h,a

MOV P2,#0F0H

MOV P0,31H

SETB P2.1

MOV R3,#10

DJNZ R3,$

CLR P2.1

MOV P0,32H

SETB P2.2

MOV R3,#10

DJNZ R3,$

CLR P2.2

jb 00h,bb

mov a,r7

cjne a,40h,bb

setb 00h

JB 01H,STZHCH

cc1:ljmp zhch

STZHCH:SETB 02H

MOV A,R6

bb:cjne r7,#00h,showbf

XCH A,R7

mov r6,#00h

LJMP showbf

jb 02h,cc1

jb 03h,cc2

JB 01H,STjsh

cc2:ljmp jsh

STjsh:setb 03h

MOV A,R6

XCH A,R7

LJMP showbf

lopint0:mov p1,#0ffh

MOV A,P1

JNB ACC.0,SJ1

JNB ACC.1,SJ10

JNB ACC.2,BF1

JNB ACC.3,BF2

JNB ACC.4,JF1

JNB ACC.5,JF2

JNB ACC.6,QZ

JNB ACC.7,ST

SJ1:inc r7

mov A,R7

mov b,#02h

div ab

DEC A

mov 40h,a

reti

SJ10:mov a,r7

add a,#0ah

mov r7,a

mov A,R7

mov b,#02h

div ab

mov 40h,a

reti

BF1:INC 41H

RETI

7

�

BF2:INC 42H

RETI

JF1:DEC 41H

RETI

JF2:DEC 42H

RETI

QZ:jb tr0,aa

setb tr0

reti

aa:clr tr0

reti

ST:INC R6

SETB 01H

RETI

lopint1:mov r0,#33h

mov r1,#30h

setb tr0

reti

lopt0:mov th0,#3ch

mov tl0,#0b0h

djnz r2,ret0

dec r7

mov r2,#0ah

ret0:reti

zhch:clr tr0

clr 02h

clr 01h

SETB P3.5

mov r7,40h

ljmp showbf

jsh:clr tr0

clr p3.5

ljmp showbf

3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,

tab: db

6fh

end

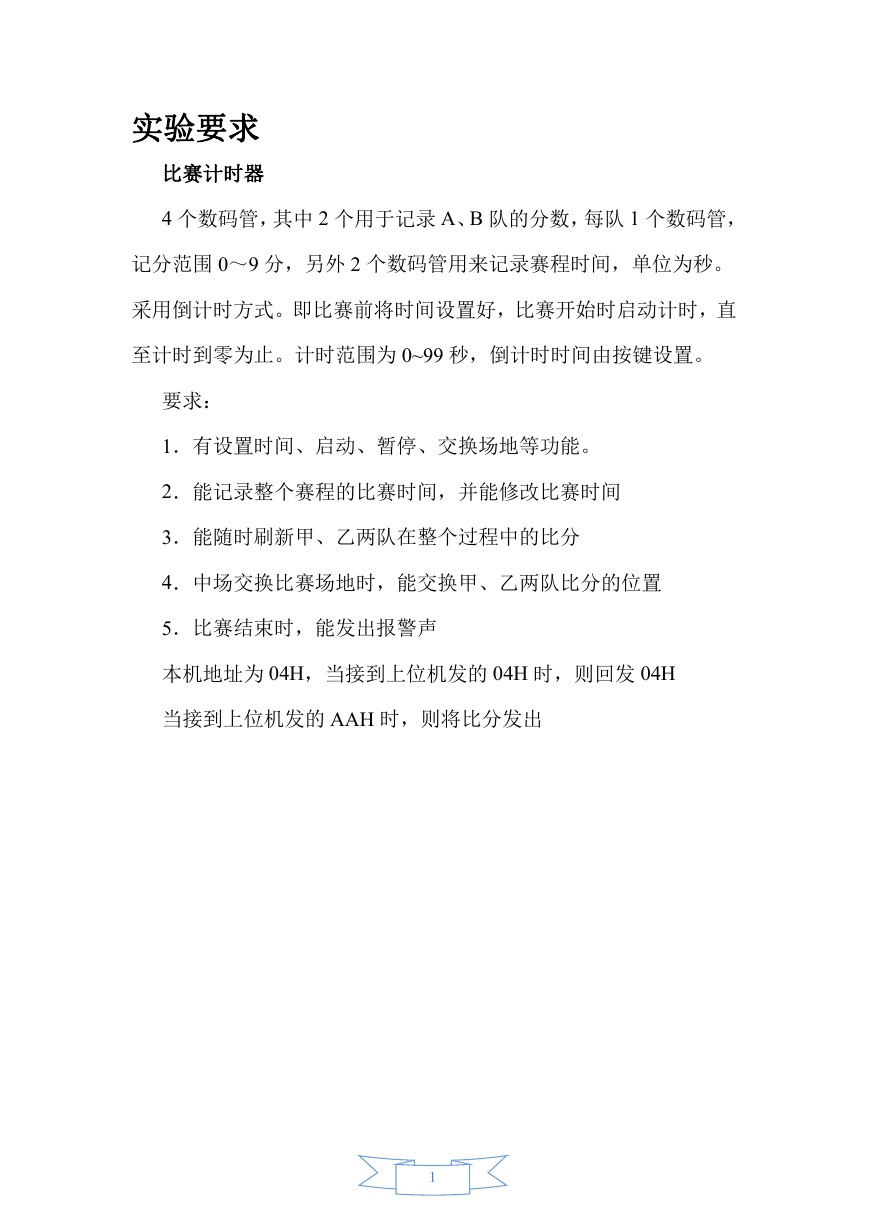

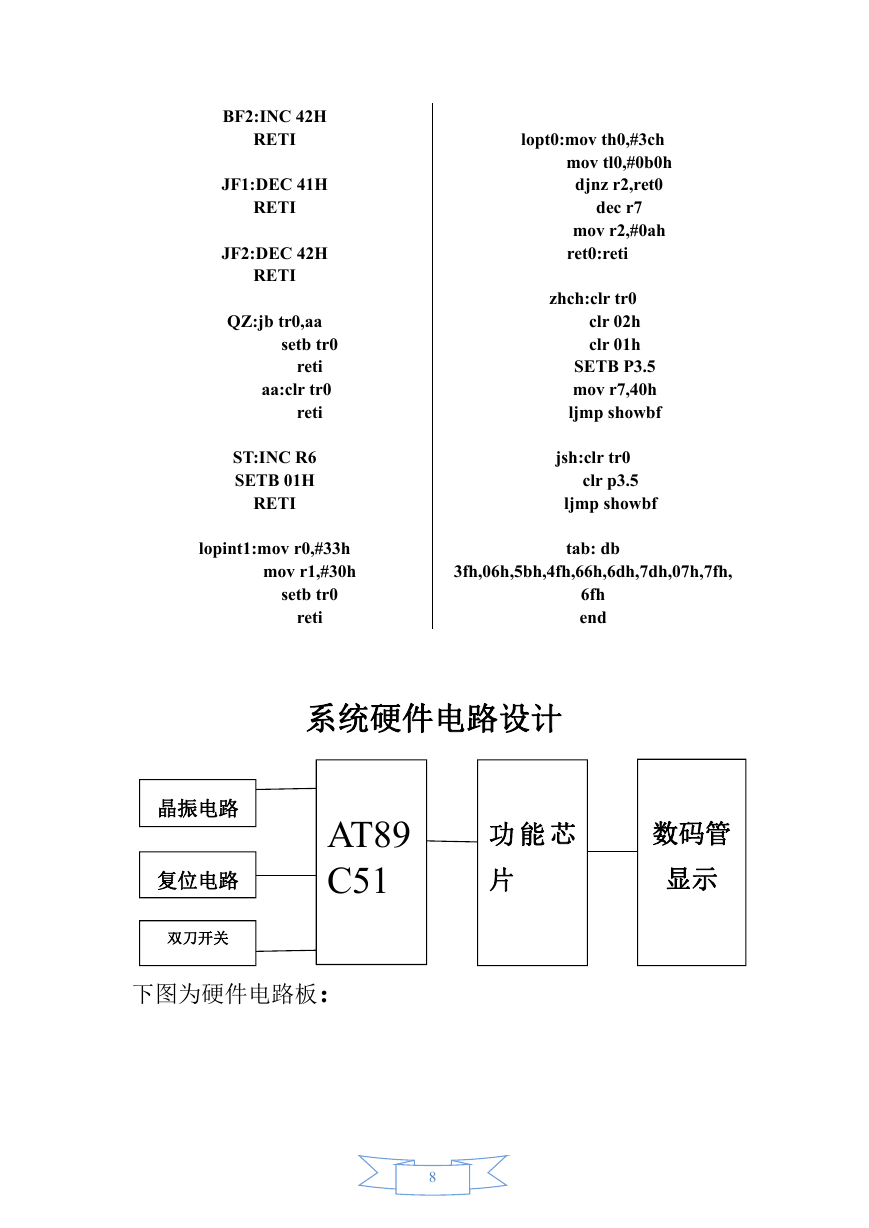

系统硬件电路设计

晶振电路

复位电路

双刀开关

AT89

C51

功 能 芯

数码管

片

显示

下图为硬件电路板:

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc