《EDA 技术》实验报告

实验名称: 循环冗余校验(CRC)模块设计

姓名:xxx

班级:xxxx

学号:xxxxx

实验日期:

指导教师:

一、实验设计要求

编译示例文件,给出仿真波形。建立一个新的设计,调入 crcm 模块。把其中的 CRC 校验生

成模块和 CRC 校验查错模块连接在一起,协调工作。引出必要的信号,锁定引脚,并在 EDA

实验系统上实现。

二、设计原理

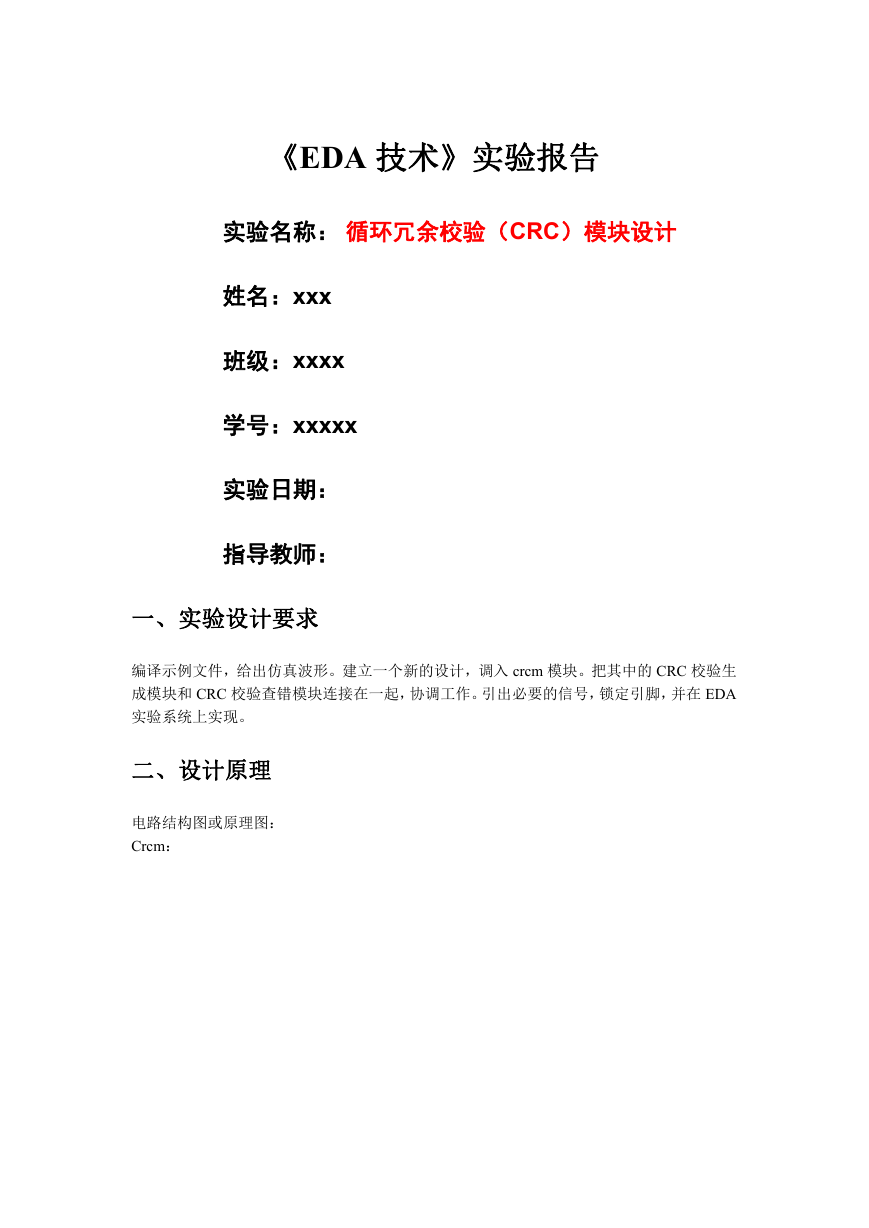

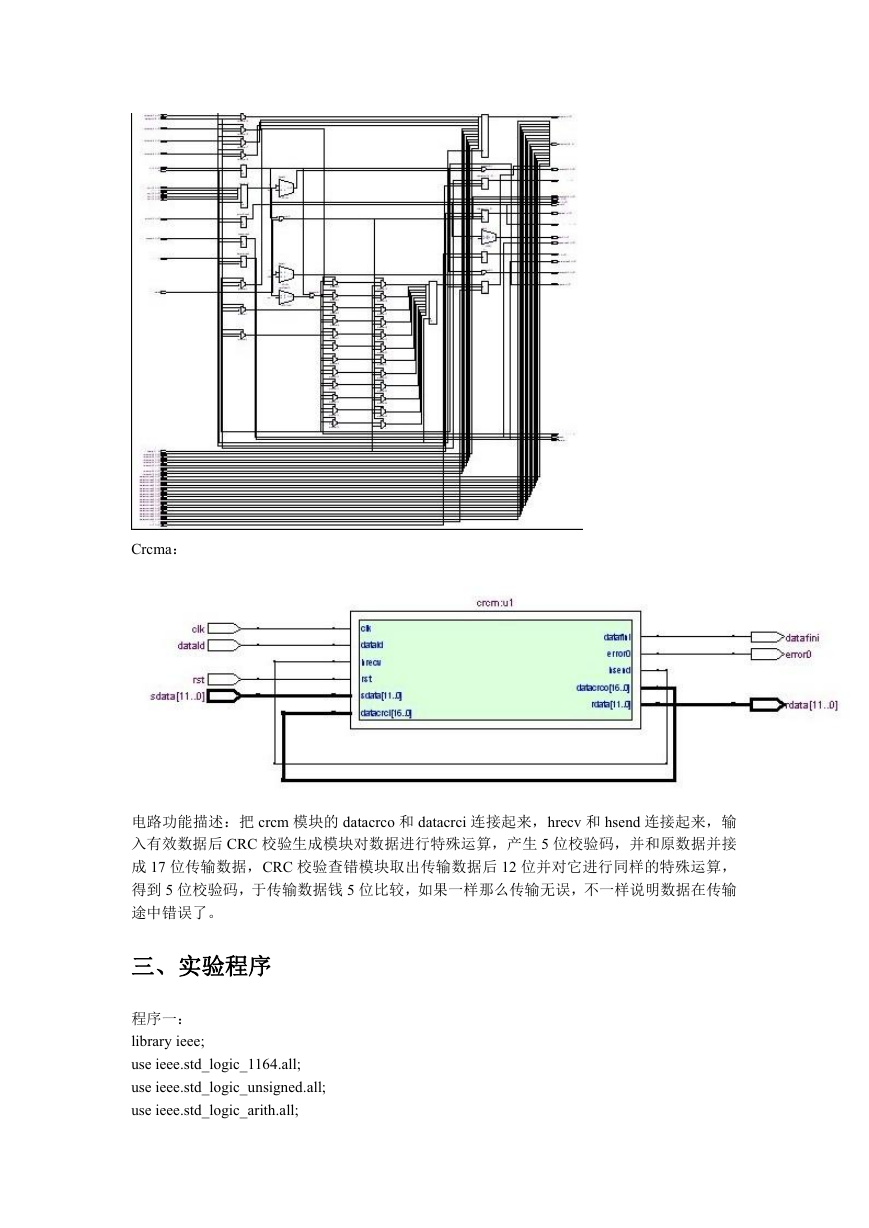

电路结构图或原理图:

Crcm:

�

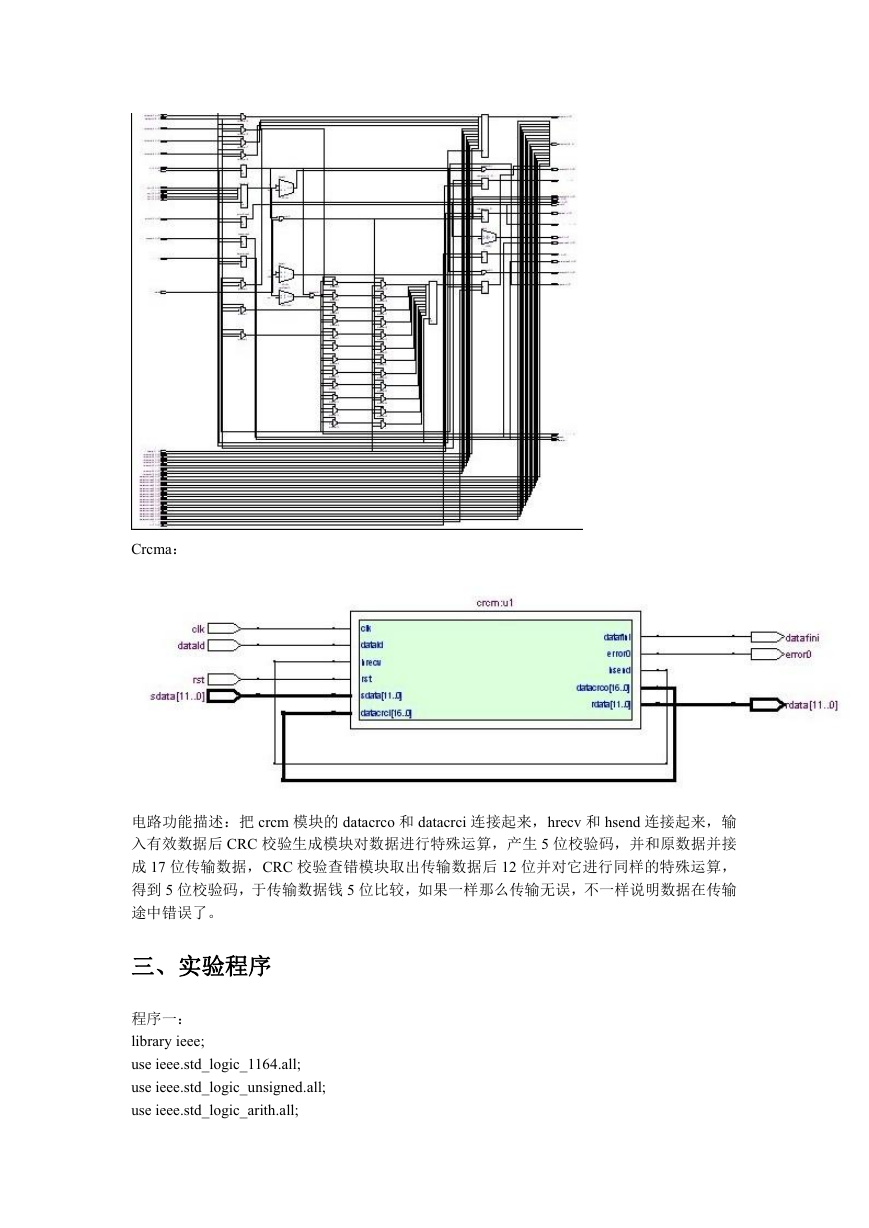

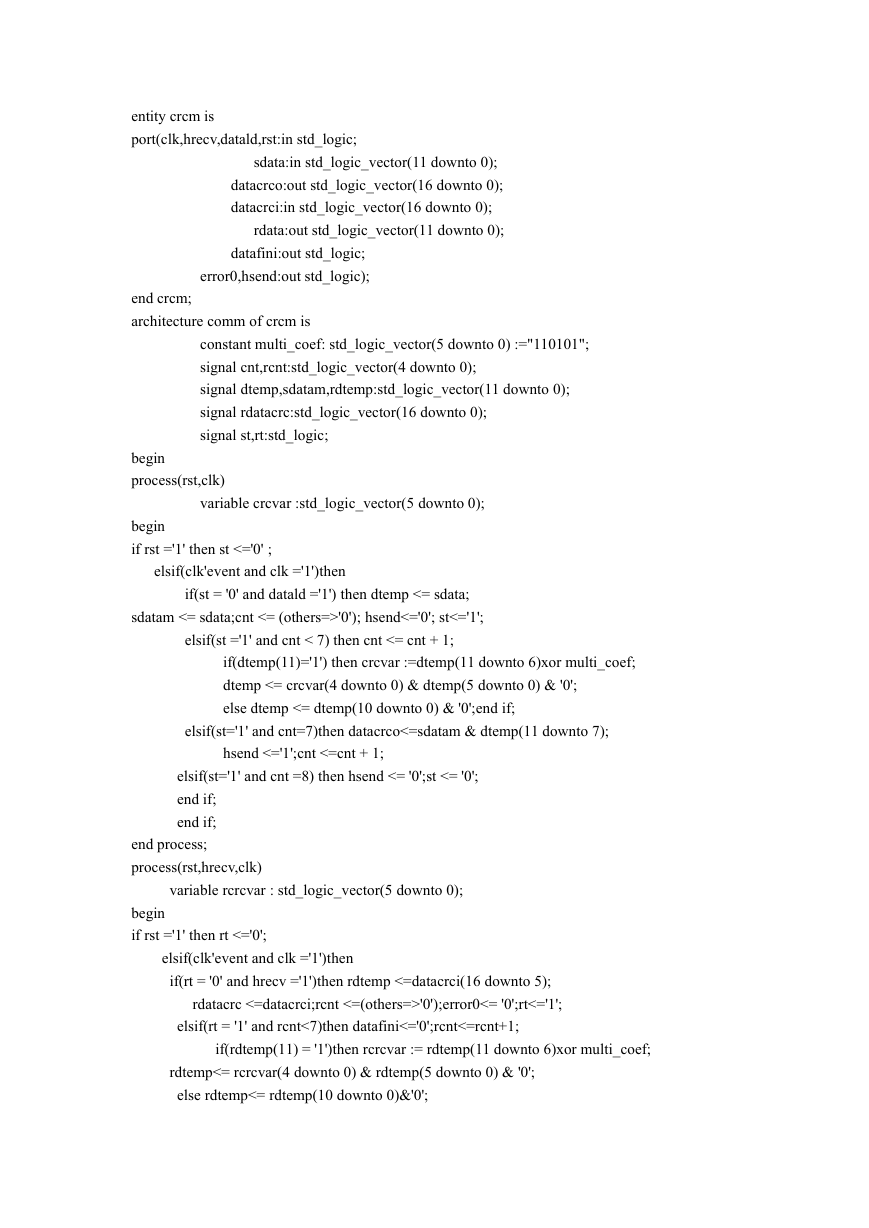

Crcma:

电路功能描述:把 crcm 模块的 datacrco 和 datacrci 连接起来,hrecv 和 hsend 连接起来,输

入有效数据后 CRC 校验生成模块对数据进行特殊运算,产生 5 位校验码,并和原数据并接

成 17 位传输数据,CRC 校验查错模块取出传输数据后 12 位并对它进行同样的特殊运算,

得到 5 位校验码,于传输数据钱 5 位比较,如果一样那么传输无误,不一样说明数据在传输

途中错误了。

三、实验程序

程序一:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

�

entity crcm is

port(clk,hrecv,datald,rst:in std_logic;

sdata:in std_logic_vector(11 downto 0);

datacrco:out std_logic_vector(16 downto 0);

datacrci:in std_logic_vector(16 downto 0);

rdata:out std_logic_vector(11 downto 0);

datafini:out std_logic;

error0,hsend:out std_logic);

end crcm;

architecture comm of crcm is

constant multi_coef: std_logic_vector(5 downto 0) :="110101";

signal cnt,rcnt:std_logic_vector(4 downto 0);

signal dtemp,sdatam,rdtemp:std_logic_vector(11 downto 0);

signal rdatacrc:std_logic_vector(16 downto 0);

signal st,rt:std_logic;

begin

process(rst,clk)

variable crcvar :std_logic_vector(5 downto 0);

begin

if rst ='1' then st <='0' ;

elsif(clk'event and clk ='1')then

if(st = '0' and datald ='1') then dtemp <= sdata;

sdatam <= sdata;cnt <= (others=>'0'); hsend<='0'; st<='1';

elsif(st ='1' and cnt < 7) then cnt <= cnt + 1;

if(dtemp(11)='1') then crcvar :=dtemp(11 downto 6)xor multi_coef;

dtemp <= crcvar(4 downto 0) & dtemp(5 downto 0) & '0';

else dtemp <= dtemp(10 downto 0) & '0';end if;

elsif(st='1' and cnt=7)then datacrco<=sdatam & dtemp(11 downto 7);

hsend <='1';cnt <=cnt + 1;

elsif(st='1' and cnt =8) then hsend <= '0';st <= '0';

end if;

end if;

end process;

process(rst,hrecv,clk)

variable rcrcvar : std_logic_vector(5 downto 0);

begin

if rst ='1' then rt <='0';

elsif(clk'event and clk ='1')then

if(rt = '0' and hrecv ='1')then rdtemp <=datacrci(16 downto 5);

rdatacrc <=datacrci;rcnt <=(others=>'0');error0<= '0';rt<='1';

elsif(rt = '1' and rcnt<7)then datafini<='0';rcnt<=rcnt+1;

if(rdtemp(11) = '1')then rcrcvar := rdtemp(11 downto 6)xor multi_coef;

rdtemp<= rcrcvar(4 downto 0) & rdtemp(5 downto 0) & '0';

else rdtemp<= rdtemp(10 downto 0)&'0';

�

end if;

elsif(rt='1' and rcnt=7)then datafini<='1';

rdata<=rdatacrc(16 downto 5); rt<='0';

if(rdatacrc(4 downto 0)/=rdtemp(11 downto 7))then

error0<='1';end if;

end if;

end if;

end process;

end comm;

程序二:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity crcma is

port (clk,datald,rst:in std_logic;

sdata:in std_logic_vector(11 downto 0);

rdata:out std_logic_vector(11 downto 0);

error0:out std_logic;

datafini:out std_logic);

end crcma;

architecture comm of crcma is

component crcm

port (clk,hrecv,datald,rst:in std_logic;

sdata:in std_logic_vector(11 downto 0);

datacrco:out std_logic_vector(16 downto 0);

datacrci:in std_logic_vector(16 downto 0);

rdata:out std_logic_vector(11 downto 0);

datafini:out std_logic;

error0,hsend:out std_logic);

end component;

signal datacrcp:std_logic_vector(16 downto 0);

signal hsenp:std_logic;

begin

u1:

map(rst=>rst,clk=>clk,sdata=>sdata,datald=>datald,datacrco=>datacrcp,hrecv=>hsenp,

hsend=>hsenp,datacrci=>datacrcp,rdata=>rdata,error0=>error0,datafini=>datafini);

end architecture comm;

crcm

port

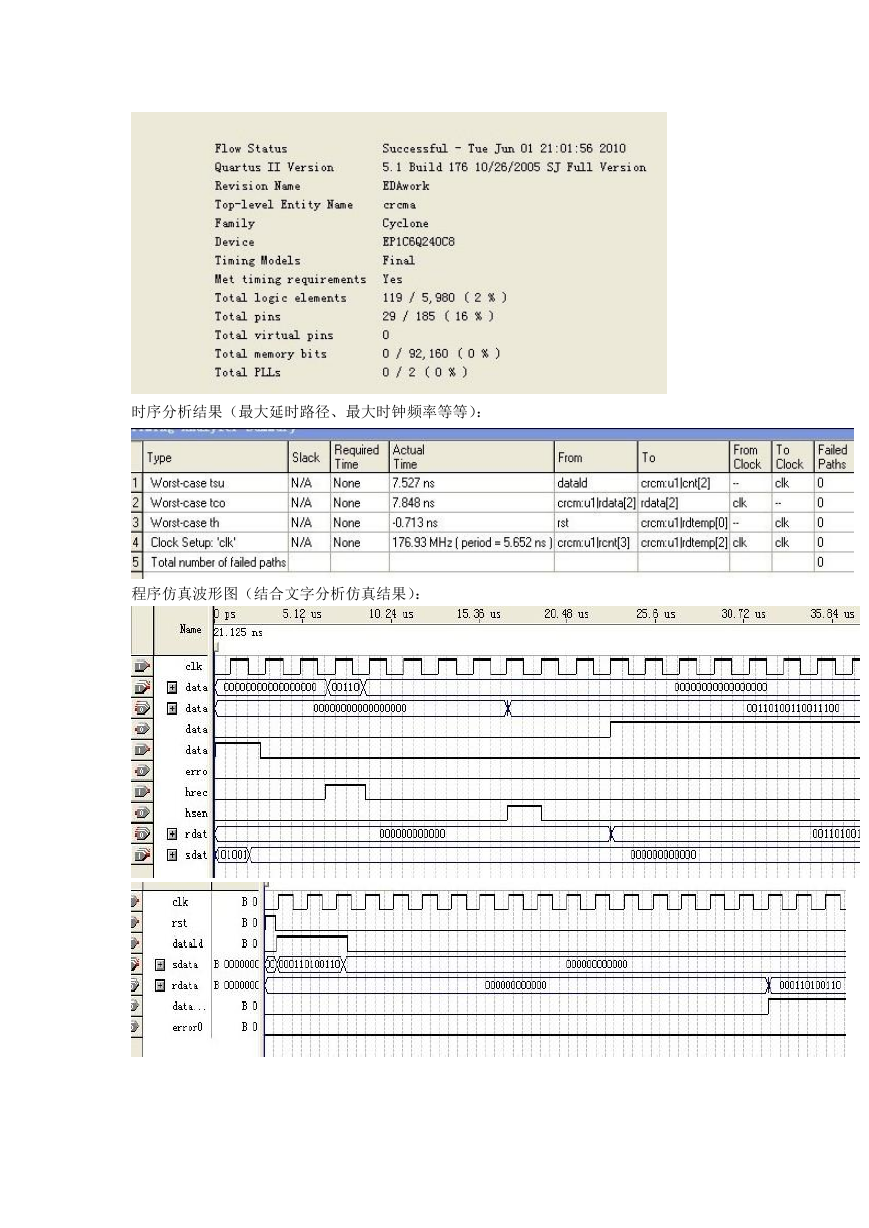

四、编译及仿真结果

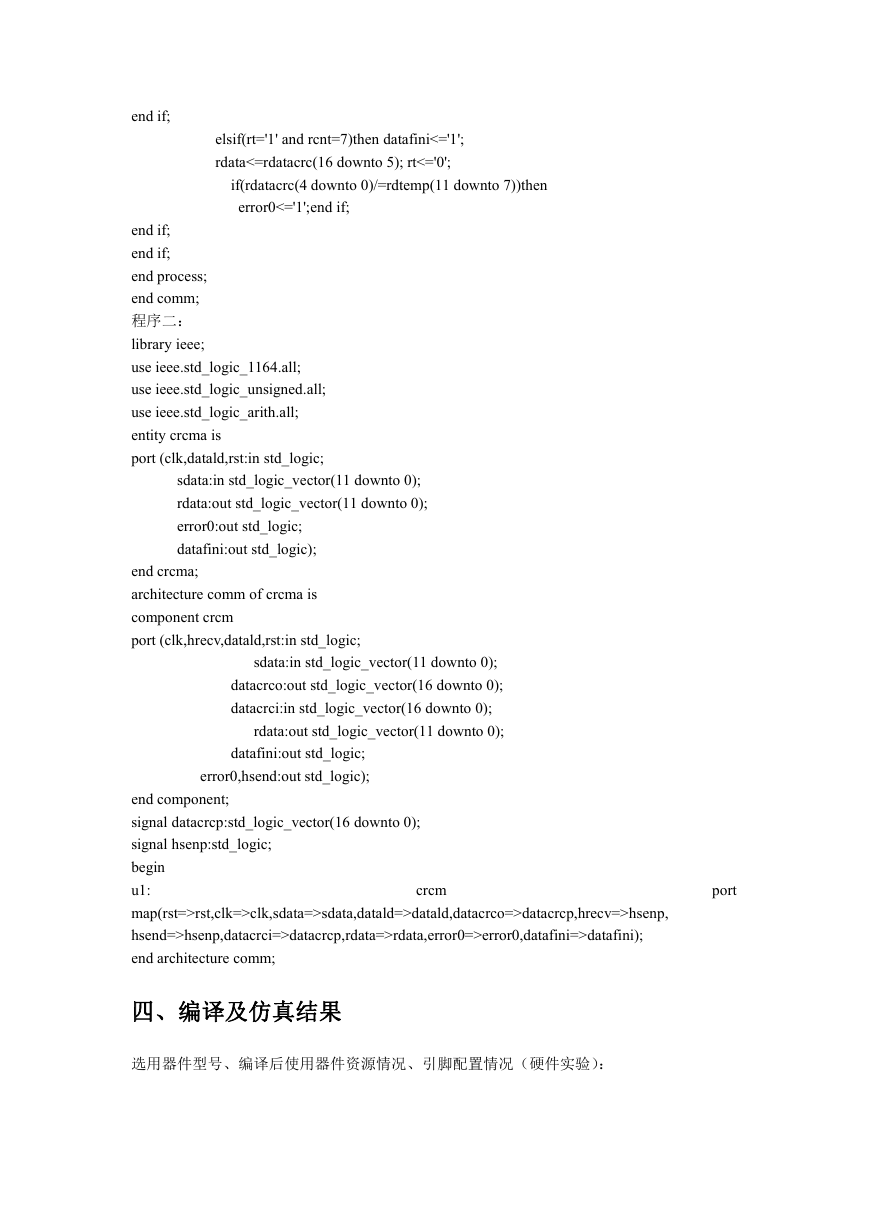

选用器件型号、编译后使用器件资源情况、引脚配置情况(硬件实验):

�

时序分析结果(最大延时路径、最大时钟频率等等):

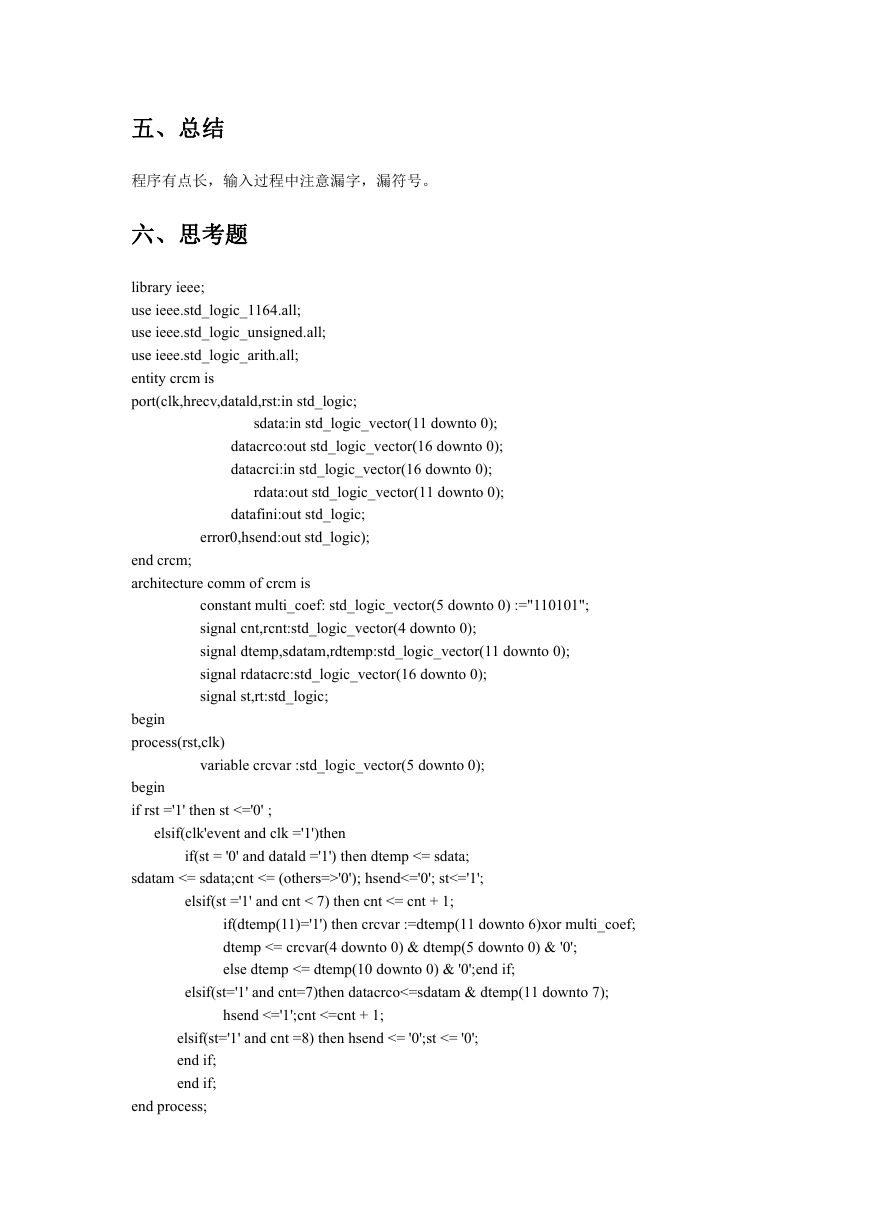

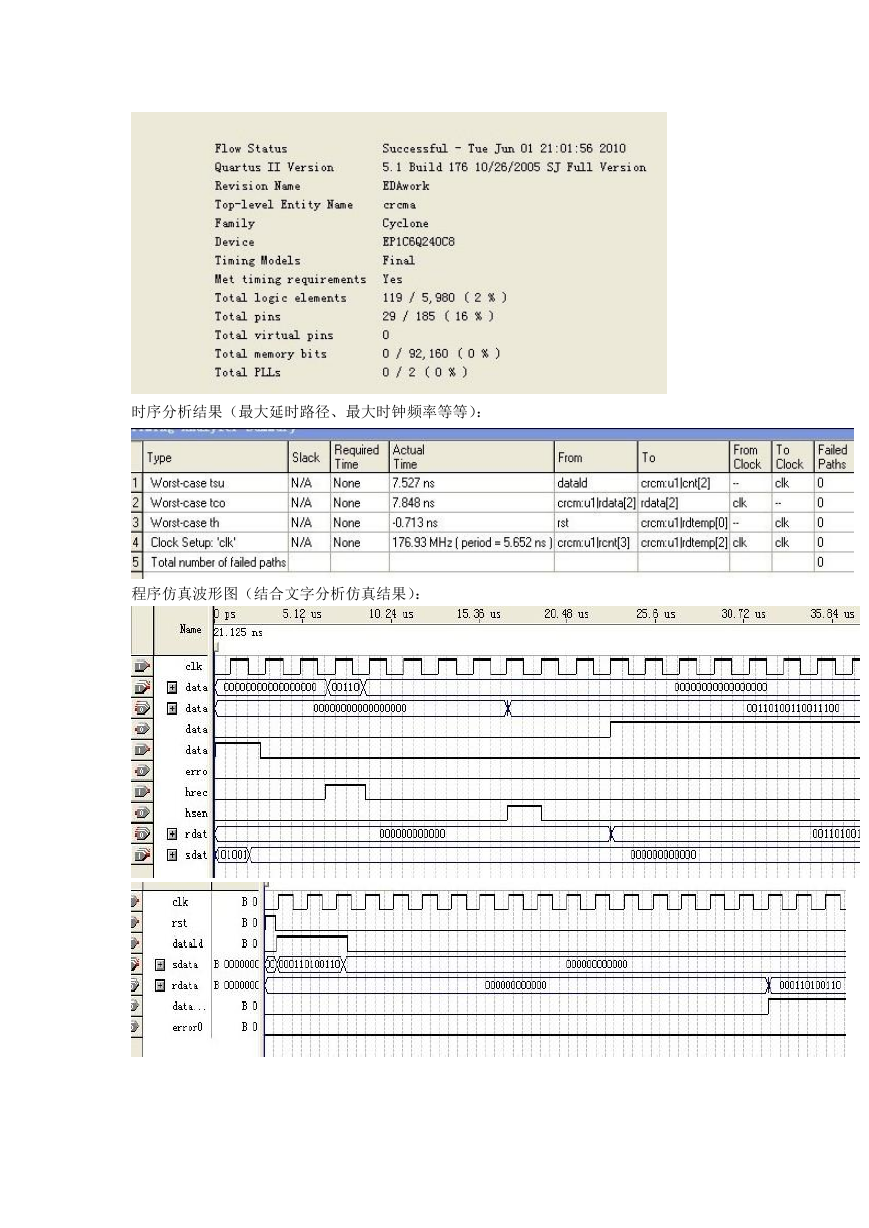

程序仿真波形图(结合文字分析仿真结果):

�

五、总结

程序有点长,输入过程中注意漏字,漏符号。

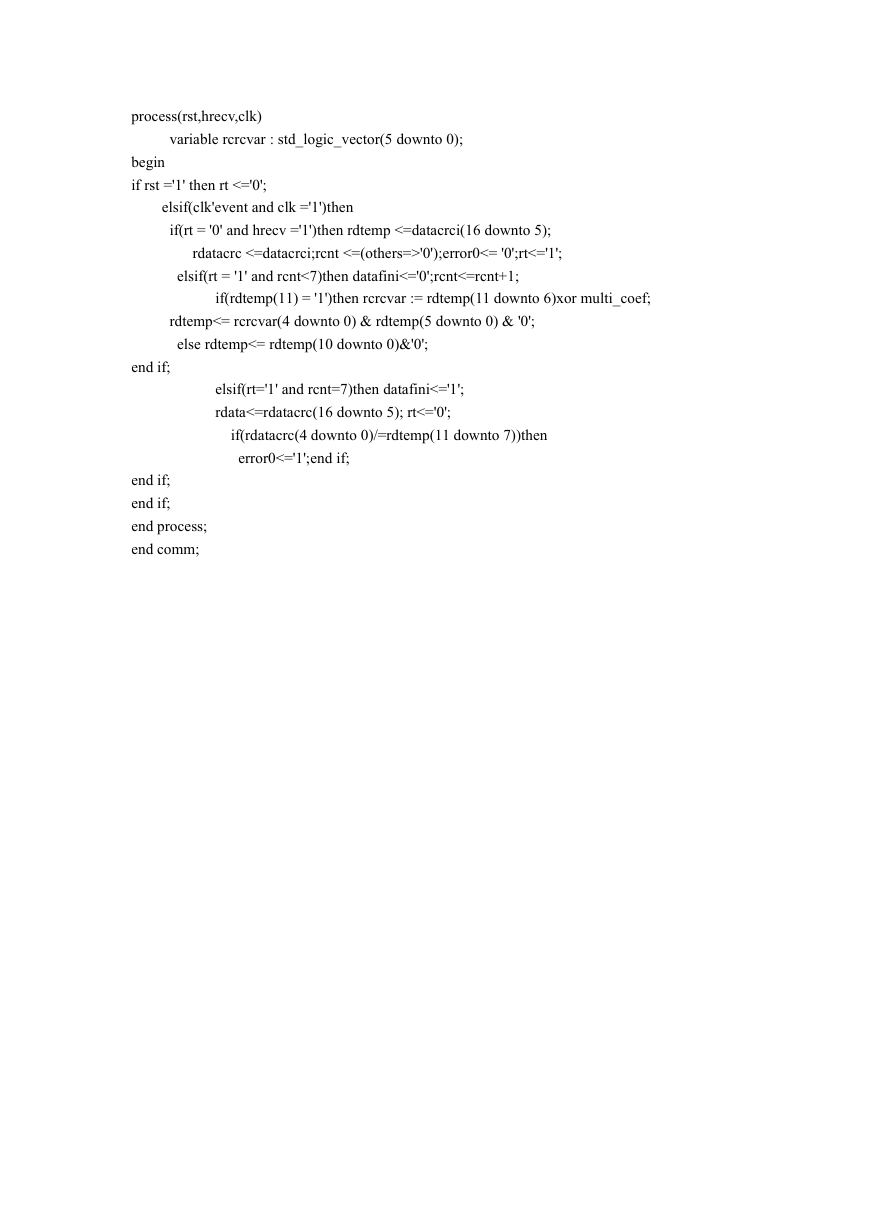

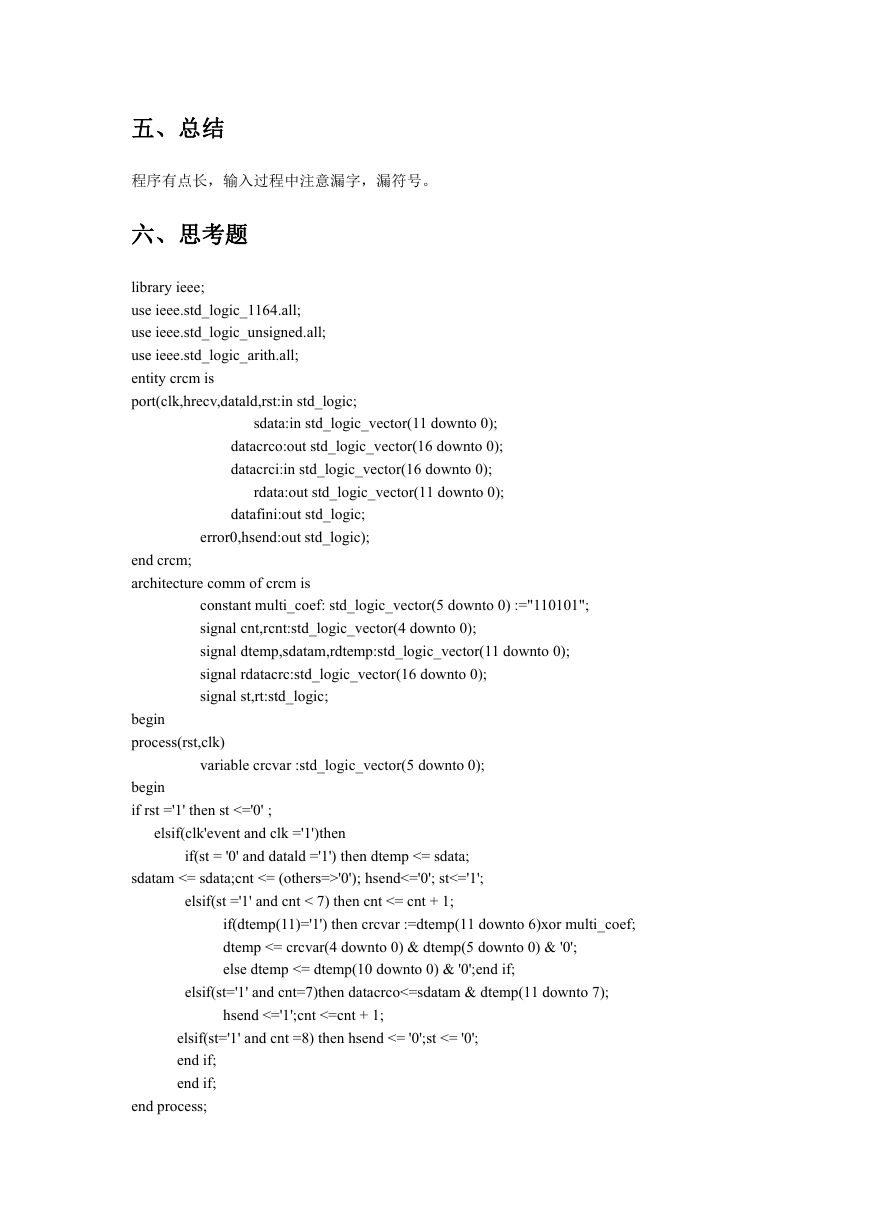

六、思考题

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity crcm is

port(clk,hrecv,datald,rst:in std_logic;

sdata:in std_logic_vector(11 downto 0);

datacrco:out std_logic_vector(16 downto 0);

datacrci:in std_logic_vector(16 downto 0);

rdata:out std_logic_vector(11 downto 0);

datafini:out std_logic;

error0,hsend:out std_logic);

end crcm;

architecture comm of crcm is

constant multi_coef: std_logic_vector(5 downto 0) :="110101";

signal cnt,rcnt:std_logic_vector(4 downto 0);

signal dtemp,sdatam,rdtemp:std_logic_vector(11 downto 0);

signal rdatacrc:std_logic_vector(16 downto 0);

signal st,rt:std_logic;

begin

process(rst,clk)

variable crcvar :std_logic_vector(5 downto 0);

begin

if rst ='1' then st <='0' ;

elsif(clk'event and clk ='1')then

if(st = '0' and datald ='1') then dtemp <= sdata;

sdatam <= sdata;cnt <= (others=>'0'); hsend<='0'; st<='1';

elsif(st ='1' and cnt < 7) then cnt <= cnt + 1;

if(dtemp(11)='1') then crcvar :=dtemp(11 downto 6)xor multi_coef;

dtemp <= crcvar(4 downto 0) & dtemp(5 downto 0) & '0';

else dtemp <= dtemp(10 downto 0) & '0';end if;

elsif(st='1' and cnt=7)then datacrco<=sdatam & dtemp(11 downto 7);

hsend <='1';cnt <=cnt + 1;

elsif(st='1' and cnt =8) then hsend <= '0';st <= '0';

end if;

end if;

end process;

�

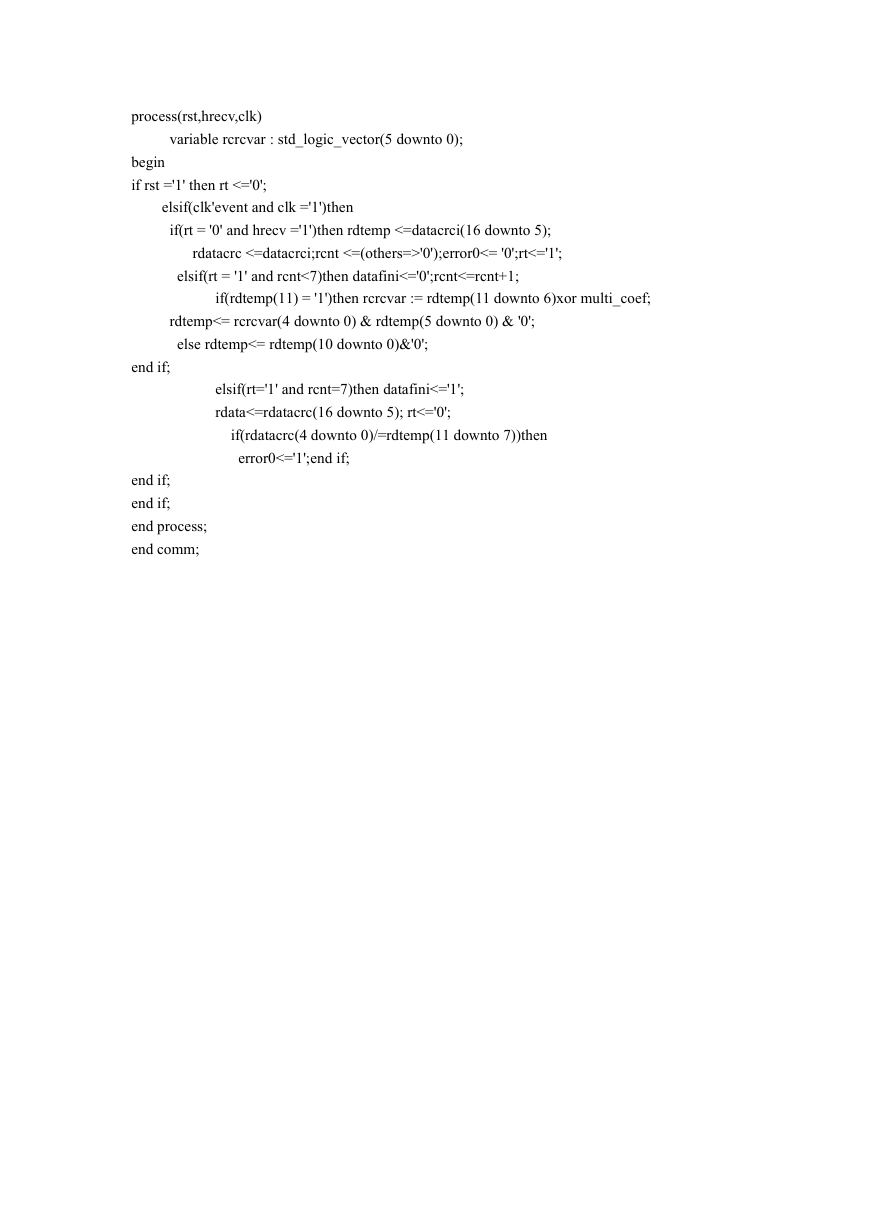

process(rst,hrecv,clk)

variable rcrcvar : std_logic_vector(5 downto 0);

begin

if rst ='1' then rt <='0';

elsif(clk'event and clk ='1')then

if(rt = '0' and hrecv ='1')then rdtemp <=datacrci(16 downto 5);

rdatacrc <=datacrci;rcnt <=(others=>'0');error0<= '0';rt<='1';

elsif(rt = '1' and rcnt<7)then datafini<='0';rcnt<=rcnt+1;

if(rdtemp(11) = '1')then rcrcvar := rdtemp(11 downto 6)xor multi_coef;

rdtemp<= rcrcvar(4 downto 0) & rdtemp(5 downto 0) & '0';

else rdtemp<= rdtemp(10 downto 0)&'0';

elsif(rt='1' and rcnt=7)then datafini<='1';

rdata<=rdatacrc(16 downto 5); rt<='0';

if(rdatacrc(4 downto 0)/=rdtemp(11 downto 7))then

error0<='1';end if;

end if;

end if;

end if;

end process;

end comm;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc