UTMI +低引脚接口(ULPI)规范

修订版1.1

2004 年10 月20

翻译于2020 年8 月22 日

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

UTMI +低引脚接口规范,修订版 1.1,中文版

2004 年 10 月 20

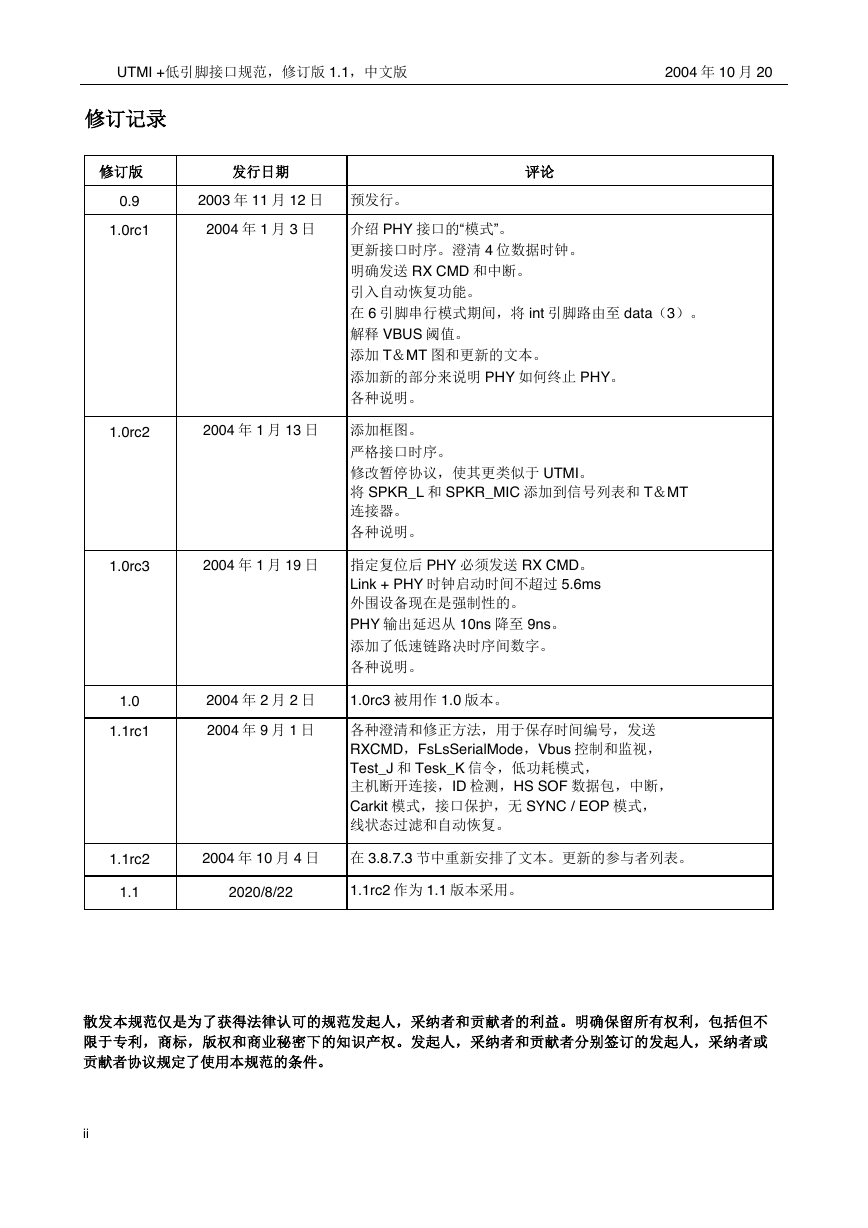

发行日期

2003 年 11 月 12 日 预发行。

评论

2004 年 1 月 3 日

介绍 PHY 接口的“模式”。

更新接口时序。澄清 4 位数据时钟。

明确发送 RX CMD 和中断。

引入自动恢复功能。

在 6 引脚串行模式期间,将 int 引脚路由至 data(3)。

解释 VBUS 阈值。

添加 T&MT 图和更新的文本。

添加新的部分来说明 PHY 如何终止 PHY。

各种说明。

2004 年 1 月 13 日 添加框图。

严格接口时序。

修改暂停协议,使其更类似于 UTMI。

将 SPKR_L 和 SPKR_MIC 添加到信号列表和 T&MT

连接器。

各种说明。

2004 年 1 月 19 日 指定复位后 PHY 必须发送 RX CMD。

Link + PHY 时钟启动时间不超过 5.6ms

修订记录

修订版

0.9

1.0rc1

1.0rc2

1.0rc3

1.0

1.1rc1

1.1rc2

1.1

外围设备现在是强制性的。

PHY 输出延迟从 10ns 降至 9ns。

添加了低速链路决时序间数字。

各种说明。

1.0rc3 被用作 1.0 版本。

各种澄清和修正方法,用于保存时间编号,发送

RXCMD,FsLsSerialMode,Vbus 控制和监视,

Test_J 和 Tesk_K 信令,低功耗模式,

主机断开连接,ID 检测,HS SOF 数据包,中断,

Carkit 模式,接口保护,无 SYNC / EOP 模式,

线状态过滤和自动恢复。

2004 年 2 月 2 日

2004 年 9 月 1 日

2004 年 10 月 4 日 在 3.8.7.3 节中重新安排了文本。更新的参与者列表。

2020/8/22

1.1rc2 作为 1.1 版本采用。

散发本规范仅是为了获得法律认可的规范发起人,采纳者和贡献者的利益。明确保留所有权利,包括但不

限于专利,商标,版权和商业秘密下的知识产权。发起人,采纳者和贡献者分别签订的发起人,采纳者或

贡献者协议规定了使用本规范的条件。

ii

�

UTMI +低引脚接口规范,修订版 1.1,中文版

2020/8/22

发起人

ARC International Inc.

科胜讯系统有限公司

Mentor Graphics Corporation

飞利浦

SMSC

TransDimension,Inc.

贡献者

巴特·韦尔滕滕

巴图汉·奥库

比尔·安德森

比尔·麦金尼

布赖恩·布克

克里斯·贝朗格

克里斯·科布

克里斯·谢尔

钟咏妍

戴夫·斯罗卡

王大卫

大卫·伍腾

川本埃里克

法伦·麦凯

弗兰克·弗雷泽

弗雷德·罗伯茨

哈桑·法鲁克

李贤

伊恩·帕尔

杰伊·斯坦迪福德

杰罗姆·贾

马克·桑德斯

穆罕默德

摩根僧侣

纳比尔·塔克拉

彼得·滕斯特兰德

拉曼德·曼达亚姆)

罗伯·道格拉斯

萨利姆·穆罕默德

肖恩·雷迈耶

西蒙·阮(Simon Nguyen) Cypress

Subramanyam Sankaran 飞利浦

苏·维宁

特里·伦普

蒂莫西·陈

张文森

问题应通过电子邮件发送给 lpcwg@boardrooms.org。

飞利浦

飞利浦

摩托罗拉

TransDimension

Cypress

ARC

ARC

飞利浦

飞利浦

飞利浦

飞利浦

TransDimension

SMSC

飞利浦

科胜讯

新思科技

科胜讯

TransDimension

Mentor

TransDimension

飞利浦

Mentor

科胜讯

SMSC

ISI

ARC

科胜讯

Mentor

新思科技

飞利浦(作者)

德州仪器

高通公司

科胜讯

科胜讯

iii

�

2020/8/22

UTMI +低引脚接口规范,修订版 1.1,中文版

图

图 1 – LPI 通用数据总线所有权 ....................................................................................................................... 3

图 2 – LPI 通用数据传输,然后是数据接收 ..................................................................................................... 3

图 3 –链路断言 stp 暂停接收数据..................................................................................................................... 4

图 4 –使用包装创建 ULPI 系统......................................................................................................................... 5

图 5 – ULPI PHY 的框图 .................................................................................................................................. 7

图 6 –抖动测量平面 ........................................................................................................................................ 12

图 7 – ULPI 时序图 ......................................................................................................................................... 13

图 8 –与 8 位接口相比,4 位数据接口的时钟 ................................................................................................ 14

图 9 – RX CMD 的发送 .................................................................................................................................. 17

图 10 – USB 数据传输(NOPID) ................................................................................................................. 18

图 11 – USB 数据传输(PID) ...................................................................................................................... 19

图 12 – PHY 驱动 RX CMD 指示 EOP(FS / LS LineState 时序未按比例缩放) .......................................... 20

图 13 –强制全速/低速 USB 传输错误(时序不正确).................................................................................... 21

图 14 – dir 先前为低时的 USB 接收 ............................................................................................................... 22

图 15 – dir 先前较高时的 USB 接收 ............................................................................................................... 23

图 16 –在分组中间检测到 USB 接收错误 ....................................................................................................... 24

图 17 –最后一个字节期间 USB 接收错误 ....................................................................................................... 25

图 18 – USB HS,FS 和 LS 位长度与时钟的关系 ......................................................................................... 26

图 19 – HS 发送到发送的分组时序 ................................................................................................................ 29

图 20 – HS 接收到发送的数据包时序。 ......................................................................................................... 29

图 21 –寄存器写 ............................................................................................................................................. 30

图 22 –读取寄存器 ......................................................................................................................................... 31

图 23 – TX CMD 字节期间 USB 接收中止的寄存器读取或写入 ..................................................................... 31

图 24 – USB 接收中止寄存器读取翻转周期或寄存器写入数据周期 ............................................................... 32

图 25 – USB 接收与寄存器读取数据的周期相同。USB 接收延迟 ................................................................. 33

图 26 –读取寄存器后立即进行 USB 接收 ....................................................................................................... 33

图 27 –在 stp 声明期间,寄存器写操作紧随 USB 接收之后 .......................................................................... 34

图 28 –读取寄存器,然后进行 USB 接收 ....................................................................................................... 34

图 29 –扩展寄存器写 ...................................................................................................................................... 35

图 30 –扩展寄存器读取 .................................................................................................................................. 35

图 31 –扩展地址周期内 USB 接收中止了扩展寄存器读取 ............................................................................. 36

图 32 – PHY 被链路断言 stp 中止。链路执行寄存器写或 USB 传输。 .......................................................... 37

图 33 – PHY 被链路断言 stp 中止。链路执行寄存器读取。 .......................................................................... 38

图 34 –链路中止 PHY。链路无法驱动 TX CMD。PHY 重新声明 dir ............................................................. 38

图 35 –高速检测握手(线性调频)序列(时序不按比例) ............................................................................ 40

图 36 –前同步码序列(D + / D-时序不按比例) ............................................................................................ 41

图 37 – LS 挂起和恢复(时序不按比例) ...................................................................................................... 43

图 38 – FS 挂起和恢复(时间不按比例) ...................................................................................................... 44

图 39 – HS 挂起和恢复(时间不按比例) ..................................................................................................... 46

图 40 –低功耗模式下的低速远程唤醒(时序不按比例) ............................................................................... 47

图 41 –低功耗模式下的全速远程唤醒(时序不按比例) ............................................................................... 48

图 42 –低功耗模式下的高速远程唤醒(时序不按比例) ............................................................................... 49

图 43 –自动恢复信令(时序不按比例) ......................................................................................................... 50

图 44 – OpMode 设置为 11b 时 USB 数据包传输。 ...................................................................................... 51

图 45 – RX CMD VA_VBUS_VLD ≤ Vbus 指示源 ................................................................................................ 54

图 46 –进入低功耗模式 .................................................................................................................................. 55

图 47 –当 PHY 提供输出时钟时退出低功耗模式 ............................................................................................ 56

图 48 – Link 提供输入时钟时退出低功耗模式 ................................................................................................ 56

图 49 –当时钟开始之前 stp 无效时,PHY 保持在低功耗模式 ........................................................................ 57

图 50 – stp 无效后,dir 无效前,PHY 重新进入低功耗模式 .......................................................................... 57

图 51 –进入串行模式且时钟关闭时的接口行为 .............................................................................................. 59

图 52 –进入串行模式且时钟保持供电时的接口行为 ...................................................................................... 59

图 53 –退出串行模式且时钟未运行时的接口行为 .......................................................................................... 60

图 54 –退出串行模式并且时钟正在运行时的接口行为 ................................................................................... 60

图 55 –时钟运行时受保护的 PHY 接口 .......................................................................................................... 62

�

图 56 – PHY 在链路之前上电时的上电顺序。接口受保护 ............................................................................. 63

图 57 – PHY 在受接口保护的情况下自动退出低功耗模式 ............................................................................. 63

图 58 –链路恢复驱动 ULPI 总线并断言 stp,因为时钟未运行 ....................................................................... 64

图 59 –链路在 PHY 之前加电时的加电顺序(符合 ULPI 1.0 的链路) .......................................................... 64

图 60 –推荐的子卡配置(不按比例) ............................................................................................................ 83

�

UTMI +低引脚接口规范,修订版 1.1,中文版

表

2020/8/22

表 1 – LPI 通用接口信号 .................................................................................................................................. 2

表 2 – PHY 接口信号 ........................................................................................................................................ 6

表 3 –模式摘要 ................................................................................................................................................. 9

表 4 –时钟时序参数 ........................................................................................................................................ 11

表 5 – ULPI 接口时序 ..................................................................................................................................... 13

表 6 –发送命令(TX CMD)字节格式 ........................................................................................................... 15

表 7 –接收命令(RX CMD)字节格式 ........................................................................................................... 16

表 8 – USB 规范数据包间时序 ....................................................................................................................... 26

表 9 – PHY 管线延迟 ...................................................................................................................................... 27

表 10 –链路决策时间 ...................................................................................................................................... 28

表 11 – OTG 控制寄存器功率控制位 ............................................................................................................. 52

表 12 – Vbus 比较器阈值 ............................................................................................................................... 52

表 13 – RX CMD VbusValid 过电流情况 ........................................................................................................ 53

表 14 –典型应用所需的 RX CMD 中的 Vbus 指示器 ...................................................................................... 54

表 15 –低功耗模式下的接口信号映射 ............................................................................................................ 55

表 16 – 6 引脚 FsLsSerialMode 的串行模式信号映射 .................................................................................... 58

表 17 – 3 引脚 FsLsSerialMode 的串行模式信号映射 .................................................................................... 58

表 18 –Carkit 信号映射................................................................................................................................... 61

表 19 –寄存器映射 ......................................................................................................................................... 66

表 20 –寄存器访问图例 .................................................................................................................................. 67

表 21 –供应商 ID 和产品 ID 寄存器说明 ......................................................................................................... 67

表 22 –功能控制寄存器 .................................................................................................................................. 68

表 23 –接口控制寄存器 .................................................................................................................................. 70

表 24 – OTG 控制寄存器................................................................................................................................ 71

表 25 – USB 中断使能上升寄存器 ................................................................................................................. 72

表 26 – USB 中断使能下降寄存器 ................................................................................................................. 73

表 27 – USB 中断状态寄存器 ......................................................................................................................... 74

表 28 – USB 中断锁存器 ................................................................................................................................ 75

表 29 –设置中断锁存寄存器位的规则 ............................................................................................................ 75

表 30 –调试寄存器 ......................................................................................................................................... 76

表 31 –暂存器 ................................................................................................................................................ 76

表 32 –Carkit 控制寄存器 ............................................................................................................................... 77

表 33 – Carkit 中断延迟寄存器 ....................................................................................................................... 77

表 34 – Carkit 中断允许寄存器 ....................................................................................................................... 78

表 35 – Carkit 中断状态寄存器 ....................................................................................................................... 78

表 36 – Carkit 中断锁存器寄存器 ................................................................................................................... 79

表 37 – Carkit 脉冲控制.................................................................................................................................. 79

表 38 –发射正宽度 ......................................................................................................................................... 80

表 39 –发射负宽度 ......................................................................................................................................... 80

表 40 –接收极性恢复 ...................................................................................................................................... 81

表 41 –上行和下行信令模式 ........................................................................................................................... 82

表 42 – T&MT 连接器引脚视图 ..................................................................................................................... 84

表 43 – T&MT 连接器的引脚分配 ................................................................................................................. 84

表 44 – T&MT 引脚说明 ................................................................................................................................ 85

�

UTMI +低引脚接口规范,修订版 1.1,中文版

1. 介绍

1.1

本规范在第 2 章中定义了通用 PHY 接口

在第 3 章中,通用接口被应用于 UTMI +协议,从而减少了支持 On-The-Go,主机和外围应用空间的离散

USB 收发器实现的引脚数。

通用

2020/8/22

命名约定

缩略语和术语

1.2

重点放在带下划线的 Arial 字体的普通描述性文本上,例如必须。

信号名称使用小写的粗体 Arial 字体表示,例如 clk。

寄存器使用首字母大写,Arial 粗体表示,例如 OTG Control。

寄存器位使用首字母大写,粗体斜体 Arial 字体表示,例如 USB 中断使能下降。

1.3

A 设备

B 设备

DRD

FPGA

FS

HNP

HS

Link

LPI

LS

OTG

PHY

PLL

SE0

SIE

SRP

T&MT

ULPI

USB

USB-IF

UTMI

UUT

1.4

[Ref 1]通用串行总线规范,修订版 2.0

[Ref 2] USB 2.0 规范,修订版 1.0a 的移动补充

[Ref 3] USB 2.0 收发器宏单元接口(UTMI)规范,v1.05

[Ref 4] UTMI +规范,修订版 1.0

[Ref 5] CEA-2011,OTG 收发器规范

[Ref 6] CEA-936A,迷你 USB 模拟 Carkit 接口规范

[Ref 7] USB 2.0 收发器和宏单元测试器(T&MT)接口规范,版本 1.2

设备的插座中插入了 Standard-A 或 Mini-A 插头

设备的插座中插入了 Standard-B 或 Mini-B 插头

双角色设备

现场可编程门阵列

全速

主机协商协议

高速

连接到 ULPI 收发器的 ASIC,SIE 或 FPGA

低引脚接口

低速

On-The-Go

物理层(收发器)

锁相环

单端零

串行接口引擎

会话请求协议

收发器和宏单元测试仪

UTMI +低引脚接口

通用串行总线

USB-IF

USB 2.0 收发器 Macrocell 接口

被测单元

Ref

1

�

UTMI +低引脚接口规范,修订版 1.1,中文版

2020/8/22

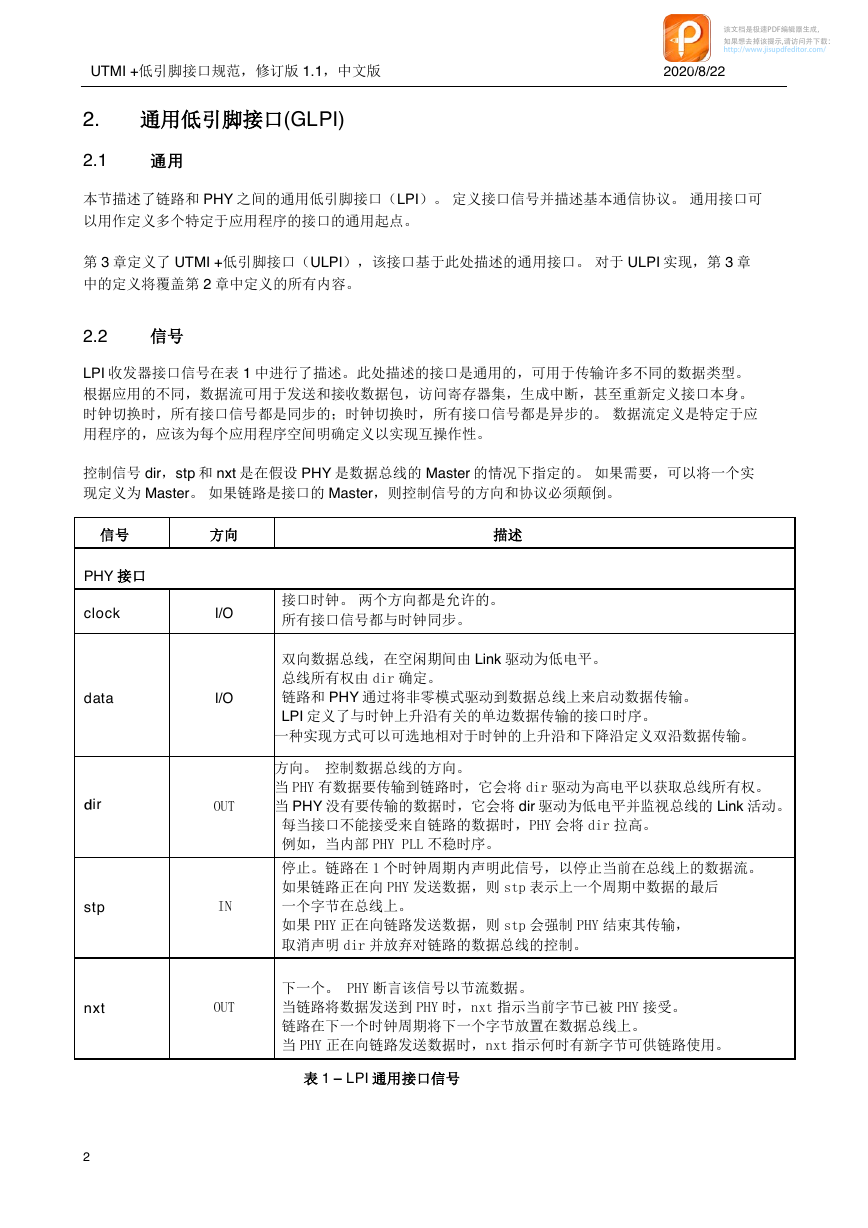

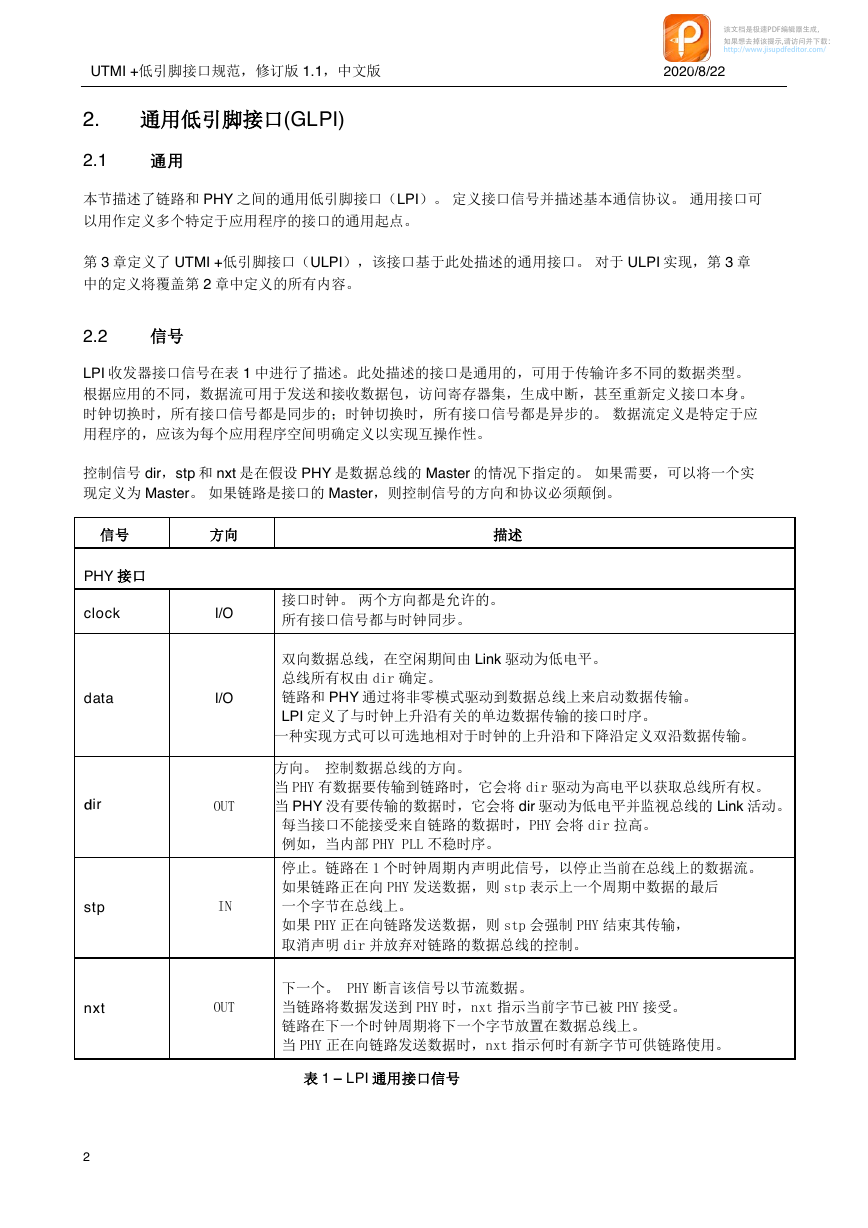

2. 通用低引脚接口(GLPI)

2.1

通用

本节描述了链路和 PHY 之间的通用低引脚接口(LPI)。 定义接口信号并描述基本通信协议。 通用接口可

以用作定义多个特定于应用程序的接口的通用起点。

第 3 章定义了 UTMI +低引脚接口(ULPI),该接口基于此处描述的通用接口。 对于 ULPI 实现,第 3 章

中的定义将覆盖第 2 章中定义的所有内容。

2.2

信号

LPI 收发器接口信号在表 1 中进行了描述。此处描述的接口是通用的,可用于传输许多不同的数据类型。

根据应用的不同,数据流可用于发送和接收数据包,访问寄存器集,生成中断,甚至重新定义接口本身。

时钟切换时,所有接口信号都是同步的;时钟切换时,所有接口信号都是异步的。 数据流定义是特定于应

用程序的,应该为每个应用程序空间明确定义以实现互操作性。

控制信号 dir,stp 和 nxt 是在假设 PHY 是数据总线的 Master 的情况下指定的。 如果需要,可以将一个实

现定义为 Master。 如果链路是接口的 Master,则控制信号的方向和协议必须颠倒。

信号

方向

描述

PHY 接口

clock

I/O

接口时钟。 两个方向都是允许的。

所有接口信号都与时钟同步。

data

I/O

dir

OUT

stp

IN

双向数据总线,在空闲期间由 Link 驱动为低电平。

总线所有权由 dir 确定。

链路和 PHY 通过将非零模式驱动到数据总线上来启动数据传输。

LPI 定义了与时钟上升沿有关的单边数据传输的接口时序。

一种实现方式可以可选地相对于时钟的上升沿和下降沿定义双沿数据传输。

方向。 控制数据总线的方向。

当 PHY 有数据要传输到链路时,它会将 dir 驱动为高电平以获取总线所有权。

当 PHY 没有要传输的数据时,它会将 dir 驱动为低电平并监视总线的 Link 活动。

每当接口不能接受来自链路的数据时,PHY 会将 dir 拉高。

例如,当内部 PHY PLL 不稳时序。

停止。链路在 1 个时钟周期内声明此信号,以停止当前在总线上的数据流。

如果链路正在向 PHY 发送数据,则 stp 表示上一个周期中数据的最后

一个字节在总线上。

如果 PHY 正在向链路发送数据,则 stp 会强制 PHY 结束其传输,

取消声明 dir 并放弃对链路的数据总线的控制。

nxt

OUT

下一个。 PHY 断言该信号以节流数据。

当链路将数据发送到 PHY 时,nxt 指示当前字节已被 PHY 接受。

链路在下一个时钟周期将下一个字节放置在数据总线上。

当 PHY 正在向链路发送数据时,nxt 指示何时有新字节可供链路使用。

表 1 – LPI 通用接口信号

2

该文档是极速PDF编辑器生成,如果想去掉该提示,请访问并下载:http://www.jisupdfeditor.com/�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc