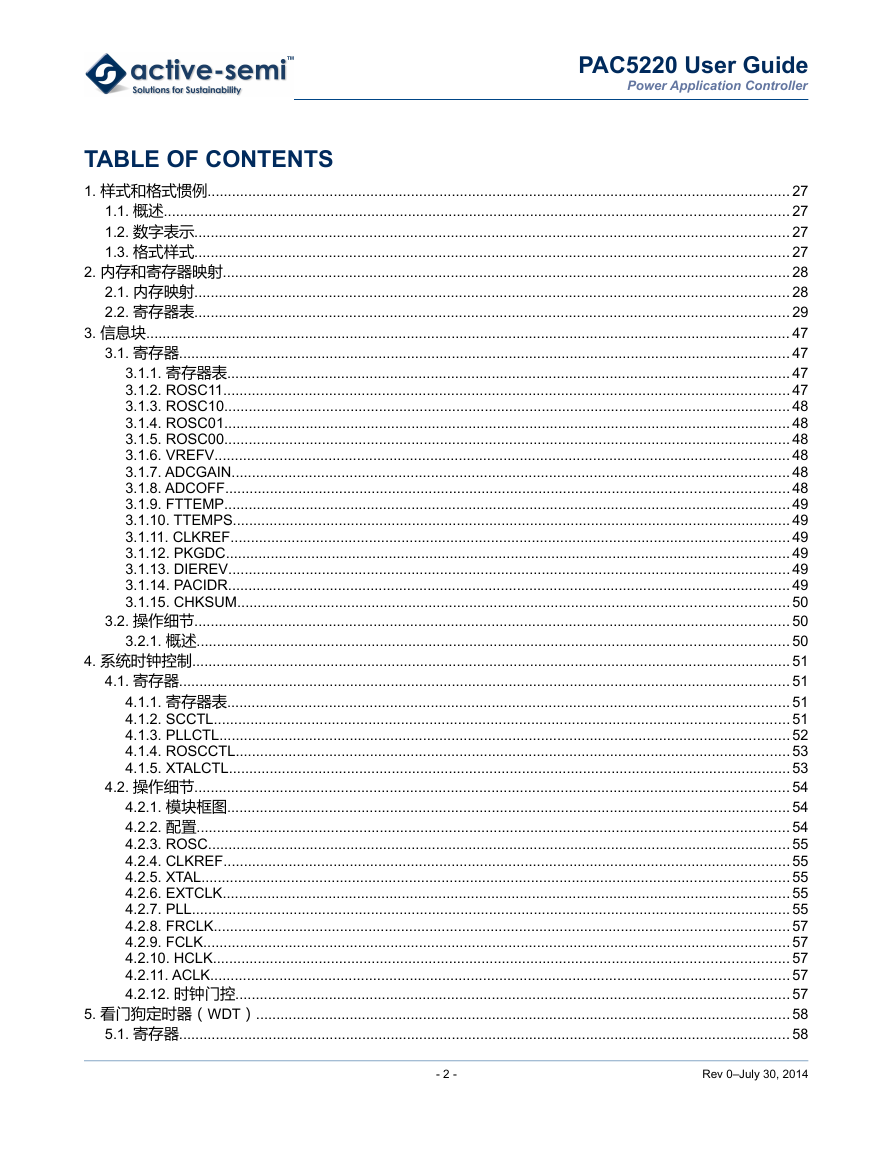

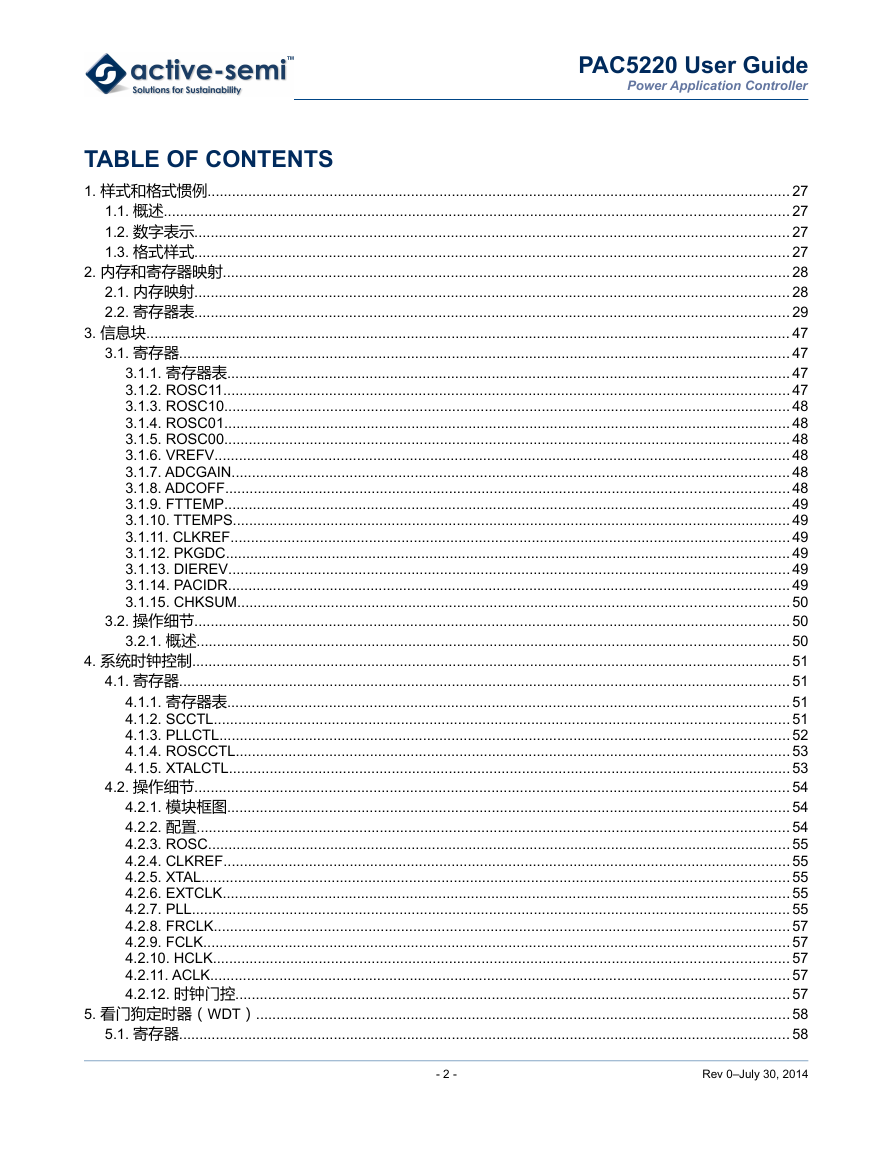

1. 样式和格式惯例

1.1. 概述

1.2. 数字表示

1.3. 格式样式

2. 内存和寄存器映射

2.1. 内存映射

2.2. 寄存器表

3. 信息块

3.1. 寄存器

3.1.1. 寄存器表

3.1.2. ROSC11

3.1.3. ROSC10

3.1.4. ROSC01

3.1.5. ROSC00

3.1.6. VREFV

3.1.7. ADCGAIN

3.1.8. ADCOFF

3.1.9. FTTEMP

3.1.10. TTEMPS

3.1.11. CLKREF

3.1.12. PKGDC

3.1.13. DIEREV

3.1.14. PACIDR

3.1.15. CHKSUM

3.2. 操作细节

3.2.1. 概述

4. 系统时钟控制

4.1. 寄存器

4.1.1. 寄存器表

4.1.2. SCCTL

4.1.3. PLLCTL

4.1.4. ROSCCTL

4.1.5. XTALCTL

4.2. 操作细节

4.2.1. 模块框图

4.2.2. 配置

4.2.3. ROSC

4.2.4. CLKREF

4.2.5. XTAL

4.2.6. EXTCLK

4.2.7. PLL

4.2.8. FRCLK

4.2.9. FCLK

4.2.10. HCLK

4.2.11. ACLK

4.2.12. 时钟门控

5. 看门狗定时器(WDT)

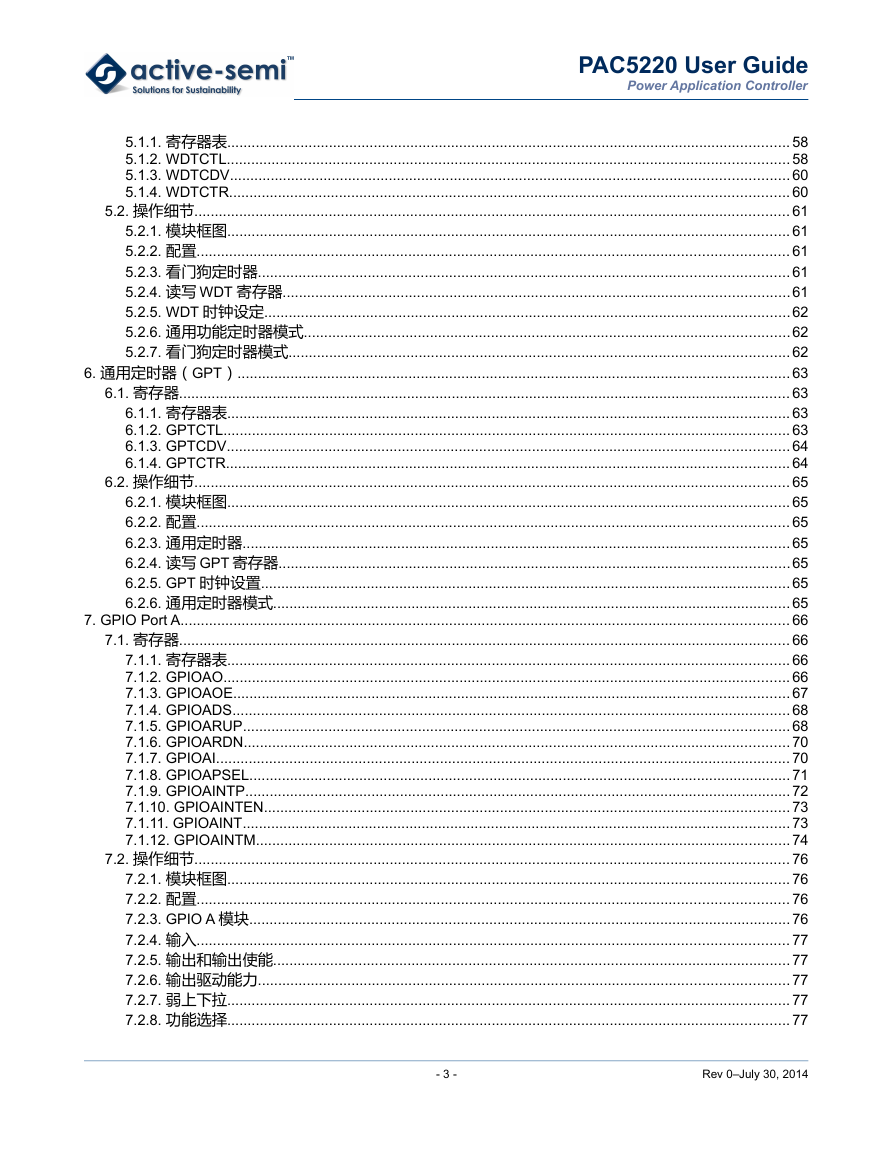

5.1. 寄存器

5.1.1. 寄存器表

5.1.2. WDTCTL

5.1.3. WDTCDV

5.1.4. WDTCTR

5.2. 操作细节

5.2.1. 模块框图

5.2.2. 配置

5.2.3. 看门狗定时器

5.2.4. 读写WDT 寄存器

5.2.5. WDT 时钟设定

5.2.6. 通用功能定时器模式

5.2.7. 看门狗定时器模式

6. 通用定时器(GPT)

6.1. 寄存器

6.1.1. 寄存器表

6.1.2. GPTCTL

6.1.3. GPTCDV

6.1.4. GPTCTR

6.2. 操作细节

6.2.1. 模块框图

6.2.2. 配置

6.2.3. 通用定时器

6.2.4. 读写GPT寄存器

6.2.5. GPT 时钟设置

6.2.6. 通用定时器模式

7. GPIO Port A

7.1. 寄存器

7.1.1. 寄存器表

7.1.2. GPIOAO

7.1.3. GPIOAOE

7.1.4. GPIOADS

7.1.5. GPIOARUP

7.1.6. GPIOARDN

7.1.7. GPIOAI

7.1.8. GPIOAPSEL

7.1.9. GPIOAINTP

7.1.10. GPIOAINTEN

7.1.11. GPIOAINT

7.1.12. GPIOAINTM

7.2. 操作细节

7.2.1. 模块框图

7.2.2. 配置

7.2.3. GPIO A 模块

7.2.4. 输入

7.2.5. 输出和输出使能

7.2.6. 输出驱动能力

7.2.7. 弱上下拉

7.2.8. 功能选择

7.2.9. 中断

8. GPIO Port B

8.1. 寄存器

8.1.1. 寄存器表

8.1.2. GPIOBO

8.1.3. GPIOBOE

8.1.4. GPIOBDS

8.1.5. GPIOBRUP

8.1.6. GPIOBRDN

8.1.7. GPIOBI

8.1.8. GPIOBPSEL

8.1.9. GPIOBINTP

8.1.10. GPIOBINTEN

8.1.11. GPIOBINT

8.1.12. GPIOBINTM

8.2. 操作细节

8.2.1. 模块框图

8.2.2. 配置

8.2.3. GPIO B 模块

8.2.4. 输入

8.2.5. 输出和输出使能

8.2.6. 输出驱动能力

8.2.7. 弱上下拉

8.2.8. 功能选择

8.2.9. 中断

9. GPIO Port C

9.1. 寄存器

9.1.1. 寄存器表

9.1.2. GPIOCO

9.1.3. GPIOCOE

9.1.4. GPIOCI

9.1.5. GPIOCIE

9.1.6. GPIOCINTP

9.1.7. GPIOCINTEN

9.1.8. GPIOCINT

9.1.9. GPIOCINTM

9.2. 操作细节

9.2.1. 模块框图

9.2.2. 配置

9.2.3. GPIO C 模块

9.2.4. 模拟输入

9.2.5. 输出和输出使能

9.2.6. 中断

10. GPIO Port D

10.1. 寄存器

10.1.1. 寄存器表

10.1.2. GPIODO

10.1.3. GPIODOE

10.1.4. GPIODDS

10.1.5. GPIODRUP

10.1.6. GPIODRDN

10.1.7. GPIODI

10.1.8. GPIODPSEL

10.1.9. GPIODINTP

10.1.10. GPIODINTEN

10.1.11. GPIODINT

10.1.12. GPIODINTM

10.2. 操作细节

10.2.1. 模块框图

10.2.2. 配置

10.2.3. GPIO D 模块

10.2.4. 输入

10.2.5. 输出和输出使能

10.2.6. 输出驱动能力

10.2.7. 弱上拉和弱下拉

10.2.8. 功能选择

10.2.9. 中断

11. GPIO Port E

11.1. 寄存器

11.1.1. 寄存器表

11.1.2. GPIOEO

11.1.3. GPIOEOE

11.1.4. GPIOEDS

11.1.5. GPIOERUP

11.1.6. GPIOERDN

11.1.7. GPIOEI

11.1.8. GPIOEPSEL

11.1.9. GPIOEINTP

11.1.10. GPIOEINTEN

11.1.11. GPIOEINT

11.1.12. GPIOEINTM

11.2. 操作细节

11.2.1. 模块框图

11.2.2. 配置

11.2.3. GPIO E 模块

11.2.4. 输入

11.2.5. 输出和输出使能

11.2.6. 输出驱动能力

11.2.7. 弱上拉和下拉

11.2.8. 功能选择

11.2.9. 中断

12. 定时器A

12.1. 寄存器

12.1.1. 寄存器表

12.1.2. TACTL

12.1.3. TAPRD

12.1.4. TACTR

12.1.5. TACC0CTL

12.1.6. TACC0CTR

12.1.7. TACC1CTL

12.1.8. TACC1CTR

12.1.9. TACC2CTL

12.1.10. TACC2CTR

12.1.11. TACC3CTL

12.1.12. TACC3CTR

12.1.13. TACC4CTL

12.1.14. TACC4CTR

12.1.15. TACC5CTL

12.1.16. TACC5CTR

12.1.17. TACC6CTL

12.1.18. TACC6CTR

12.1.19. TACC7CTL

12.1.20. TACC7CTR

12.1.21. DTGA0CTL

12.1.22. DTGA0LED

12.1.23. DTGA0TED

12.1.24. DTGA1CTL

12.1.25. DTGA1LED

12.1.26. DTGA1TED

12.1.27. DTGA2CTL

12.1.28. DTGA2LED

12.1.29. DTGA2TED

12.1.30. DTGA3CTL

12.1.31. DTGA3LED

12.1.32. DTGA3TED

12.2. 操作细节

12.2.1. 模块框图

12.2.2. 配置

12.2.3. 定时器A模块

12.2.4. 计数器

12.2.5. 寄存器更新

12.2.6. 计数模式

12.2.7. 单周期模式

12.2.8. 输入时钟源和分频

12.2.9. 定时器同步

12.2.10. PWM/捕获通道

12.2.10.1. PWM模式

12.2.10.2. 捕获模式

12.2.11. 计数器和PWM/捕获中断

12.2.12. 死区时间发生器

12.2.12.1. 死区时间输入时钟选择

12.2.12.2. 死区时间范围

12.2.12.3. 旁路模式

12.2.12.4. 翻转PWM信号

12.2.12.5. 死区时间插入

12.2.12.6. 上桥时间保持的死区插入

12.2.13. PWM输出和捕获输入引脚选择

13. 定时器B

13.1. 寄存器

13.1.1. 寄存器表

13.1.2. TBCTL

13.1.3. TBPRD

13.1.4. TBCTR

13.1.5. TBCC0CTL

13.1.6. TBCC0CTR

13.1.7. TBCC1CTL

13.1.8. TBCC1CTR

13.1.9. TBCC2CTL

13.1.10. TBCC2CTR

13.1.11. TBCC3CTL

13.1.12. TBCC3CTR

13.1.13. DTGB0CTL

13.1.14. DTGB0LED

13.1.15. DTGB0TED

13.2. 操作细节

13.2.1. 模块框图

13.2.2. 配置

13.2.3. 定时器B 模块

13.2.4. 计数器

13.2.5. 寄存器更新

13.2.6. 计数模式

13.2.7. 单周期模式

13.2.8. 输入时钟源和分频

13.2.9. 定时器同步

13.2.10. PWM/捕获通道

13.2.10.1. PWM 模式

13.2.10.2. 捕获模式

13.2.11. 计数器和PWM/捕获中断

13.2.12. 死区时间发生器

13.2.12.1. 死区时间输入时钟选择

13.2.12.2. 死区时间范围

13.2.12.3. 旁路模式

13.2.12.4. 翻转PWM信号

13.2.12.5. 死区时间插入

13.2.12.6. 上桥时间保持的死区插入

13.2.13. PWM 输出和捕获输入引脚选择

14. 定时器C

14.1. 寄存器

14.1.1. 寄存器表

14.1.2. TCCTL

14.1.3. TCPRD

14.1.4. TCCTR

14.1.5. TCCC0CTL

14.1.6. TCCC0CTR

14.1.7. TCCC1CTL

14.1.8. TCCC1CTR

14.1.9. DTGC0CTL

14.1.10. DTGC0LED

14.1.11. DTGC0TED

14.2. 操作细节

14.2.1. 模块框图

14.2.2. 配置

14.2.3. 定时器C模块

14.2.4. 计数器

14.2.5. 寄存器更新

14.2.6. 计数模式

14.2.7. 单周期模式

14.2.8. 输入时钟源和分频

14.2.9. 定时器同步

14.2.10. PWM/捕获通道

14.2.10.1. PWM 模式

14.2.10.2. 捕获模式

14.2.11. 计数器和PWM/捕获中断

14.2.12. 死区时间发生器

14.2.12.1. 死区时间输入时钟选择

14.2.12.2. 死区时间范围

14.2.12.3. 旁路模式

14.2.12.4. 翻转PWM信号

14.2.12.5. 死区时间插入

14.2.12.6. 上桥时间保持的死区插入

14.2.13. PWM 输出和捕获输入引脚选择

15. 定时器D

15.1. 寄存器

15.1.1. 寄存器表

15.1.2. TDCTL

15.1.3. TDPRD

15.1.4. TDCTR

15.1.5. TDCC0CTL

15.1.6. TDCC0CTR

15.1.7. TDCC1CTL

15.1.8. TDCC1CTR

15.1.9. DTGD0CTL

15.1.10. DTGD0LED

15.1.11. DTGD0TED

15.2. 操作细节

15.2.1. 模块框图

15.2.2. 配置

15.2.3. 定时器D模块

15.2.4. 计数器

15.2.5. 寄存器更新

15.2.6. 计数模式

15.2.7. 单周期模式

15.2.8. 输入时钟源和分频

15.2.9. 定时器同步

15.2.10. PWM/捕获通道

15.2.10.1. PWM 模式

15.2.10.2. 捕获模式

15.2.11. 计数器和PWM/捕获中断

15.2.12. 死区时间发生器

15.2.12.1. 死区时间输入时钟选择

15.2.12.2. 死区时间范围

15.2.12.3. 旁路模式

15.2.12.4. 翻转PWM信号

15.2.12.5. 死区时间插入

15.2.12.6. 上桥时间保持的死区插入

15.2.13. PWM 输出和捕获输入引脚选择

16. FLASH内存控制

16.1. 寄存器

16.1.1. 寄存器表

16.1.2. FLASHLOCK

16.1.3. FLASHSTATUS

16.1.4. FLASHPAGE

16.1.5. FLASHPERASE

16.1.6. SWDACCESS

16.1.7. FLASHWSTATE

16.1.8. FLASHBWRITE

16.1.9. FLASHBWDATA

16.2. 操作细节

16.2.1. 模块框图

16.2.2. 配置

16.2.3. FLASH 内存

16.2.4. 对FLASH控制寄存器的写入操作

16.2.5. FLASH 等待周期

16.2.6. FLASH 页擦除

16.2.7. 写入FLASH

16.2.8. 缓冲写入FLASH

16.2.9. SWD访问禁止

17. ADC和自动转换序列

17.1. 寄存器

17.1.1. 寄存器表

17.1.2. EMUXCTL

17.1.3. EMUXDATA

17.1.4. ADCCTL

17.1.5. ADCCR

17.1.6. ADCINT

17.1.7. AS0CTL

17.1.8. AS0S0

17.1.9. AS0R0

17.1.10. AS0S1

17.1.11. AS0R1

17.1.12. AS0S2

17.1.13. AS0R2

17.1.14. AS0S3

17.1.15. AS0R3

17.1.16. AS0S4

17.1.17. AS0R4

17.1.18. AS0S5

17.1.19. AS0R5

17.1.20. AS0S6

17.1.21. AS0R6

17.1.22. AS0S7

17.1.23. AS0R7

17.1.24. AS1CTL

17.1.25. AS1S0

17.1.26. AS1R0

17.1.27. AS1S1

17.1.28. AS1R1

17.1.29. AS1S2

17.1.30. AS1R2

17.1.31. AS1S3

17.1.32. AS1R3

17.1.33. AS1S4

17.1.34. AS1R4

17.1.35. AS1S5

17.1.36. AS1R5

17.1.37. AS1S6

17.1.38. AS1R6

17.1.39. AS1S7

17.1.40. AS1R7

17.2. 操作细节

17.2.1. 模块框图

17.2.2. 基本配置

17.2.3. ADC,自动转换序列和EMUX

17.2.4. 时钟设定

17.2.5. ADC

17.2.6. EMUX

17.2.7. 自动转换序列 ASC0,ASC1

17.2.7.1. 自动转换序列模式

17.2.7.2. 序列触发

17.2.7.3. ASC 采样通道

17.2.7.4. ASC0,ASC1 优先级和冲突

18. I2C

18.1. 寄存器

18.1.1. 寄存器表

18.1.2. I2CCFG

18.1.3. I2CINT

18.1.4. I2CINTEN

18.1.5. I2CMACTL

18.1.6. I2CMARXDATA

18.1.7. I2CMATXDATA

18.1.8. I2CBAUD

18.1.9. I2CSLRXDATA

18.1.10. I2CSLTXDATA

18.1.11. I2CSLADDR

18.2. 操作细节

18.2.1. 模块框图

18.2.2. 配置

18.2.3. I2C

18.2.4. I2C 时钟设定

18.2.5. I2C 地址

19. UART

19.1. 寄存器

19.1.1. 寄存器表

19.1.2. UARTRXTX/UARTDL_L

19.1.3. UARTIEN/UARTDL_H

19.1.4. UARTII

19.1.5. UARTLC

19.1.6. UARTLS

19.1.7. UARTFCTL

19.1.8. UARTIEN

19.1.9. UARTDL_L

19.1.10. UARTDL_H

19.1.11. UARTFD_F

19.1.12. UARTFD_CTL

19.1.13. UARTFSTAT

19.2. 操作细节

19.2.1. 模块框图

19.2.2. 配置

19.2.3. UART

19.2.4. UART 时钟频率设定

19.2.5. 数据设定

19.2.6. FIFO 设定

19.2.7. 接收数据上的错误检查

20. SOC 总线桥

20.1. 寄存器

20.1.1. 寄存器表

20.1.2. SOCBCTL

20.1.3. SOCBCFG

20.1.4. SOCBCLKDIV

20.1.5. SOCBSTAT

20.1.6. SOCBD

20.1.7. SOCBINT_EN

20.2. 操作细节

20.2.1. 模块框图

20.2.2. 配置

20.2.3. SOC总线桥

20.2.4. SOC总线桥时钟频率设定

20.2.5. 使能并且建立SOC总线桥

20.2.6. SOC 中断

20.2.7. SOC总线桥协议

20.2.8. SOC总线桥读操作

20.2.9. SOC总线桥写操作

21. SPI

21.1. 寄存器

21.1.1. 寄存器表

21.1.2. SPICTL

21.1.3. SPICFG

21.1.4. SPICLKDIV

21.1.5. SPISTAT

21.1.6. SPICSSTR

21.1.7. SPID

21.1.8. SPIINT_EN

21.2. 操作细节

21.2.1. 模块框图

21.2.2. 配置

21.2.3. SPI

21.2.4. SPI 时钟频率设置

21.2.5. 主机/从机模式

21.2.6. 时钟相位和极性

21.2.7. SPI数据发送相位提前

21.2.8. 数据格式

21.2.9. 片选设定

21.2.10. 自动重发数据字

21.2.11. 环回模式

21.2.12. SPI中断

21.2.13. SPI 使能

22. 多模式电源管理模块

22.1. 寄存器

22.1.1. 寄存器表

22.1.2. SOC.SYSSTAT

22.1.3. SOC.PWRCTL

22.1.4. SOC.PWRSTAT

22.1.5. SOC.PWRSTATCFG

22.1.6. SOC.SCFG

22.1.7. SOC.PWRCFG

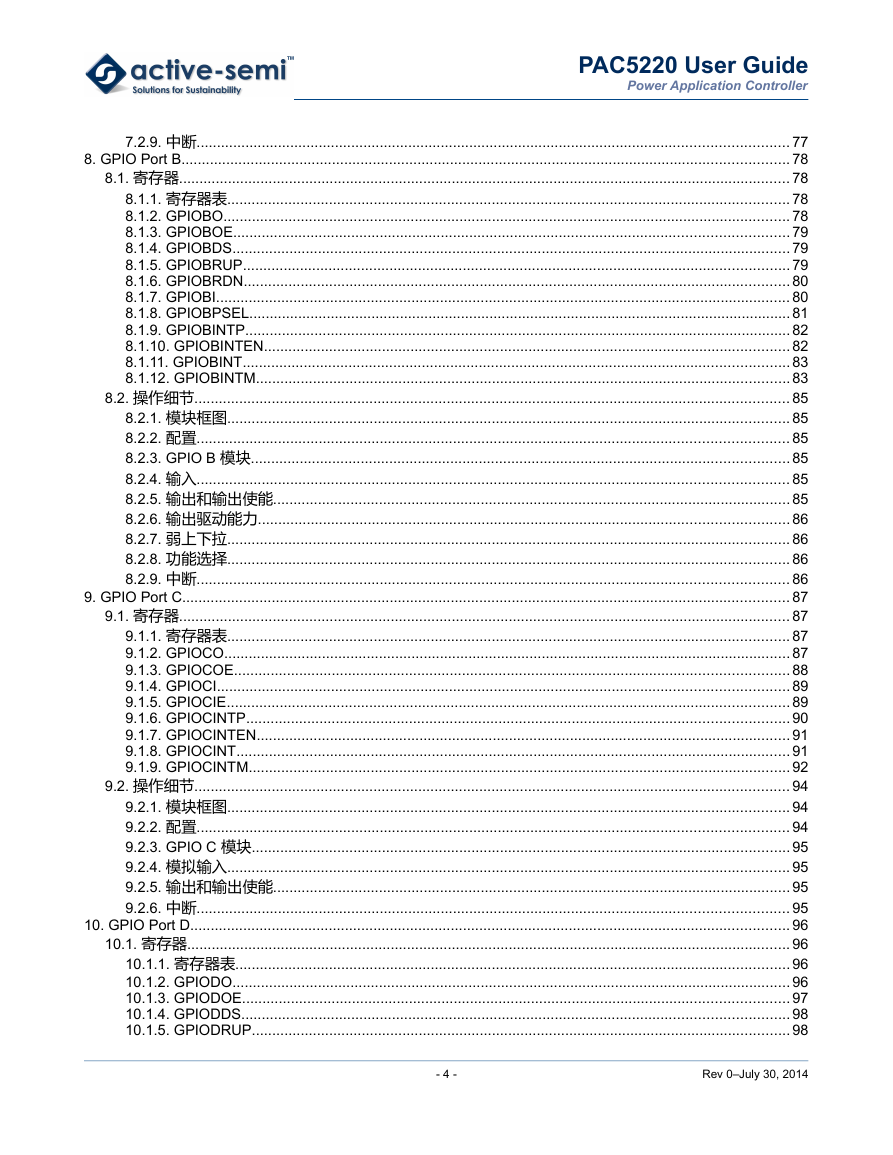

23. 模拟前端总线

23.1. 寄存器

23.1.1. 寄存器表

23.1.2. SOC.AIO0CFG

23.1.3. SOC.AIO1CFG

23.1.4. SOC.AIO2CFG

23.1.5. SOC.AIO3CFG

23.1.6. SOC.AIO4CFG

23.1.7. SOC.AIO5CFG

23.1.8. SOC.AIO6CFG

23.1.9. SOC.AIO7CFG

23.1.10. SOC.AIO8CFG

23.1.11. SOC.AIO9CFG

23.1.12. SOC.SMCFG

23.1.13. SOC.HPDAC

23.1.14. SOC.LPDAC0

23.1.15. SOC.LPDAC1

23.1.16. SOC.ADCSCANCFG

23.1.17. SOC.ADMUX

23.1.18. SOC.PROTINTEN

23.1.19. SOC.PROTINT

23.1.20. SOC.AIOOUT0

23.1.21. SOC.AIOOUT1

23.1.22. SOC.AIOIN0

23.1.23. SOC.AIOIN1

23.1.24. SOC.AIOINTEN

23.1.25. SOC.AIOINT

23.1.26. SOC.SMCTL

23.2. 操作细节

23.2.1. 模块框图

23.2.2. 配置

23.2.3. 模拟前端总线

23.2.3.1. 模拟前端总线使能

23.3. AIO1, AIO0

23.3.1. 模块框图

23.3.2. AIO1, AIO0

23.3.3. AIO1, AIO0 数字I/O模式

23.3.3.1. AIO0 IO

23.3.3.2. AIO1 IO

23.3.3.3. AIO0 极性

23.3.3.4. AIO1 极性

23.3.4. AIO1, AIO0 差分放大模式

23.3.4.1. AIO1, AIO0 差分放大器放大倍率

23.3.4.2. AIO1, AIO0 差分放大器参考电压

23.3.4.3. AIO1, AIO0 差分放大器校准模式

23.3.5. AIO1, AIO0 保护

23.3.5.1. HP10 比较器

23.3.5.2. LP10 比较器

23.4. AIO3, AIO2

23.4.1. 模块框图

23.4.2. AIO3, AIO2

23.4.3. AIO3, AIO2 数字I/O模式

23.4.3.1. AIO2 IO

23.4.3.2. AIO3 IO

23.4.3.3. AIO2 极性

23.4.3.4. AIO3 极性

23.4.4. AIO3, AIO2 差分放大模式

23.4.4.1. AIO3, AIO2 差分放大器放大倍率

23.4.4.2. AIO3, AIO2 差分放大器参考电压

23.4.4.3. AIO3, AIO2 差分放大器校准模式

23.4.5. AIO3, AIO2 保护

23.4.5.1. HP32 比较器

23.4.5.2. LP32 比较器

23.5. AIO5, AIO4

23.5.1. 模块框图

23.5.2. AIO5, AIO4

23.5.3. AIO5, AIO4 数字I/O模式

23.5.3.1. AIO4 IO

23.5.3.2. AIO5 IO

23.5.3.3. AIO4 极性

23.5.3.4. AIO5 极性

23.5.4. AIO5, AIO4 差分放大模式

23.5.4.1. AIO5, AIO4 差分放大器放大倍率

23.5.4.2. AIO5, AIO4 差分放大器参考电压

23.5.4.3. AIO5, AIO4 差分放大器校准模式

23.5.5. AIO5, AIO4 保护

23.5.5.1. HP54 比较器

23.5.5.2. LP54 比较器

23.6. AIO6

23.6.1. 模块框图

23.6.2. AIO6

23.6.3. AIO6 数字I/O模式

23.6.3.1. AIO6 IO

23.6.3.2. AIO6 IO 中断

23.6.3.3. AIO6 极性

23.6.4. AIO6 单端放大器模式

23.6.4.1. AIO6 单端放大倍数

23.6.4.2. AIO6 模拟MUX

23.6.5. AIO6 比较器模式

23.6.5.1. AIO6 比较器迟滞

23.6.5.2. AIO6 比较器参考电压

23.6.5.3. AIO6 比较器极性

23.6.5.4. AIO6 比较器输出MUX

23.6.6. AIO6 特殊模式

23.6.6.1. AIO6 特殊模式MUX

23.6.6.2. AIO6 特殊模式 ADMUX

23.6.6.3. AIO6 特殊模式偏移交换

23.6.7. AIO6 唤醒按键模式

23.6.7.1. AIO6 休眠唤醒

23.6.7.2. AIO6 按键休眠

23.6.7.3. AIO6 按键复位

23.7. AIO7

23.7.1. 模块框图

23.7.2. AIO7

23.7.3. AIO7 数字I/O模式

23.7.3.1. AIO7 IO

23.7.3.2. AIO7 IO 中断

23.7.3.3. AIO7 极性

23.7.4. AIO7 单端放大器模式

23.7.4.1. AIO7 单端放大倍数

23.7.4.2. AIO7 模拟MUX

23.7.5. AIO7 比较器模式

23.7.5.1. AIO7 比较器迟滞

23.7.5.2. AIO7 比较器参考电压

23.7.5.3. AIO7 比较器极性

23.7.5.4. AIO7 比较器输出

23.7.6. AIO7 特殊模式

23.7.6.1. AIO7 比较器参考电压

23.7.6.2. AIO7 比较器参考电压星形连接点

23.7.6.3. AIO7 电压读取

23.7.6.4. AIO7 比较器输出

23.7.6.5. AIO7 POS采样保持器旁路

23.7.6.6. AIO7 nIRQ2/POS 选择器

23.8. AIO8

23.8.1. 模块框图

23.8.2. AIO8

23.8.3. AIO8 数字I/O模式

23.8.3.1. AIO8 IO

23.8.3.2. AIO8 IO 中断

23.8.3.3. AIO8 极性

23.8.4. AIO8 单端放大器模式

23.8.4.1. AIO8 单端放大倍数

23.8.4.2. AIO8 模拟MUX

23.8.5. AIO8 比较器模式

23.8.5.1. AIO8 比较器迟滞

23.8.5.2. AIO8 比较器参考电压

23.8.5.3. AIO8 比较器极性

23.8.5.4. AIO8 比较器输出

23.8.6. AIO8 特殊模式

23.8.6.1. AIO8 比较器参考电压

23.8.6.2. AIO8 比较器参考电压星形连接点

23.8.6.3. AIO8 电压读取

23.8.6.4. AIO8 比较器输出

23.8.6.5. AIO8 POS采样保持器旁路

23.8.6.6. AIO8 nIRQ2/POS 选择器

23.9. AIO9

23.9.1. 模块框图

23.9.2. AIO9

23.9.3. AIO9 数字I/O模式

23.9.3.1. AIO9 IO

23.9.3.2. AIO9 IO 中断

23.9.3.3. AIO9 极性

23.9.4. AIO9 单端放大器模式

23.9.4.1. AIO9 单端放大倍数

23.9.4.2. AIO9 模拟MUX

23.9.5. AIO9 比较器模式

23.9.5.1. AIO9 比较器迟滞

23.9.5.2. AIO9 比较器参考电压

23.9.5.3. AIO9 比较器极性

23.9.5.4. AIO9 比较器输出

23.9.6. AIO9 特殊模式

23.9.6.1. AIO9 比较器参考电压

23.9.6.2. AIO9 比较器参考电压星形连接点

23.9.6.3. AIO9 电压读取

23.9.6.4. AIO9 比较器输出

23.9.6.5. AIO9 POS采样保持器旁路

23.9.6.6. AIO9 nIRQ2/POS 选择器

23.10. ENHS1,ENLS1 保护

23.10.1. 模块框图

23.10.2. ENHS1,ENLS1 保护

23.10.2.1. ENLS1 保护使能

23.10.2.2. ENHS1 保护使能

23.11. EMUX和ADMUX

23.11.1. 模块框图

23.11.2. EMUX

23.11.2.1. EMUX 使能

23.11.2.2. EMUXD 数据包的结构

23.11.2.3. EMUX 时序

23.11.3. ADMUX

23.11.3.1. ADMUX 控制

23.11.3.2. ADMUX 缓冲器

23.11.3.3. ADMUX

24. 针对应用定制的功率驱动单元

24.1. 寄存器

24.1.1. 寄存器表

24.1.2. SOC.DRVCFG0

24.1.3. SOC.DRVCFG1

24.1.4. SOC.OHI6CFG

24.1.5. SOC.OHI7CFG

24.1.6. SOC.OHIOUT

24.1.7. SOC.OHIIN

24.1.8. SOC.DRVCTL

24.1.9. SOC.BBMCTL

24.1.10. SOC.HDTCTL

24.2. 操作细节

24.2.1. 模块框图

24.2.2. 配置

24.2.3. 针对应用定制的功率驱动单元

24.2.3.1. 功率驱动单元使能

24.3. DRL0 下桥驱动

24.3.1. 模块框图

24.3.2. DRL0

24.3.2.1. DRL0 传输延迟

24.3.2.2. DRL0 使能

24.3.2.3. 先断后合控制

24.3.2.4. 硬件死区时间控制

24.4. DRL1 下桥驱动

24.4.1. 模块框图

24.4.2. DRL1

24.4.2.1. DRL1 传输延迟

24.4.2.2. DRL1 使能

24.4.2.3. 先断后合控制

24.4.2.4. 硬件死区时间控制

24.5. DRL2 下桥驱动

24.5.1. 模块框图

24.5.2. DRL2

24.5.2.1. DRL2 传输延迟

24.5.2.2. DRL2 使能

24.5.2.3. 先断后合控制

24.5.2.4. 硬件死区时间控制

24.6. DRH3 上桥驱动

24.6.1. 模块框图

24.6.2. DRH3

24.6.2.1. DRH3 传输延迟

24.6.2.2. DRH3 使能

24.6.2.3. 先断后合控制

24.6.2.4. 硬件死区时间控制

24.7. DRH4 上桥驱动

24.7.1. 模块框图

24.7.2. DRH4

24.7.2.1. DRH4 传输延迟

24.7.2.2. DRH4 使能

24.7.2.3. 先断后合控制

24.7.2.4. 硬件死区时间控制

24.8. DRH5 上桥驱动

24.8.1. 模块框图

24.8.2. DRH5

24.8.2.1. DRH5 传输延迟

24.8.2.2. DRH5 使能

24.8.2.3. 先断后合控制

24.8.2.4. 硬件死区时间控制

24.9. OHI6

24.9.1. 模块框图

24.9.2. OHI6

24.9.2.1. OHI6 数字I/O

24.9.2.2. OHI6 极性

24.10. OHI7

24.10.1. 模块框图

24.10.2. OHI7

24.10.2.1. OHI7 数字I/O

24.10.2.2. OHI7 极性

25. Arm Cortex-M0 参考

25.1. 介绍

25.1.1. 概述

25.1.2. 关于Cortex-M0处理器内核和外设

25.1.2.1. 系统级中断

25.1.2.2. 集成的可配置调试接口

25.1.2.3. Cortex-M0 处理器功能汇总

25.1.2.4. Cortex-M0 核心外设

25.1.2.4.1. NVIC

25.1.2.4.2. 系统控制模块

25.1.2.4.3. 系统定时器

25.2. Cortex-M0 处理器

25.2.1. 编程模型

25.2.1.1. 处理器模式

25.2.1.2. 栈

25.2.1.3. 内核寄存器

25.2.1.3.1. 通用寄存器

25.2.1.3.2. 堆栈指针

25.2.1.3.3. 链接寄存器

25.2.1.3.4. 程序计数器

25.2.1.3.5. 程序状态寄存器

25.2.1.3.6. 应用程序状态寄存器

25.2.1.3.7. 中断程序状态寄存器

25.2.1.3.8. 异常程序状态寄存器

25.2.1.3.9. 中断性的重启指令

25.2.1.3.10. 异常屏蔽寄存器

25.2.1.3.11. 优先级屏蔽寄存器

25.2.1.3.12. 控制寄存器

25.2.1.4. 异常和中断

25.2.1.5. 数据类型

25.2.1.6. Cortex微控制器软件接口标准

25.2.2. 内存模型

25.2.2.1. 存储区,类型和属性

25.2.2.1.1. 普通

25.2.2.1.2. 设备

25.2.2.1.3. 强有序

25.2.2.1.4. 永不执行区 (XN)

25.2.2.2. 内存访问顺序的存储系统

25.2.2.3. 内存访问行为

25.2.2.4. 内存访问的软件顺序

25.2.2.4.1. DMB

25.2.2.4.2. DSB

25.2.2.4.3. ISB

25.2.2.4.4. 向量表

25.2.2.4.5. 自修正代码

25.2.2.4.6. 内存映射切换

25.2.2.5. 字节存储顺序

25.2.2.5.1. 小端格式

25.2.3. 异常模块

25.2.3.1. 异常状态

25.2.3.1.1. 非活动

25.2.3.1.2. 挂起

25.2.3.1.3. 活动

25.2.3.1.4. 活动并挂起

25.2.3.2. 异常类型

25.2.3.2.1. 复位异常

25.2.3.2.2. NMI

25.2.3.2.3. 硬件故障

25.2.3.2.4. SVCall

25.2.3.2.5. PendSV

25.2.3.2.6. SysTick

25.2.3.2.7. 中断(IRQ)

25.2.3.3. 异常处理

25.2.3.3.1. 中断服务程序(ISRs)

25.2.3.3.2. 故障处理

25.2.3.3.3. System handlers

25.2.3.4. 向量表

25.2.3.5. 异常优先级

25.2.3.6. 异常入口和回归

25.2.3.6.1. 抢占

25.2.3.6.2. 回归

25.2.3.6.3. 尾联

25.2.3.6.4. 迟到

25.2.3.6.5. 异常入口

25.2.3.6.6. 异常回归

25.2.4. 故障处理

25.2.4.1. 锁定

25.2.5. 电源管理模块

25.2.5.1. 进入睡眠模式

25.2.5.1.1. 等待中断

25.2.5.1.2. 等待事件

25.2.5.1.3. Sleep-on-exit

25.2.5.2. 从睡眠模式唤醒

25.2.5.2.1. 从WFI 或 sleep-on-exit唤醒

25.2.5.2.2. 从WFE唤醒

25.2.5.3. 唤醒中断控制

25.2.5.4. 外部事件输入

25.2.5.5. 电源管理编程提示

25.3. Cortex-M0指令设置

25.3.1. 指令集汇总

25.3.2. 内部函数

25.3.3. 关于指令描述

25.3.3.1. 操作数

25.3.3.2. 使用PC或SP时的限制

25.3.3.3. 位操作

25.3.3.3.1. ASR

25.3.3.3.2. LSR

25.3.3.3.3. LSL

25.3.3.3.4. ROR

25.3.3.4. 地址对齐

25.3.3.5. PC相对的表达式

25.3.3.6. 条件执行

25.3.3.6.1. 条件标志位

25.3.3.6.2. 条件码后缀

25.3.4. 内存访问指令

25.3.4.1. ADR

25.3.4.1.1. 语法

25.3.4.1.2. 操作

25.3.4.1.3. 限制

25.3.4.1.4. 状态标志位

25.3.4.1.5. 示例

25.3.4.2. LDR和STR,直接偏移量

25.3.4.2.1. 语法

25.3.4.2.2. 操作

25.3.4.2.3. 限制

25.3.4.2.4. 状态标志位

25.3.4.2.5. 示例

25.3.4.3. LDR和STR,寄存器偏移

25.3.4.3.1. 语法

25.3.4.3.2. 操作

25.3.4.3.3. 限制

25.3.4.3.4. 状态标志位

25.3.4.3.5. 示例

25.3.4.4. LDR, PC-relative

25.3.4.4.1. 语法

25.3.4.4.2. 操作

25.3.4.4.3. 限制

25.3.4.4.4. 状态标志位

25.3.4.4.5. 示例

25.3.4.5. LDM 和 STM

25.3.4.5.1. 语法

25.3.4.5.2. 操作

25.3.4.5.3. 限制

25.3.4.5.4. 状态标志位

25.3.4.5.5. 示例

25.3.4.5.6. 错误示例

25.3.4.6. PUSH 和 POP

25.3.4.6.1. 语法

25.3.4.6.2. 操作

25.3.4.6.3. 限制

25.3.4.6.4. 状态标志位

25.3.4.6.5. 示例

25.3.5. 通用数据处理指令

25.3.5.1. ADC, ADD, RSB, SBC, and SUB

25.3.5.1.1. 语法

25.3.5.1.2. 操作

25.3.5.1.3. 限制

25.3.5.1.4. 示例

25.3.5.2. AND, ORR, EOR, and BIC

25.3.5.2.1. 语法

25.3.5.2.2. 操作

25.3.5.2.3. 限制

25.3.5.2.4. 状态标志位

25.3.5.2.5. 示例

25.3.5.3. ASR,LSL,LSR和ROR

25.3.5.3.1. 语法

25.3.5.3.2. 操作

25.3.5.3.3. 限制

25.3.5.3.4. 状态标志位

25.3.5.3.5. 示例

25.3.5.4. CMP 和 CMN

25.3.5.4.1. 语法

25.3.5.4.2. 操作

25.3.5.4.3. 限制

25.3.5.4.4. 状态标志位

25.3.5.4.5. 示例

25.3.5.5. MOV 和 MVN

25.3.5.5.1. 语法

25.3.5.5.2. 操作

25.3.5.5.3. 限制

25.3.5.5.4. 状态标志位

25.3.5.5.5. 示例

25.3.5.6. MULS

25.3.5.6.1. 语法

25.3.5.6.2. 操作

25.3.5.6.3. 限制

25.3.5.6.4. 状态标志位

25.3.5.6.5. 示例

25.3.5.7. REV, REV16和 REVSH

25.3.5.7.1. 语法

25.3.5.7.2. 操作

25.3.5.7.3. 限制

25.3.5.7.4. 状态标志位

25.3.5.7.5. 示例

25.3.5.8. SXT 和 UXT

25.3.5.8.1. 语法

25.3.5.8.2. 操作

25.3.5.8.3. 限制

25.3.5.8.4. 状态标志位

25.3.5.8.5. 示例

25.3.5.9. TST

25.3.5.9.1. 语法

25.3.5.9.2. 操作

25.3.5.9.3. 限制

25.3.5.9.4. 状态标志位

25.3.5.9.5. 示例

25.3.6. 跳转和控制指令

25.3.6.1. B, BL, BX, and BLX

25.3.6.1.1. 语法

25.3.6.1.2. 操作

25.3.6.1.3. 限制

25.3.6.1.4. 状态标志位

25.3.6.1.5. 示例

25.3.7. 其他指令

25.3.7.1. BKPT

25.3.7.1.1. 语法

25.3.7.1.2. 操作

25.3.7.1.3. 限制

25.3.7.1.4. 状态标志位

25.3.7.1.5. 示例

25.3.7.2. CPS

25.3.7.2.1. 语法

25.3.7.2.2. 操作

25.3.7.2.3. 限制

25.3.7.2.4. 状态标志位

25.3.7.2.5. 示例

25.3.7.3. DMB

25.3.7.3.1. 语法

25.3.7.3.2. 操作

25.3.7.3.3. 限制

25.3.7.3.4. 状态标志位

25.3.7.3.5. 示例

25.3.7.4. DSB

25.3.7.4.1. 语法

25.3.7.4.2. 操作

25.3.7.4.3. 限制

25.3.7.4.4. 状态标志位

25.3.7.4.5. 示例

25.3.7.5. ISB

25.3.7.5.1. 语法

25.3.7.5.2. 操作

25.3.7.5.3. 限制

25.3.7.5.4. 状态标志位

25.3.7.5.5. 示例

25.3.7.6. MRS

25.3.7.6.1. 语法

25.3.7.6.2. 操作

25.3.7.6.3. 限制

25.3.7.6.4. 状态标志位

25.3.7.6.5. 示例

25.3.7.7. MSR

25.3.7.7.1. 语法

25.3.7.7.2. 操作

25.3.7.7.3. 限制

25.3.7.7.4. 状态标志位

25.3.7.7.5. 示例

25.3.7.8. NOP

25.3.7.8.1. 语法

25.3.7.8.2. 操作

25.3.7.8.3. 限制

25.3.7.8.4. 状态标志位

25.3.7.8.5. 示例

25.3.7.9. SEV

25.3.7.9.1. 语法

25.3.7.9.2. 操作

25.3.7.9.3. 限制

25.3.7.9.4. 状态标志位

25.3.7.9.5. 示例

25.3.7.10. SVC

25.3.7.10.1. 语法

25.3.7.10.2. 操作

25.3.7.10.3. 限制

25.3.7.10.4. 状态标志位

25.3.7.10.5. 示例

25.3.7.11. WFE

25.3.7.11.1. 语法

25.3.7.11.2. 操作

25.3.7.11.3. 限制

25.3.7.11.4. 状态标志位

25.3.7.11.5. 示例

25.3.7.12. WFI

25.3.7.12.1. 语法

25.3.7.12.2. 操作

25.3.7.12.3. 限制

25.3.7.12.4. 状态标志位

25.3.7.12.5. 示例

25.4. Cortex-M0外设

25.4.1. 关于Cortex-M0外设

25.4.2. 嵌套向量中断控制器

25.4.2.1. 使用CMSIS访问Cortex-M0 NVIC寄存器

25.4.2.2. 中断设置使能寄存器

25.4.2.3. 中断清使能寄存器

25.4.2.4. 中断挂起设置寄存器

25.4.2.5. 中断清挂起设置寄存器

25.4.2.6. 中断优先级寄存器

25.4.2.7. 电平和边沿中断

25.4.2.7.1. 中断控制的软件和硬件

25.4.2.8. NVIC的使用提示和技巧

25.4.2.8.1. NVIC 编程提示

25.4.3. 系统控制模块

25.4.3.1. CMSIS Cortex-M0 SCB寄存器映射

25.4.3.2. CPUID寄存器

25.4.3.3. 中断控制和状态寄存器

25.4.3.4. 应用中断和复位控制寄存器

25.4.3.5. System 控制寄存器

25.4.3.6. 配置和控制寄存器

25.4.3.7. 系统处理优先级寄存器

25.4.3.7.1. 系统处理优先级寄存器 2

25.4.3.7.2. 系统处理优先级寄存器 3

25.4.3.8. SCB的使用提示和技巧

25.4.4. 系统定时器,SysTick

25.4.4.1. SysTick 控制和状态寄存器

25.4.4.2. SysTick 重载值寄存器

25.4.4.2.1. 计算RELOAD值

25.4.4.3. SysTick当前值寄存器

25.4.4.4. SysTick校准值寄存器

25.4.4.5. SysTick使用提示和技巧

26. 法律信息及免责声明

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc