进行Altera FPGA开发入门

Author : Bradley Feng Date :2016.07.20

Tel :18682383361

开发环境 :Quartus II 16.0

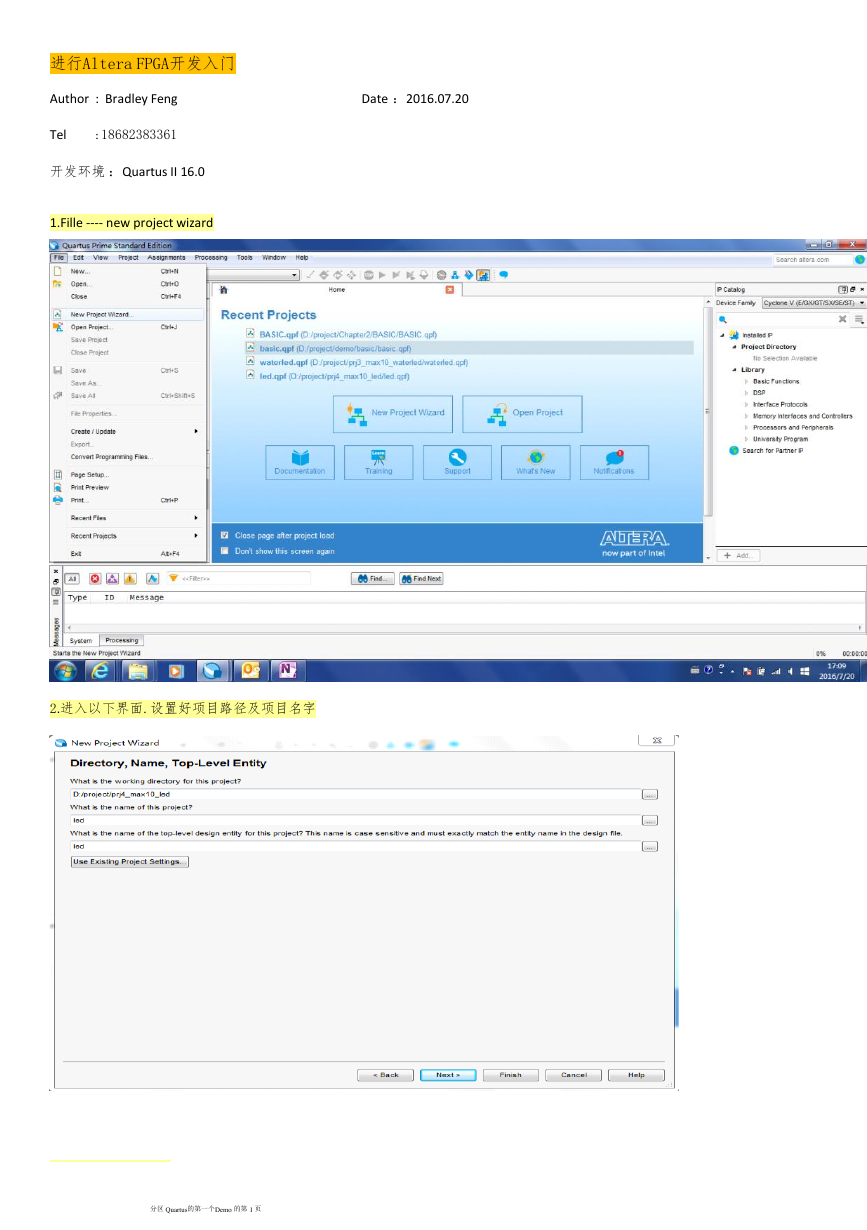

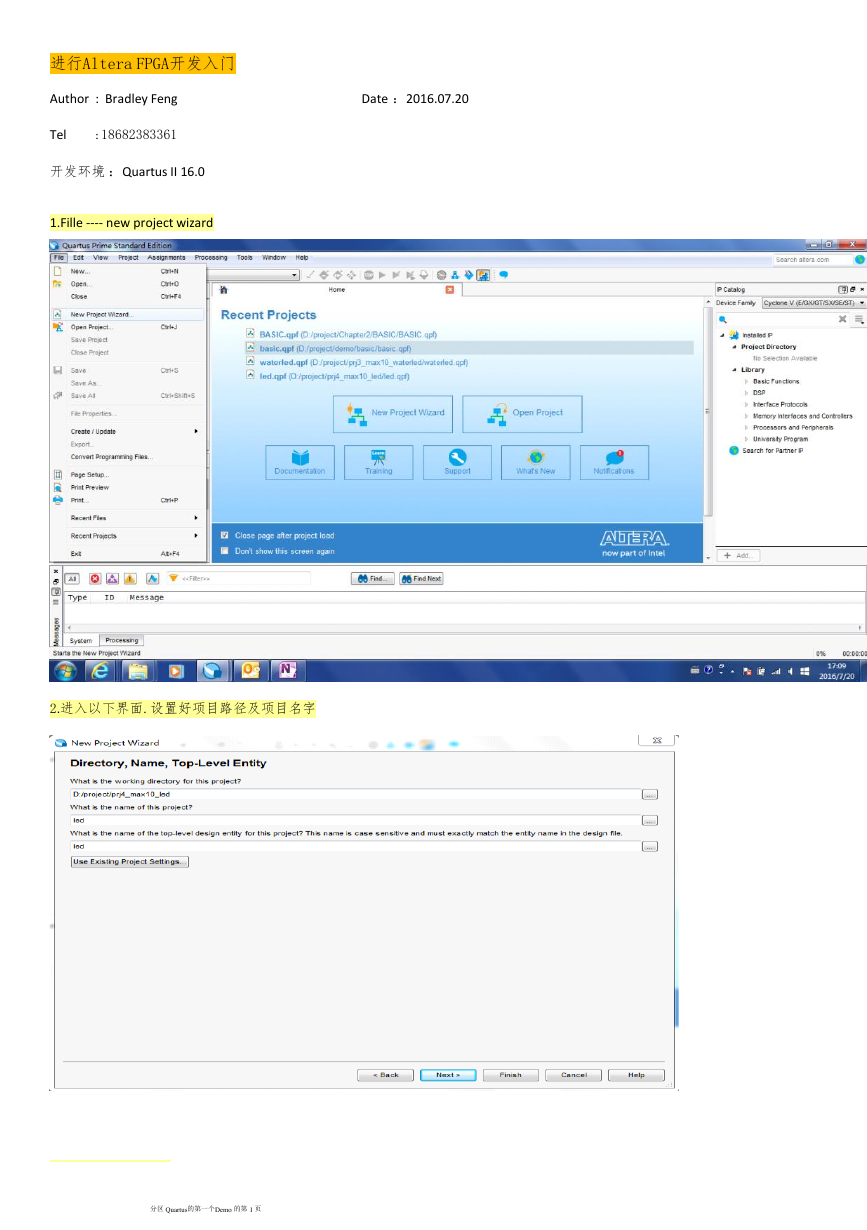

1.Fille ---- new project wizard

2.进入以下界面.设置好项目路径及项目名字

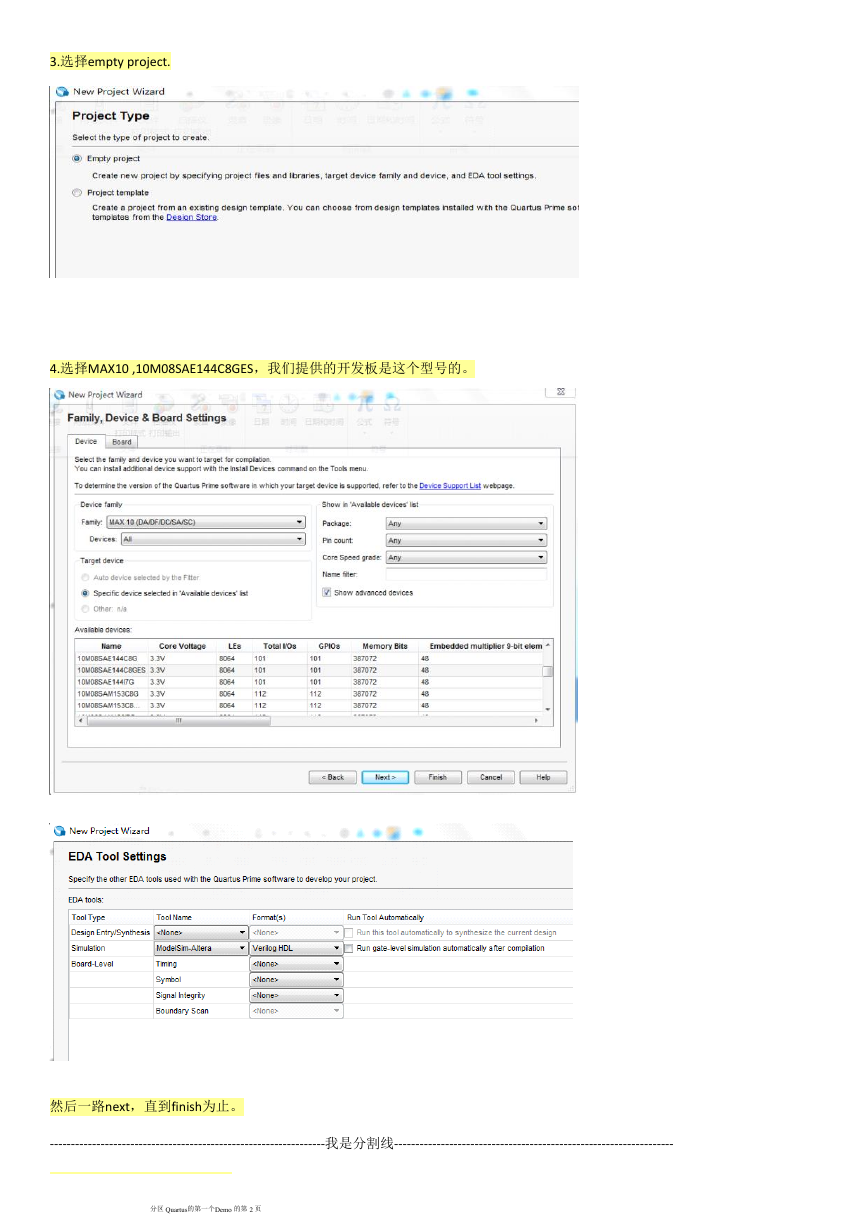

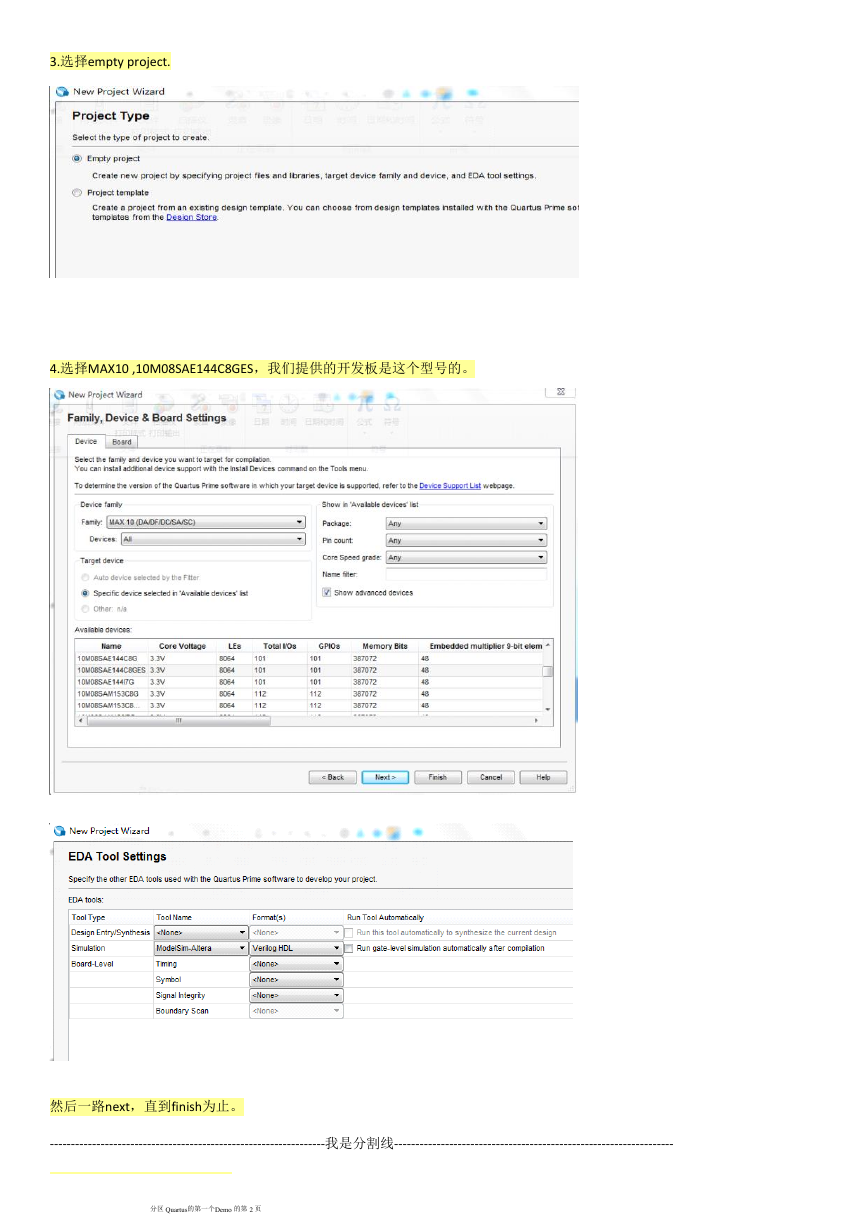

3.选择empty project.

分区 Quartus的第一个Demo 的第 1 页

�

3.选择empty project.

4.选择MAX10 ,10M08SAE144C8GES,我们提供的开发板是这个型号的。

然后一路next,直到finish为止。

-----------------------------------------------------------------我是分割线------------------------------------------------------------------

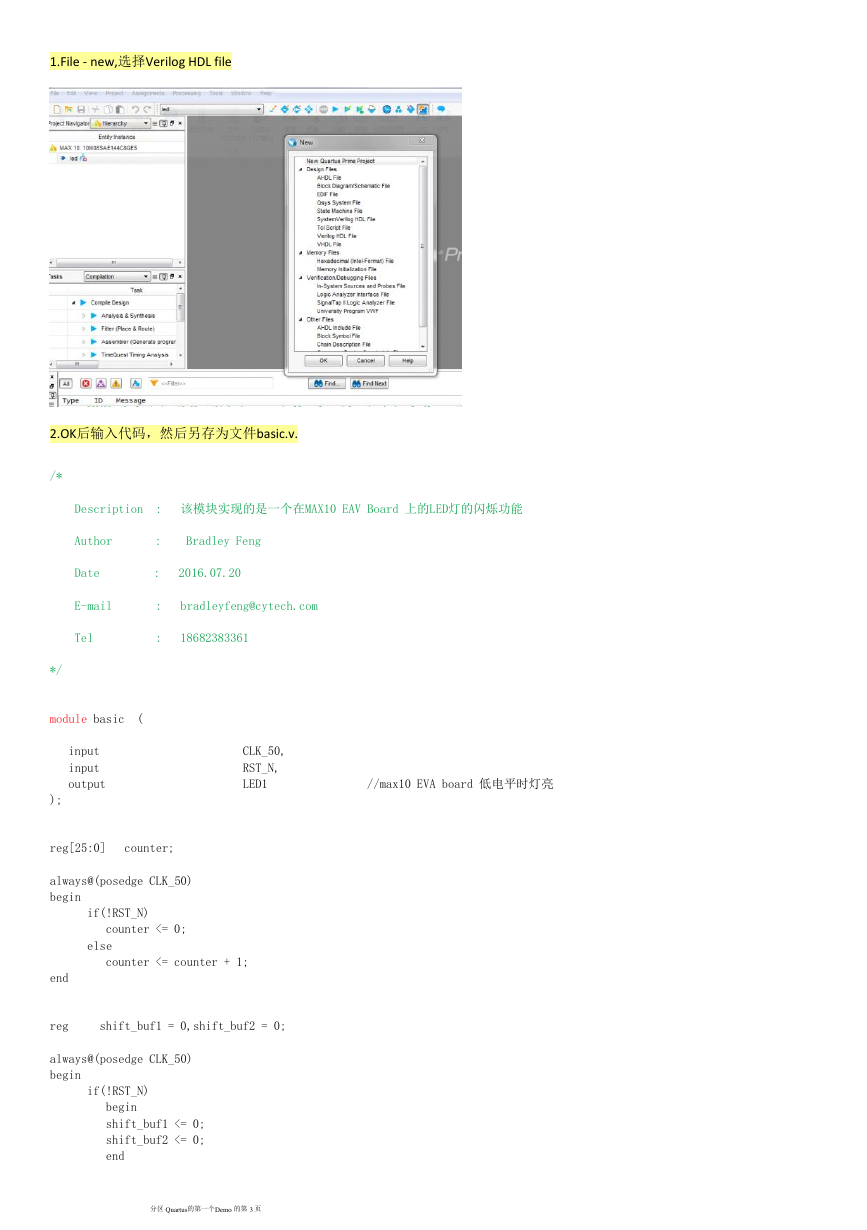

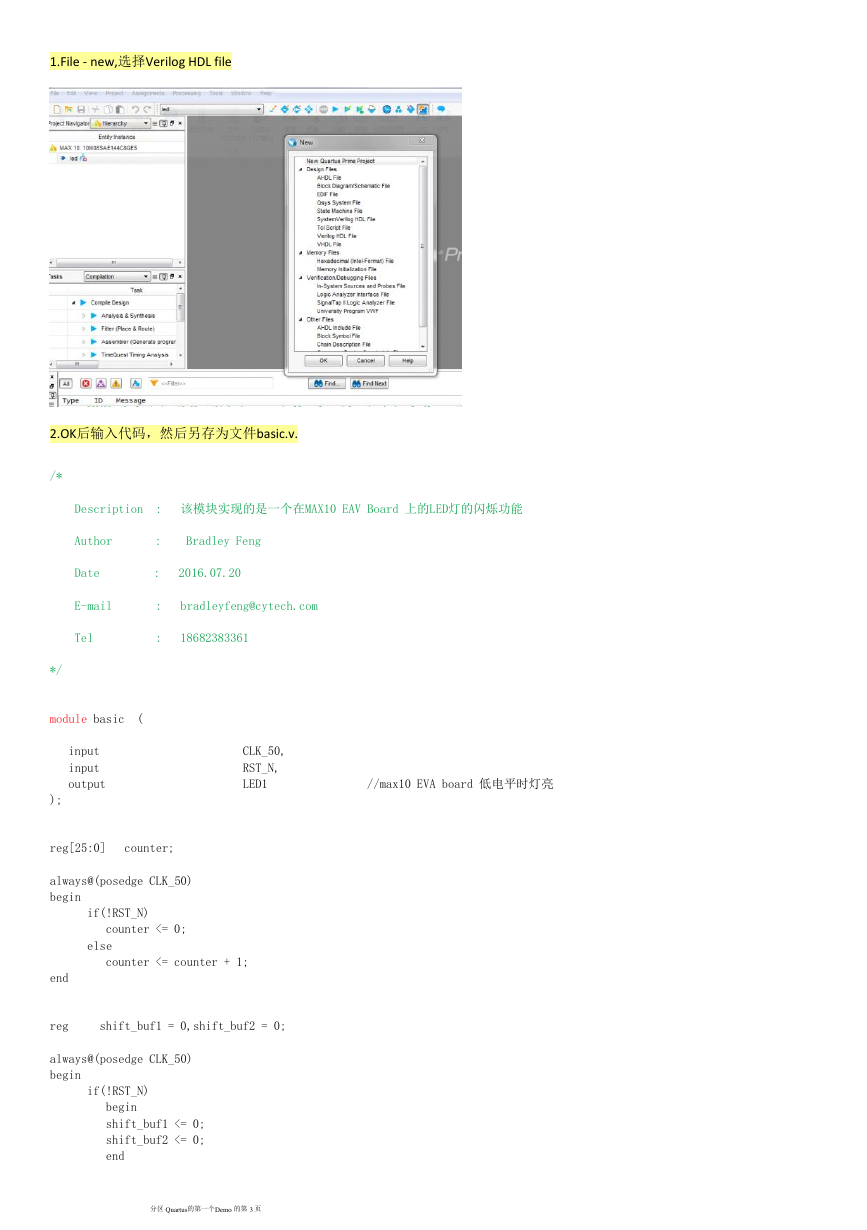

1.File - new,选择Verilog HDL file

分区 Quartus的第一个Demo 的第 2 页

�

1.File - new,选择Verilog HDL file

2.OK后输入代码,然后另存为文件basic.v.

/*

*/

Description : 该模块实现的是一个在MAX10 EAV Board 上的LED灯的闪烁功能

Author : Bradley Feng

Date : 2016.07.20

E-mail : bradleyfeng@cytech.com

Tel : 18682383361

module basic (

input

input

output

);

CLK_50,

RST_N,

LED1

//max10 EVA board 低电平时灯亮

reg[25:0]

counter;

always@(posedge CLK_50)

begin

if(!RST_N)

counter <= 0;

else

counter <= counter + 1;

end

reg

shift_buf1 = 0,shift_buf2 = 0;

always@(posedge CLK_50)

begin

if(!RST_N)

begin

shift_buf1 <= 0;

shift_buf2 <= 0;

end

else

分区 Quartus的第一个Demo 的第 3 页

�

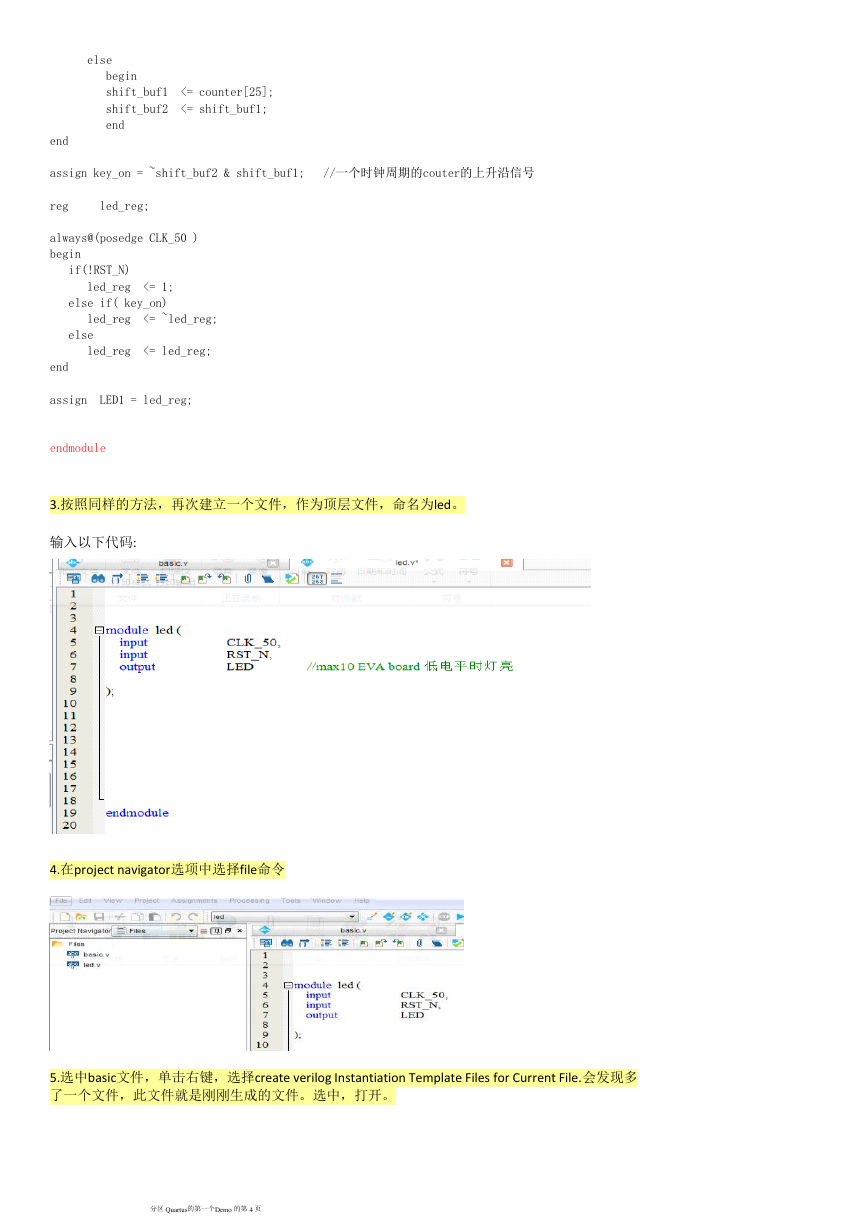

else

begin

shift_buf1 <= counter[25];

shift_buf2 <= shift_buf1;

end

end

assign key_on = ~shift_buf2 & shift_buf1; //一个时钟周期的couter的上升沿信号

reg

led_reg;

always@(posedge CLK_50 )

begin

if(!RST_N)

led_reg <= 1;

else if( key_on)

led_reg <= ~led_reg;

else

led_reg <= led_reg;

end

assign LED1 = led_reg;

endmodule

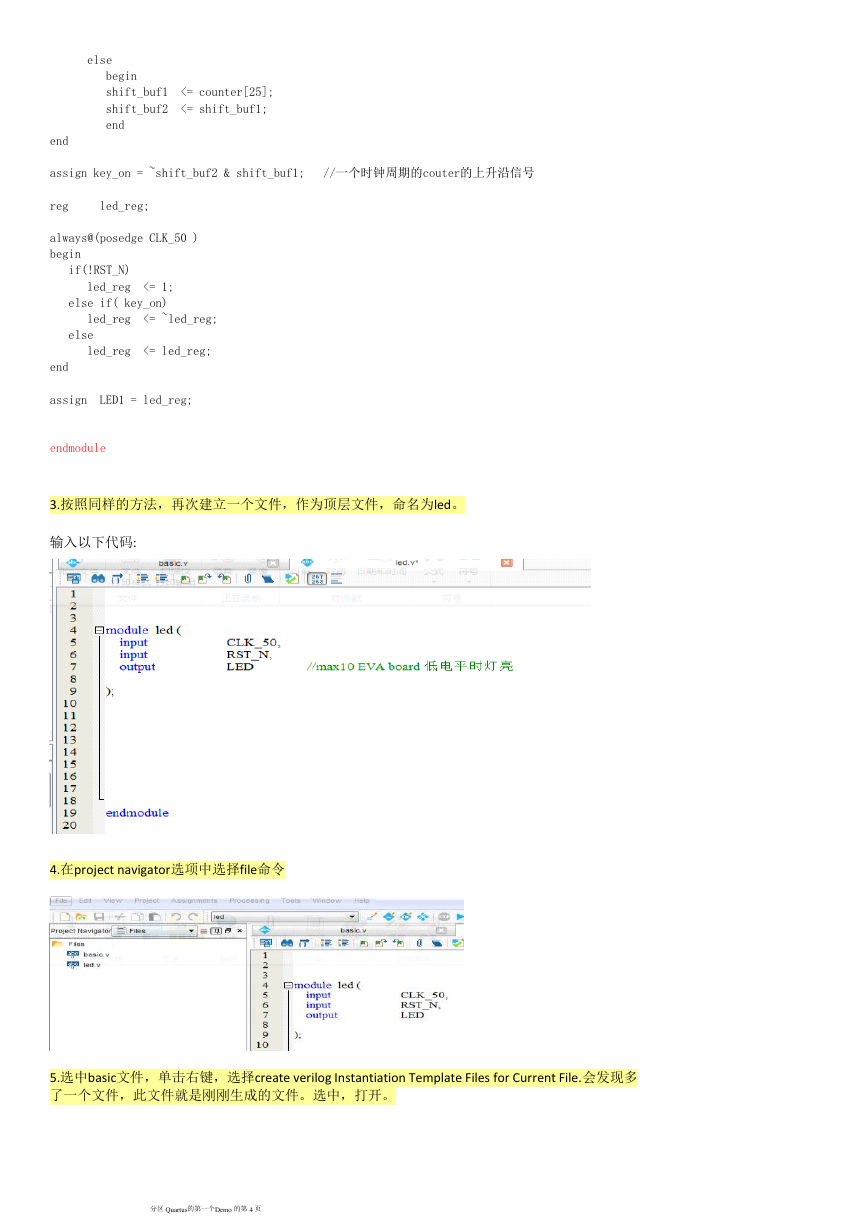

3.按照同样的方法,再次建立一个文件,作为顶层文件,命名为led。

输入以下代码:

4.在project navigator选项中选择file命令

5.选中basic文件,单击右键,选择create verilog Instantiation Template Files for Current File.会发现多

了一个文件,此文件就是刚刚生成的文件。选中,打开。

分区 Quartus的第一个Demo 的第 4 页

�

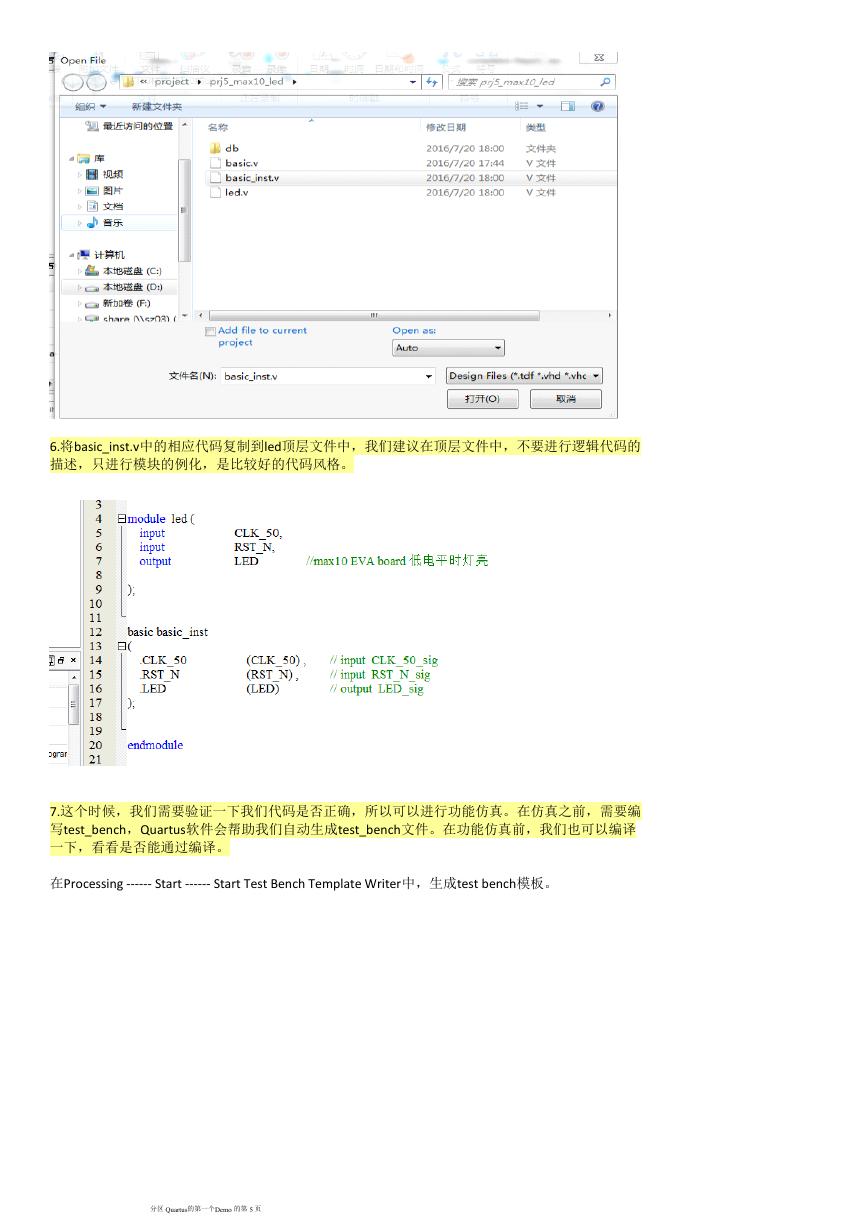

6.将basic_inst.v中的相应代码复制到led顶层文件中,我们建议在顶层文件中,不要进行逻辑代码的

描述,只进行模块的例化,是比较好的代码风格。

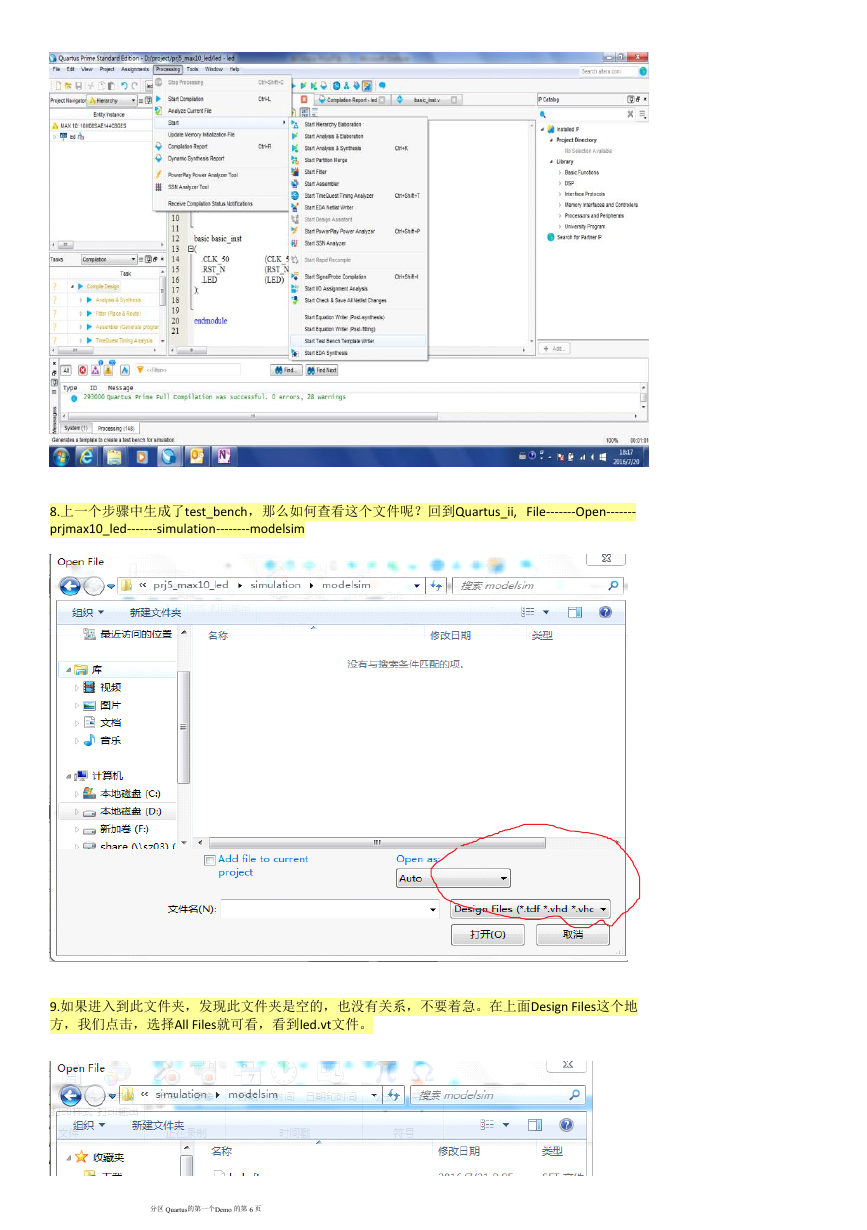

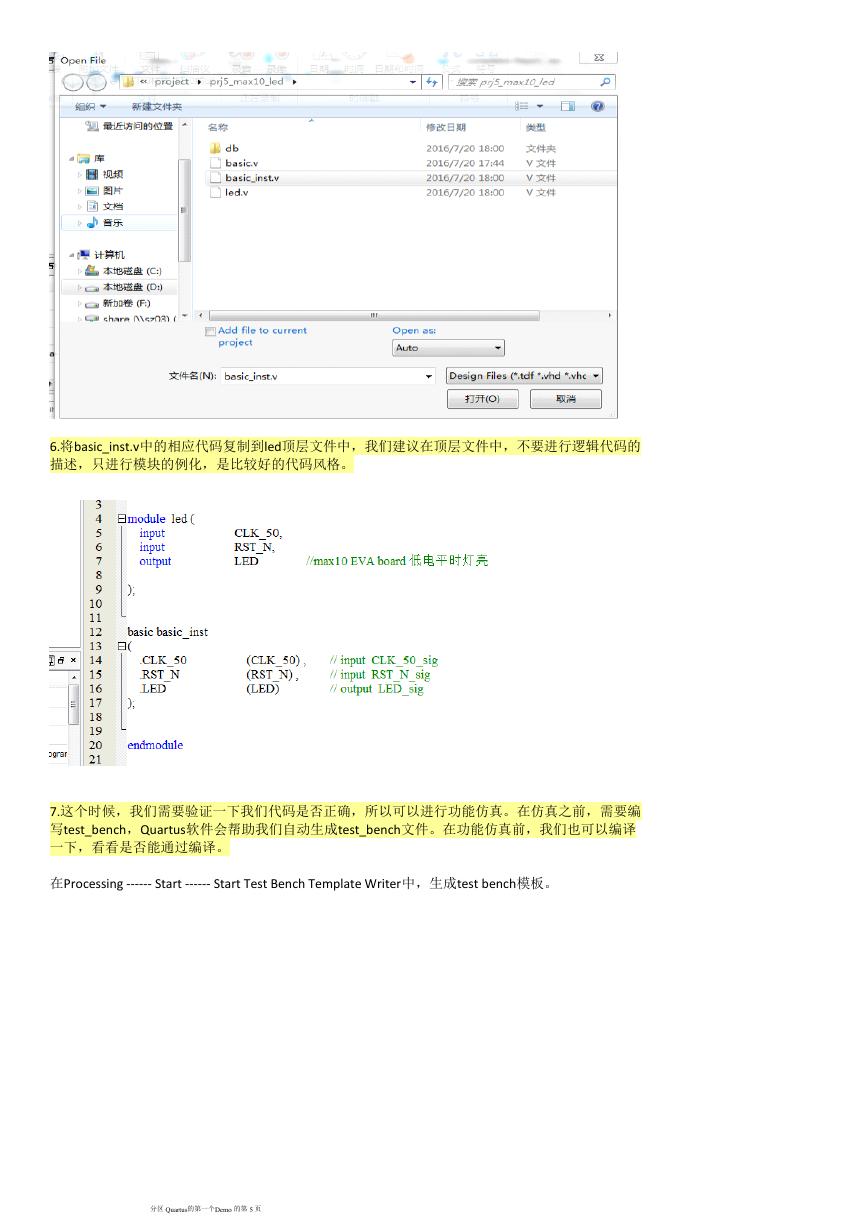

7.这个时候,我们需要验证一下我们代码是否正确,所以可以进行功能仿真。在仿真之前,需要编

写test_bench,Quartus软件会帮助我们自动生成test_bench文件。在功能仿真前,我们也可以编译

一下,看看是否能通过编译。

在Processing ------ Start ------ Start Test Bench Template Writer中,生成test bench模板。

分区 Quartus的第一个Demo 的第 5 页

�

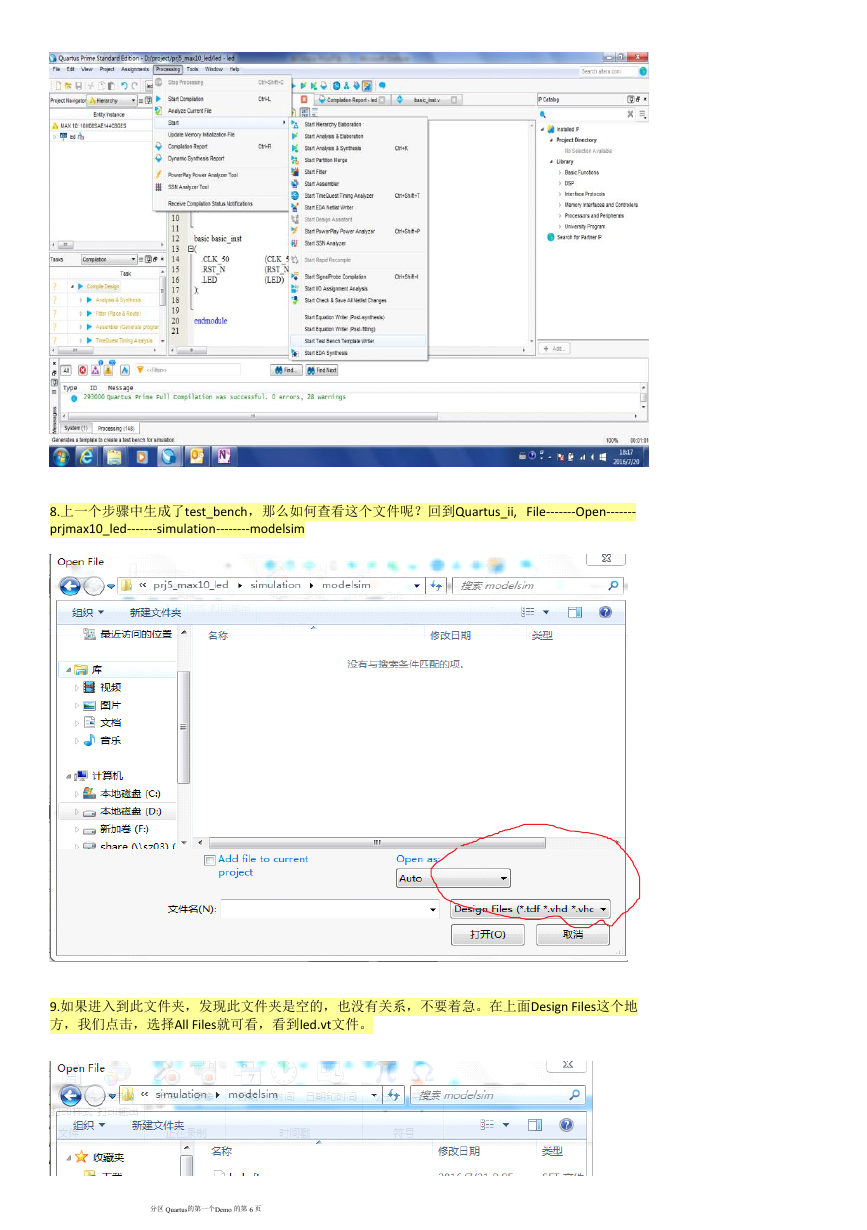

8.上一个步骤中生成了test_bench,那么如何查看这个文件呢?回到Quartus_ii, File-------Open-------

prjmax10_led-------simulation--------modelsim

9.如果进入到此文件夹,发现此文件夹是空的,也没有关系,不要着急。在上面Design Files这个地

方,我们点击,选择All Files就可看,看到led.vt文件。

分区 Quartus的第一个Demo 的第 6 页

�

10.打开led.vt,我们看一下代码结构,这段代码就是led.v (也就是顶层文件)的test_bench.

11.接下来我们要设置一下Quartus ii 软件,进行仿真的操作。在仿真操作开始前,我们要编写

test_bench,上面这个文件led.vt只是一个模板,具体我们期望的电路行为还是要通过写test_bench

来实现。

我们可以稍稍改进一下代码,如下,然后保存led.vt。需要注意花圈的这几个地方。

分区 Quartus的第一个Demo 的第 7 页

�

12.回到Quartus ii菜单栏,点击Assignment-------setting,会弹出这个框图。

13.在nativelink setting里选择compile test bench,然后按照下面的步骤就行操作。

一共有五个步骤

分区 Quartus的第一个Demo 的第 8 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc