武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

课程设计任务书

专业班级:

XX

工作单位: XX

学生姓名:

XX

XX

指导教师:

题 目: 密码锁设计

初始条件:

(1)软件 QuartusⅡ14.0

(2)FPGA 实验箱

(3)电脑设备

要求完成的主要任务:

1、熟悉和掌握使用 QuartusⅡ14.0 软件进行系统设计与仿真的方法。

2、设计一个电子密码锁:在锁开的状态下输入密码,设置的密码共 4 位,用拨码开关分别

代表数字 1,2,…,9,0,输入的密码用数码管显示,最后输入的密码显示在最右边的数码

管上,即每输入一位数,密码在数码管上的显示左移一位。可删除输入的数字,删除的是最

后输入的数字,每删除一位,密码在数码管上的显示右移一位,并在左边空出的位上灭掉。

用一位输出电平的状态代表锁的开闭状态。也可自行规定操作方式。为保证密码锁主人能打

开密码锁,设置一个万能密码,在主人忘记密码时使用

3、利用 QuartusⅡ软件对所设计的电路进行仿真分析。

时间安排:

1、2019 年 1 月 11 日分班集中,布置课程设计任务、选题;讲解课设具体实施计划与课程

设计报告格式的要求;课设答疑事项。

2、2019 年 1 月 12 日 至 2019 年 1 月 16 日完成资料查阅、设计、制作与调试;完成课程设

计报告撰写。

3、2019 年 1 月 17 日提交课程设计报告,进行课程设计验收和答辩。

指导教师签名:

系主任(或责任教师)签名:

年

年

月 日

月 日

�

武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

目 录

摘要.............................................................................................................................................I

Abstract......................................................................................................................................II

第 1 章 EDA 简介......................................................................................................................1

1.1 EDA 功能及特点............................................................................................................. 1

1.2 VHDA 语言及特点..........................................................................................................1

第 2 章 方案论证与对比..........................................................................................................3

2.1 方案一............................................................................................................................. 3

2.2 方案二............................................................................................................................. 4

2.3 方案对比及选择.............................................................................................................. 4

第 3 章 基于 FPGA 的电子密码锁设计..................................................................................5

3.1 输入模块.......................................................................................................................... 6

3.2 分频模块......................................................................................................................... 7

3.3 控制模块......................................................................................................................... 7

3.4 数码管输出显示模块................................................................................................... 10

3.5 各模块组合电路........................................................................................................... 10

第 4 章 结果分析....................................................................................................................11

第 5 章 小结体会....................................................................................................................12

参考文献..................................................................................................................................13

附录..........................................................................................................................................14

�

武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

摘 要

锁是保护人类生命财产安全的重要工具。随着社会发展技术进步,人类发明了保密

性能和防盗功能更强的电子密码锁,以取代传统的机械锁。

电子密码锁的种类很多[2],有简易的电路产品,也有基于芯片的性价比较高的产品。

应用较广的电子密码锁是以芯片为核心,通过编程来实现的。其控制核心一般通过数字

电路,单片机或 FPGA 实现。FPGA 作为专用集成电路领域中的一种半定制电路,既解

决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。相比单片机开发

需要同时设计硬件电路与编写程序,FPGA 开发以硬件描述语言来实现,可以更高效地

实现电子密码锁的功能。

本次电子密码锁设计通过使用 VHDL 硬件描述语言在 Quartus Ⅱ软件环境下设计

编译并仿真,下载至 FPGA 以实现需要的功能。

关键词:电子密码锁;FPGA;VHDL

I

�

武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

Abstract

Lock is an important tool to protect human life and property. With the development

of society and technological progress, people have invented electronic password locks with

stronger security performance and anti-theft function to replace traditional mechanical locks.

There are many kinds of electronic password locks, including simple circuit products and

high cost products based on chips. The widely used electronic password lock is realized by

programming with the chip as the core. Its control core is usually realized by digital circuit,

single chip computer or FPGA. As a semi-customized circuit in the field of ASIC, FPGA not

only solves the shortcomings of customized circuit, but also overcomes the shortcomings of

limited number of original programmable gate circuits[4]. Compared with the development of

single chip microprocessor, hardware circuit and program need to be designed at the same

time. The development of FPGA is realized by hardware description language, which can

realize the function of electronic password lock more efficiently.

This design of electronic password lock uses Verilog HDL hardware description

language to design, compile and simulate in Max+plus II software environment, and

download to the FPGA to achieve the required functions.

Keywords: electronic organ; the quartus; the EDA; VHDL language

II

�

武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

第 1 章 EDA 简介

1.1 EDA 功能及特点

EDA 是电子设计自动化(Electronics Design Automation)的缩写,在 20 世纪 60 年

代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)

和计算机辅助工程(CAE)的概念发展而来的。

EDA 技术就是以计算机为工具[5],设计者在 EDA 软件平台上,用硬件描述语言

VerilogHDL 完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、

优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等

工作。EDA 技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的

劳动强度。

1.2 VHDL 语言及特点

VHDL 的英文全名是 VHSIC Hardware Description Language(VHSIC 硬件描述语言)。

VHSIC 是 Very High Speed Integrated Circuit 的缩写[3],是 20 世纪 80 年代在美国国防部

的资助下始创的,并最终导致了 VHDL 语言的出现。1987 年底,VHDL 被 IEEE 和美

国国防部确认为标准硬件描述语言。VHDL 主要用于描述数字系统的结构,行为,功能

和接口。除了含有许多具有硬件特征的语句外,VHDL 的语言形式和描述风格与句法是

十分类似于一般的计算机高级语言。VHDL 的程序结构特点是将一项工程设计,或称设

计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端

口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设

计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实

体。这种将设计实体分成内外部分的概念是 VHDL 系统设计的基本点。

VHDL 语言能够成为标准化的硬件描述语言并获得广泛应用,它自身必然具有很多

其他硬件描述语言所不具备的优点。归纳起来,VHDL 语言主要具有以下优点[1]:

(1) VHDL 语言功能强大,设计方式多样

VHDL 语言具有强大的语言结构,只需采用简单明确的 VHDL 语言程序就可以描

述十分复杂的硬件电路。同时,它还具有多层次的电路设计描述功能。此外,VHDL 语

1

�

武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

言能够同时支持同步电路、异步电路和随机电路的设计实现,这是其他硬件描述语言所

不能比拟的。VHDL 语言设计方法灵活多样,既支持自顶向下的设计方式,也支持自底

向上的设计方法; 既支持模块化设计方法,也支持层次化设计方法。

(2) VHDL 语言具有强大的硬件描述能力

VHDL 语言具有多层次的电路设计描述功能,既可描述系统级电路,也可以描述门

级电路;描述方式既可以采用行为描述、寄存器传输描述或者结构描述,也可以采用三

者的混合描述方式。同时,VHDL 语言也支持惯性延迟和传输延迟,这样可以准确地建

立硬件电路的模型。VHDL 语言的强大描述能力还体现在它具有丰富的数据类型。

VHDL 语言既支持标准定义的数据类型,也支持用户定义的数据类型,这样便会给硬件

描述带来较大的自由度。

(3) VHDL 语言具有很强的移植能力

VHDL 语言很强的移植能力主要体现在: 对于同一个硬件电路的 VHDL 语言描

述,它可以从一个模拟器移植到另一个模拟器上、从一个综合器移植到另一个综合器上

或者从一个工作平台移植到另一个工作平台上去执行。

(4) VHDL 语言的设计描述与器件无关

采用 VHDL 语言描述硬件电路时,设计人员并不需要首先考虑选择进行设计的器

件。这样做的好处是可以使设计人员集中精力进行电路设计的优化,而不需要考虑其他

的问题。当硬件电路的设计描述完成以后,VHDL 语言允许采用多种不同的器件结构来

实现。

(5) VHDL 语言程序易于共享和复用

VHDL 语言采用基于库 ( library) 的设计方法。在设计过程中,设计人员可以建立

各种可再次利用的模块,一个大规模的硬件电路的设计不可能从门级电路开始一步步地

进行设计,而是一些模块的累加。这些模块可以预先设计或者使用以前设计中的存档模

块,将这些模块存放在库中,就可以在以后的设计中进行复用。

由于 VHDL 语言是一种描述、模拟、综合、优化和布线的标准硬件描述语言,因

此它可以使设计成果在设计人员之间方便地进行交流和共享,从而减小硬件电路设计的

工作量,缩短开发周期。

2

�

武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

第 2 章 方案论证与对比

2.1 方案一

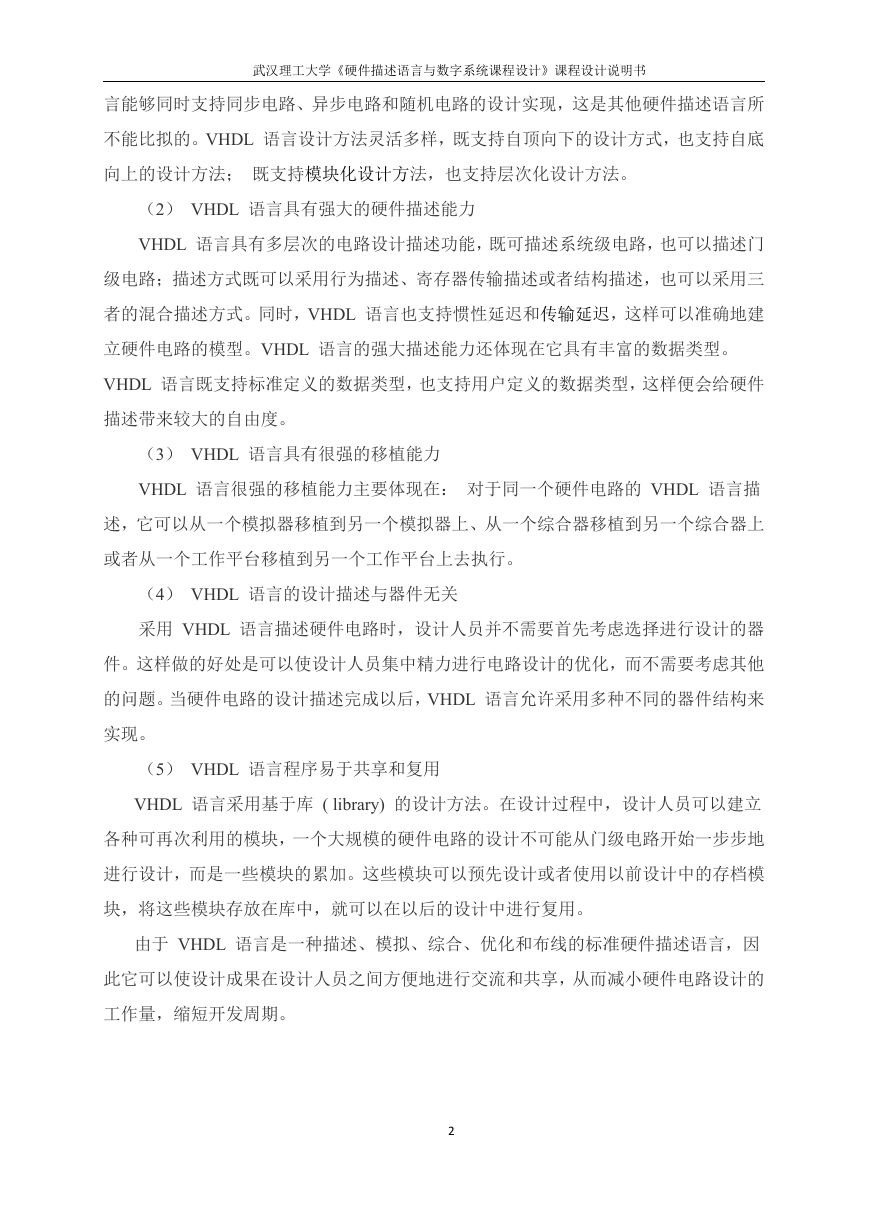

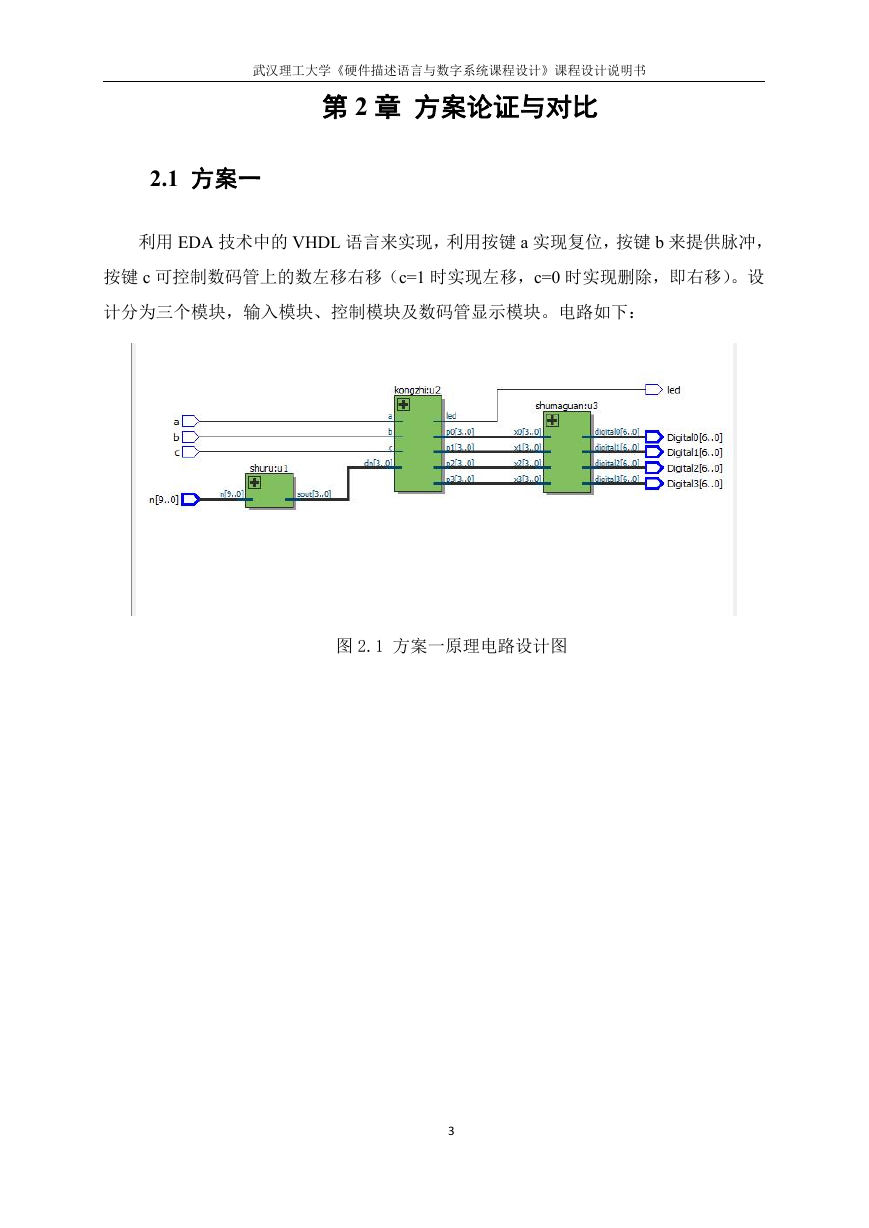

利用 EDA 技术中的 VHDL 语言来实现,利用按键 a 实现复位,按键 b 来提供脉冲,

按键 c 可控制数码管上的数左移右移(c=1 时实现左移,c=0 时实现删除,即右移)。设

计分为三个模块,输入模块、控制模块及数码管显示模块。电路如下:

图 2.1 方案一原理电路设计图

3

�

武汉理工大学《硬件描述语言与数字系统课程设计》课程设计说明书

2.2 方案二

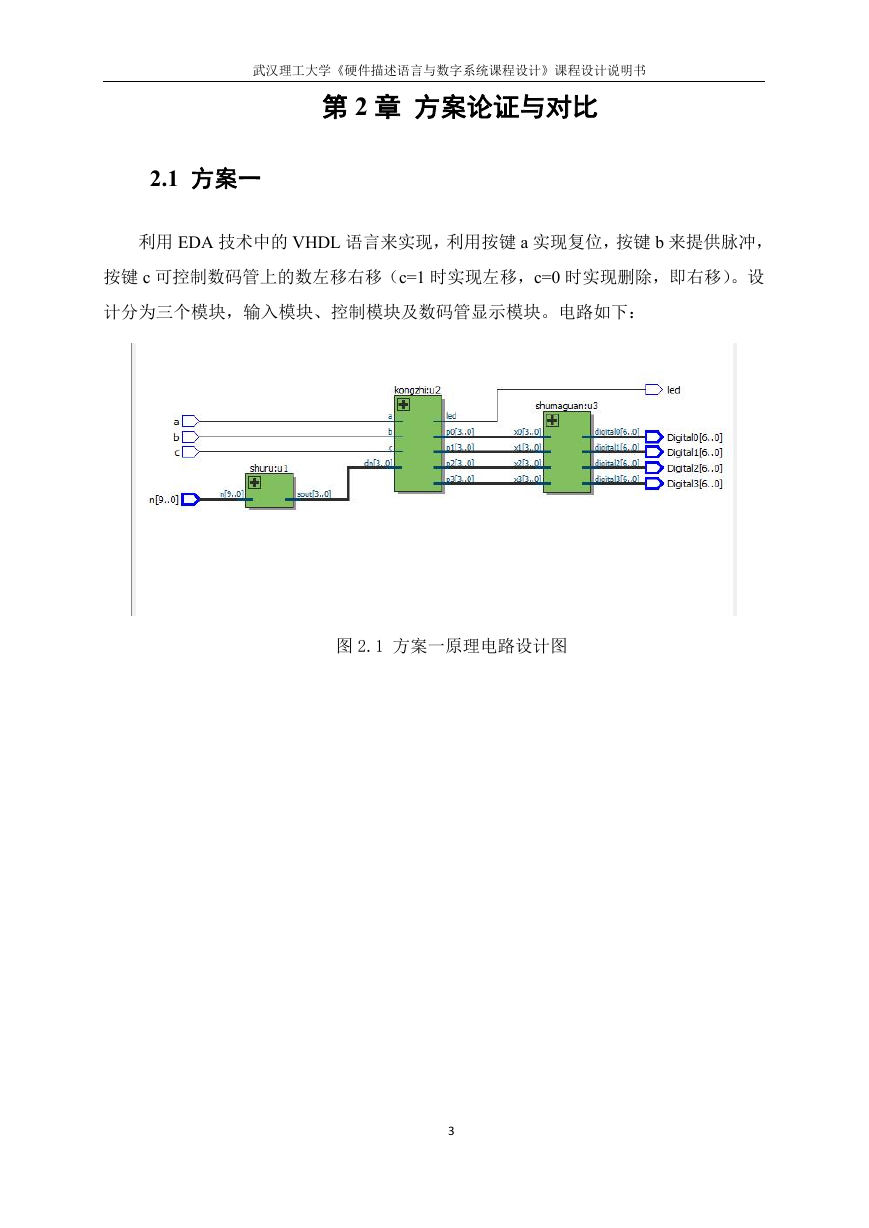

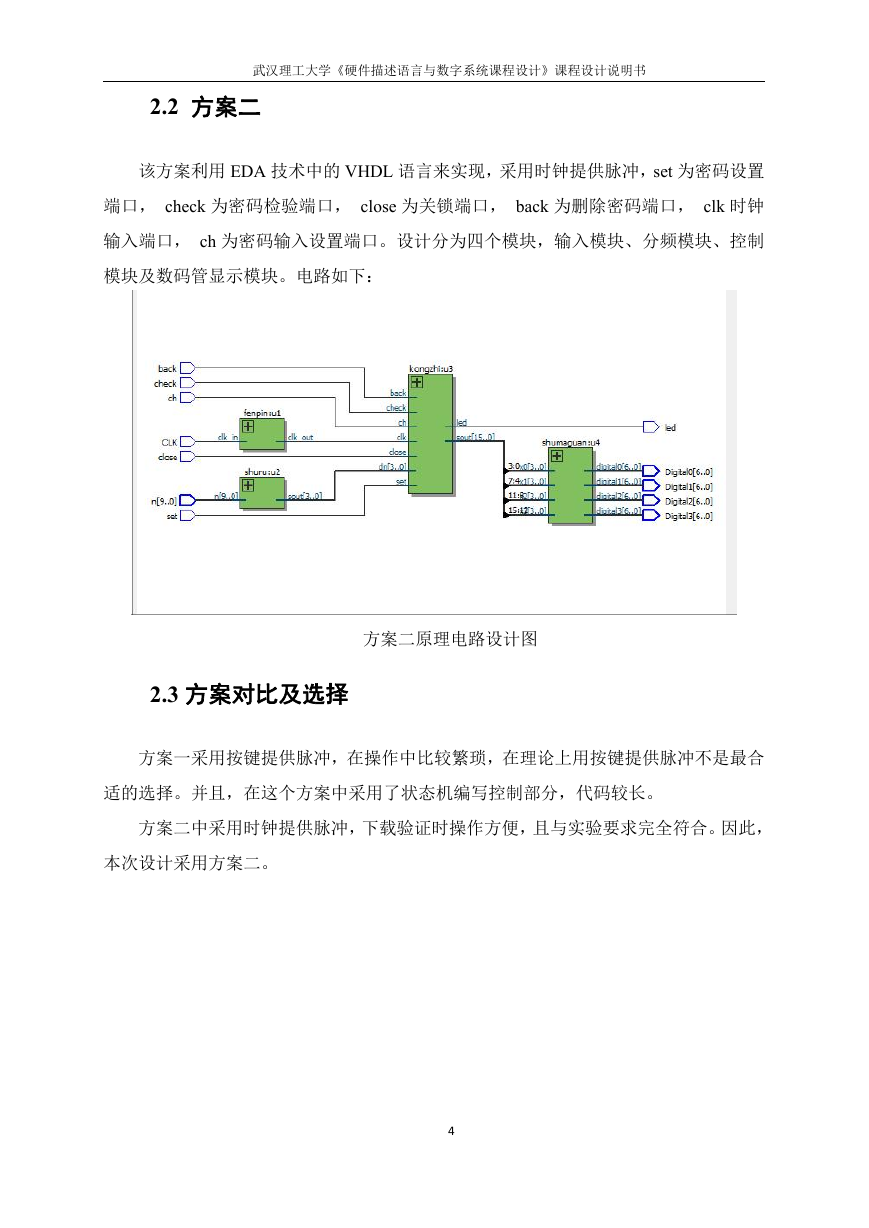

该方案利用 EDA 技术中的 VHDL 语言来实现,采用时钟提供脉冲,set 为密码设置

端口, check 为密码检验端口, close 为关锁端口, back 为删除密码端口, clk 时钟

输入端口, ch 为密码输入设置端口。设计分为四个模块,输入模块、分频模块、控制

模块及数码管显示模块。电路如下:

方案二原理电路设计图

2.3 方案对比及选择

方案一采用按键提供脉冲,在操作中比较繁琐,在理论上用按键提供脉冲不是最合

适的选择。并且,在这个方案中采用了状态机编写控制部分,代码较长。

方案二中采用时钟提供脉冲,下载验证时操作方便,且与实验要求完全符合。因此,

本次设计采用方案二。

4

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc