第 53 章 集成芯片间的声音总线(I2S)

53.1 介绍

注意

该模块实例的具体实现细节见芯片配置章节。

这个部分讨论体系结构,编程模型,操作模式和 I2S 模块的初始化。

I2S 是全双工的串口,它可以使芯片和各种串行设备通信,这些串行设备有:

•标准解码器

•数字信号处理器(DSPs)

•微处理器

•外设

•实现了 inter-IC sound 总线(I2S)和 Intel® AC97 标准的音频解码器

I2S 模块是典型的以一个周期性的方式转移样例。I2S 由拥有独立的时钟发生器和帧同步的

独立发射器和接收器部分组成。

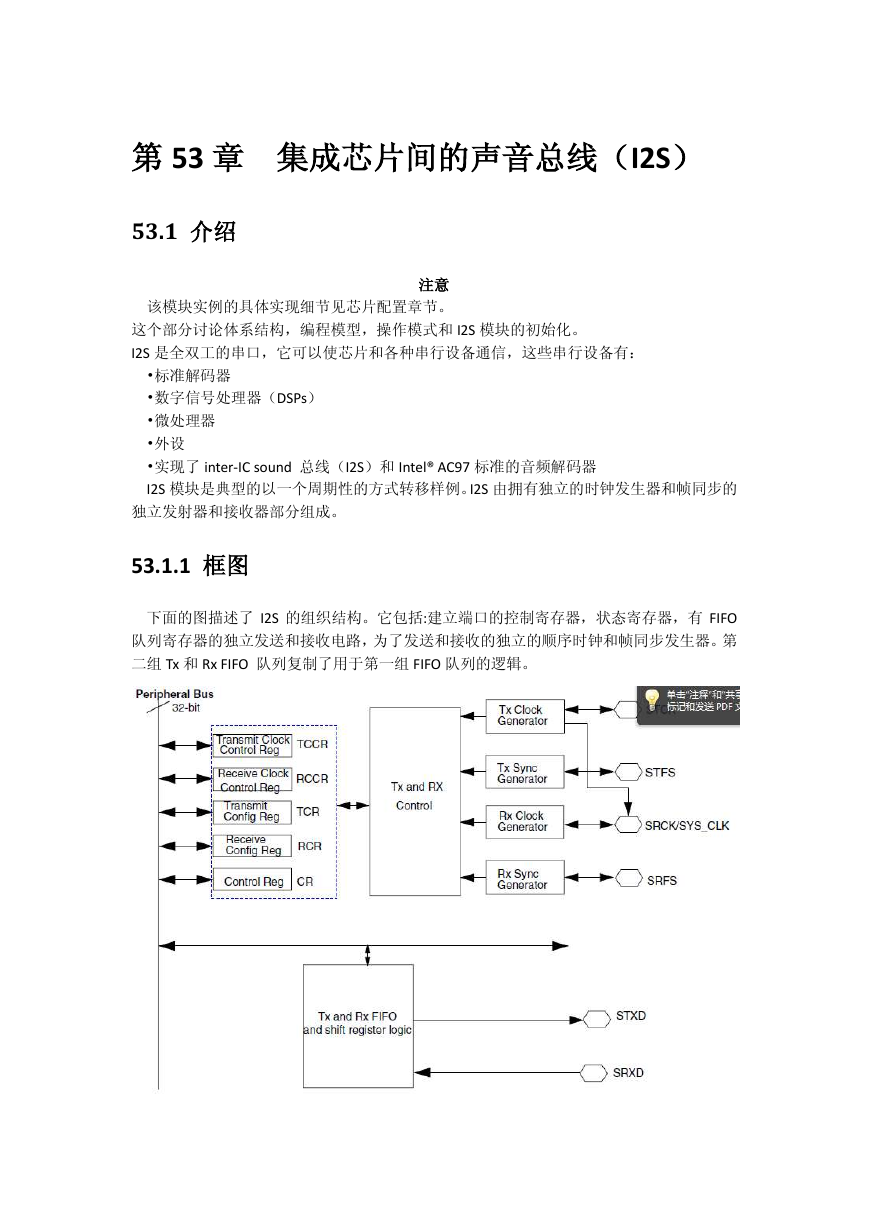

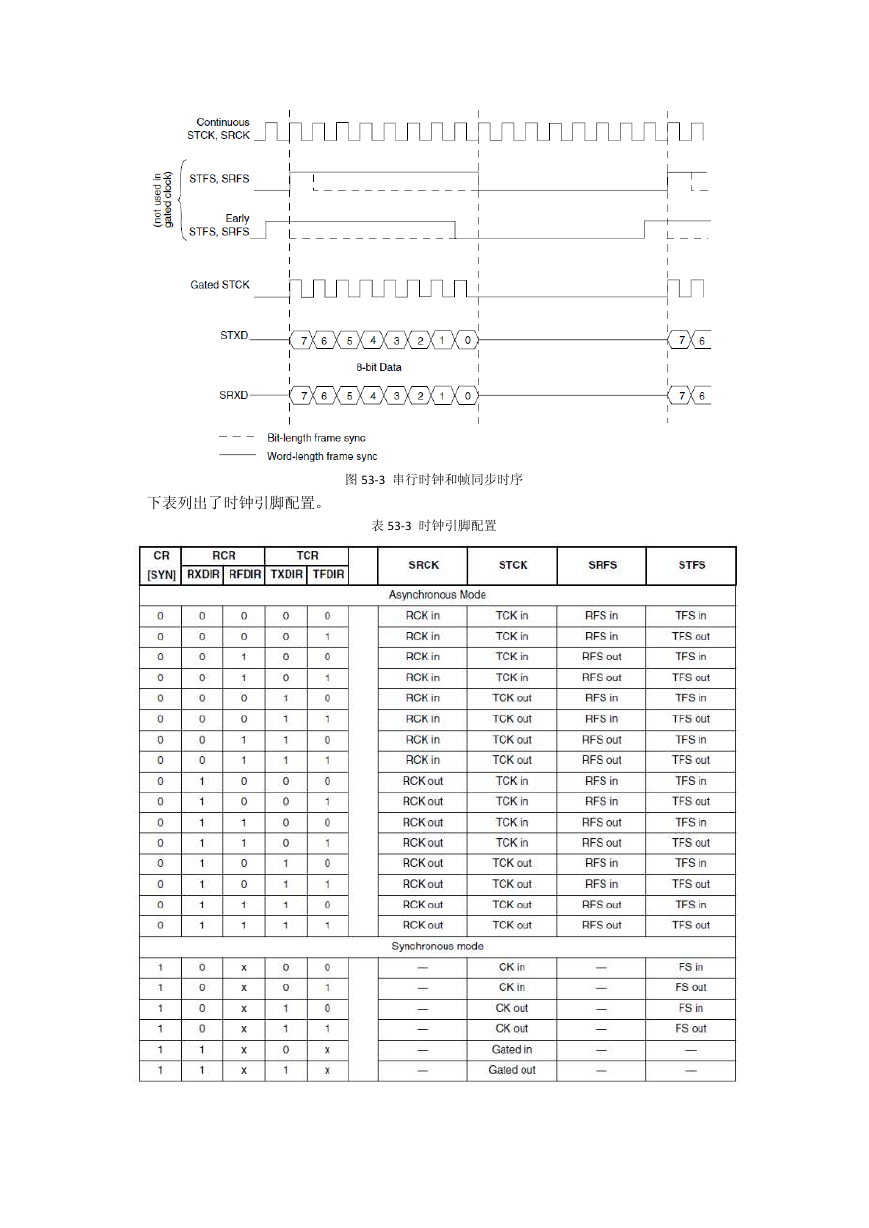

53.1.1 框图

下面的图描述了 I2S 的组织结构。它包括:建立端口的控制寄存器,状态寄存器,有 FIFO

队列寄存器的独立发送和接收电路,为了发送和接收的独立的顺序时钟和帧同步发生器。第

二组 Tx 和 Rx FIFO 队列复制了用于第一组 FIFO 队列的逻辑。

�

图 53-1 面向用户的 I2S 框图

53.1.2 特性

I2S 包含以下特性:

•有独立或共享的内/外部时钟和帧同步的独立(异步)或共享(同步)的发送和接收部

分,在主或从模式下工作。

•使用帧同步的正常操作模式

•允许多个设备共享端口多大三十二个时段的网络操作模式

•无需同步帧的门控时钟操作模式

•两组 FIFO 发送和接收队列。四组 FIFO 队列中每组都是 15x32 位。两组 Tx/Rx FIFO 队

列可以用于网络模式从而为发送和接收提供两个独立的通道

•可编程数据接口模式,例如 I2S, lsb- and msb-aligned

•可编程单词长度(8, 10, 12, 16, 18, 20, 22 or 24 位)

•用于帧同步和时钟发生器的编程选项

•可编程的 I2S 模式(主,从,正常)

•在 I2S 的主模式下过采样时钟作为 SRCK 的输出

•AC97 支持

•用于发送和接收部分的完全独立的时钟和帧同步选择。在 AC97 标准中时钟来自外部

源,而帧同步是内部产生的

•外部网络时钟输入用于 I2S 的主模式。当在同步模式下,主模式下的采样频率的过采

样时钟可作为 SRCK 的输出

•可编程的内部时钟分频器

•为减少 CPU 开销的发送和接收的时隙屏蔽寄存器

•I2S 的断电特性

53.1.3 操作模式

I2S 含有以下基本操作模式:

•正常模式

•异步协议

•同步协议

•网络模式

•异步协议

•同步协议

•门控时钟模式

•只有同步协议

•I2S 模式

•AC97 模式

•AC97 静态模式(ACNT[FV] = 0)

•AC97 动态模式(ACNT[FV] = 1)

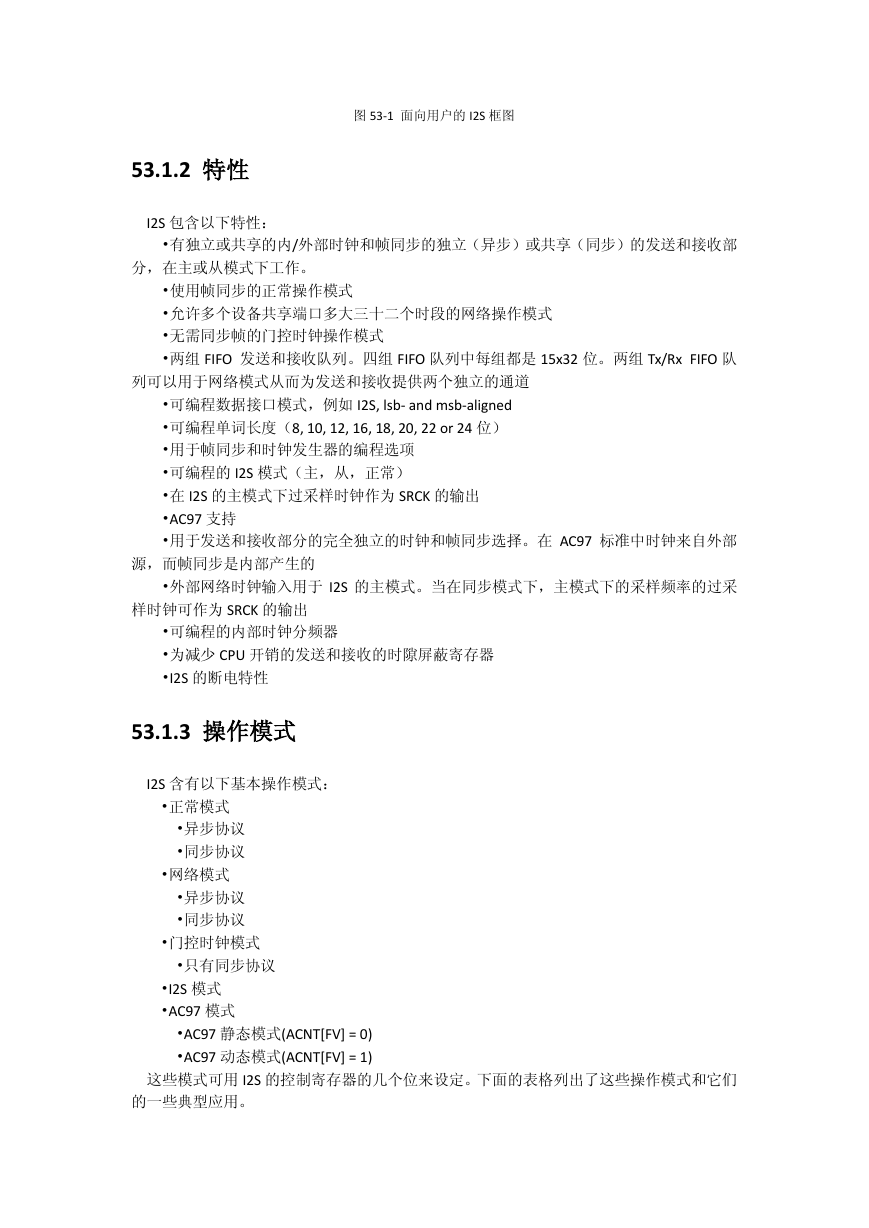

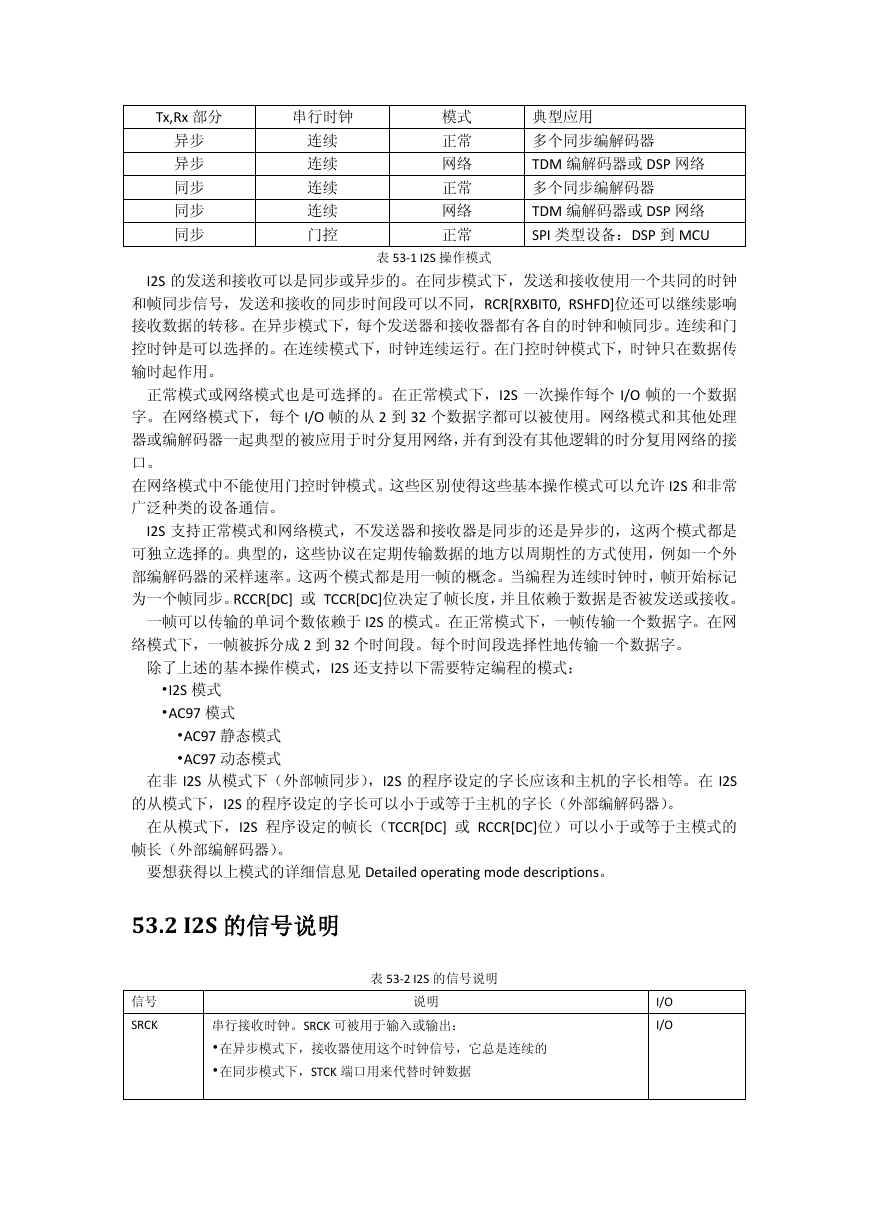

这些模式可用 I2S 的控制寄存器的几个位来设定。下面的表格列出了这些操作模式和它们

的一些典型应用。

�

Tx,Rx 部分

串行时钟

异步

异步

同步

同步

同步

连续

连续

连续

连续

门控

模式

正常

网络

正常

网络

正常

典型应用

多个同步编解码器

TDM 编解码器或 DSP 网络

多个同步编解码器

TDM 编解码器或 DSP 网络

SPI 类型设备:DSP 到 MCU

表 53-1 I2S 操作模式

I2S 的发送和接收可以是同步或异步的。在同步模式下,发送和接收使用一个共同的时钟

和帧同步信号,发送和接收的同步时间段可以不同,RCR[RXBIT0, RSHFD]位还可以继续影响

接收数据的转移。在异步模式下,每个发送器和接收器都有各自的时钟和帧同步。连续和门

控时钟是可以选择的。在连续模式下,时钟连续运行。在门控时钟模式下,时钟只在数据传

输时起作用。

正常模式或网络模式也是可选择的。在正常模式下,I2S 一次操作每个 I/O 帧的一个数据

字。在网络模式下,每个 I/O 帧的从 2 到 32 个数据字都可以被使用。网络模式和其他处理

器或编解码器一起典型的被应用于时分复用网络,并有到没有其他逻辑的时分复用网络的接

口。

在网络模式中不能使用门控时钟模式。这些区别使得这些基本操作模式可以允许 I2S 和非常

广泛种类的设备通信。

I2S 支持正常模式和网络模式,不发送器和接收器是同步的还是异步的,这两个模式都是

可独立选择的。典型的,这些协议在定期传输数据的地方以周期性的方式使用,例如一个外

部编解码器的采样速率。这两个模式都是用一帧的概念。当编程为连续时钟时,帧开始标记

为一个帧同步。RCCR[DC] 或 TCCR[DC]位决定了帧长度,并且依赖于数据是否被发送或接收。

一帧可以传输的单词个数依赖于 I2S 的模式。在正常模式下,一帧传输一个数据字。在网

络模式下,一帧被拆分成 2 到 32 个时间段。每个时间段选择性地传输一个数据字。

除了上述的基本操作模式,I2S 还支持以下需要特定编程的模式:

•I2S 模式

•AC97 模式

•AC97 静态模式

•AC97 动态模式

在非 I2S 从模式下(外部帧同步),I2S 的程序设定的字长应该和主机的字长相等。在 I2S

的从模式下,I2S 的程序设定的字长可以小于或等于主机的字长(外部编解码器)。

在从模式下,I2S 程序设定的帧长(TCCR[DC] 或 RCCR[DC]位)可以小于或等于主模式的

帧长(外部编解码器)。

要想获得以上模式的详细信息见 Detailed operating mode descriptions。

53.2 I2S 的信号说明

表 53-2 I2S 的信号说明

说明

串行接收时钟。SRCK 可被用于输入或输出:

•在异步模式下,接收器使用这个时钟信号,它总是连续的

•在同步模式下,STCK 端口用来代替时钟数据

I/O

I/O

信号

SRCK

�

信号

SRFS

说明

串行接收帧同步。SRFS 端口可用于输入或输出。接收器使用帧同步来同步数

据传输。一个帧同步信号的长度可以是一位或一个字,在数据传输之前或正

在传输时帧同步信号可以传输一位。如果 SRFS 被配置为输入,外部设备应

该在 STCK 或 SRCK 的上升沿驱动 SRFS。

I/O

I/O

SRXD

串行接收数据。SRXD 端口是输入端口且把串行数据放到接收数据移位寄存

I

器

STCK

串行发送时钟。STCK 端口可被用于输入或输出。该时钟信号被发送器使用

I/O

且可以是连续的或是门控的。在门控时钟模式期间,只有在数据传输期间

SCTK 上的数据才是有效的。否则,它被拉到无效状态。在同步模式下,这

个端口被发送和接受单元使用。

STFS

串行发送帧同步。STFS 端口可被用于输入或输出。发送器使用帧同步来同步

I/O

数据传输。一个帧同步信号的长度可以是一位或一个字,在数据传输之前或

正在传输时帧同步信号可以传输一位。在同步模式下,这个端口被发送和接

受单元使用。在门控时钟模式下,不使用帧同步信号。当 STFS 被配置为输

入时,如果 TSCKP 是上升沿触发,外部设备应该在 STCK 的上升沿期间驱动

STFS,如果 TSCKP 是下降沿触发,外部设备应该在 STCK 的下降沿期间驱动

STFS。

STXD

串行发送数据。STXD 端口是输出端口且从串行发送移位寄存器发送数据。

O

当数据发送后,STXD 端口是输出端口。当一个字的最后一位被发送后,在

数据字发送和位时钟的下降沿之间 STXD 无效。

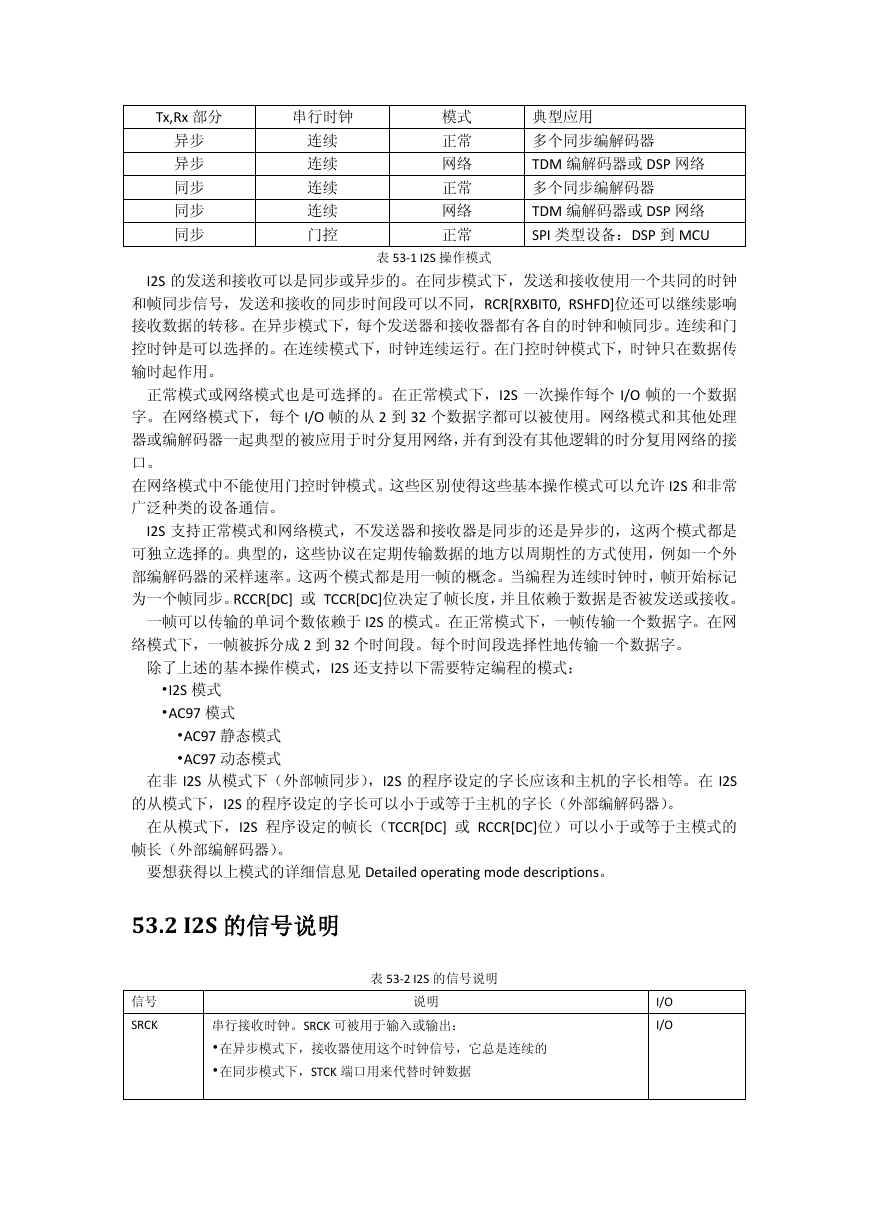

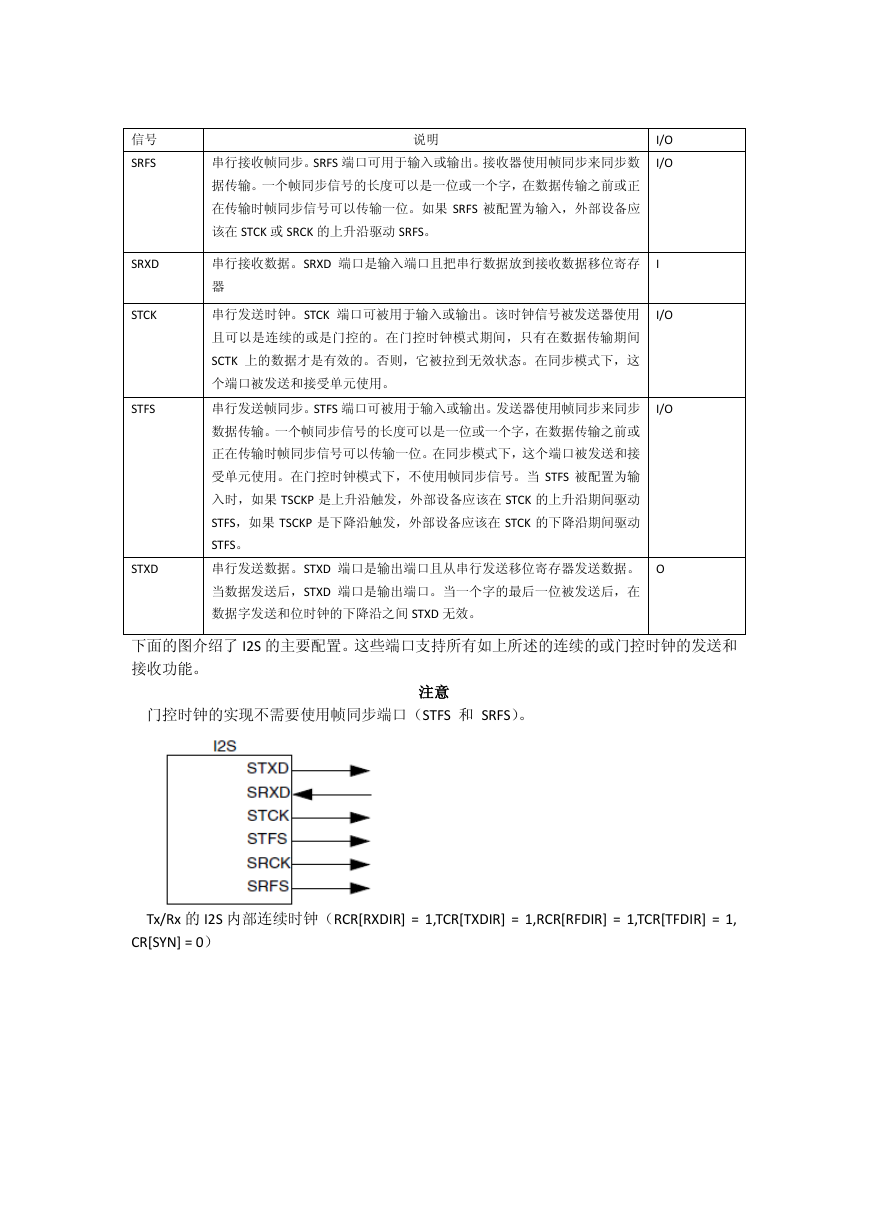

下面的图介绍了 I2S 的主要配置。这些端口支持所有如上所述的连续的或门控时钟的发送和

接收功能。

门控时钟的实现不需要使用帧同步端口(STFS 和 SRFS)。

注意

Tx/Rx 的 I2S 内部连续时钟(RCR[RXDIR] = 1,TCR[TXDIR] = 1,RCR[RFDIR] = 1,TCR[TFDIR] = 1,

CR[SYN] = 0)

�

Tx/Rx 的 I2S 外部连续时钟(RCR[RXDIR] = 0,TCR[TXDIR] = 0,RCR[RFDIR] = 0,TCR[TFDIR] = 0,

CR[SYN] = 0)

Rx 的 I2S 内部连续时钟(RCR[RXDIR] = 1, TCR[TXDIR] = 0,RCR[RFDIR] = 1,TCR[TFDIR] = 0,

CR[SYN] = 0)

Tx 的 I2S 外部连续时钟

Tx 的 I2S 内部连续时钟(RCR[RXDIR] = 0, TCR[TXDIR] = 1, RCR[RFDIR] = 0, TCR[TFDIR] = 1,

CR[SYN] = 0)

Rx 的 I2S 外部连续时钟

图 53-2 异步(SYN = 0)I2S 配置—连续时钟

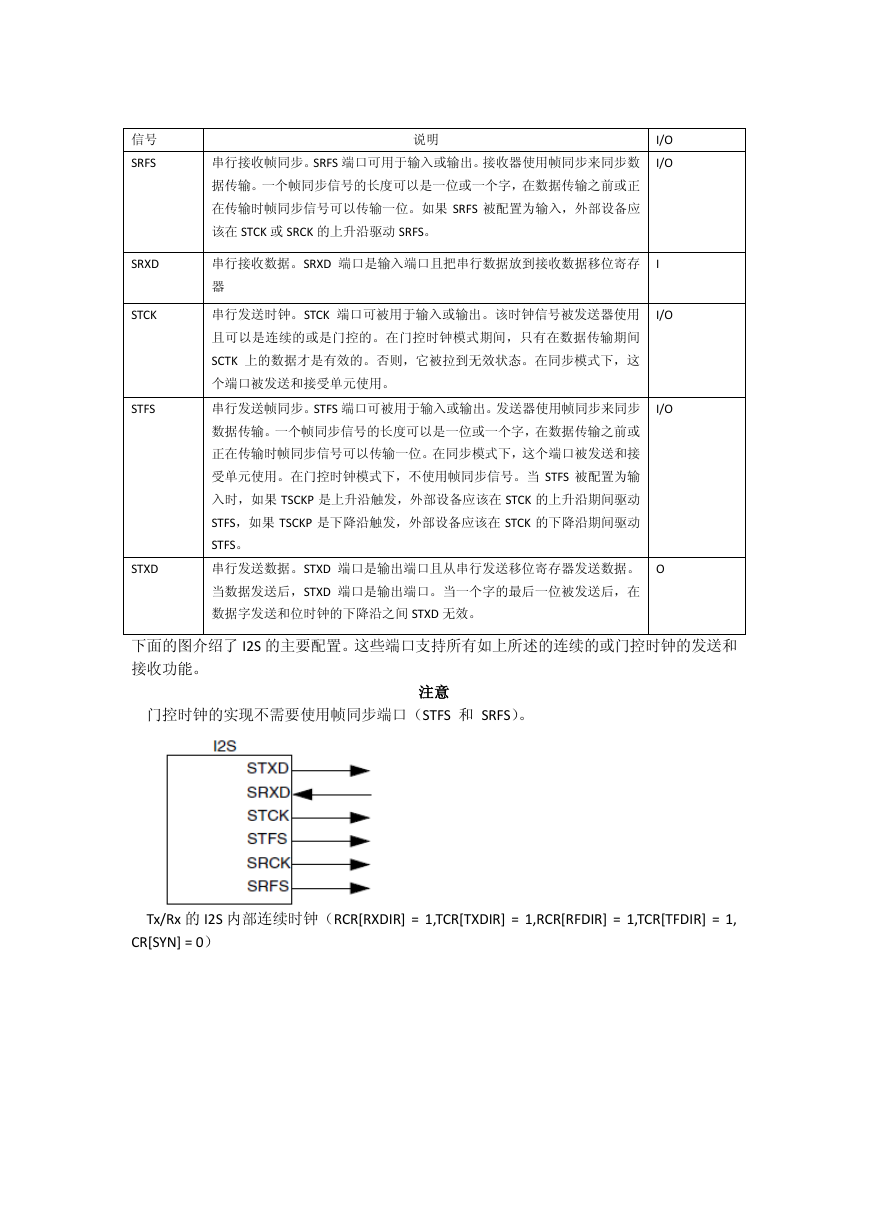

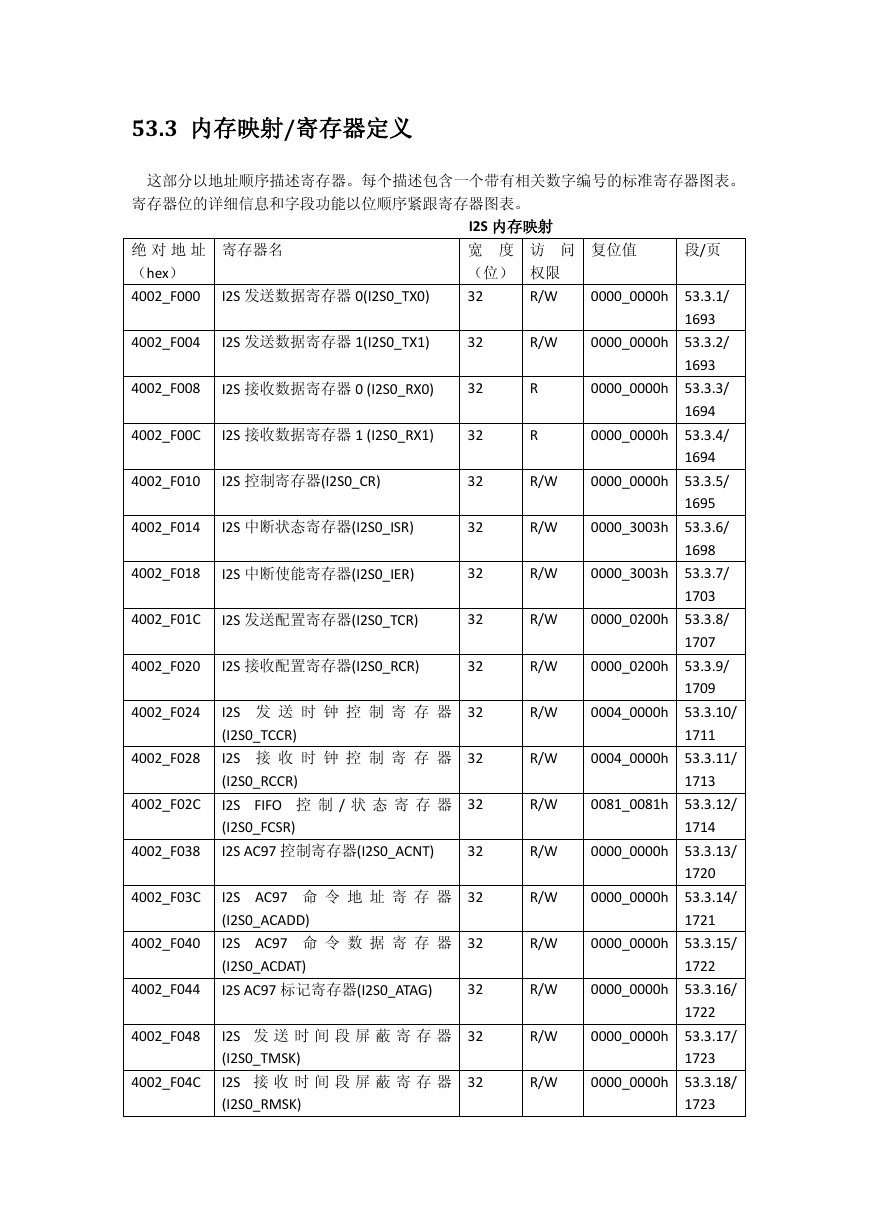

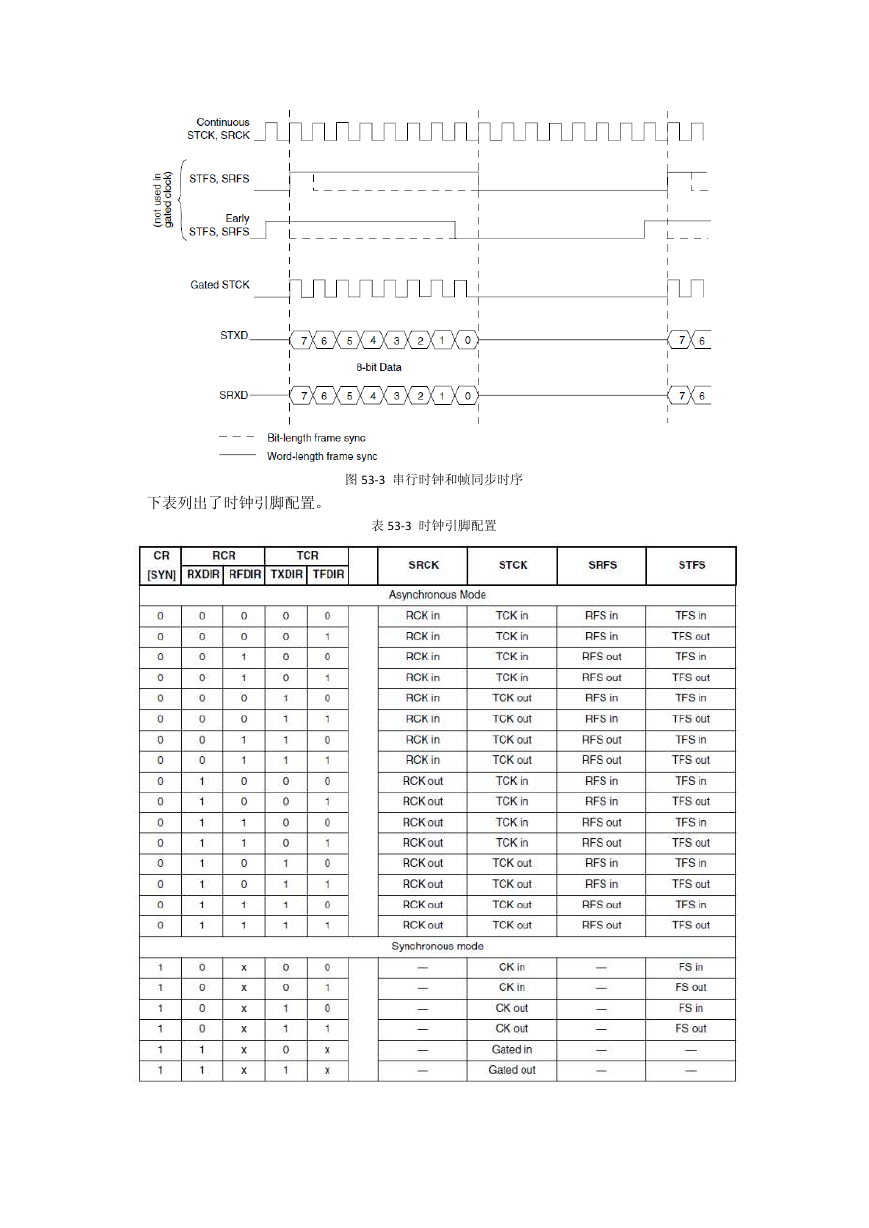

下图介绍一个 8 位数据传输端口信号的例子。介绍的有连续的门控时钟信号,位长帧同步

信号,字长帧同步信号。

�

下表列出了时钟引脚配置。

图 53-3 串行时钟和帧同步时序

表 53-3 时钟引脚配置

�

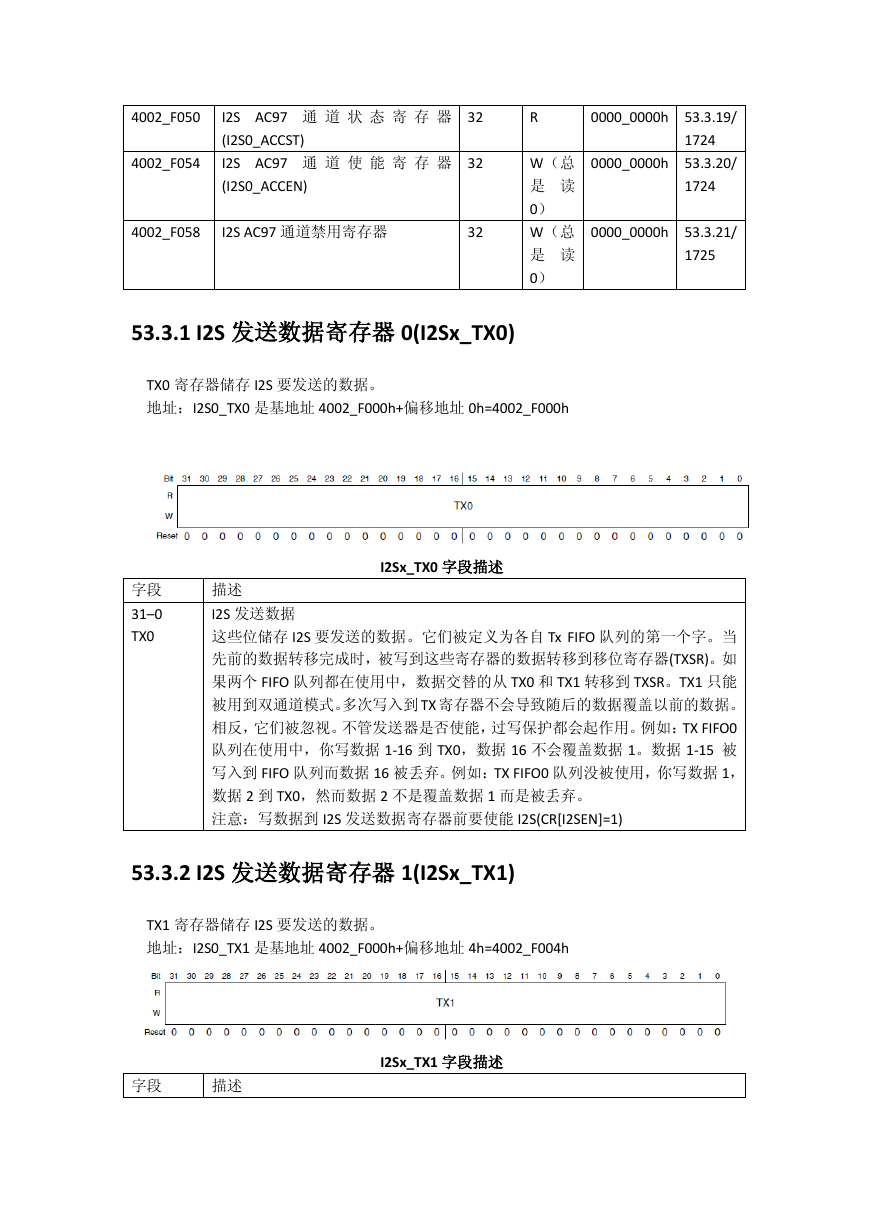

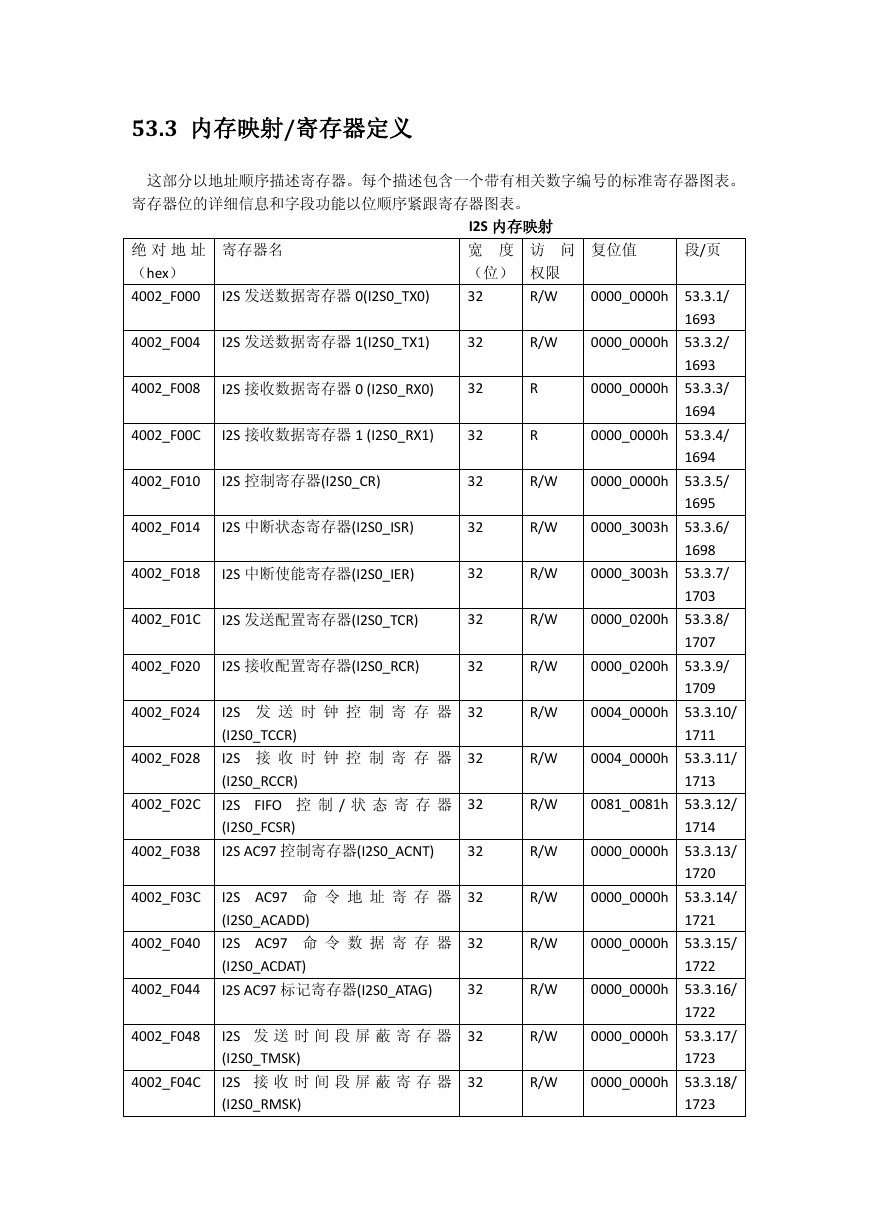

53.3 内存映射/寄存器定义

这部分以地址顺序描述寄存器。每个描述包含一个带有相关数字编号的标准寄存器图表。

寄存器位的详细信息和字段功能以位顺序紧跟寄存器图表。

绝 对 地 址

(hex)

4002_F000

寄存器名

I2S 发送数据寄存器 0(I2S0_TX0)

I2S 内存映射

宽 度

(位)

32

访 问

权限

R/W

复位值

段/页

0000_0000h 53.3.1/

1693

4002_F004

I2S 发送数据寄存器 1(I2S0_TX1)

32

R/W

0000_0000h 53.3.2/

4002_F008

I2S 接收数据寄存器 0 (I2S0_RX0)

32

4002_F00C

I2S 接收数据寄存器 1 (I2S0_RX1)

32

4002_F010

I2S 控制寄存器(I2S0_CR)

4002_F014

I2S 中断状态寄存器(I2S0_ISR)

4002_F018

I2S 中断使能寄存器(I2S0_IER)

4002_F01C

I2S 发送配置寄存器(I2S0_TCR)

4002_F020

I2S 接收配置寄存器(I2S0_RCR)

4002_F024

4002_F028

4002_F02C

4002_F038

4002_F03C

4002_F040

4002_F044

4002_F048

4002_F04C

I2S 发 送 时 钟 控 制 寄 存 器

(I2S0_TCCR)

I2S 接 收 时 钟 控 制 寄 存 器

(I2S0_RCCR)

I2S FIFO 控 制 / 状 态 寄 存 器

(I2S0_FCSR)

I2S AC97 控制寄存器(I2S0_ACNT)

I2S AC97 命 令 地 址 寄 存 器

(I2S0_ACADD)

I2S AC97 命 令 数 据 寄 存 器

(I2S0_ACDAT)

I2S AC97 标记寄存器(I2S0_ATAG)

I2S 发 送 时 间 段 屏 蔽 寄 存 器

(I2S0_TMSK)

I2S 接 收 时 间 段 屏 蔽 寄 存 器

(I2S0_RMSK)

32

32

32

32

32

32

32

32

32

32

32

32

32

32

R

R

1693

0000_0000h 53.3.3/

1694

0000_0000h 53.3.4/

1694

R/W

0000_0000h 53.3.5/

1695

R/W

0000_3003h 53.3.6/

1698

R/W

0000_3003h 53.3.7/

1703

R/W

0000_0200h 53.3.8/

1707

R/W

0000_0200h 53.3.9/

1709

R/W

0004_0000h 53.3.10/

1711

R/W

0004_0000h 53.3.11/

1713

R/W

0081_0081h 53.3.12/

1714

R/W

0000_0000h 53.3.13/

1720

R/W

0000_0000h 53.3.14/

1721

R/W

0000_0000h 53.3.15/

1722

R/W

0000_0000h 53.3.16/

1722

R/W

0000_0000h 53.3.17/

1723

R/W

0000_0000h 53.3.18/

1723

�

4002_F050

4002_F054

I2S AC97 通 道 状 态 寄 存 器

(I2S0_ACCST)

I2S AC97 通 道 使 能 寄 存 器

(I2S0_ACCEN)

4002_F058

I2S AC97 通道禁用寄存器

32

32

32

R

0000_0000h 53.3.19/

1724

0000_0000h 53.3.20/

1724

0000_0000h 53.3.21/

1725

W(总

是 读

0)

W(总

是 读

0)

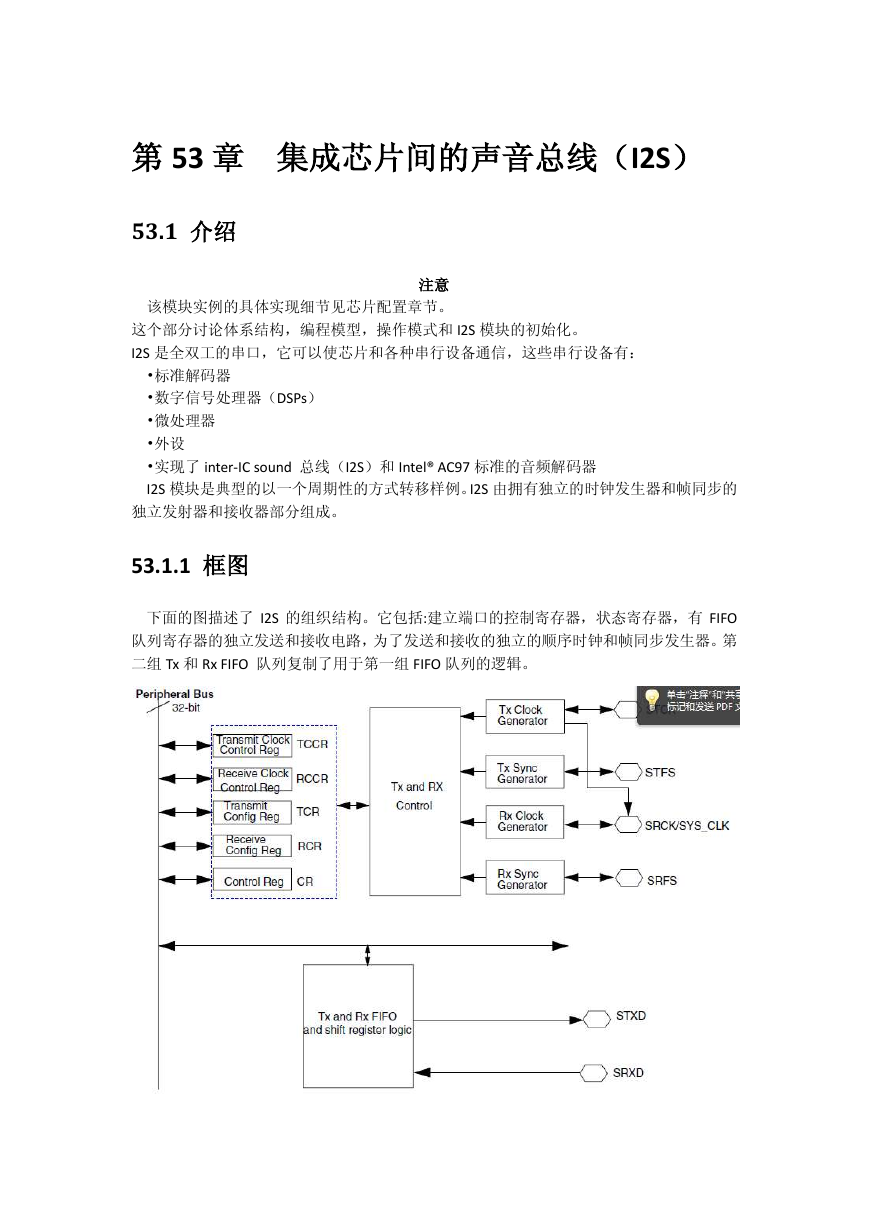

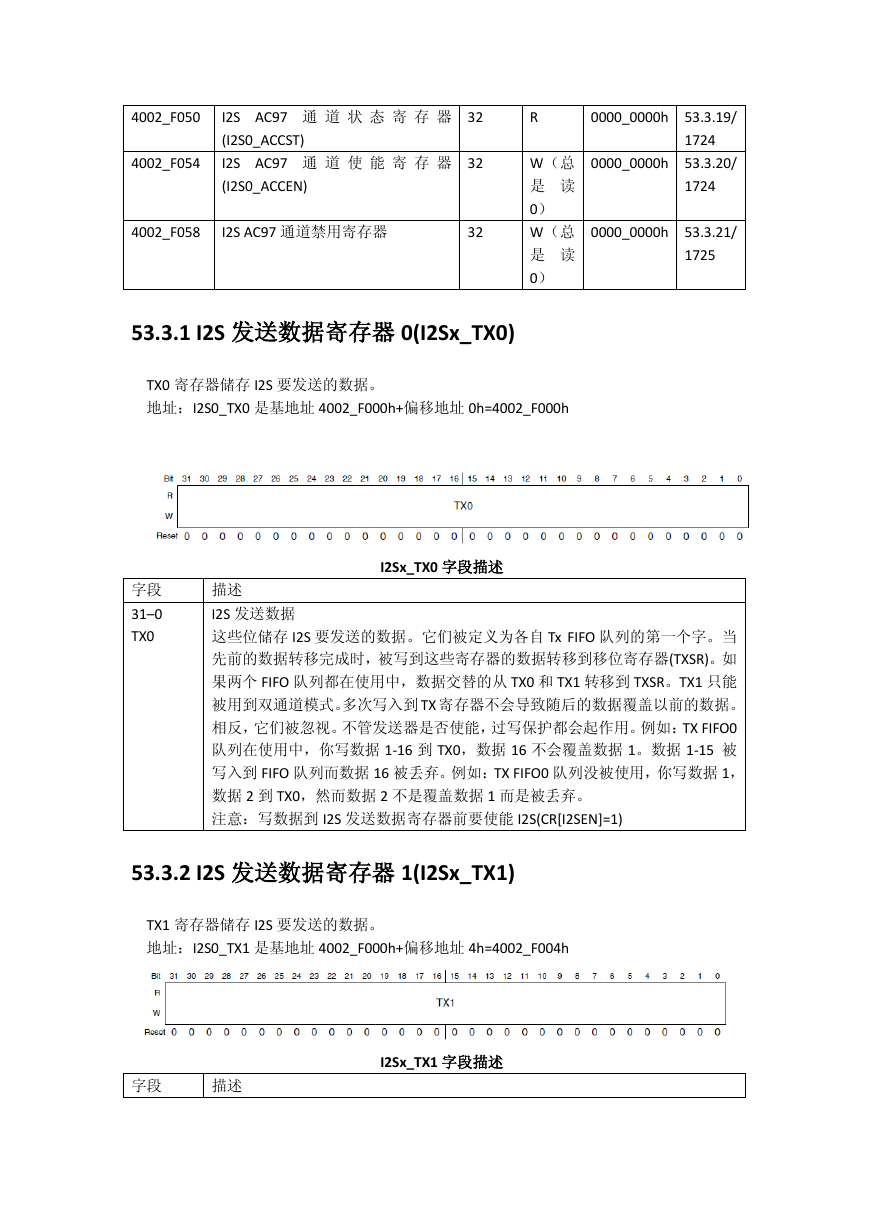

53.3.1 I2S 发送数据寄存器 0(I2Sx_TX0)

TX0 寄存器储存 I2S 要发送的数据。

地址:I2S0_TX0 是基地址 4002_F000h+偏移地址 0h=4002_F000h

字段

31–0

TX0

I2Sx_TX0 字段描述

描述

I2S 发送数据

这些位储存 I2S 要发送的数据。它们被定义为各自 Tx FIFO 队列的第一个字。当

先前的数据转移完成时,被写到这些寄存器的数据转移到移位寄存器(TXSR)。如

果两个 FIFO 队列都在使用中,数据交替的从 TX0 和 TX1 转移到 TXSR。TX1 只能

被用到双通道模式。多次写入到 TX 寄存器不会导致随后的数据覆盖以前的数据。

相反,它们被忽视。不管发送器是否使能,过写保护都会起作用。例如:TX FIFO0

队列在使用中,你写数据 1-16 到 TX0,数据 16 不会覆盖数据 1。数据 1-15 被

写入到 FIFO 队列而数据 16 被丢弃。例如:TX FIFO0 队列没被使用,你写数据 1,

数据 2 到 TX0,然而数据 2 不是覆盖数据 1 而是被丢弃。

注意:写数据到 I2S 发送数据寄存器前要使能 I2S(CR[I2SEN]=1)

53.3.2 I2S 发送数据寄存器 1(I2Sx_TX1)

TX1 寄存器储存 I2S 要发送的数据。

地址:I2S0_TX1 是基地址 4002_F000h+偏移地址 4h=4002_F004h

字段

描述

I2Sx_TX1 字段描述

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc