MSP430G2x53

MSP430G2x13

www.ti.com.cn

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

混混合合信信号号微微控控制制器器

1特特性性

• 低低电电源源电电压压范范围围:: 1.8V 至至 3.6V

• 超超低低功功耗耗

• 通通用用串串行行通通信信接接口口 (USCI)

– 支支持持自自动动波波特特率率检检测测的的增增强强型型通通用用异异步步收收发发器器

– 运运行行模模式式:: 230μA ((在在 1MHz 频频率率和和 2.2V 电电

(UART)

压压条条件件下下))

– 待待机机模模式式:: 0.5μA

– 关关闭闭模模式式 ((RAM 保保持持)):: 0.1μA

5 种种节节能能模模式式

•

• 可可在在不不到到 1μs 的的时时间间里里超超快快速速地地从从待待机机模模式式唤唤醒醒

•

16 位位精精简简指指令令集集 (RISC) 架架构构,,62.5ns 指指令令周周期期时时

间间

• 基基本本时时钟钟模模块块配配置置

– 具具有有四四种种校校准准频频率率并并高高达达 16MHz 的的内内部部频频率率

– 内内部部超超低低功功耗耗低低频频 (LF) 振振荡荡器器

– 32kHz 晶晶体体

– 外外部部数数字字时时钟钟源源

• 两两个个16 位位 Timer_A,,分分别别具具有有三三个个捕捕获获/比比较较寄寄存存

器器

• 多多达达 24 个个支支持持触触摸摸感感测测的的 I/O 引引脚脚

– IrDA 编编码码器器和和解解码码器器

– 同同步步 SPI

– I2C™

• 用用于于模模拟拟信信号号比比较较功功能能或或者者斜斜率率模模数数 (A/D) 转转换换的的

片片载载比比较较器器

• 带带内内部部基基准准、、采采样样与与保保持持以以及及自自动动扫扫描描功功能能的的 10

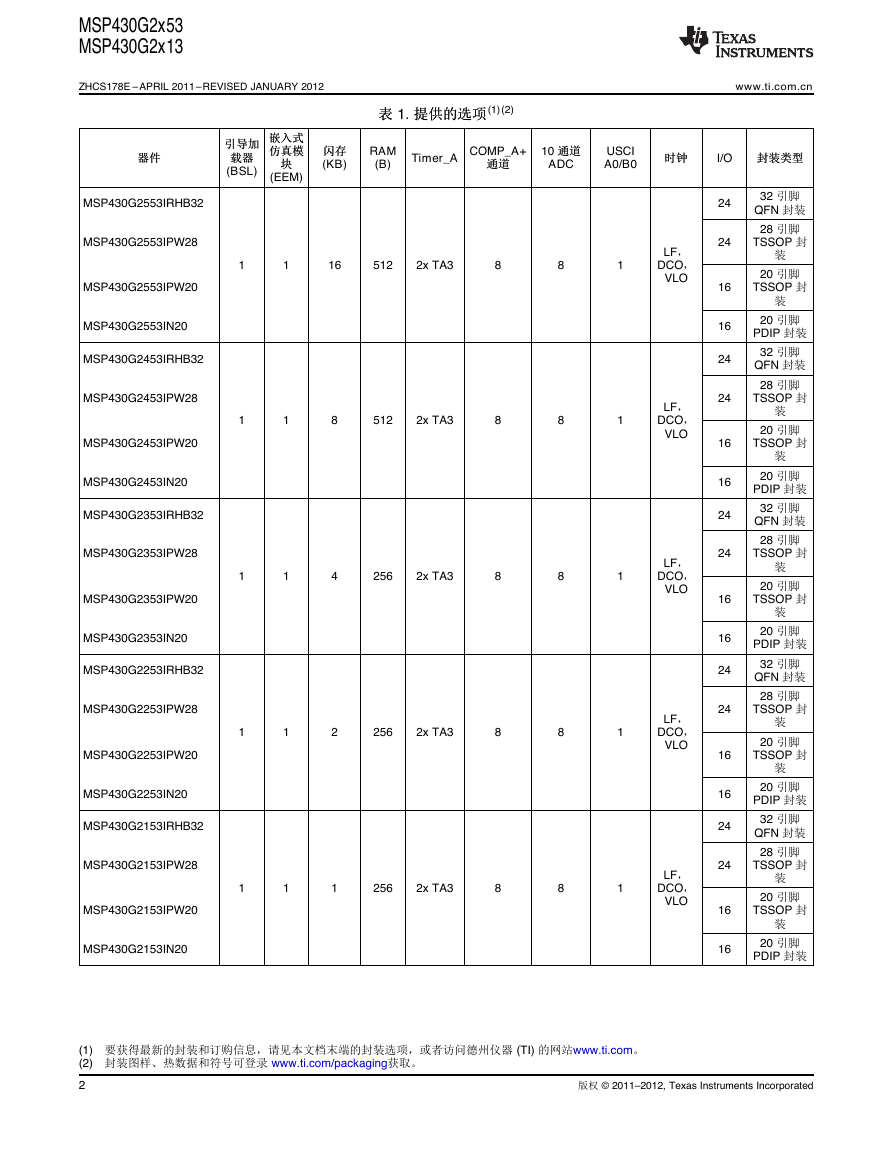

位位 200-ksps 模模数数 (A/D) 转转换换器器((见见 表表 1))

• 欠欠压压检检测测器器

• 串串行行板板上上编编程程,,

无无需需外外部部编编程程电电压压,,

利利用用安安全全熔熔丝丝 (Security Fuse) 实实现现可可编编程程代代码码保保

护护

• 具具有有两两线线制制 (Spy-Bi-Wire) 接接口口的的片片上上仿仿真真逻逻辑辑电电

路路

• 系系列列成成员员汇汇总总于于 表表 1

• 封封装装选选项项

– 薄薄型型小小外外形形尺尺寸寸封封装装 (TSSOP)::20 引引脚脚、、28引引

脚脚

– 塑塑料料双双列列直直插插式式封封装装 (PDIP)::20 引引脚脚

– 四四方方扁扁平平无无引引线线封封装装 (QFN)::32 引引脚脚

• 如如需需了了解解完完整整的的模模块块说说明明,, 请请查查阅阅

《《MSP430x2xx 系系列列产产品品用用户户指指南南》》 ((文文献献编编

号号))

说说明明

德州仪器 (TI) 的MSP430 系列超低功率微控制器包含几个器件,这些器件特有针对多种应用的不同的外设集。 这

种架构与 5 种低功耗模式相组合,专为在便携式测量应用中延长电池的使用寿命而优化。 该器件具有一个强大的

16 位 RISC CPU、16 位寄存器和有助于获得最大编码效率的常数发生器。 数字控制振荡器 (DCO) 可在不到 1 µs

的时间里完成从低功耗模式至运行模式的唤醒。

MSP430G2x13 和 MSP430G2x53 系列是超低功耗混合信号微控制器,具有内置的 16 位定时器、多达 24 个支持

触摸感测的 I/O 引脚、一个通用型模拟比较器以及采用通用串行通信接口的内置通信能力。 此外,MSP430G2x53

系列成员还具有一个 10 位模数 (A/D) 转换器。 有关配置的详情请见 表 1。

典型应用包括低成本传感器系统,此类系统负责捕获模拟信号、将之转换为数字值、随后对数据进行处理以进行显

示或传送至主机系统。

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

版权 © 2011–2012, Texas Instruments Incorporated

English Data Sheet: SLAS735

�

MSP430G2x53

MSP430G2x13

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

www.ti.com.cn

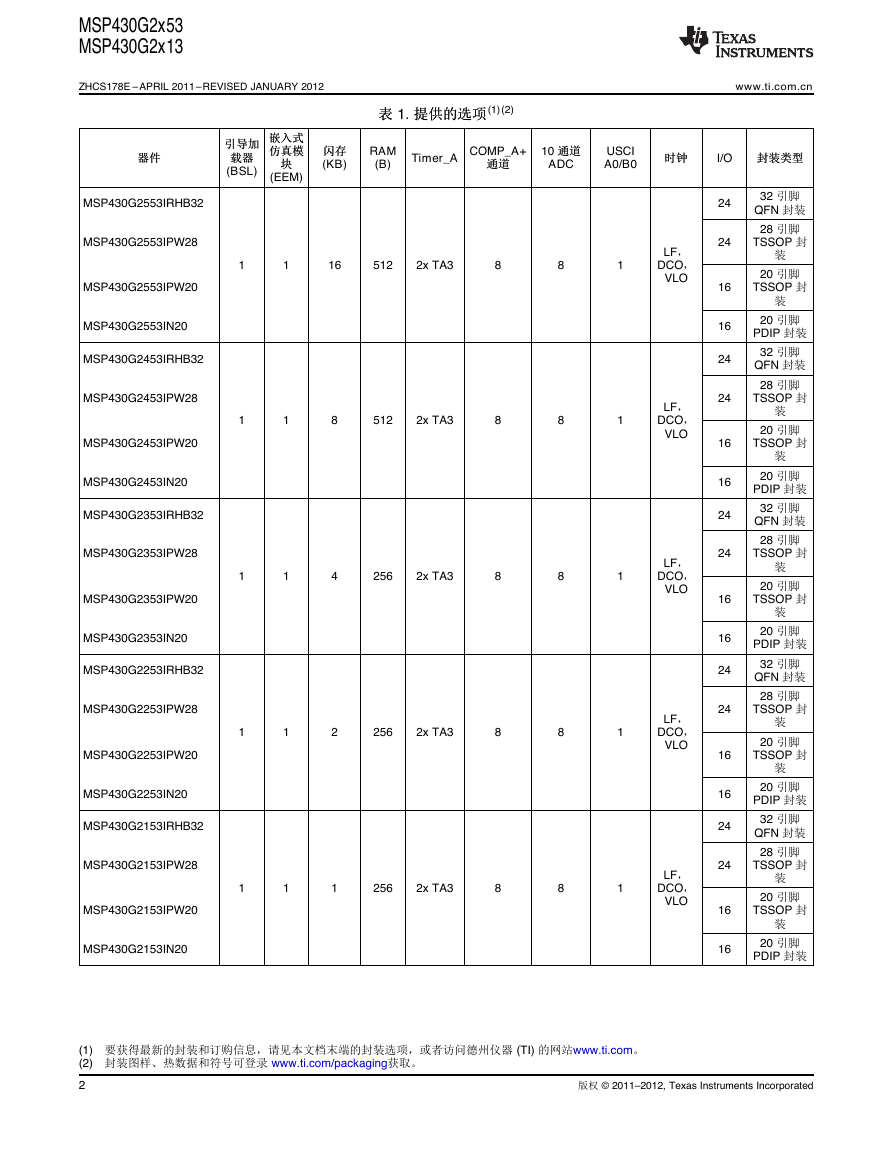

表表 1. 提提供供的的选选项项(1)(2)

器器件件

引引导导加加

载载器器

(BSL)

嵌嵌入入式式

仿仿真真模模 闪闪存存 RAM

(B)

(KB)

块块

(EEM)

Timer_A

COMP_A+

通通道道

10 通通道道

ADC

USCI

A0/B0

时时钟钟

I/O

封封装装类类型型

MSP430G2553IRHB32

MSP430G2553IPW28

MSP430G2553IPW20

MSP430G2553IN20

MSP430G2453IRHB32

MSP430G2453IPW28

MSP430G2453IPW20

MSP430G2453IN20

MSP430G2353IRHB32

MSP430G2353IPW28

MSP430G2353IPW20

MSP430G2353IN20

MSP430G2253IRHB32

MSP430G2253IPW28

MSP430G2253IPW20

MSP430G2253IN20

MSP430G2153IRHB32

MSP430G2153IPW28

MSP430G2153IPW20

MSP430G2153IN20

1

1

16

512

2x TA3

8

8

1

1

1

8

512

2x TA3

8

8

1

1

1

4

256

2x TA3

8

8

1

1

1

2

256

2x TA3

8

8

1

1

1

1

256

2x TA3

8

8

1

LF,

DCO,

VLO

LF,

DCO,

VLO

LF,

DCO,

VLO

LF,

DCO,

VLO

LF,

DCO,

VLO

24

24

16

16

24

24

16

16

24

24

16

16

24

24

16

16

24

24

16

16

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

(1) 要获得最新的封装和订购信息,请见本文档末端的封装选项,或者访问德州仪器 (TI) 的网站www.ti.com。

(2) 封装图样、热数据和符号可登录 www.ti.com/packaging获取。

2

版权 © 2011–2012, Texas Instruments Incorporated

�

www.ti.com.cn

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

表表 1. 提提供供的的选选项项(1)(2) (接接下下页页)

MSP430G2x53

MSP430G2x13

器器件件

引引导导加加

载载器器

(BSL)

嵌嵌入入式式

仿仿真真模模 闪闪存存 RAM

(B)

(KB)

块块

(EEM)

Timer_A

COMP_A+

通通道道

10 通通道道

ADC

USCI

A0/B0

时时钟钟

I/O

封封装装类类型型

MSP430G2513IRHB32

MSP430G2513IPW28

MSP430G2513IPW20

MSP430G2513IN20

MSP430G2413IRHB32

MSP430G2413IPW28

MSP430G2413IPW20

MSP430G2413IN20

MSP430G2313IRHB32

MSP430G2313IPW28

MSP430G2313IPW20

MSP430G2313IN20

MSP430G2213IRHB32

MSP430G2213IPW28

MSP430G2213IPW20

MSP430G2213IN20

MSP430G2113IRHB32

MSP430G2113IPW28

MSP430G2113IPW20

MSP430G2113IN20

1

1

16

512

2x TA3

8

1

1

8

512

2x TA3

8

1

1

4

256

2x TA3

8

1

1

2

256

2x TA3

8

1

1

1

256

2x TA3

8

-

-

-

-

-

1

1

1

1

1

LF,

DCO,

VLO

LF,

DCO,

VLO

LF,

DCO,

VLO

LF,

DCO,

VLO

LF,

DCO,

VLO

24

24

16

16

24

24

16

16

24

24

16

16

24

24

16

16

24

24

16

16

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

32 引脚

QFN 封装

28 引脚

TSSOP 封

装

20 引脚

TSSOP 封

装

20 引脚

PDIP 封装

Copyright © 2011–2012, Texas Instruments Incorporated

3

�

MSP430G2x53

MSP430G2x13

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

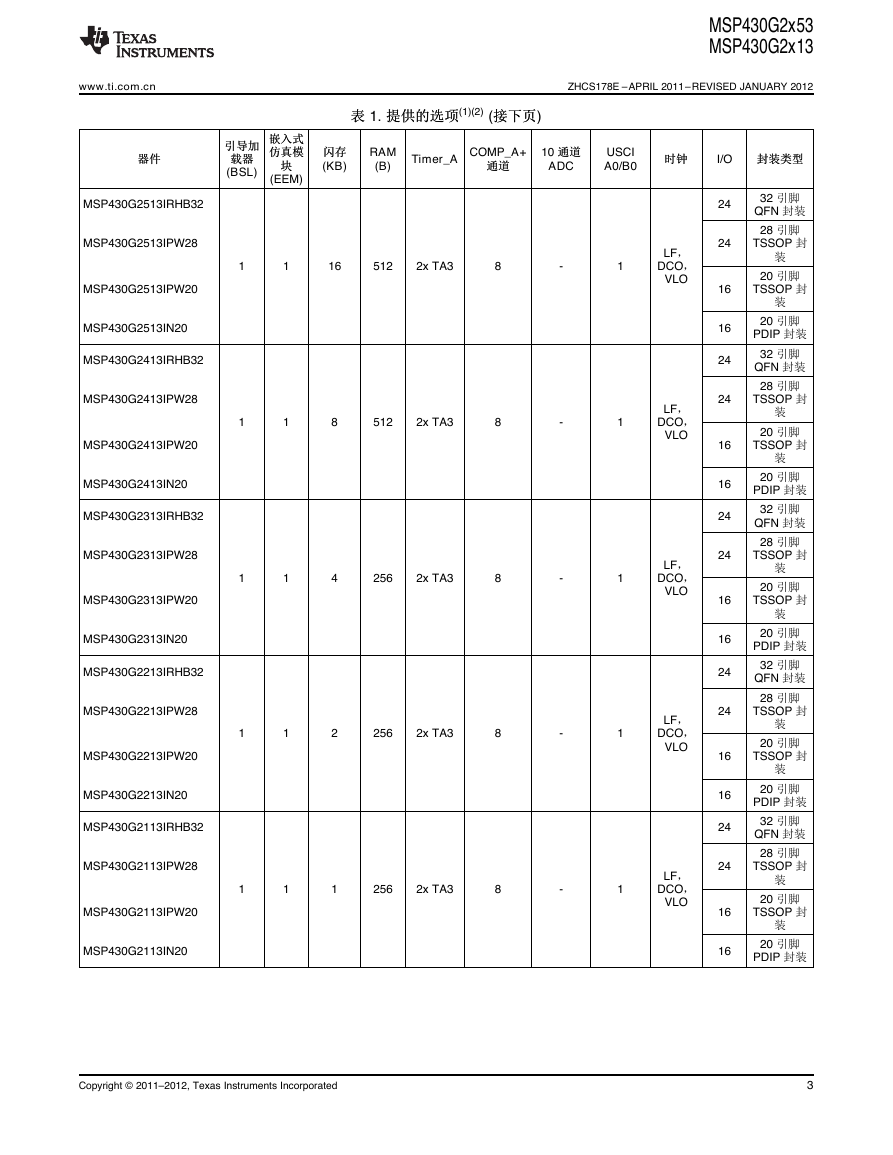

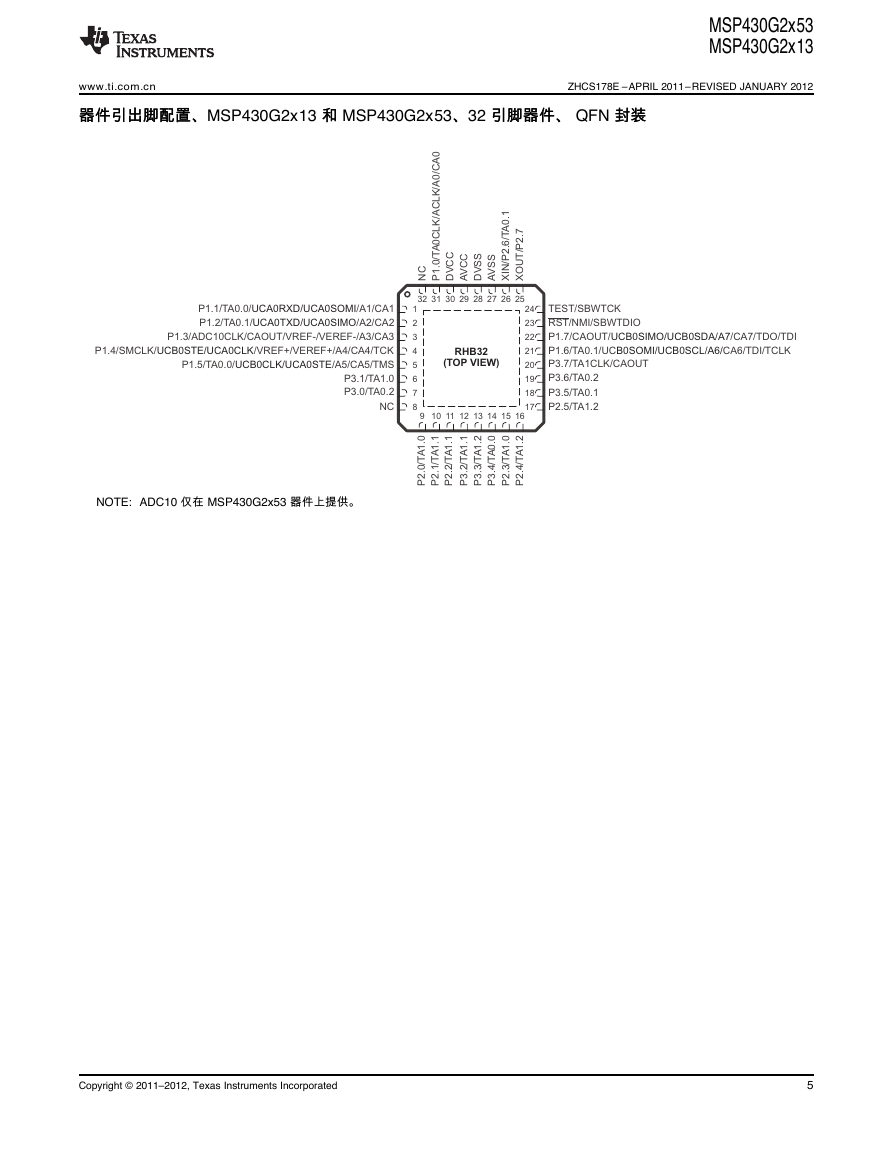

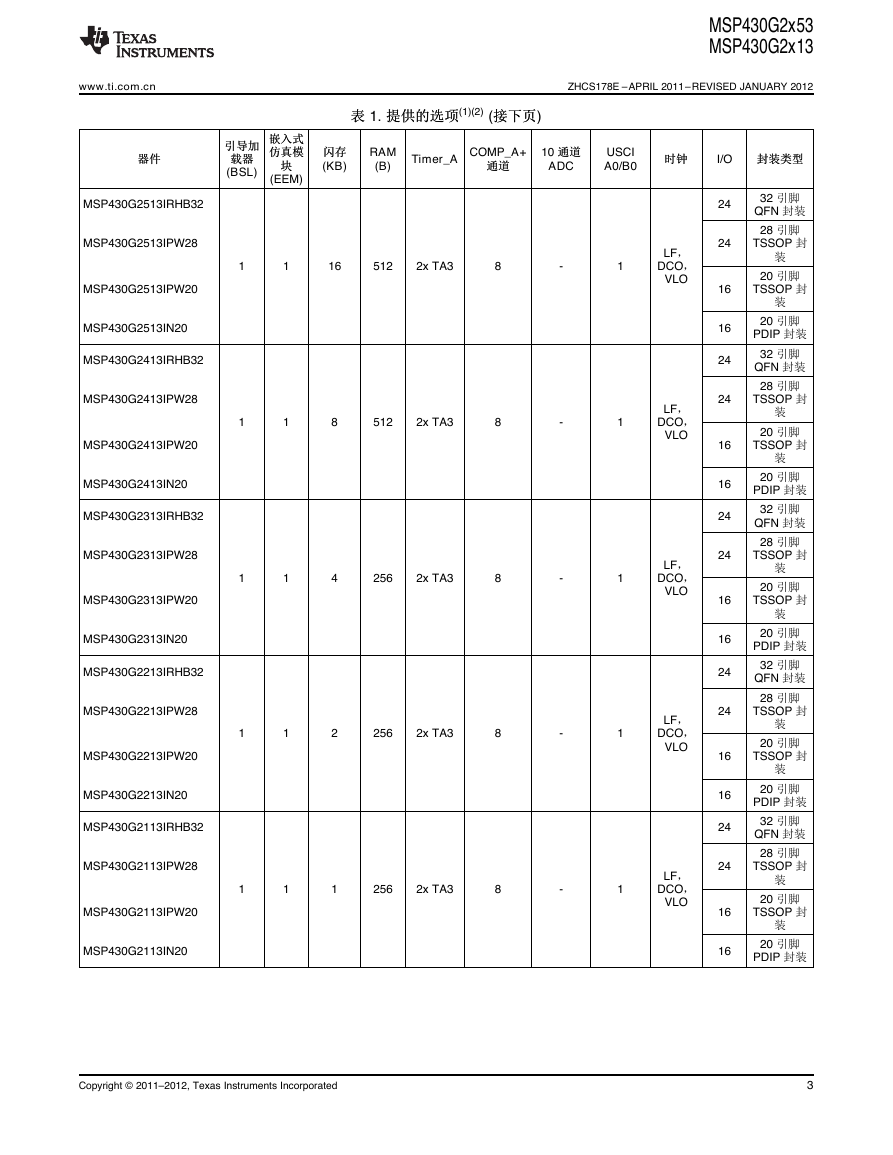

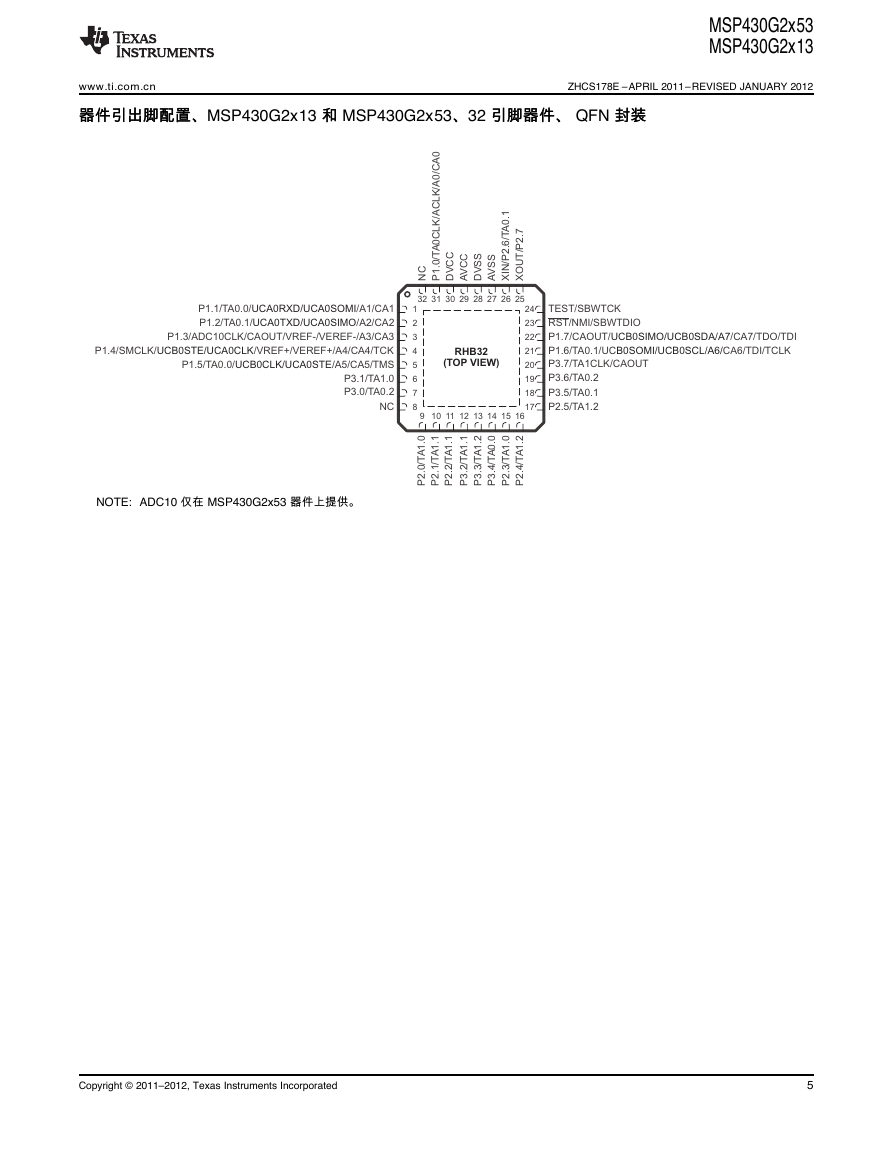

器器件件引引出出脚脚配配置置、、MSP430G2x13 和和 MSP430G2x53、、20 引引脚脚器器件件、、 TSSOP 和和 PDIP 封封装装

www.ti.com.cn

NOTE: ADC10 仅在 MSP430G2x53 器件上提供。

NOTE: P3 端口上的下拉电阻器应通过设定 P3REN.x = 1 来启用。

器器件件引引出出脚脚配配置置、、MSP430G2x13 和和 MSP430G2x53、、28 引引脚脚器器件件、、 TSSOP 封封装装

NOTE: ADC10 仅在 MSP430G2x53 器件上提供。

4

Copyright © 2011–2012, Texas Instruments Incorporated

N20PW20(TOPVIEW)1DVCC2P1.0/TA0CLK/ACLK/A0/CA0345P1.3/ADC10CLK/CAOUT/VREF-/VEREF-/A3/CA3678P2.0/TA1.09P2.1/TA1.110P2.2/TA1.111P2.3/TA1.012P2.4/TA1.213P2.5/TA1.2141516RST/NMI/SBWTDIO17TEST/SBWTCK18XOUT/P2.719XIN/P2.6/TA0.120DVSSP1.6/TA0.1/CA6/TDI/TCLKUCB0SOMI/UCB0SCL/A6/P1.7/CAOUT/A7/CA7/TDO/TDI/UCB0SIMO/UCB0SDAP1.1/TA0.0/A1/CA1/UCA0RXD/UCA0SOMIP1.2/TA0.1/A2/CA2/UCA0TXD/PUCA0SIMOP1.4/SMCLK/CA4/TCK/VREF+/VEREF+/A4/UCB0STE/UCA0CLKP1.5/TA0.0/A5/CA5/TMS/UCB0CLK/UCA0STEPW28(TOPVIEW)1DVCC2P1.0/TA0CLK/ACLK/A0/CA0345P1.3/ADC10CLK/CAOUT/VREF-/VEREF-/A3/CA3678P3.0/TA0.29P3.1/TA1.010P2.0/TA1.019P3.5/TA0.120P3.6/TA0.221P3.7/TA1CLK/CAOUT222324RST/NMI/SBWTDIO25TEST/SBWTCK26XOUT/P2.727XIN/P2.6/TA0.128DVSSP1.6/TA0.1/CA6/TDI/TCLKUCB0SOMI/UCB0SCL/A6/P1.7/CAOUT/A7/CA7/TDO/TDI/UCB0SIMO/UCB0SDAP1.1/TA0.0/A1/CA1/UCA0RXD/UCA0SOMIP1.2/TA0.1/A2/CA2/UCA0TXD/PUCA0SIMOP1.4/SMCLK/CA4/TCK/VREF+/VEREF+/A4/UCB0STE/UCA0CLKP1.5/TA0.0/A5/CA5/TMS/UCB0CLK/UCA0STE1112P2.2/TA1.113P3.2/TA1.114P3.3/TA1.215P3.4/TA0.016P2.3/TA1.017P2.4/TA1.218P2.5/TA1.2P2.1/TA1.1�

www.ti.com.cn

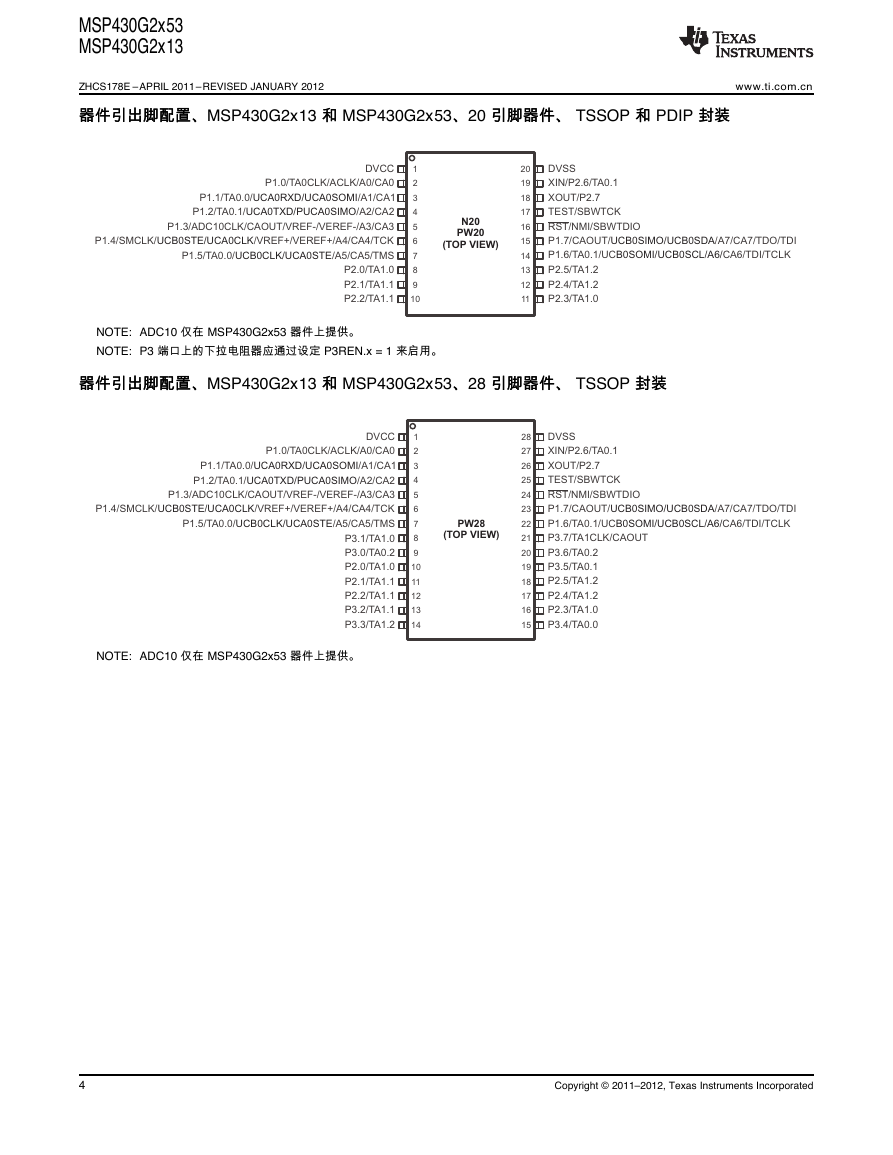

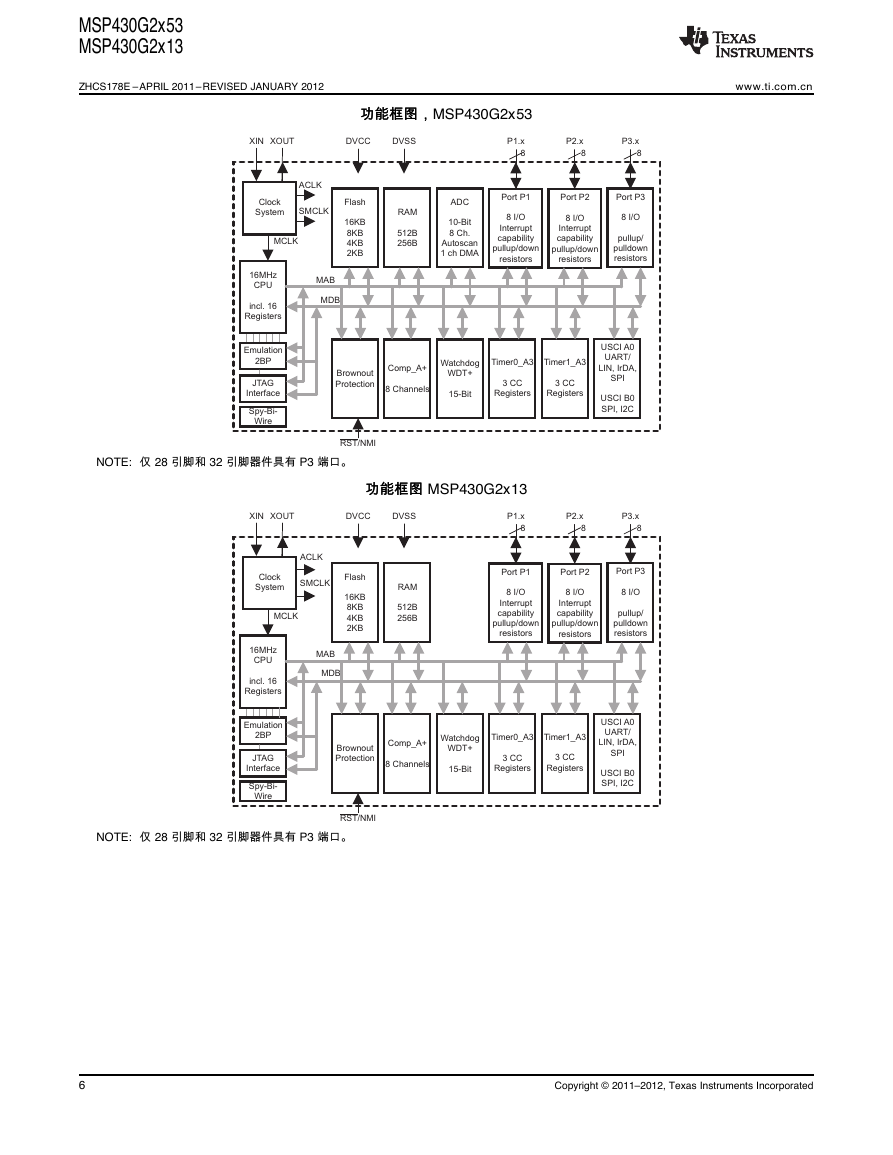

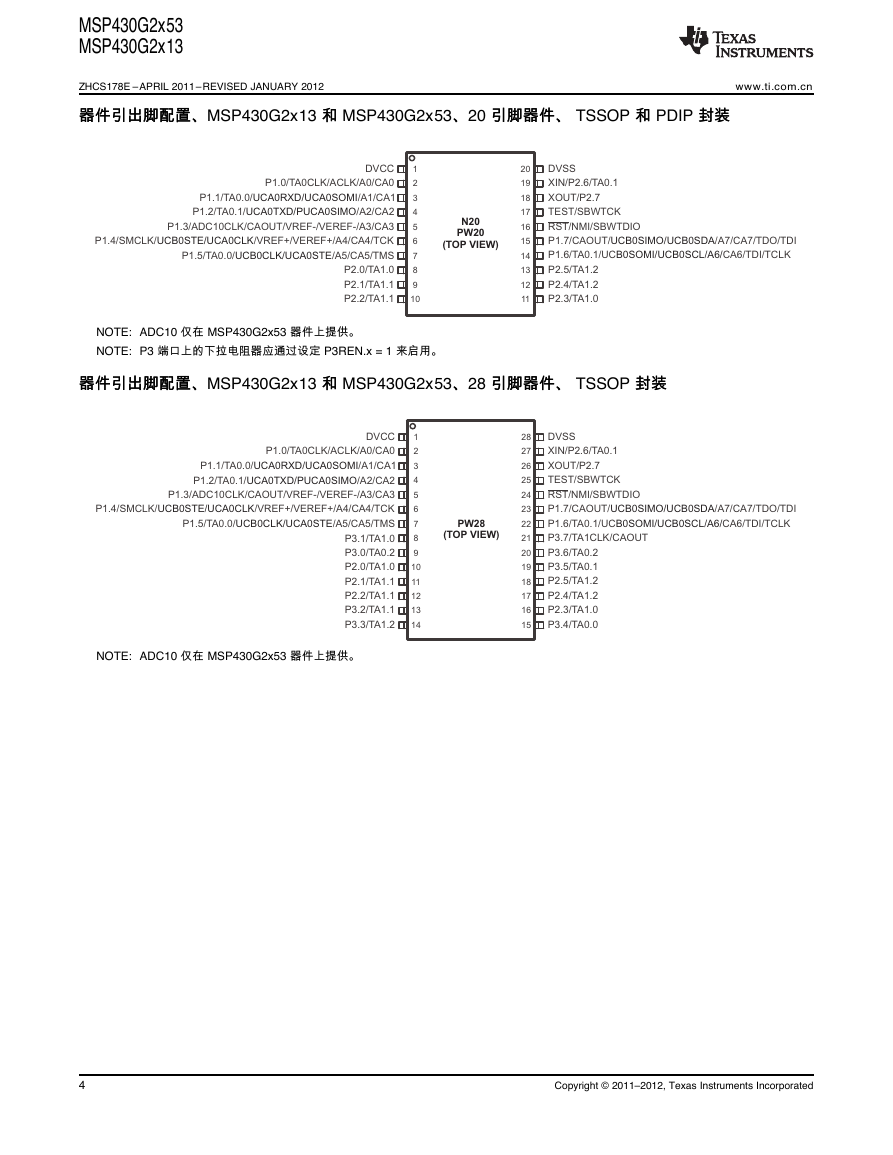

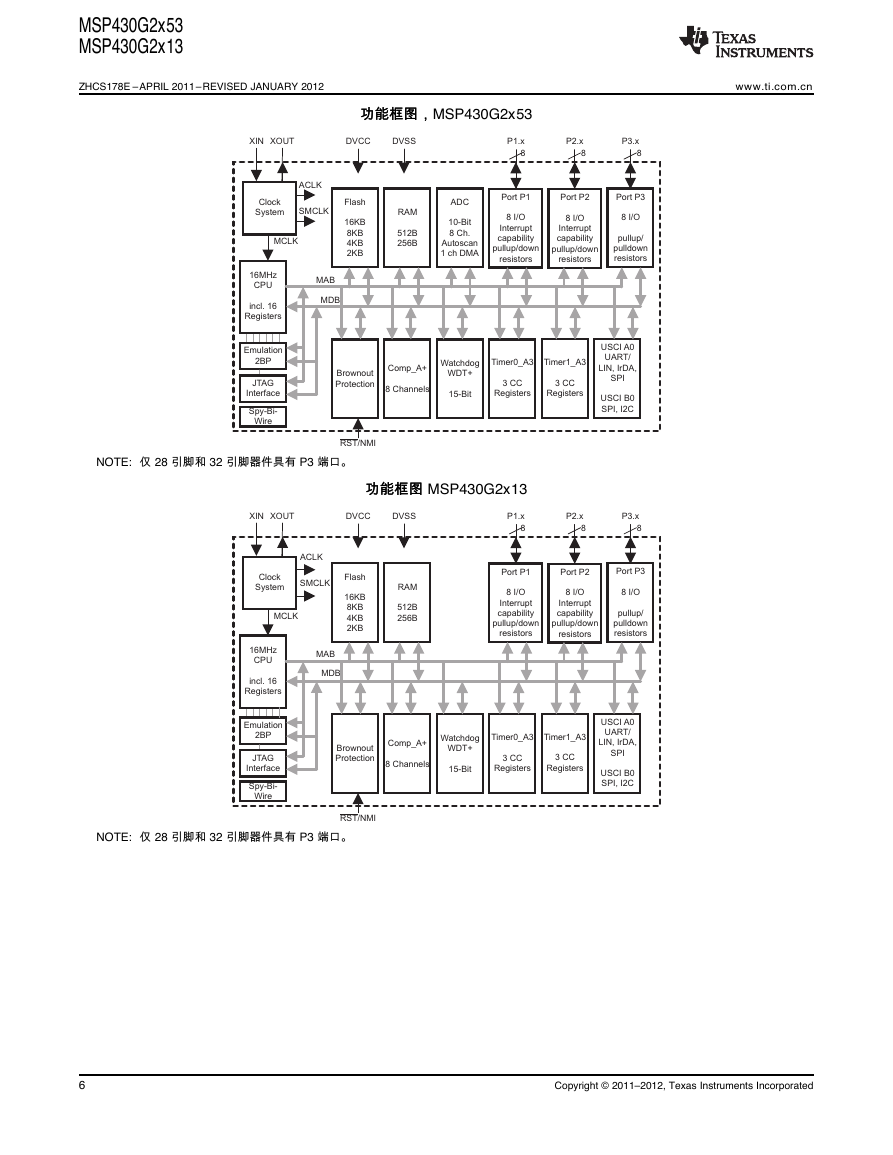

器器件件引引出出脚脚配配置置、、MSP430G2x13 和和 MSP430G2x53、、32 引引脚脚器器件件、、 QFN 封封装装

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

MSP430G2x53

MSP430G2x13

NOTE: ADC10 仅在 MSP430G2x53 器件上提供。

Copyright © 2011–2012, Texas Instruments Incorporated

5

RHB32(TOPVIEW)123456P2.0/TA1.07P2.1/TA1.18NC9P2.2/TA1.110P3.0/TA0.211P3.1/TA1.012P3.2/TA1.113P3.3/TA1.214P3.4/TA0.015P3.5/TA0.116P2.3/TA1.017P2.4/TA1.218P2.5/TA1.21920P3.6/TA0.221P3.7/TA1CLK/CAOUT2223RST/NMI/SBWTDIO24TEST/SBWTCK25XOUT/P2.726XIN/P2.6/TA0.127AVSS28DVSS29AVCC30DVCC31P1.0/TA0CLK/ACLK/A0/CA032NCP1.3/ADC10CLK/CAOUT/VREF-/VEREF-/A3/CA3P1.1/TA0.0/A1/CA1/UCA0RXD/UCA0SOMIP1.2/TA0.1/A2/CA2/UCA0TXD/UCA0SIMOP1.4/SMCLK/CA4/TCK/VREF+/VEREF+/A4/UCB0STE/UCA0CLKP1.5/TA0.0/A5/CA5/TMS/UCB0CLK/UCA0STEP1.6/TA0.1/CA6/TDI/TCLKUCB0SOMI/UCB0SCL/A6/P1.7/CAOUT/CA7/TDO/TDI/UCB0SIMO/UCB0SDA/A7�

MSP430G2x53

MSP430G2x13

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

www.ti.com.cn

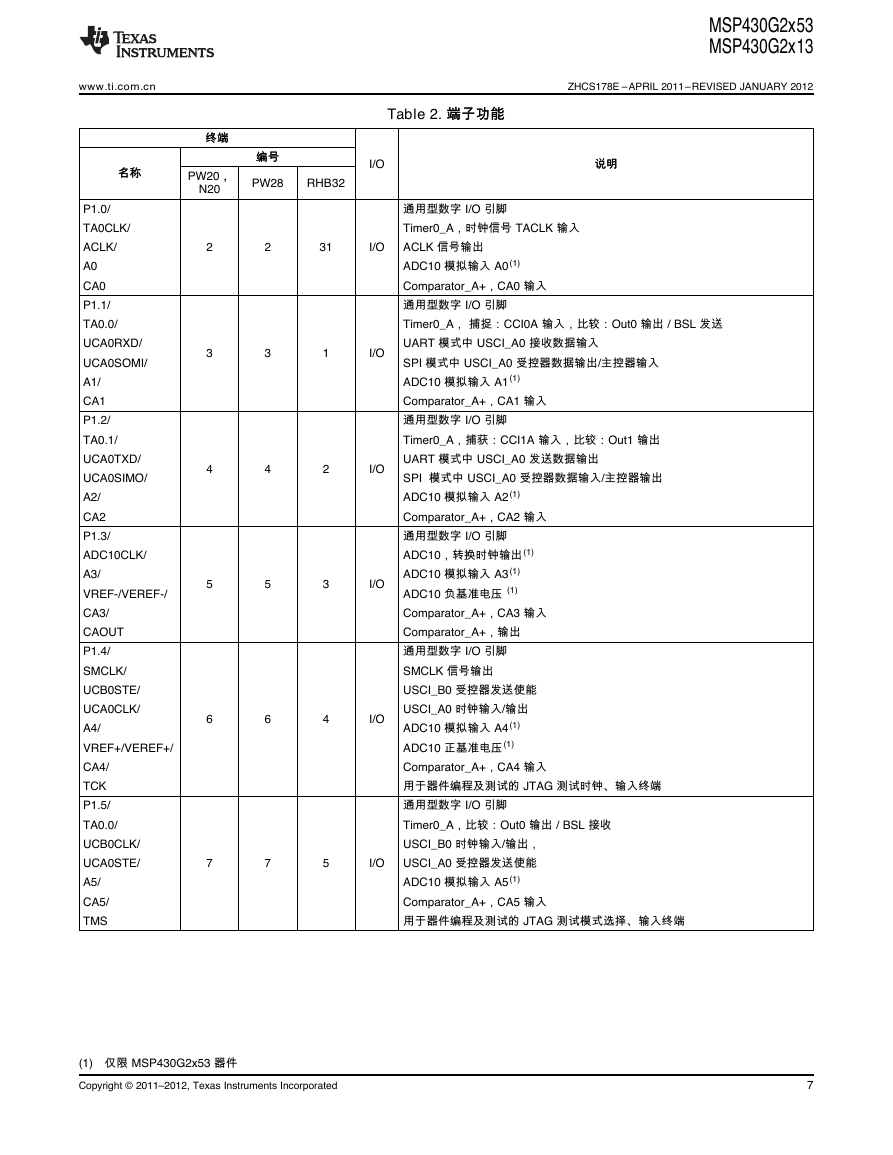

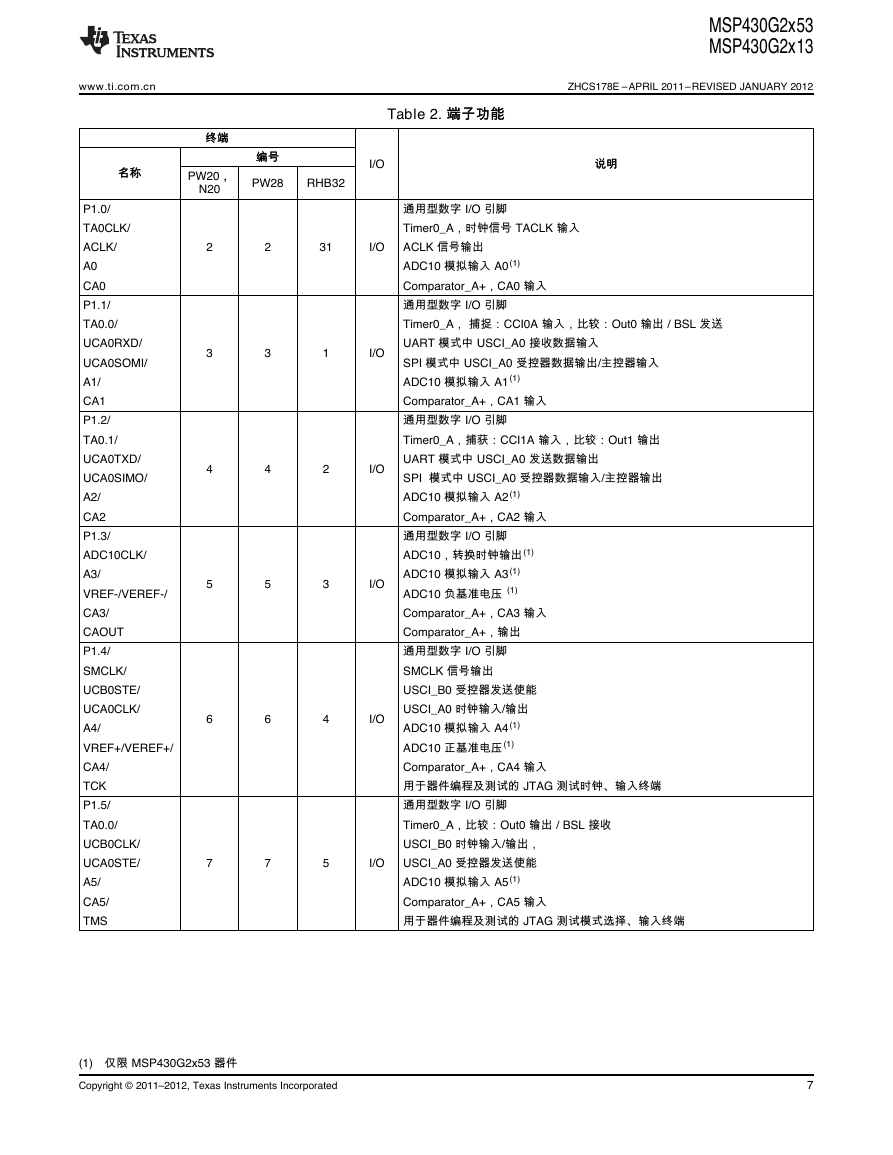

功功能能框框图图,,MSP430G2x53

NOTE: 仅 28 引脚和 32 引脚器件具有 P3 端口。

功功能能框框图图 MSP430G2x13

NOTE: 仅 28 引脚和 32 引脚器件具有 P3 端口。

6

Copyright © 2011–2012, Texas Instruments Incorporated

ClockSystemBrownoutProtectionRST/NMIDVCCDVSSMCLKWatchdogWDT+15-BitTimer0_A33 CCRegisters16MHzCPUincl. 16RegistersEmulation2BPJTAGInterfaceSMCLKACLKMDBMABPort P18 I/OInterruptcapabilitypullup/downresistorsP1.x8P2.xPort P28 I/OInterruptcapabilitypullup/downresistorsSpy-Bi-WireComp_A+8 ChannelsTimer1_A33 CCRegistersXINXOUTPort P38 I/Opullup/pulldownresistorsP3.x88RAM512B256BFlash16KB8KB4KB2KBUSCIA0UART/LIN, IrDA,SPIUSCI B0SPI, I2CADC10-Bit8 Ch.Autoscan1 ch DMAClockSystemBrownoutProtectionRST/NMIDVCCDVSSMCLKWatchdogWDT+15-BitTimer0_A33 CCRegisters16MHzCPUincl. 16RegistersEmulation2BPJTAGInterfaceSMCLKACLKPort P18 I/OInterruptcapabilitypullup/downresistorsP1.x8P2.xPort P28 I/OInterruptcapabilitypullup/downresistorsSpy-Bi-WireComp_A+8 ChannelsTimer1_A33 CCRegistersXINXOUTPort P38 I/Opullup/pulldownresistorsP3.x88RAM512B256BFlash16KB8KB4KB2KBUSCIA0UART/LIN, IrDA,SPIUSCI B0SPI, I2CMDBMAB�

www.ti.com.cn

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

MSP430G2x53

MSP430G2x13

终终端端

编编号号

PW20,, PW28

N20

2

3

4

5

2

3

4

5

I/O

RHB32

31

I/O

1

I/O

2

I/O

3

I/O

6

6

4

I/O

7

7

5

I/O

名名称称

P1.0/

TA0CLK/

ACLK/

A0

CA0

P1.1/

TA0.0/

UCA0RXD/

UCA0SOMI/

A1/

CA1

P1.2/

TA0.1/

UCA0TXD/

UCA0SIMO/

A2/

CA2

P1.3/

ADC10CLK/

A3/

VREF-/VEREF-/

CA3/

CAOUT

P1.4/

SMCLK/

UCB0STE/

UCA0CLK/

A4/

VREF+/VEREF+/

CA4/

TCK

P1.5/

TA0.0/

UCB0CLK/

UCA0STE/

A5/

CA5/

TMS

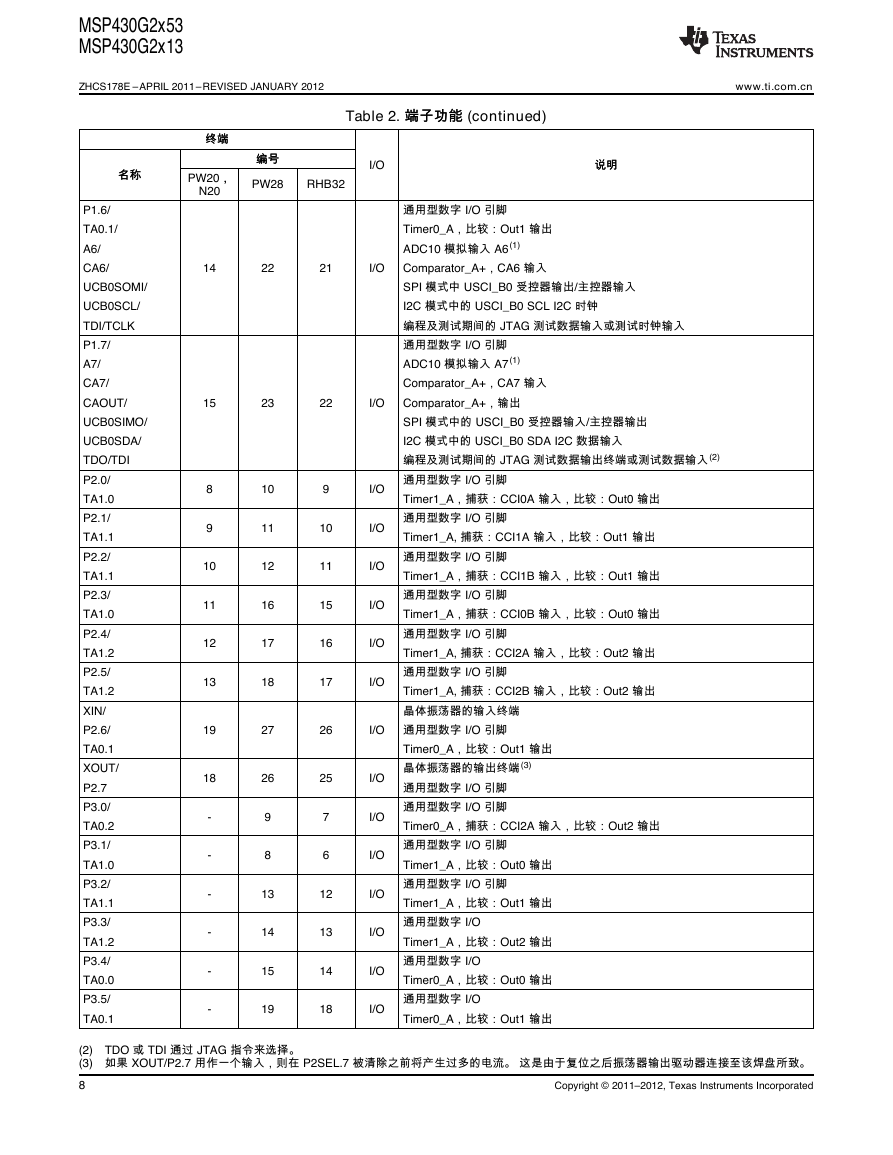

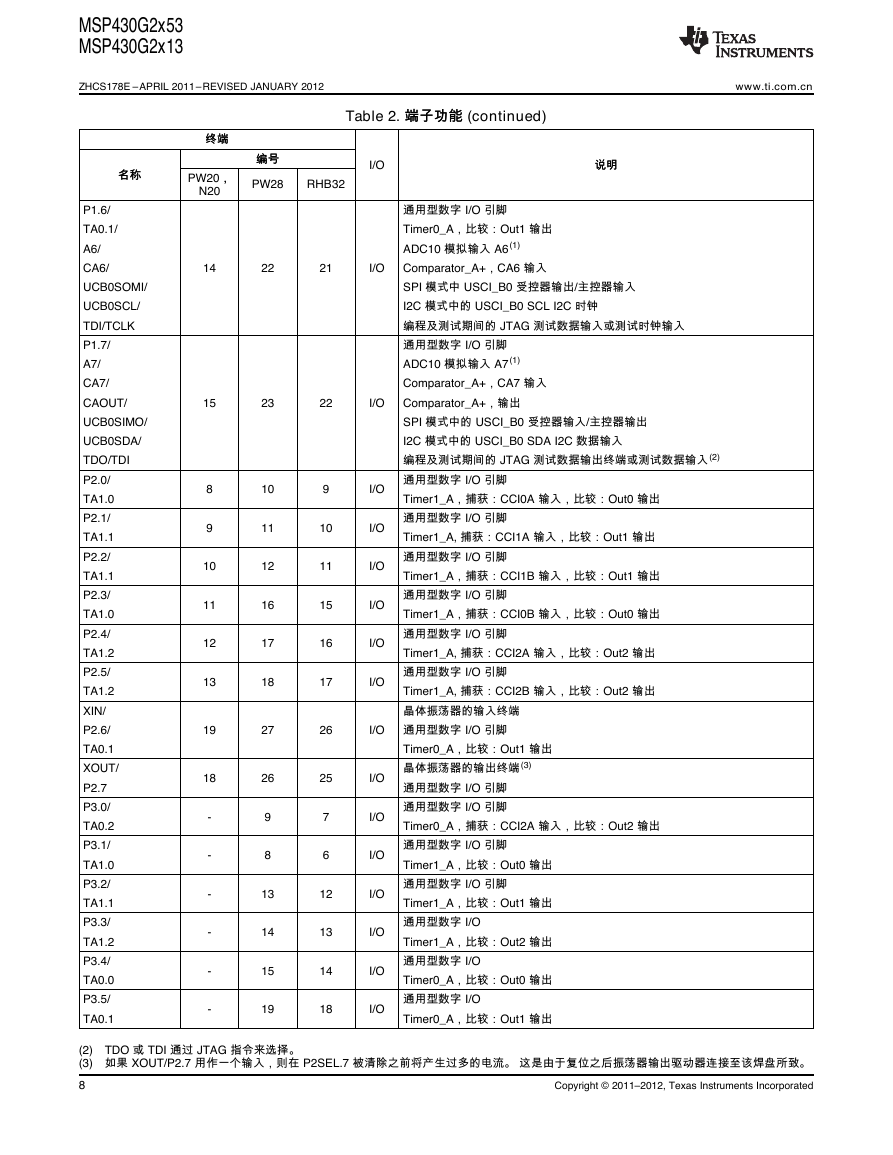

Table 2. 端端子子功功能能

说说明明

通用型数字 I/O 引脚

Timer0_A,时钟信号 TACLK 输入

ACLK 信号输出

ADC10 模拟输入 A0 (1)

Comparator_A+,CA0 输入

通用型数字 I/O 引脚

Timer0_A, 捕捉:CCI0A 输入,比较:Out0 输出 / BSL 发送

UART 模式中 USCI_A0 接收数据输入

SPI 模式中 USCI_A0 受控器数据输出/主控器输入

ADC10 模拟输入 A1(1)

Comparator_A+,CA1 输入

通用型数字 I/O 引脚

Timer0_A,捕获:CCI1A 输入,比较:Out1 输出

UART 模式中 USCI_A0 发送数据输出

SPI 模式中 USCI_A0 受控器数据输入/主控器输出

ADC10 模拟输入 A2(1)

Comparator_A+,CA2 输入

通用型数字 I/O 引脚

ADC10,转换时钟输出 (1)

ADC10 模拟输入 A3(1)

ADC10 负基准电压 (1)

Comparator_A+,CA3 输入

Comparator_A+,输出

通用型数字 I/O 引脚

SMCLK 信号输出

USCI_B0 受控器发送使能

USCI_A0 时钟输入/输出

ADC10 模拟输入 A4(1)

ADC10 正基准电压 (1)

Comparator_A+,CA4 输入

用于器件编程及测试的 JTAG 测试时钟、输入终端

通用型数字 I/O 引脚

Timer0_A,比较:Out0 输出 / BSL 接收

USCI_B0 时钟输入/输出,

USCI_A0 受控器发送使能

ADC10 模拟输入 A5(1)

Comparator_A+,CA5 输入

用于器件编程及测试的 JTAG 测试模式选择、输入终端

(1) 仅限 MSP430G2x53 器件

Copyright © 2011–2012, Texas Instruments Incorporated

7

�

MSP430G2x53

MSP430G2x13

ZHCS178E –APRIL 2011–REVISED JANUARY 2012

www.ti.com.cn

Table 2. 端端子子功功能能 (continued)

终终端端

编编号号

PW20,, PW28

N20

I/O

RHB32

14

22

21

I/O

15

23

22

I/O

8

9

10

11

12

13

19

18

-

-

-

-

-

-

10

11

12

16

17

18

27

26

9

8

13

14

15

19

9

10

11

15

16

17

26

25

7

6

12

13

14

18

说说明明

通用型数字 I/O 引脚

Timer0_A,比较:Out1 输出

ADC10 模拟输入 A6(1)

Comparator_A+,CA6 输入

SPI 模式中 USCI_B0 受控器输出/主控器输入

I2C 模式中的 USCI_B0 SCL I2C 时钟

编程及测试期间的 JTAG 测试数据输入或测试时钟输入

通用型数字 I/O 引脚

ADC10 模拟输入 A7(1)

Comparator_A+,CA7 输入

Comparator_A+,输出

SPI 模式中的 USCI_B0 受控器输入/主控器输出

I2C 模式中的 USCI_B0 SDA I2C 数据输入

编程及测试期间的 JTAG 测试数据输出终端或测试数据输入 (2)

通用型数字 I/O 引脚

Timer1_A,捕获:CCI0A 输入,比较:Out0 输出

通用型数字 I/O 引脚

Timer1_A, 捕获:CCI1A 输入,比较:Out1 输出

通用型数字 I/O 引脚

Timer1_A,捕获:CCI1B 输入,比较:Out1 输出

通用型数字 I/O 引脚

Timer1_A,捕获:CCI0B 输入,比较:Out0 输出

通用型数字 I/O 引脚

Timer1_A, 捕获:CCI2A 输入,比较:Out2 输出

通用型数字 I/O 引脚

Timer1_A, 捕获:CCI2B 输入,比较:Out2 输出

晶体振荡器的输入终端

I/O

I/O

I/O

I/O

I/O

I/O

I/O 通用型数字 I/O 引脚

Timer0_A,比较:Out1 输出

晶体振荡器的输出终端 (3)

通用型数字 I/O 引脚

通用型数字 I/O 引脚

Timer0_A,捕获:CCI2A 输入,比较:Out2 输出

通用型数字 I/O 引脚

Timer1_A,比较:Out0 输出

通用型数字 I/O 引脚

Timer1_A,比较:Out1 输出

通用型数字 I/O

Timer1_A,比较:Out2 输出

通用型数字 I/O

Timer0_A,比较:Out0 输出

通用型数字 I/O

Timer0_A,比较:Out1 输出

I/O

I/O

I/O

I/O

I/O

I/O

I/O

名名称称

P1.6/

TA0.1/

A6/

CA6/

UCB0SOMI/

UCB0SCL/

TDI/TCLK

P1.7/

A7/

CA7/

CAOUT/

UCB0SIMO/

UCB0SDA/

TDO/TDI

P2.0/

TA1.0

P2.1/

TA1.1

P2.2/

TA1.1

P2.3/

TA1.0

P2.4/

TA1.2

P2.5/

TA1.2

XIN/

P2.6/

TA0.1

XOUT/

P2.7

P3.0/

TA0.2

P3.1/

TA1.0

P3.2/

TA1.1

P3.3/

TA1.2

P3.4/

TA0.0

P3.5/

TA0.1

(2) TDO 或 TDI 通过 JTAG 指令来选择。

(3) 如果 XOUT/P2.7 用作一个输入,则在 P2SEL.7 被清除之前将产生过多的电流。 这是由于复位之后振荡器输出驱动器连接至该焊盘所致。

8

Copyright © 2011–2012, Texas Instruments Incorporated

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc