TMS320x2833x, 2823x System Control and Interrupts

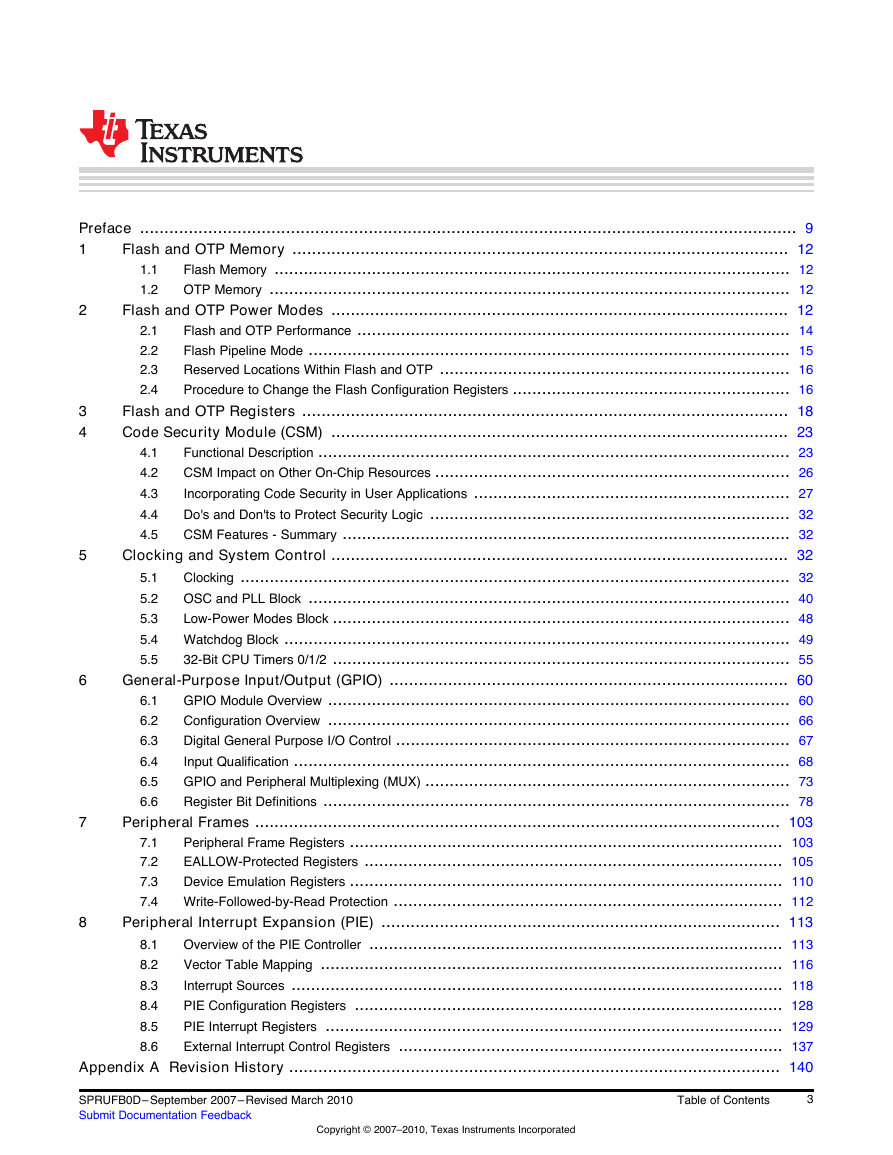

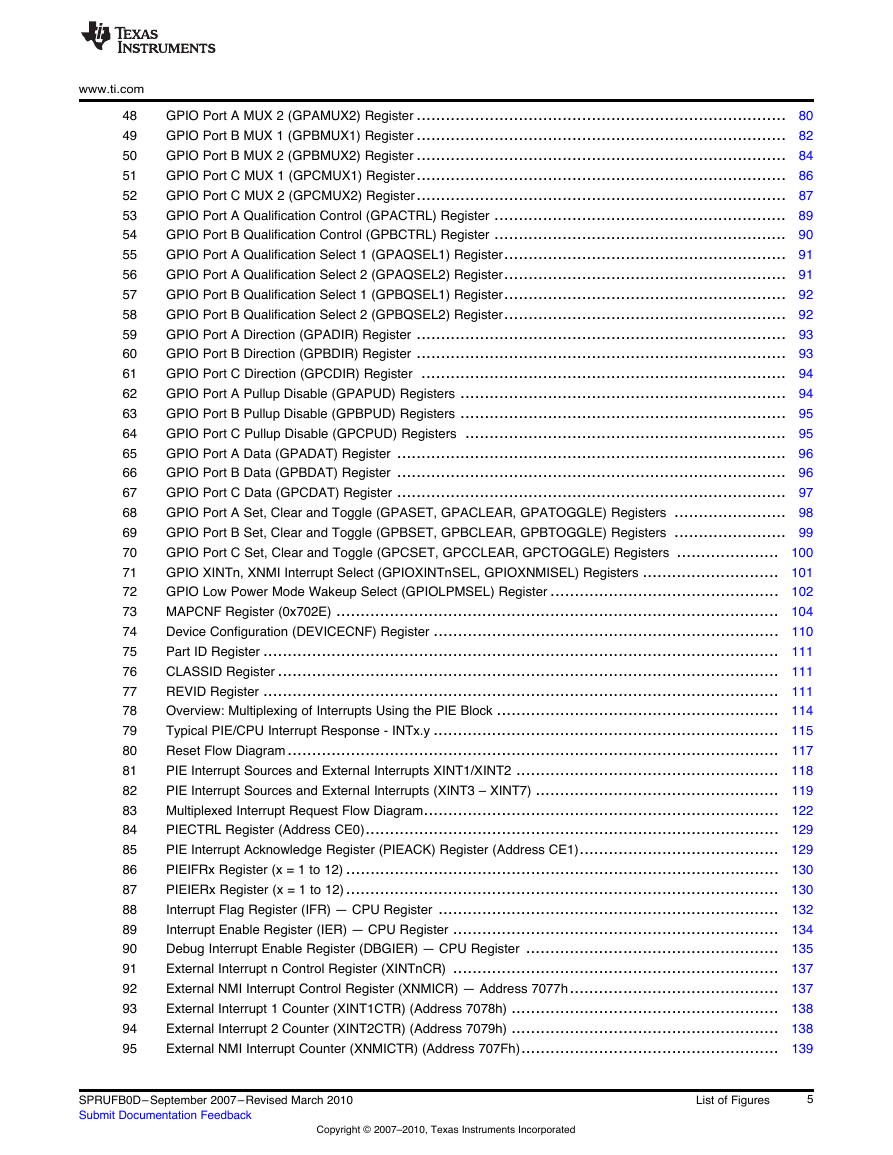

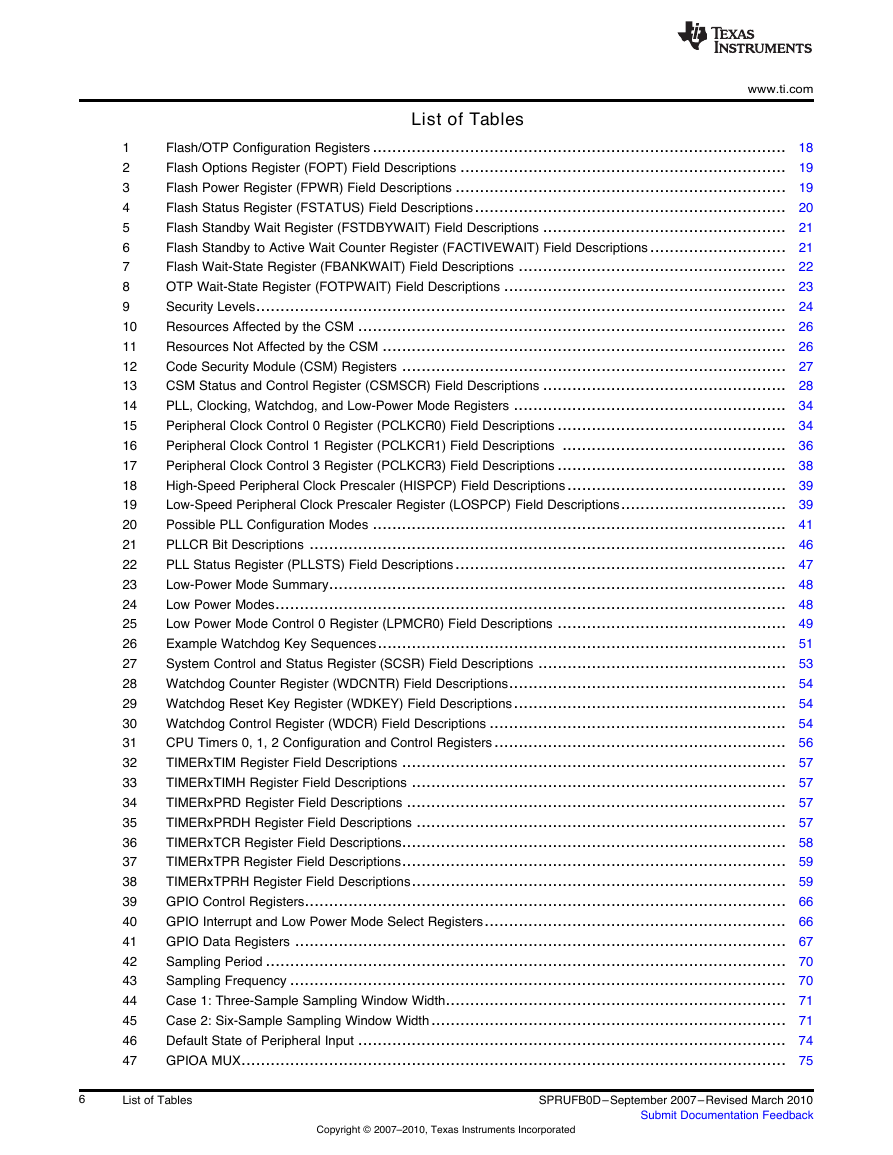

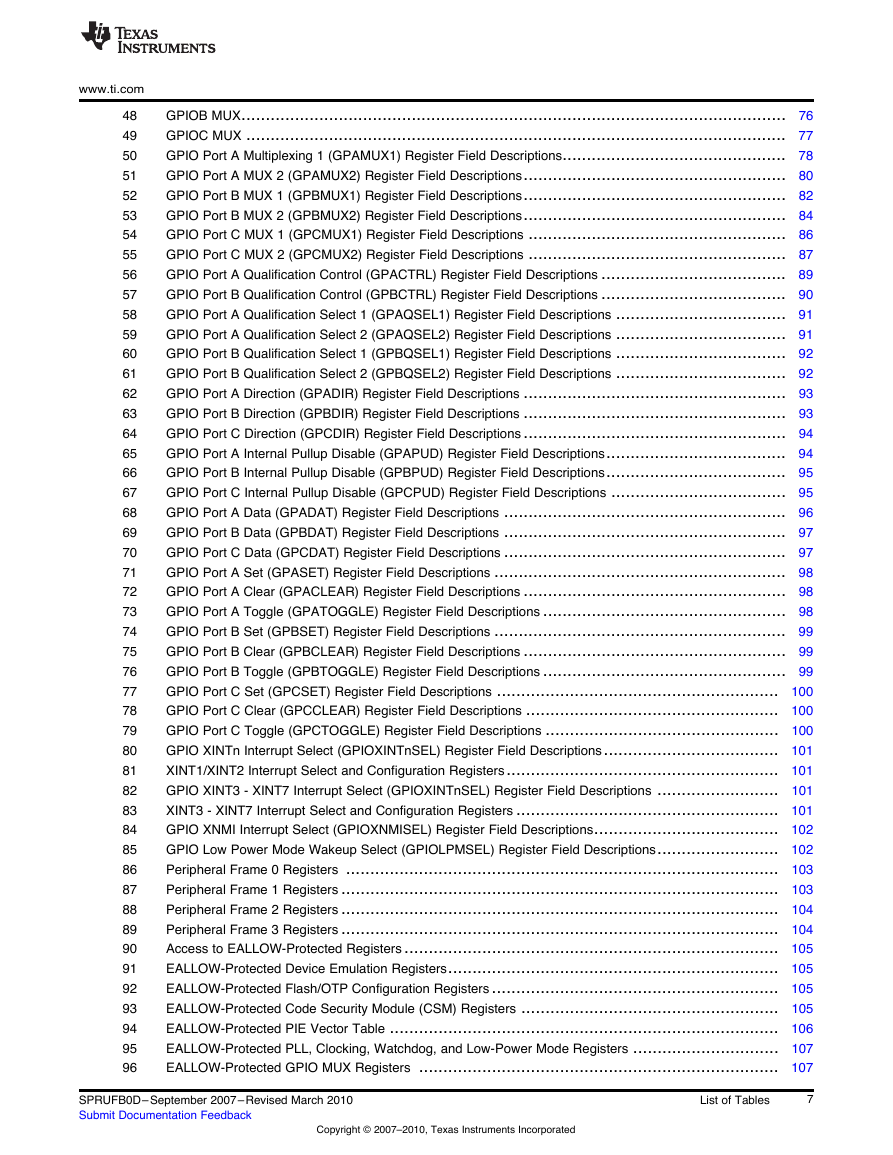

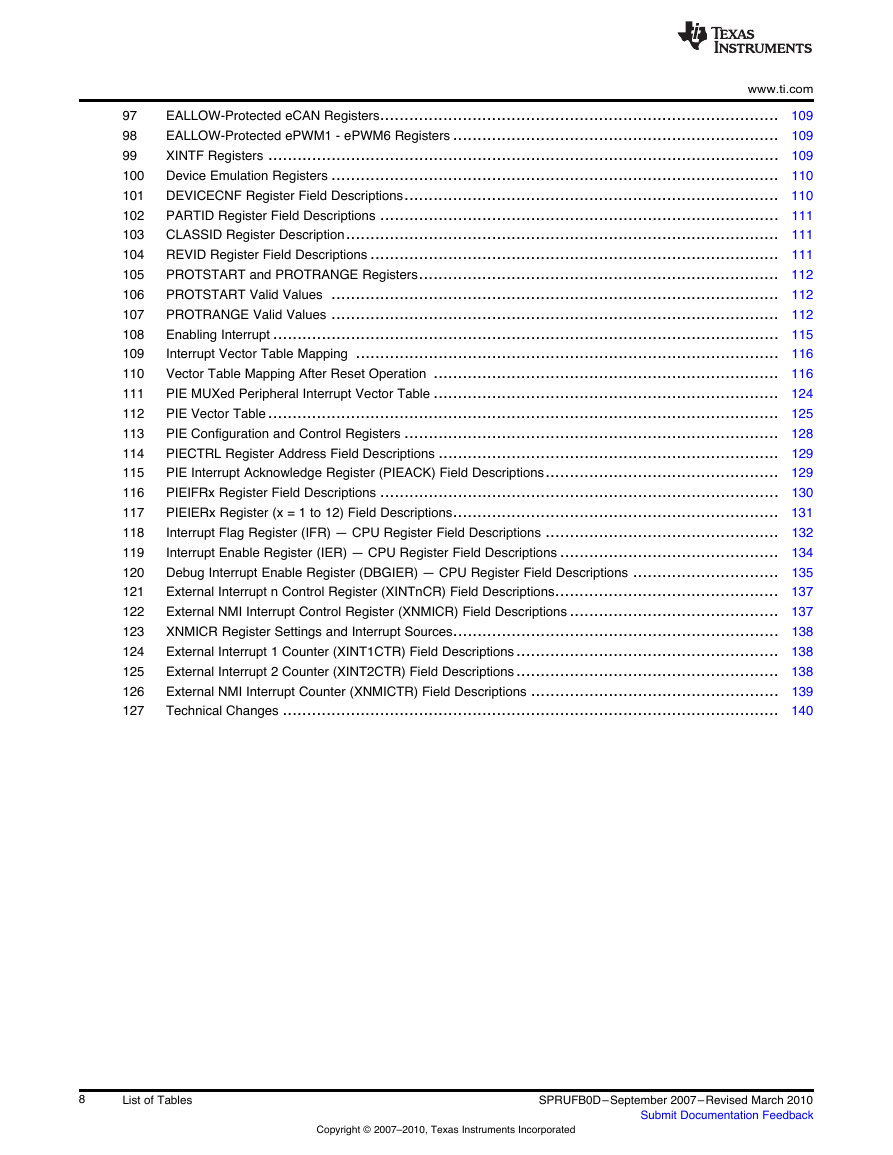

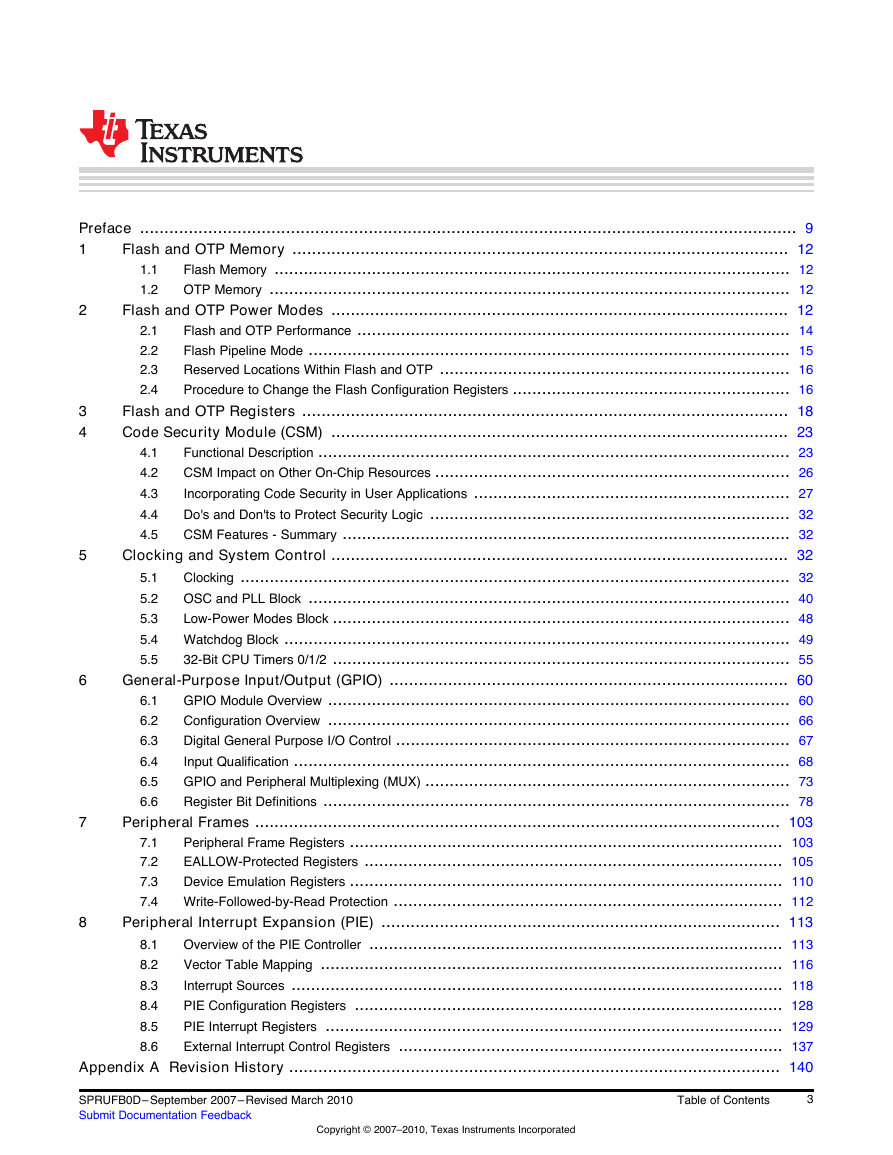

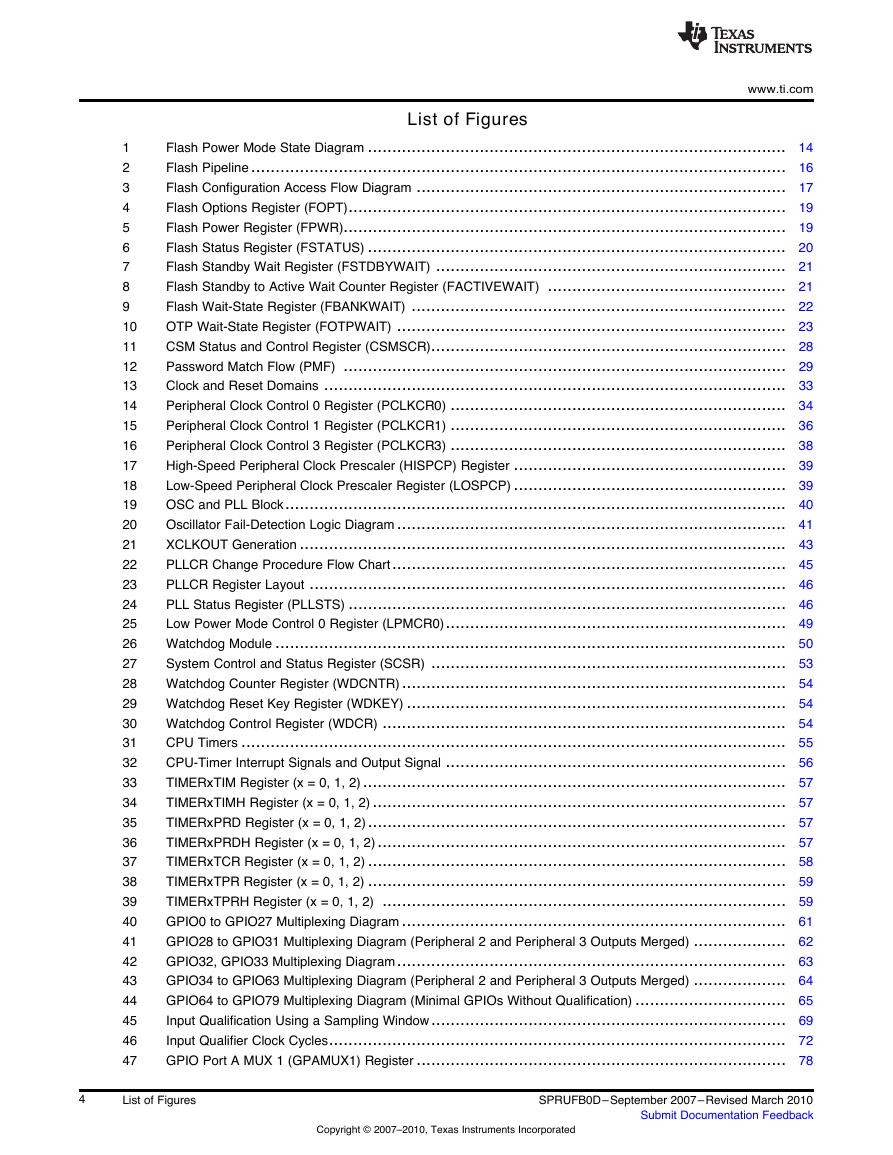

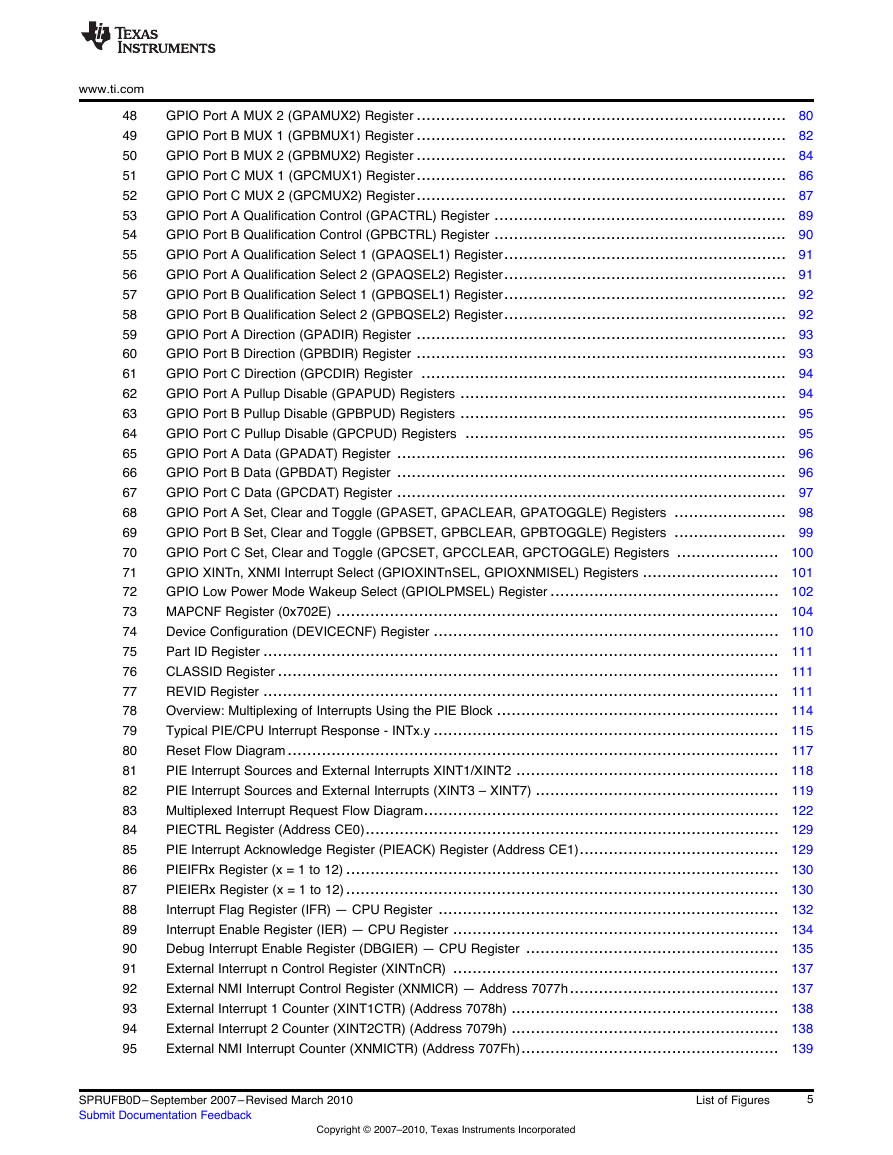

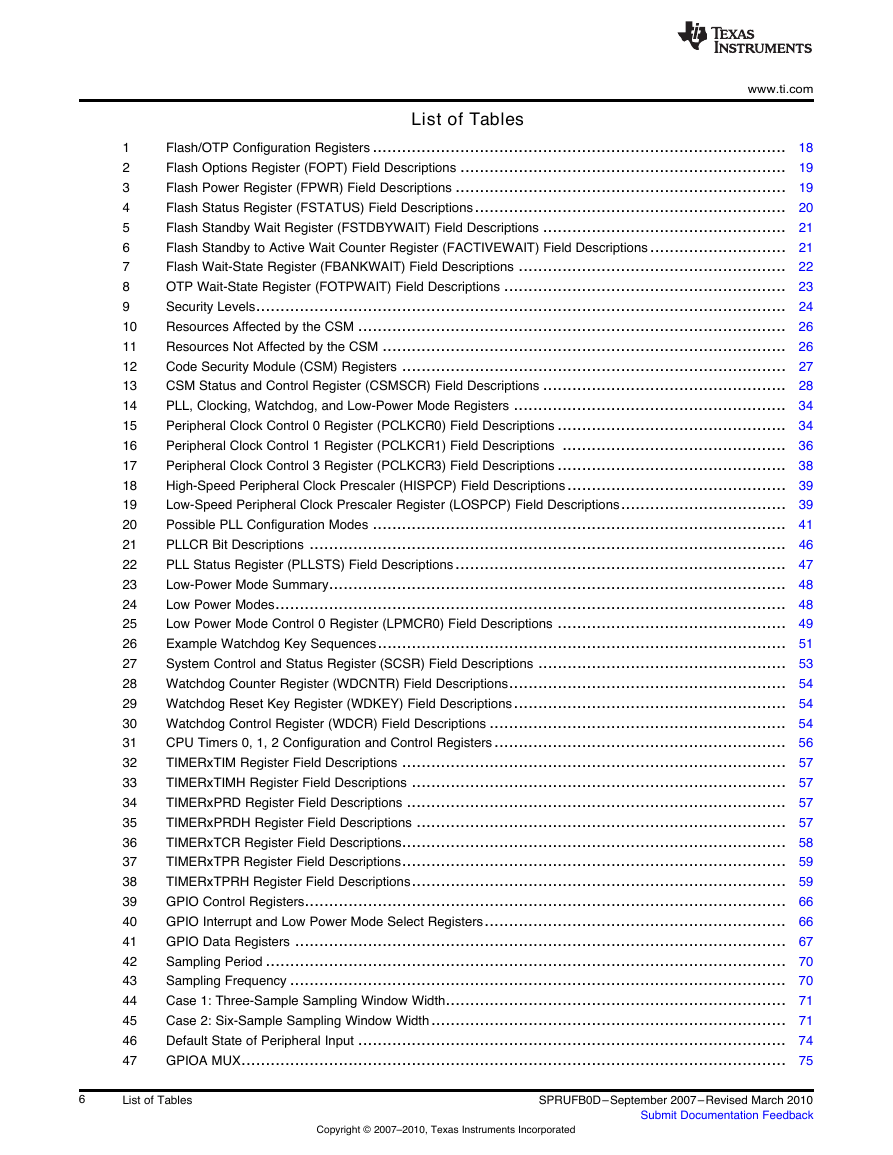

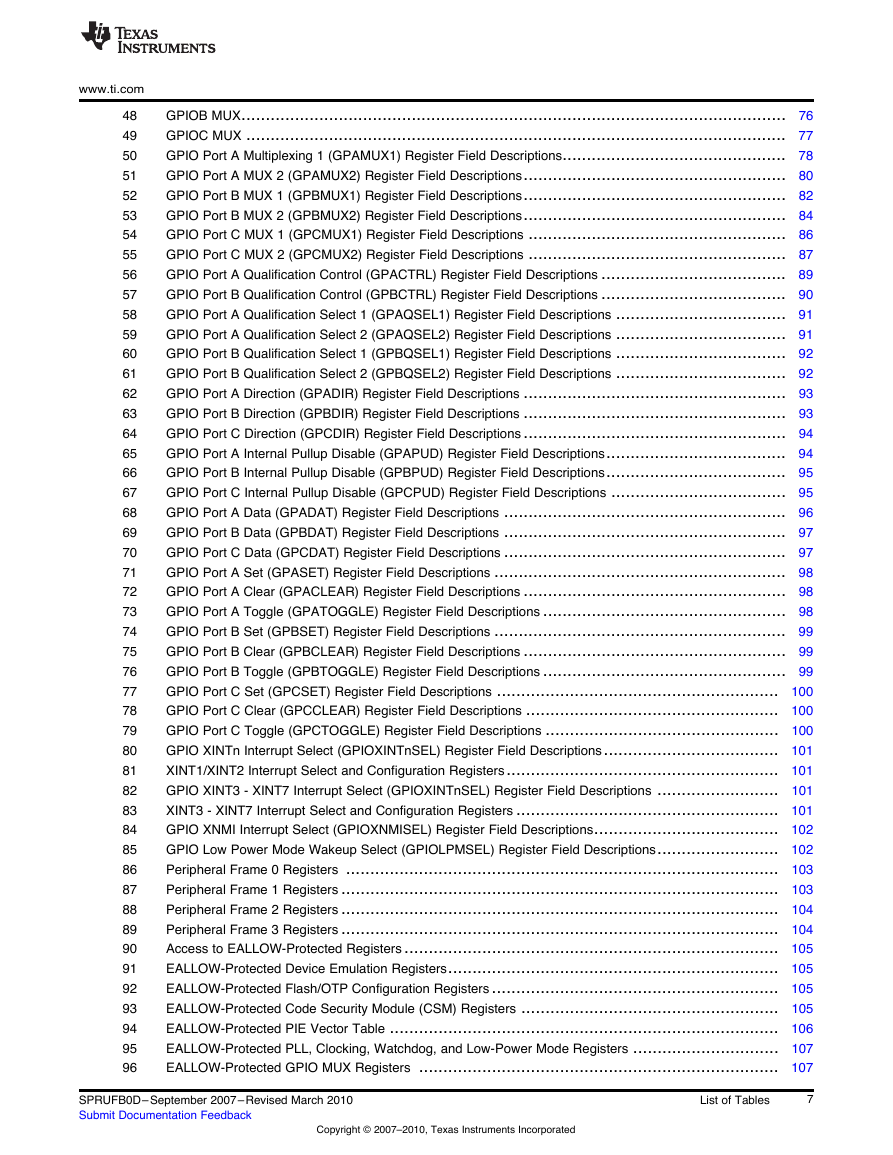

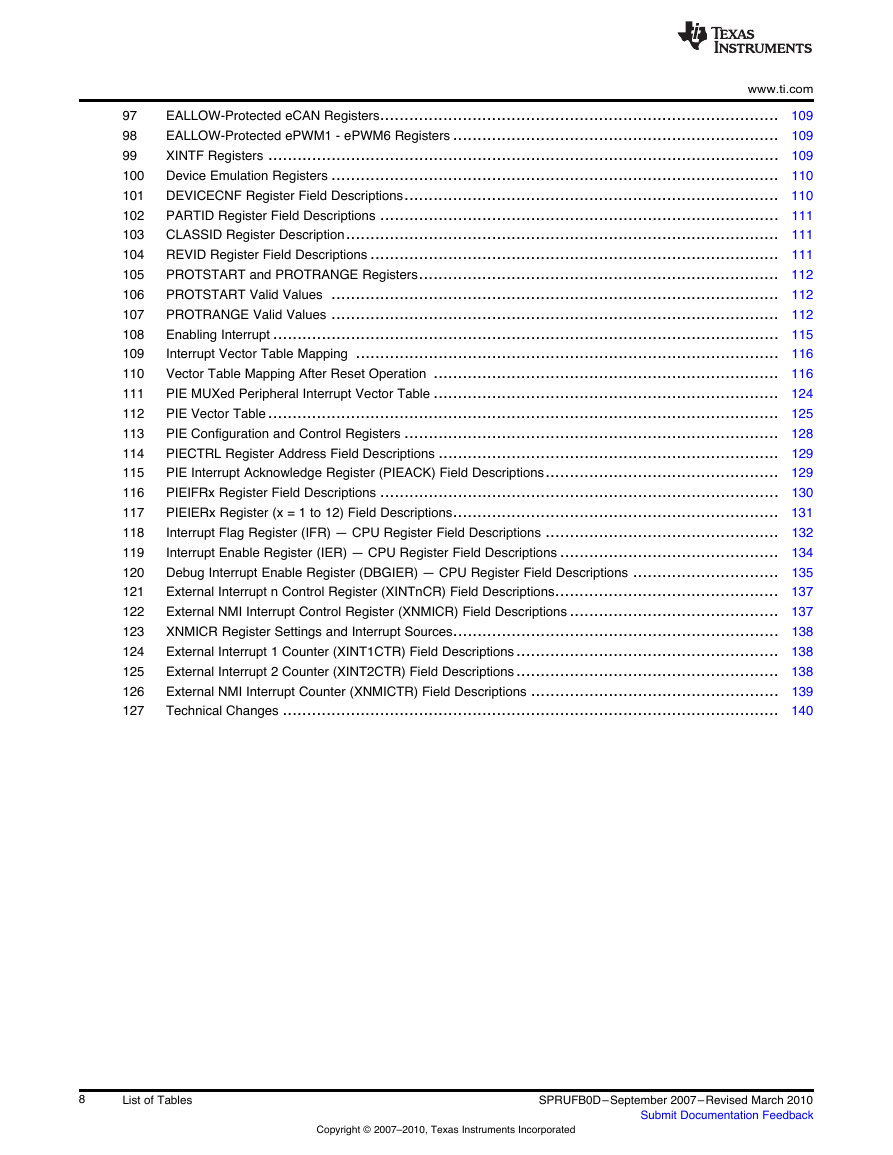

Table of Contents

Preface

1 Flash and OTP Memory

1.1 Flash Memory

1.2 OTP Memory

2 Flash and OTP Power Modes

2.1 Flash and OTP Performance

2.2 Flash Pipeline Mode

2.3 Reserved Locations Within Flash and OTP

2.4 Procedure to Change the Flash Configuration Registers

3 Flash and OTP Registers

4 Code Security Module (CSM)

4.1 Functional Description

4.2 CSM Impact on Other On-Chip Resources

4.3 Incorporating Code Security in User Applications

4.3.1 Environments That Require Security Unlocking

4.3.2 Password Match Flow

4.3.3 Unsecuring Considerations for Devices With/Without Code Security

4.3.3.1 C Code Example to Unsecure

4.3.3.2 C Code Example to Resecure

4.4 Do's and Don'ts to Protect Security Logic

4.4.1 Do's

4.4.2 Don'ts

4.5 CSM Features - Summary

5 Clocking and System Control

5.1 Clocking

5.1.1 Enabling/Disabling Clocks to the Peripheral Modules

5.2 OSC and PLL Block

5.2.1 PLL-Based Clock Module

5.2.2 Main Oscillator Fail Detection

5.2.3 XCLKOUT Generation

5.2.4 PLL Control (PLLCR) Register

5.2.5 PLL Control, Status and XCLKOUT Register Descriptions

5.2.6 External Reference Oscillator Clock Option

5.3 Low-Power Modes Block

5.4 Watchdog Block

5.4.1 Servicing The Watchdog Timer

5.4.2 Watchdog Reset or Watchdog Interrupt Mode

5.4.3 Watchdog Operation in Low Power Modes

5.4.4 Emulation Considerations

5.4.5 Watchdog Registers

5.5 32-Bit CPU Timers 0/1/2

6 General-Purpose Input/Output (GPIO)

6.1 GPIO Module Overview

6.2 Configuration Overview

6.3 Digital General Purpose I/O Control

6.4 Input Qualification

6.4.1 No Synchronization (asynchronous input)

6.4.2 Synchronization to SYSCLKOUT Only

6.4.3 Qualification Using a Sampling Window

6.5 GPIO and Peripheral Multiplexing (MUX)

6.6 Register Bit Definitions

7 Peripheral Frames

7.1 Peripheral Frame Registers

7.2 EALLOW-Protected Registers

7.3 Device Emulation Registers

7.4 Write-Followed-by-Read Protection

8 Peripheral Interrupt Expansion (PIE)

8.1 Overview of the PIE Controller

8.1.1 Interrupt Operation Sequence

8.2 Vector Table Mapping

8.3 Interrupt Sources

8.3.1 Procedure for Handling Multiplexed Interrupts

8.3.2 Procedures for Enabling And Disabling Multiplexed Peripheral Interrupts

8.3.3 Flow of a Multiplexed Interrupt Request From a Peripheral to the CPU

8.3.4 The PIE Vector Table

8.4 PIE Configuration Registers

8.5 PIE Interrupt Registers

8.5.1 PIE Interrupt Flag Registers

8.5.2 PIE Interrupt Enable Registers

8.5.3 CPU Interrupt Flag Register (IFR)

8.5.4 Interrupt Enable Register (IER) and Debug Interrupt Enable Register (DBGIER)

8.6 External Interrupt Control Registers

Appendix A Revision History

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc