1. 试从速度、容量、价格三个角度比较 cache、主存、硬盘。

答: 按照 cache→主存→硬盘的顺序

速度越来越慢、容量越来越大、价格越来越便宜

2. 说明 cache、主存、辅存三者的作用(即其中存放什么信息)。

答:Cache:存放 CPU 在当前一小段时间内多次使用的程序和数据。

主存:主要存放 CPU 当前使用的程序和数据。

辅存:存放大量的后备程序和数据。

3. 简述随机存取的两点含义。

答:①可按地址访问存储器中的任一单元;②访问时间与单元地址无关。

4. 简述存取时间和存取周期的定义。

答:存取时间:从存储器收到读/写申请命令,到从存储器取出/写入信息所需的时间。

存取周期:存储器作连续访问操作过程中一次完整的存取操作所需的全部时间。

5. 磁带、主存、硬盘、光盘四种存储器分属于随机存取存储器、顺序存取存储器、直接存

取存储器中的哪一类?

答:主存属于随机存取存储器;

磁带属于顺序存取存储器;

硬盘、光盘属于直接存取存储器。

6. 引入 cache 的目的是什么?引入虚拟存储器的目的是什么?

答:引入 cache 的目的是为了匹配 CPU 与主存之间的速度差异。

引入虚拟存储器的目的是为了扩大存储器的容量。

RAM 区:5KB

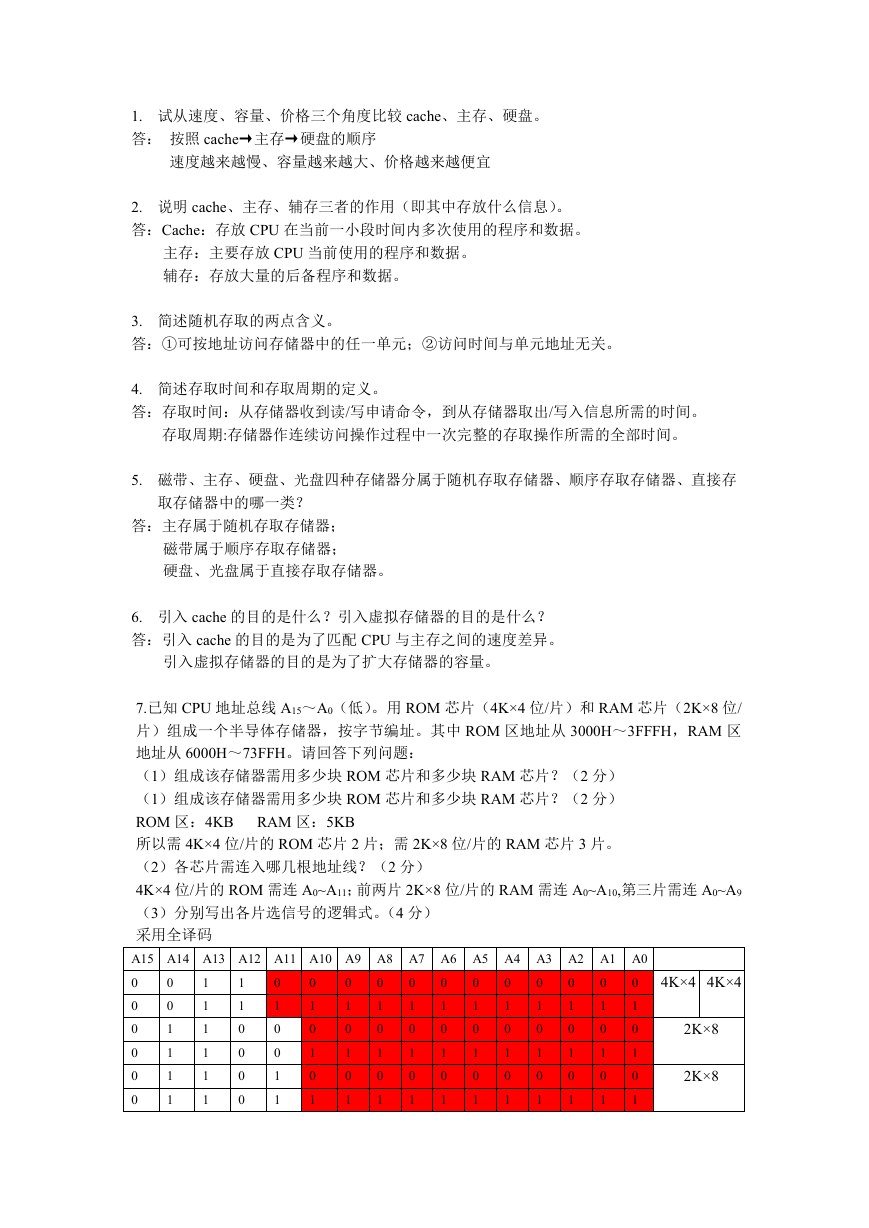

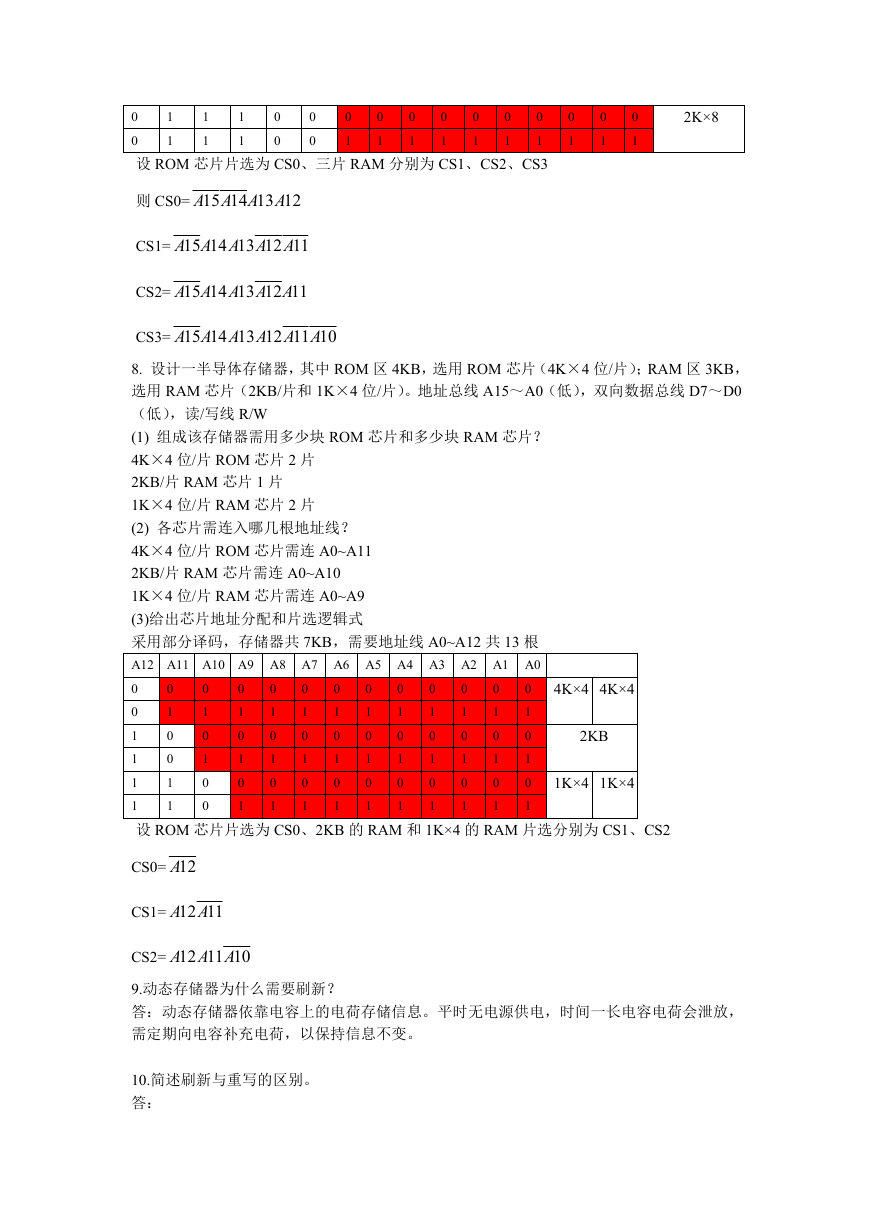

7.已知 CPU 地址总线 A15~A0(低)。用 ROM 芯片(4K×4 位/片)和 RAM 芯片(2K×8 位/

片)组成一个半导体存储器,按字节编址。其中 ROM 区地址从 3000H~3FFFH,RAM 区

地址从 6000H~73FFH。请回答下列问题:

(1)组成该存储器需用多少块 ROM 芯片和多少块 RAM 芯片?(2 分)

(1)组成该存储器需用多少块 ROM 芯片和多少块 RAM 芯片?(2 分)

ROM 区:4KB

所以需 4K×4 位/片的 ROM 芯片 2 片;需 2K×8 位/片的 RAM 芯片 3 片。

(2)各芯片需连入哪几根地址线?(2 分)

4K×4 位/片的 ROM 需连 A0~A11;前两片 2K×8 位/片的 RAM 需连 A0~A10,第三片需连 A0~A9

(3)分别写出各片选信号的逻辑式。(4 分)

采用全译码

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

0

0

0

0

0

0

4K×4 4K×4

2K×8

2K×8

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

0

1

0

1

0

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

�

1

1

1

1

0

0

0

1

设 ROM 芯片片选为 CS0、三片 RAM 分别为 CS1、CS2、CS3

1

1

0

0

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

2K×8

则 CS0=

15

AAAA

13

14

12

CS1=

CS2=

CS3=

15

AAAAA

12

13

14

11

15

12

AAAAA

13

14

11

15

11

AAAAAA

12

13

14

10

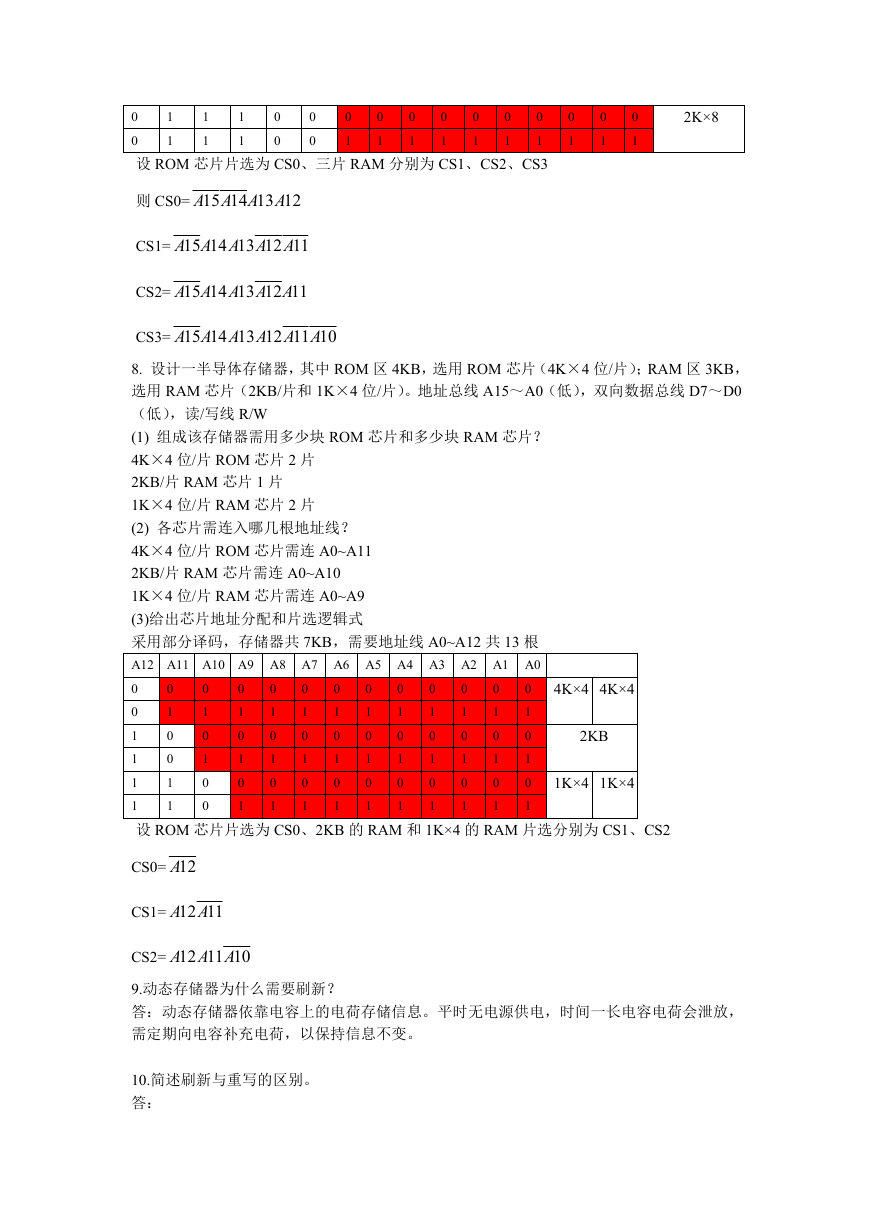

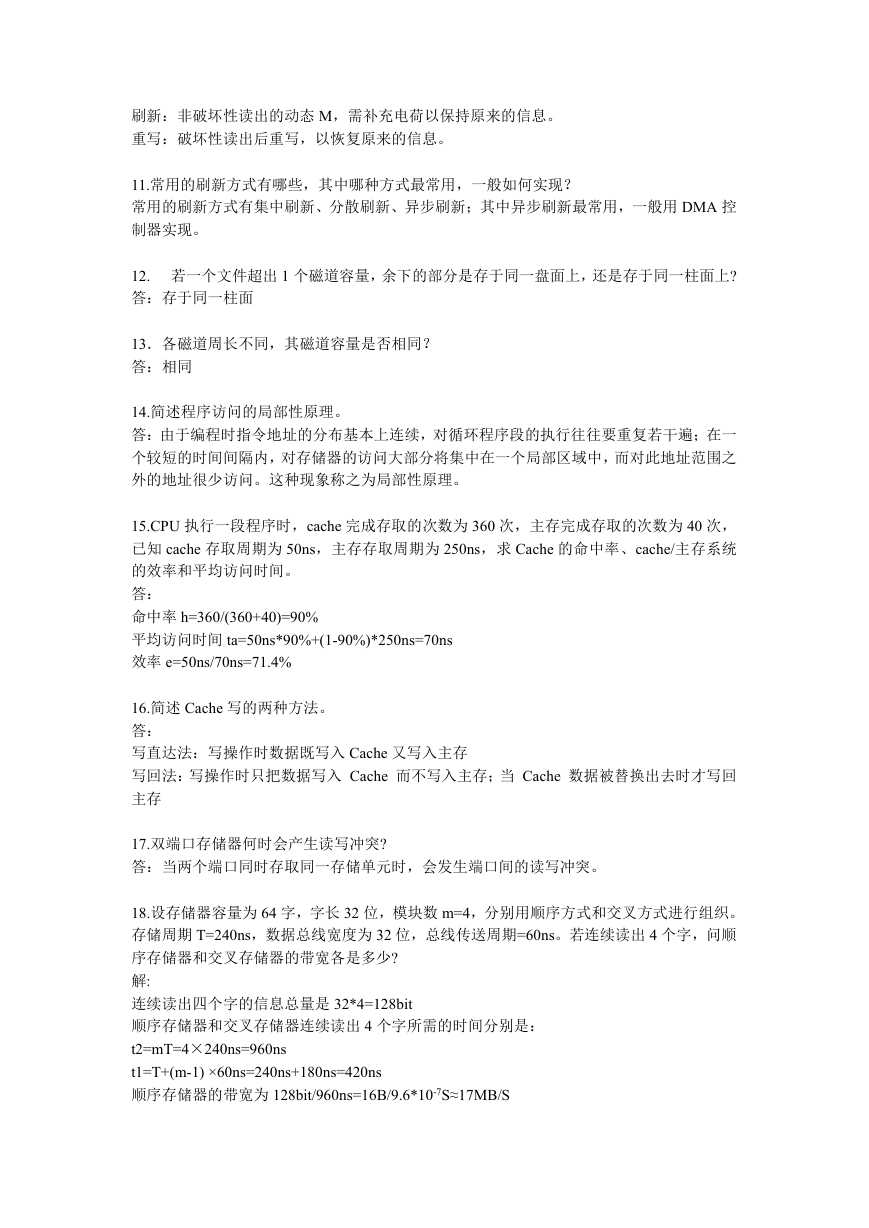

8. 设计一半导体存储器,其中 ROM 区 4KB,选用 ROM 芯片(4K×4 位/片);RAM 区 3KB,

选用 RAM 芯片(2KB/片和 1K×4 位/片)。地址总线 A15~A0(低),双向数据总线 D7~D0

(低),读/写线 R/W

(1) 组成该存储器需用多少块 ROM 芯片和多少块 RAM 芯片?

4K×4 位/片 ROM 芯片 2 片

2KB/片 RAM 芯片 1 片

1K×4 位/片 RAM 芯片 2 片

(2) 各芯片需连入哪几根地址线?

4K×4 位/片 ROM 芯片需连 A0~A11

2KB/片 RAM 芯片需连 A0~A10

1K×4 位/片 RAM 芯片需连 A0~A9

(3)给出芯片地址分配和片选逻辑式

采用部分译码,存储器共 7KB,需要地址线 A0~A12 共 13 根

A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

0

0

1

1

1

1

设 ROM 芯片片选为 CS0、2KB 的 RAM 和 1K×4 的 RAM 片选分别为 CS1、CS2

4K×4 4K×4

1K×4 1K×4

0

1

0

0

1

1

0

1

0

1

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

2KB

CS0= 12A

CS1=

12AA

11

CS2=

12

11

AAA

10

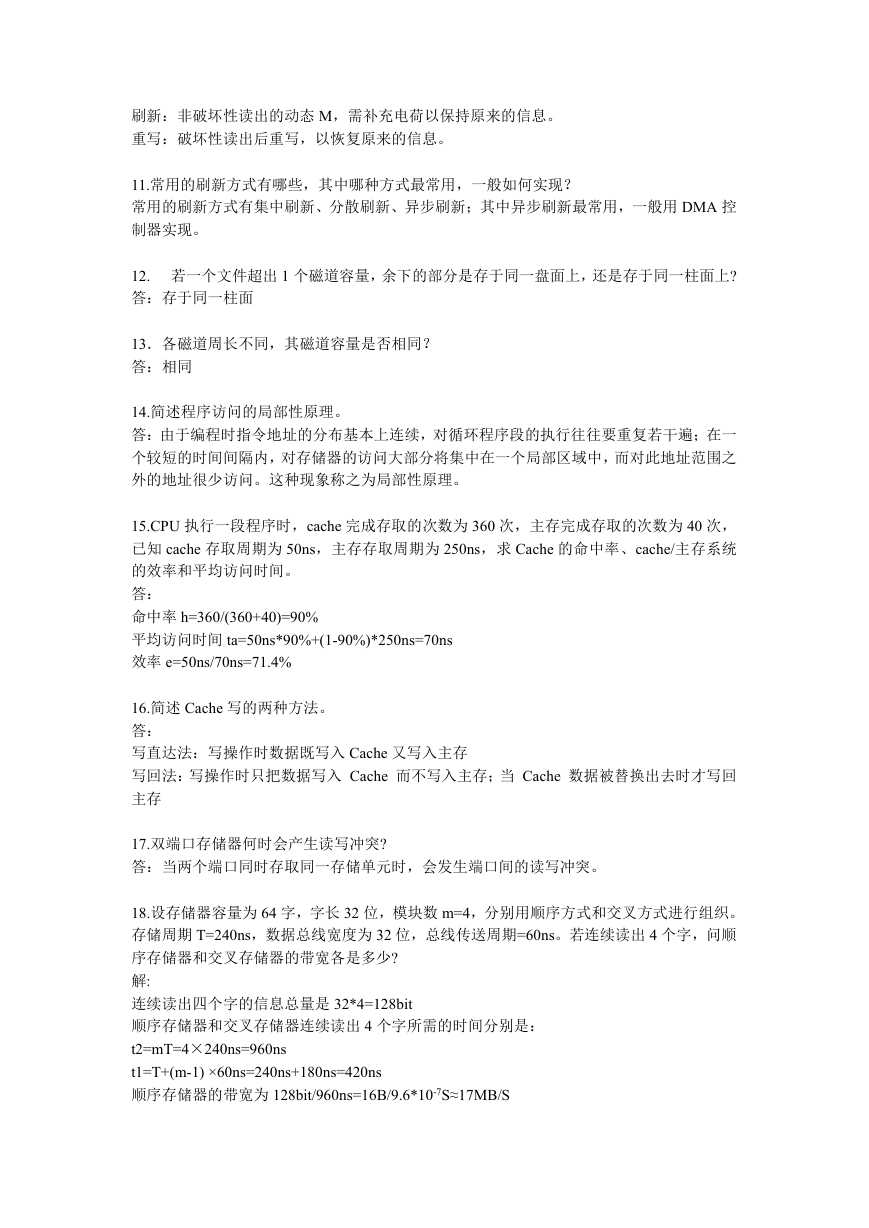

9.动态存储器为什么需要刷新?

答:动态存储器依靠电容上的电荷存储信息。平时无电源供电,时间一长电容电荷会泄放,

需定期向电容补充电荷,以保持信息不变。

10.简述刷新与重写的区别。

答:

�

刷新:非破坏性读出的动态 M,需补充电荷以保持原来的信息。

重写:破坏性读出后重写,以恢复原来的信息。

11.常用的刷新方式有哪些,其中哪种方式最常用,一般如何实现?

常用的刷新方式有集中刷新、分散刷新、异步刷新;其中异步刷新最常用,一般用 DMA 控

制器实现。

12. 若一个文件超出 1 个磁道容量,余下的部分是存于同一盘面上,还是存于同一柱面上?

答:存于同一柱面

13.各磁道周长不同,其磁道容量是否相同?

答:相同

14.简述程序访问的局部性原理。

答:由于编程时指令地址的分布基本上连续,对循环程序段的执行往往要重复若干遍;在一

个较短的时间间隔内,对存储器的访问大部分将集中在一个局部区域中,而对此地址范围之

外的地址很少访问。这种现象称之为局部性原理。

15.CPU 执行一段程序时,cache 完成存取的次数为 360 次,主存完成存取的次数为 40 次,

已知 cache 存取周期为 50ns,主存存取周期为 250ns,求 Cache 的命中率、cache/主存系统

的效率和平均访问时间。

答:

命中率 h=360/(360+40)=90%

平均访问时间 ta=50ns*90%+(1-90%)*250ns=70ns

效率 e=50ns/70ns=71.4%

16.简述 Cache 写的两种方法。

答:

写直达法:写操作时数据既写入 Cache 又写入主存

写回法:写操作时只把数据写入 Cache 而不写入主存;当 Cache 数据被替换出去时才写回

主存

17.双端口存储器何时会产生读写冲突?

答:当两个端口同时存取同一存储单元时,会发生端口间的读写冲突。

18.设存储器容量为 64 字,字长 32 位,模块数 m=4,分别用顺序方式和交叉方式进行组织。

存储周期 T=240ns,数据总线宽度为 32 位,总线传送周期=60ns。若连续读出 4 个字,问顺

序存储器和交叉存储器的带宽各是多少?

解:

连续读出四个字的信息总量是 32*4=128bit

顺序存储器和交叉存储器连续读出 4 个字所需的时间分别是:

t2=mT=4×240ns=960ns

t1=T+(m-1) ×60ns=240ns+180ns=420ns

顺序存储器的带宽为 128bit/960ns=16B/9.6*10-7S≈17MB/S

�

交叉存储器的带宽为 128bit/420ns=16B/4.2*10-7S≈38MB/S

19.相联存储器与一般存储器的显著区别在于哪里?

答:一般存储器是按地址访问存储器的,而相联存储器是按内容寻址的存储器。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc