2016 年广西桂林电子科技大学通信电子电路及 EDA 技术考

研真题 A 卷

通信电子电路

一、填空题(每空1分,共14分)

1. 理想的LC谐振回路的矩形系数是

,单LC谐振回路的矩形系数是

。

2. 设丙类高频功放开始工作于临界工作状态,则:单独增大集电极直流电源电压Ec(其他

参数不变)时,功放将进入

工作状态;单独增大负载R(其他参数不变)时,功

放将进入

工作状态。

3. 振幅平衡条件是环路增益 (

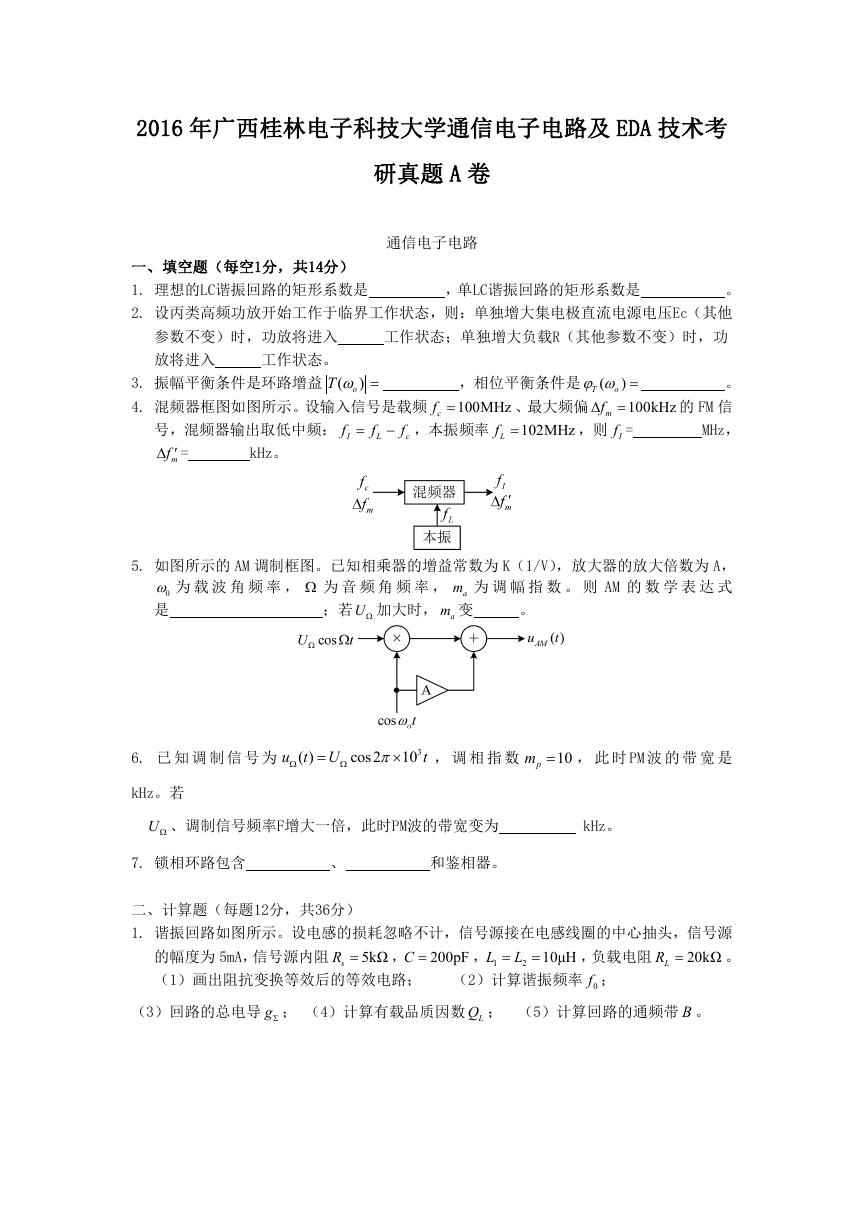

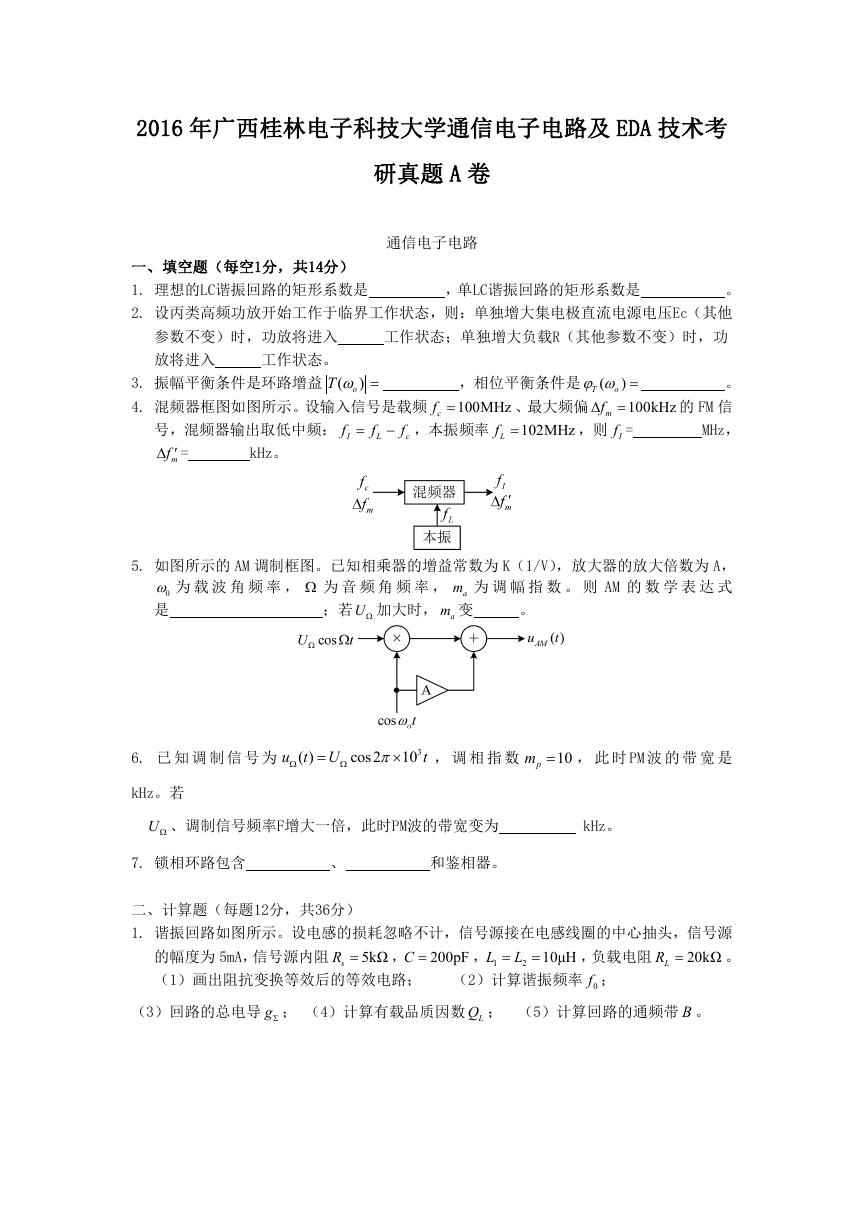

4. 混频器框图如图所示。设输入信号是载频 100MHz

Lf

,本振频率

)

,相位平衡条件是 (

o

T

mf

,则 If =

、最大频偏

102MHz

)oT

cf

f

c

f

L

f

号,混频器输出取低中频: I

mf =

kHz。

100kHz

。

的 FM 信

MHz,

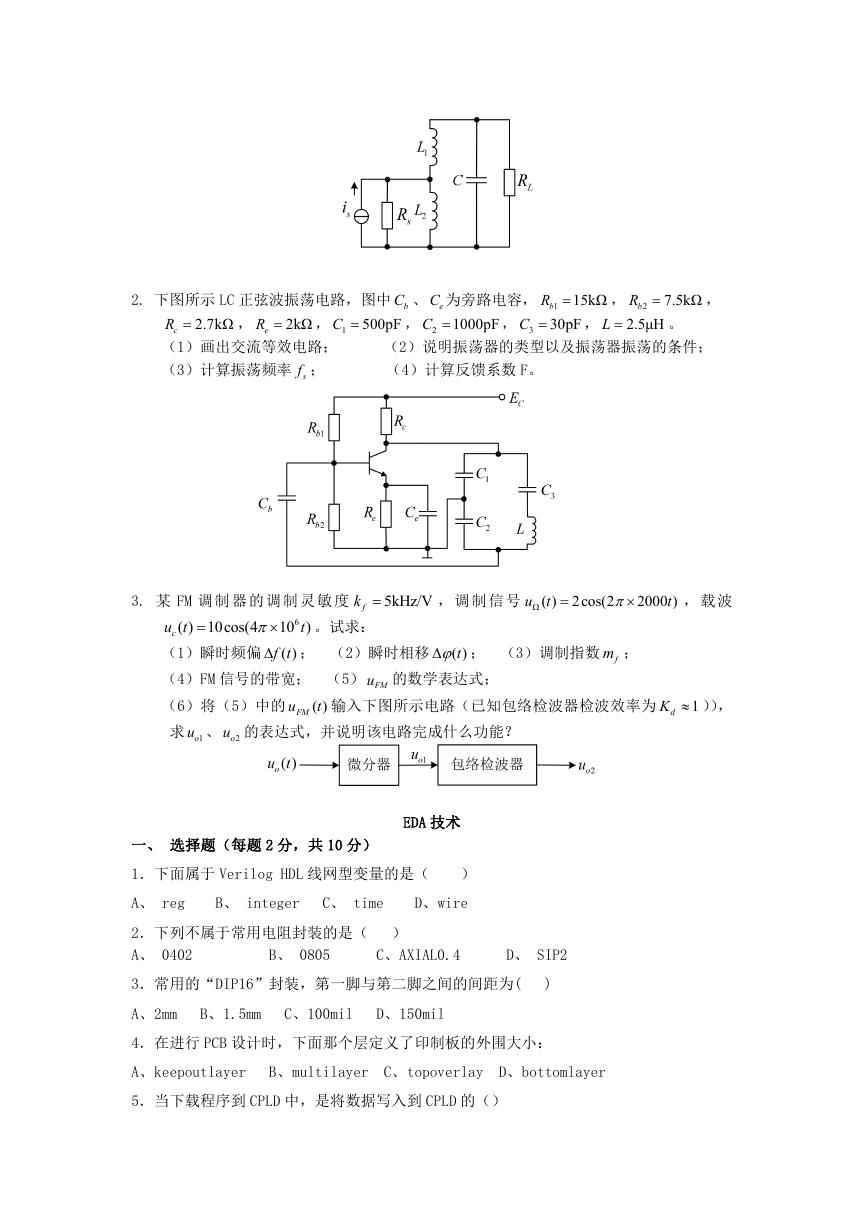

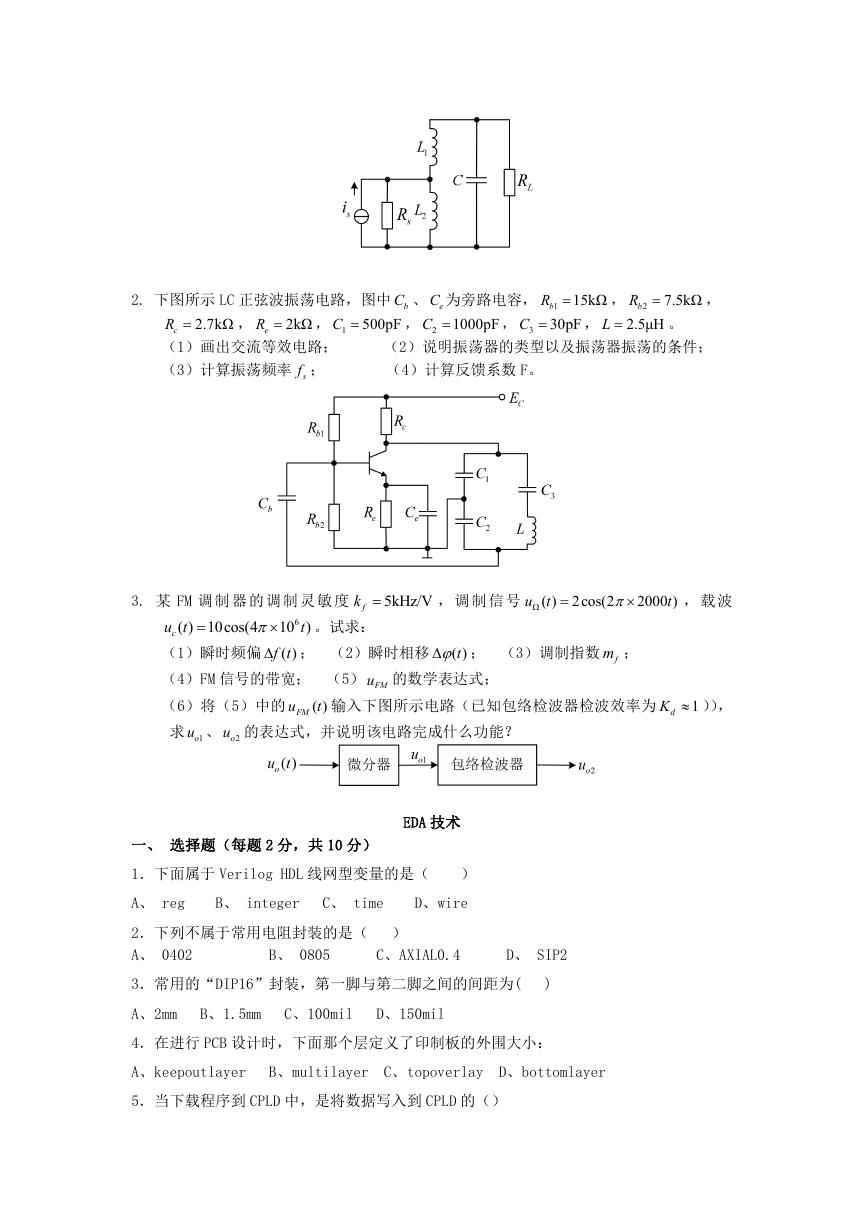

5. 如图所示的 AM 调制框图。已知相乘器的增益常数为 K(1/V),放大器的放大倍数为 A,

0 为 载 波 角 频 率 , 为 音 频 角 频 率 , am 为 调 幅 指 数 。 则 AM 的 数 学 表 达 式

是

;若U 加大时, am 变

。

6. 已 知 调 制 信 号 为

u t U

( )

cos2

3

10

t

, 调 相 指 数

10pm

, 此 时 PM 波 的 带 宽 是

kHz。若

U 、调制信号频率F增大一倍,此时PM波的带宽变为

kHz。

7. 锁相环路包含

、

和鉴相器。

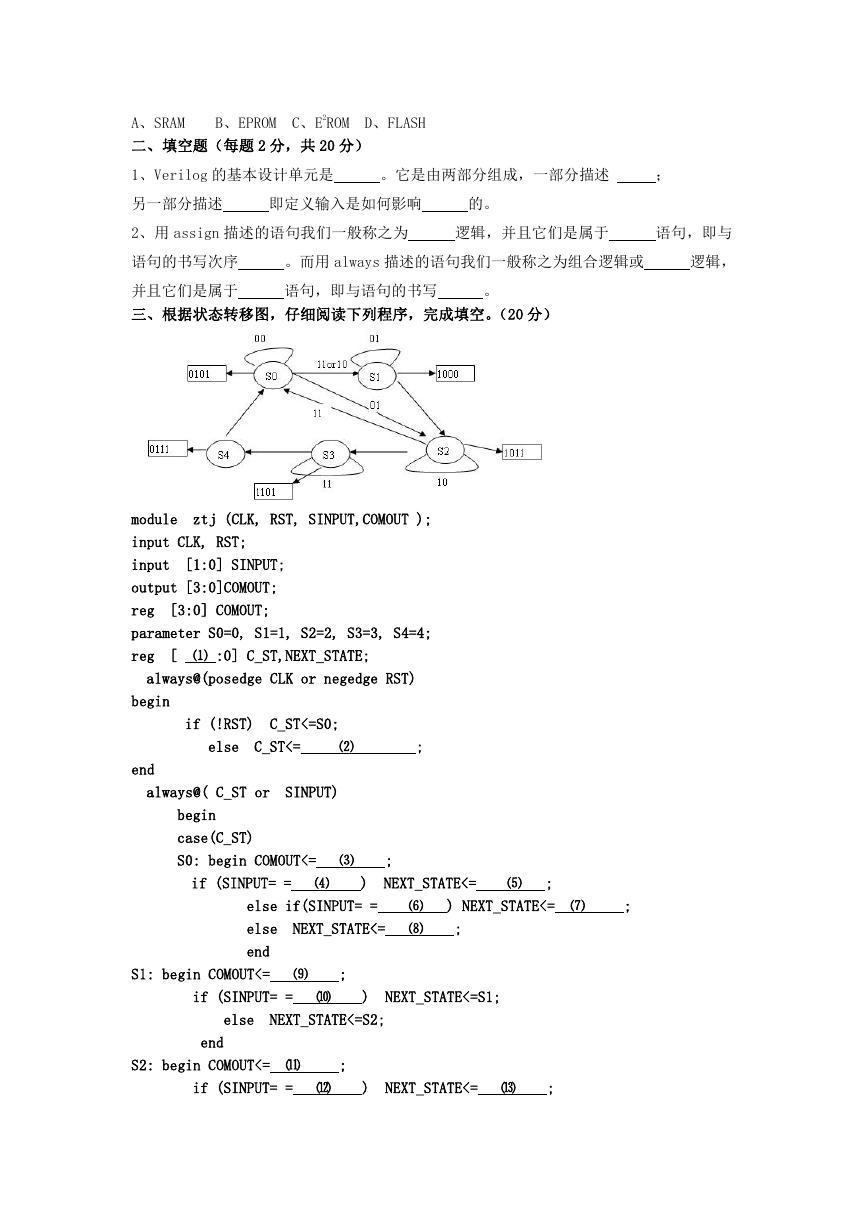

二、计算题(每题12分,共36分)

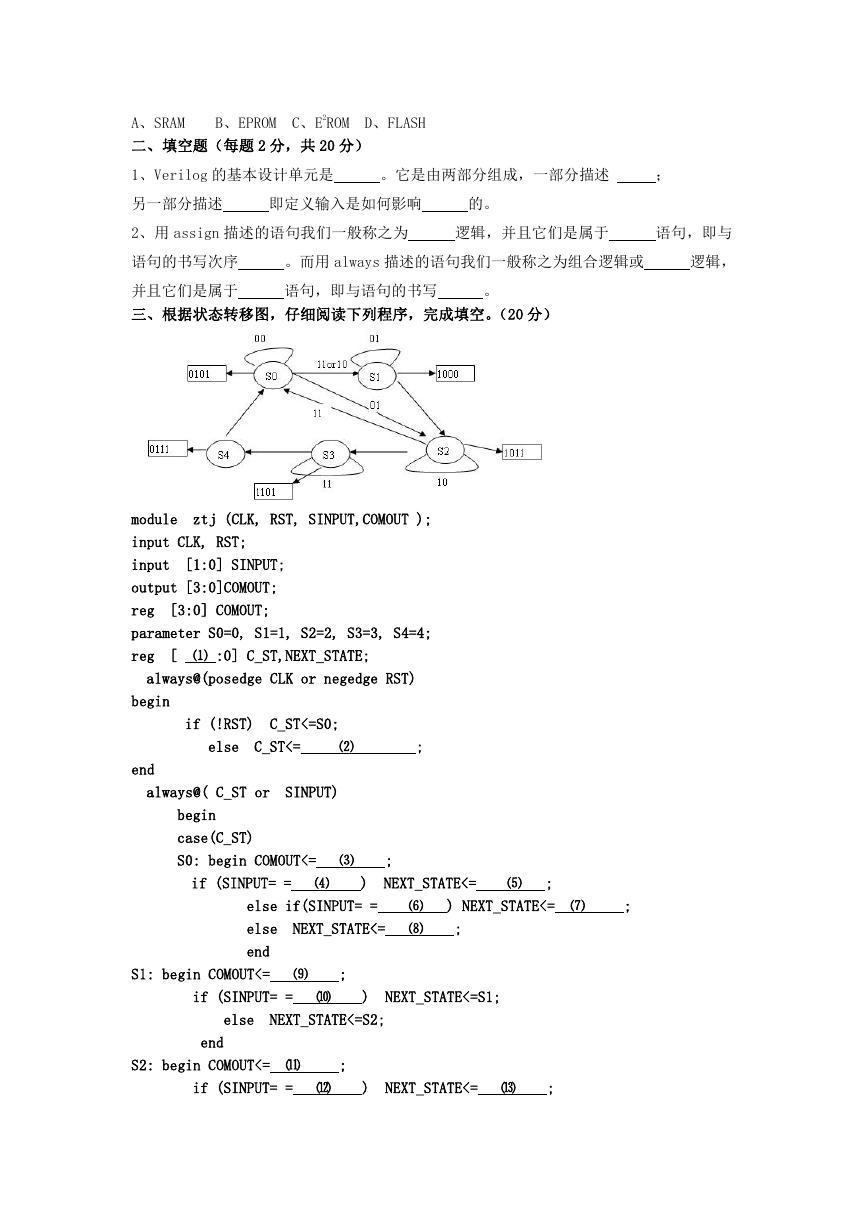

1. 谐振回路如图所示。设电感的损耗忽略不计,信号源接在电感线圈的中心抽头,信号源

的幅度为 5mA,信号源内阻

C

(1)画出阻抗变换等效后的等效电路;

sR

5kΩ

, 200pF

L

, 1

L

2

10μH

,负载电阻

LR

20kΩ

。

(2)计算谐振频率 0f ;

(3)回路的总电导 g ; (4)计算有载品质因数 LQ ; (5)计算回路的通频带 B 。

�

2. 下图所示 LC 正弦波振荡电路,图中 bC 、 eC 为旁路电容, 1 15kΩ

500pF

, 2

C

1000pF

, 3

C

bR

30pF

bR

, 2.5μH

, 2

L

,

7.5kΩ

。

,

2kΩ

eR

2.7kΩ

cR

, 1

(1)画出交流等效电路;

(3)计算振荡频率 sf ;

C

(2)说明振荡器的类型以及振荡器振荡的条件;

(4)计算反馈系数 F。

5kHz/V

, 调 制 信 号 ( )

u t

2cos(2

2000 )

t

, 载 波

3. 某 FM 调 制 器 的 调 制 灵 敏 度

fk

。试求:

6

10 )

t

( ) 10cos(4

t ; (2)瞬时相移 ( )t ; (3)调制指数 fm ;

f

cu t

(1)瞬时频偏 ( )

(4)FM 信号的带宽; (5) FMu 的数学表达式;

(6)将(5)中的 ( )

求 1ou 、 2ou 的表达式,并说明该电路完成什么功能?

t 输入下图所示电路(已知包络检波器检波效率为

FMu

dK )),

1

EDA 技术

一、 选择题(每题 2 分,共 10 分)

1.下面属于 Verilog HDL 线网型变量的是(

)

A、 reg

B、 integer

C、 time

D、wire

2.下列不属于常用电阻封装的是( )

A、 0402

B、 0805

C、AXIAL0.4

D、 SIP2

3.常用的“DIP16”封装,第一脚与第二脚之间的间距为(

)

A、2mm

B、1.5mm

C、100mil

D、150mil

4.在进行 PCB 设计时,下面那个层定义了印制板的外围大小:

A、keepoutlayer

B、multilayer

C、topoverlay

D、bottomlayer

5.当下载程序到 CPLD 中,是将数据写入到 CPLD 的()

�

A、SRAM

二、填空题(每题 2 分,共 20 分)

B、EPROM

C、E2ROM

D、FLASH

1、Verilog 的基本设计单元是

。它是由两部分组成,一部分描述

;

另一部分描述

即定义输入是如何影响

的。

2、用 assign 描述的语句我们一般称之为

逻辑,并且它们是属于

语句,即与

语句的书写次序

。而用 always 描述的语句我们一般称之为组合逻辑或

逻辑,

并且它们是属于

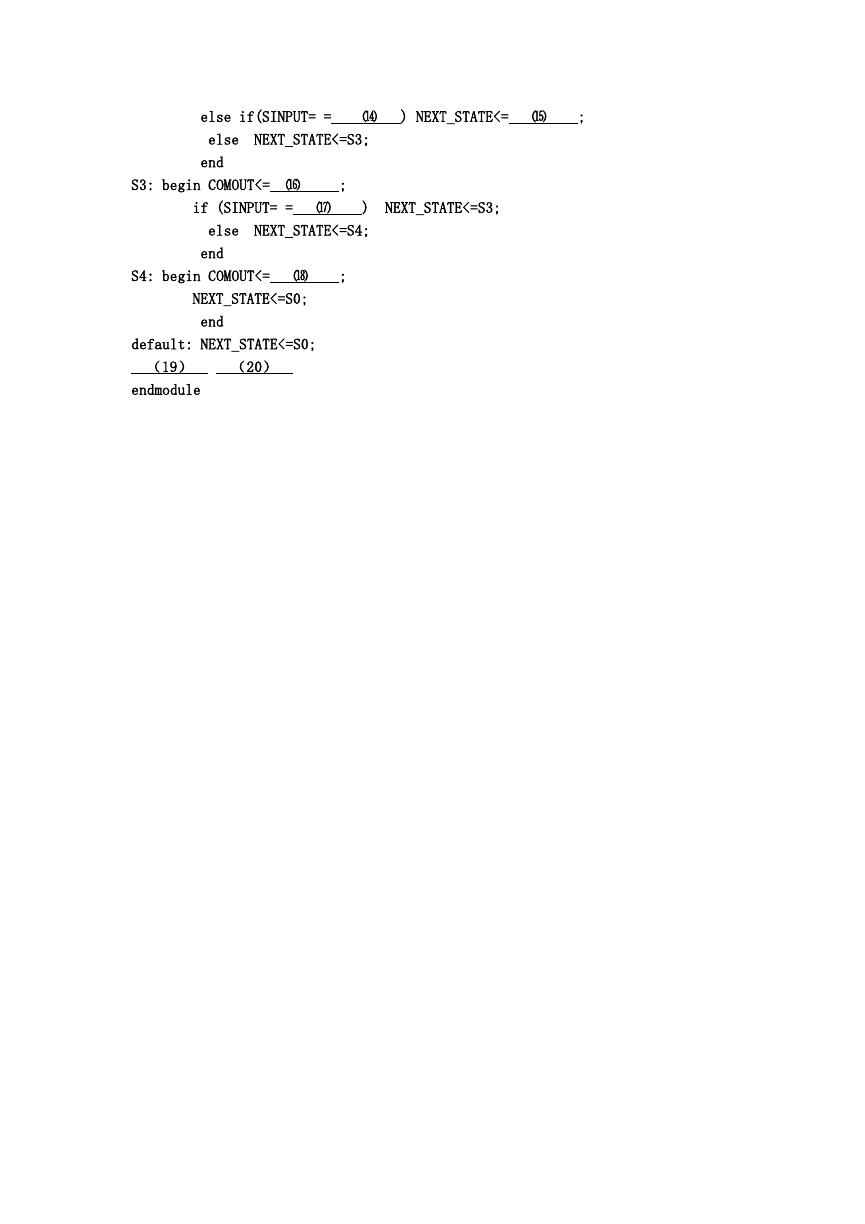

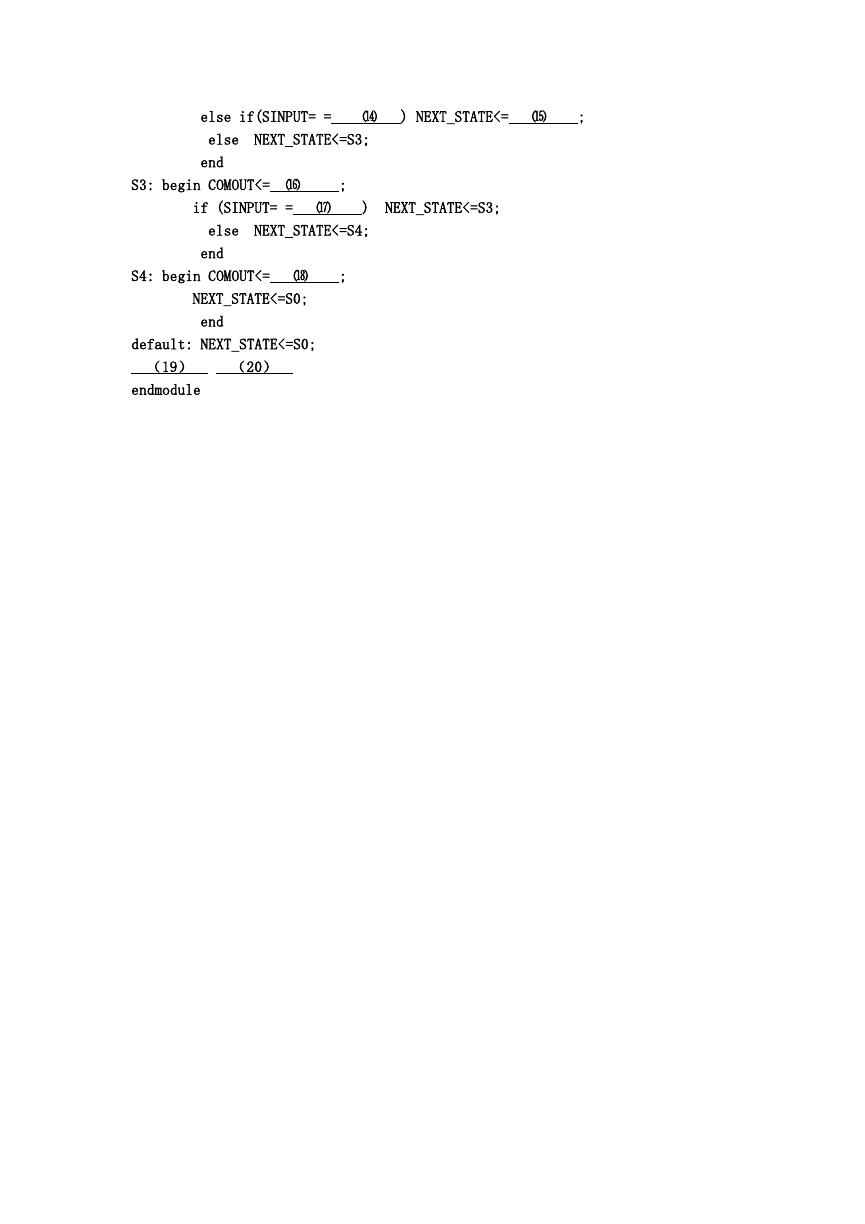

三、根据状态转移图,仔细阅读下列程序,完成填空。(20 分)

语句,即与语句的书写

。

ztj (CLK, RST, SINPUT,COMOUT );

module

input CLK, RST;

input

[1:0] SINPUT;

output [3:0]COMOUT;

reg

parameter S0=0, S1=1, S2=2, S3=3, S4=4;

reg

[ ⑴ :0] C_ST,NEXT_STATE;

[3:0] COMOUT;

always@(posedge CLK or negedge RST)

begin

end

if (!RST)

C_ST<=S0;

else

C_ST<=

⑵

;

always@( C_ST or

SINPUT)

begin

case(C_ST)

S0: begin COMOUT<= ⑶

if (SINPUT= = ⑷

)

else if(SINPUT= =

else

end

;

NEXT_STATE<=

⑸ ;

⑹ ) NEXT_STATE<= ⑺

;

NEXT_STATE<= ⑻

;

S1: begin COMOUT<= ⑼

;

if (SINPUT= = ⑽

)

NEXT_STATE<=S1;

else

NEXT_STATE<=S2;

end

S2: begin COMOUT<= ⑾

;

if (SINPUT= = ⑿

)

NEXT_STATE<= ⒀

;

�

else if(SINPUT= =

⒁ ) NEXT_STATE<= ⒂

;

else

NEXT_STATE<=S3;

end

S3: begin COMOUT<= ⒃

;

if (SINPUT= = ⒄

)

NEXT_STATE<=S4;

else

end

NEXT_STATE<=S3;

S4: begin COMOUT<= ⒅

NEXT_STATE<=S0;

;

end

default: NEXT_STATE<=S0;

(19)

(20)

endmodule

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc