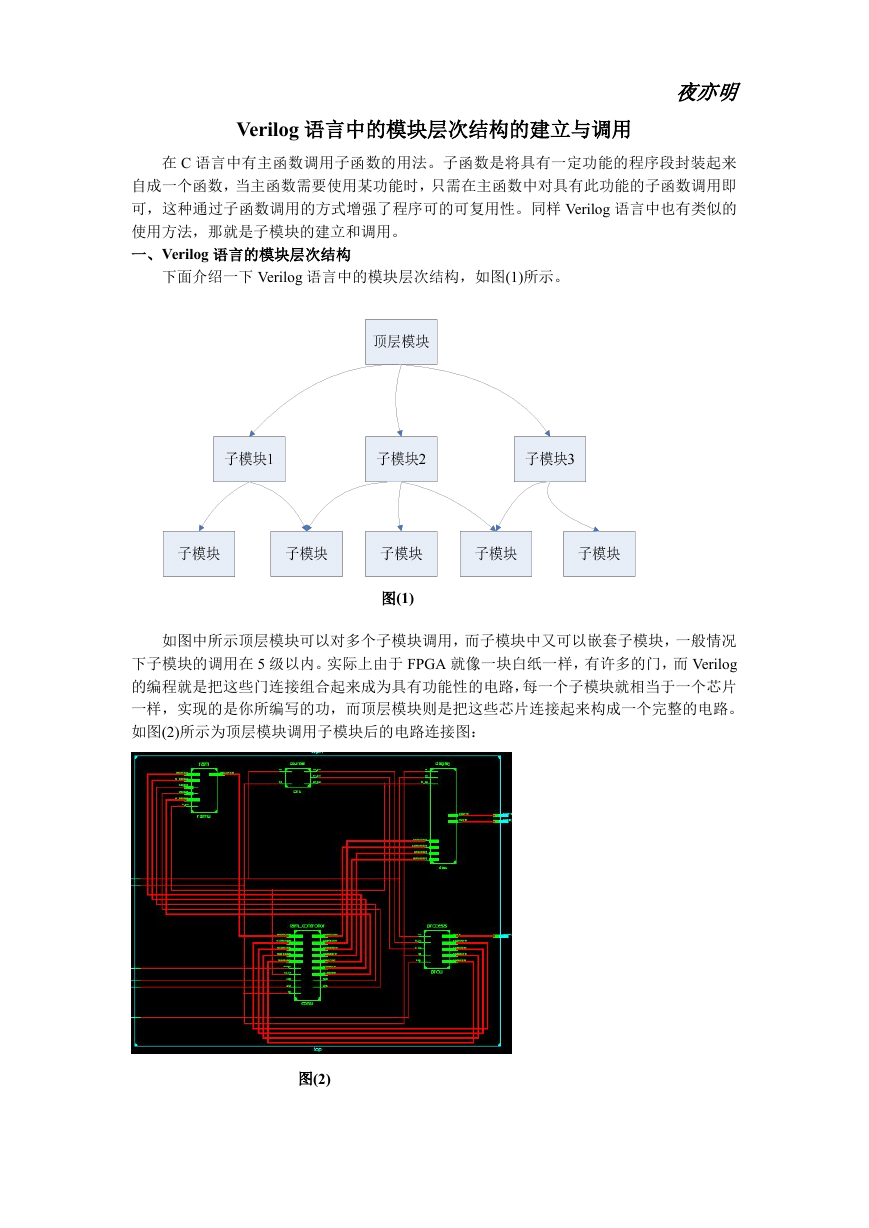

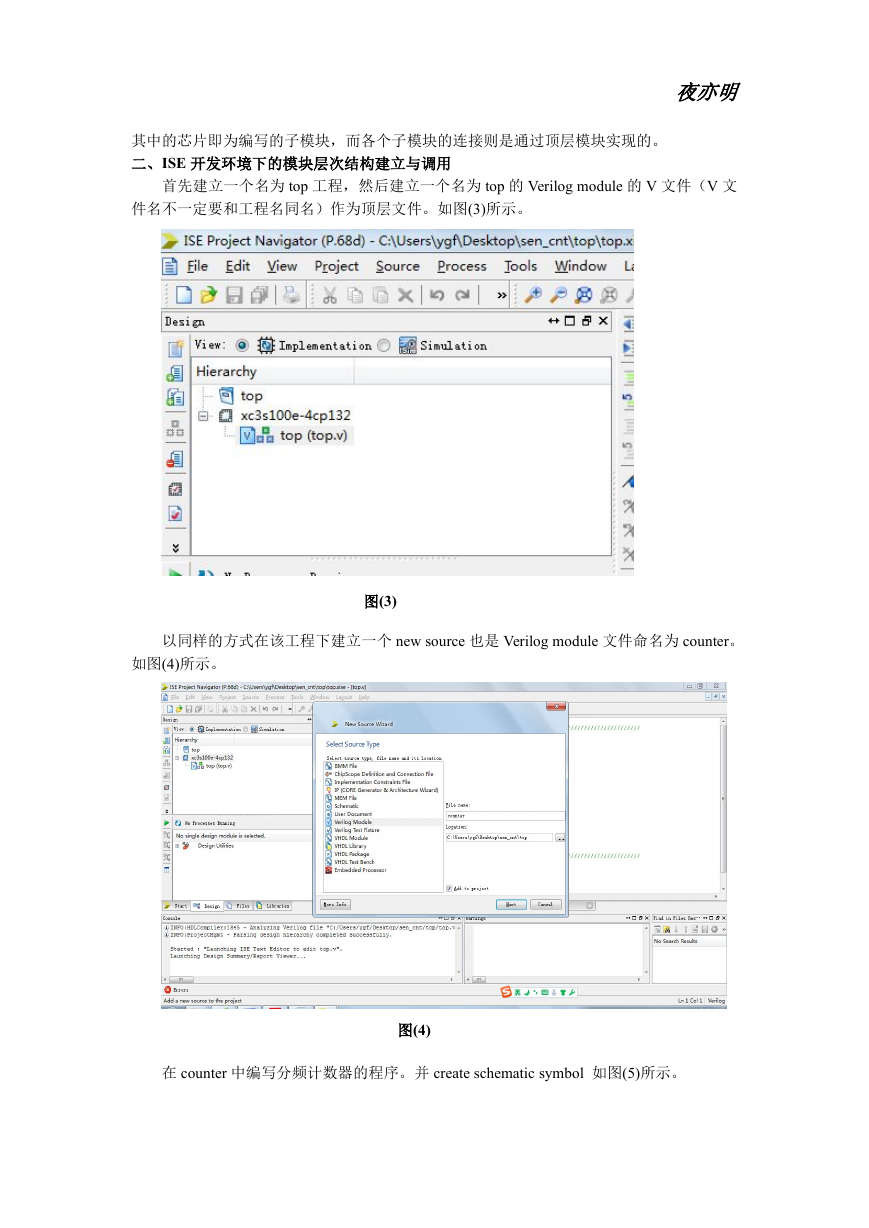

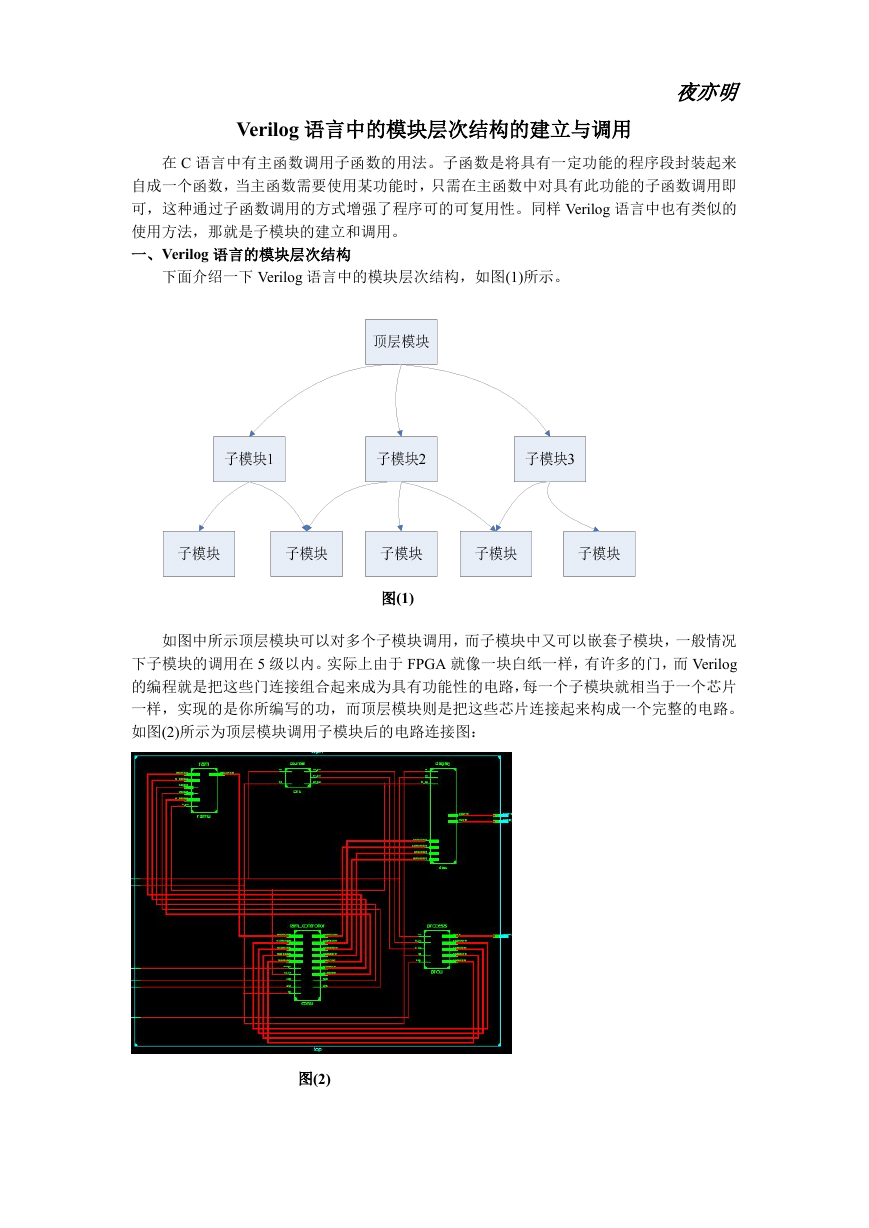

夜亦明Verilog语言中的模块层次结构的建立与调用在C语言中有主函数调用子函数的用法。子函数是将具有一定功能的程序段封装起来自成一个函数,当主函数需要使用某功能时,只需在主函数中对具有此功能的子函数调用即可,这种通过子函数调用的方式增强了程序可的可复用性。同样Verilog语言中也有类似的使用方法,那就是子模块的建立和调用。一、Verilog语言的模块层次结构下面介绍一下Verilog语言中的模块层次结构,如图(1)所示。如图中所示顶层模块可以对多个子模块调用,而子模块中又可以嵌套子模块,一般情况下子模块的调用在5级以内。实际上由于FPGA就像一块白纸一样,有许多的门,而Verilog的编程就是把这些门连接组合起来成为具有功能性的电路,每一个子模块就相当于一个芯片一样,实现的是你所编写的功,而顶层模块则是把这些芯片连接起来构成一个完整的电路。如图(2)所示为顶层模块调用子模块后的电路连接图:图(1)图(2)�

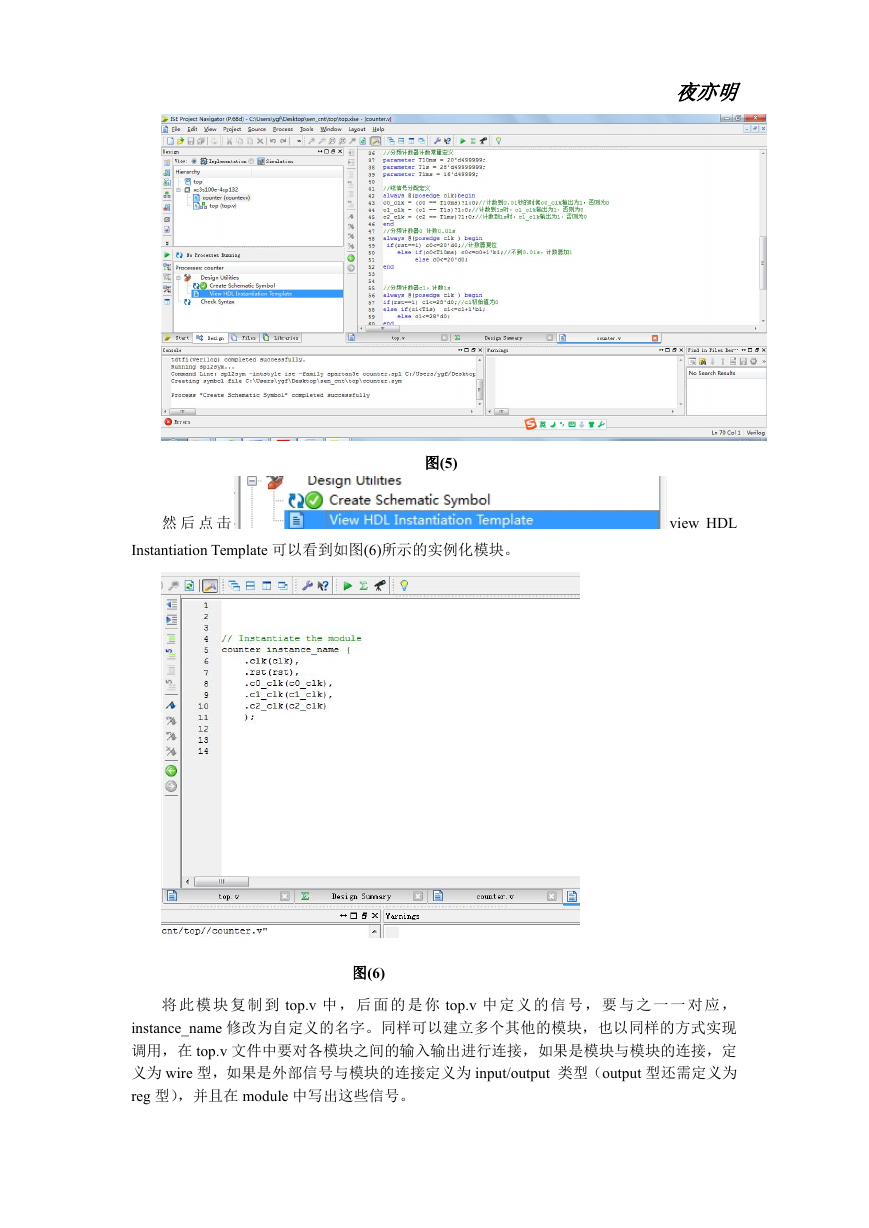

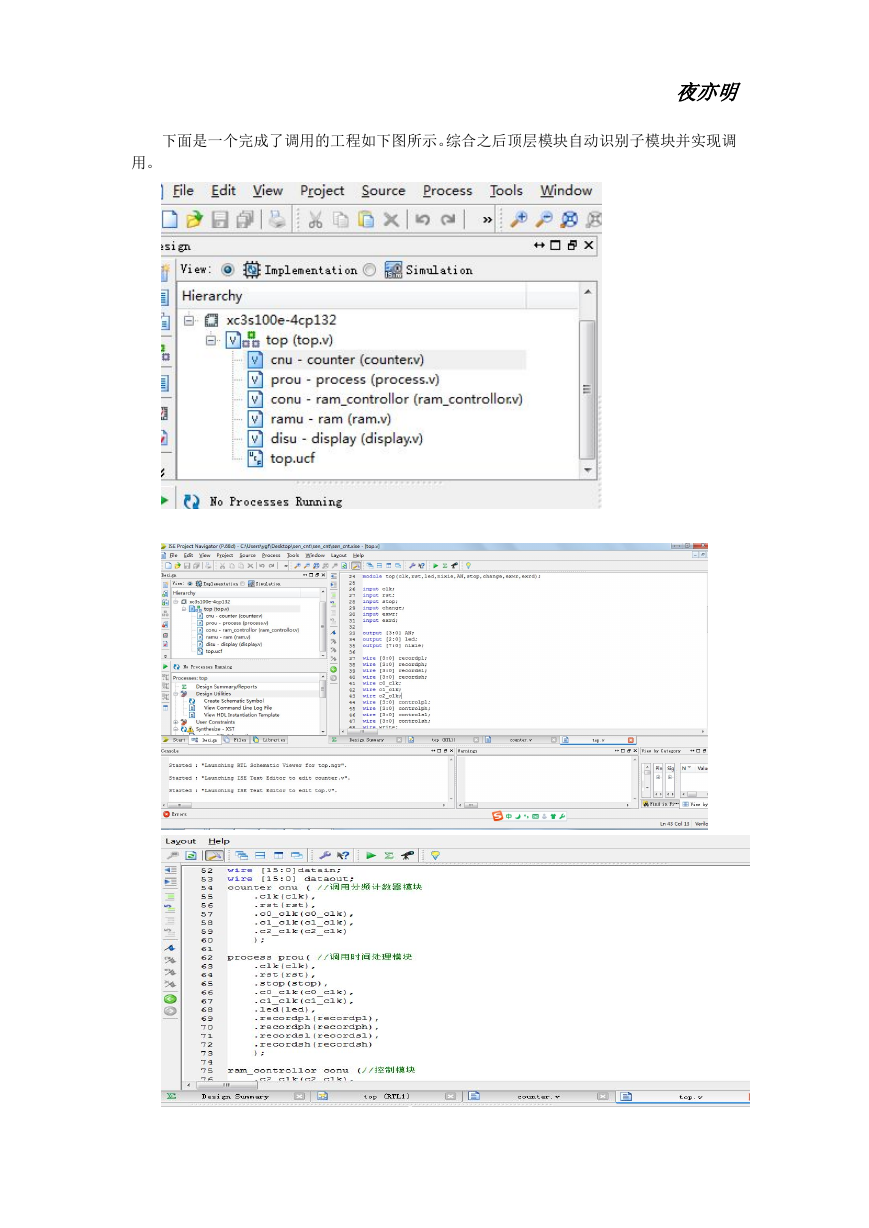

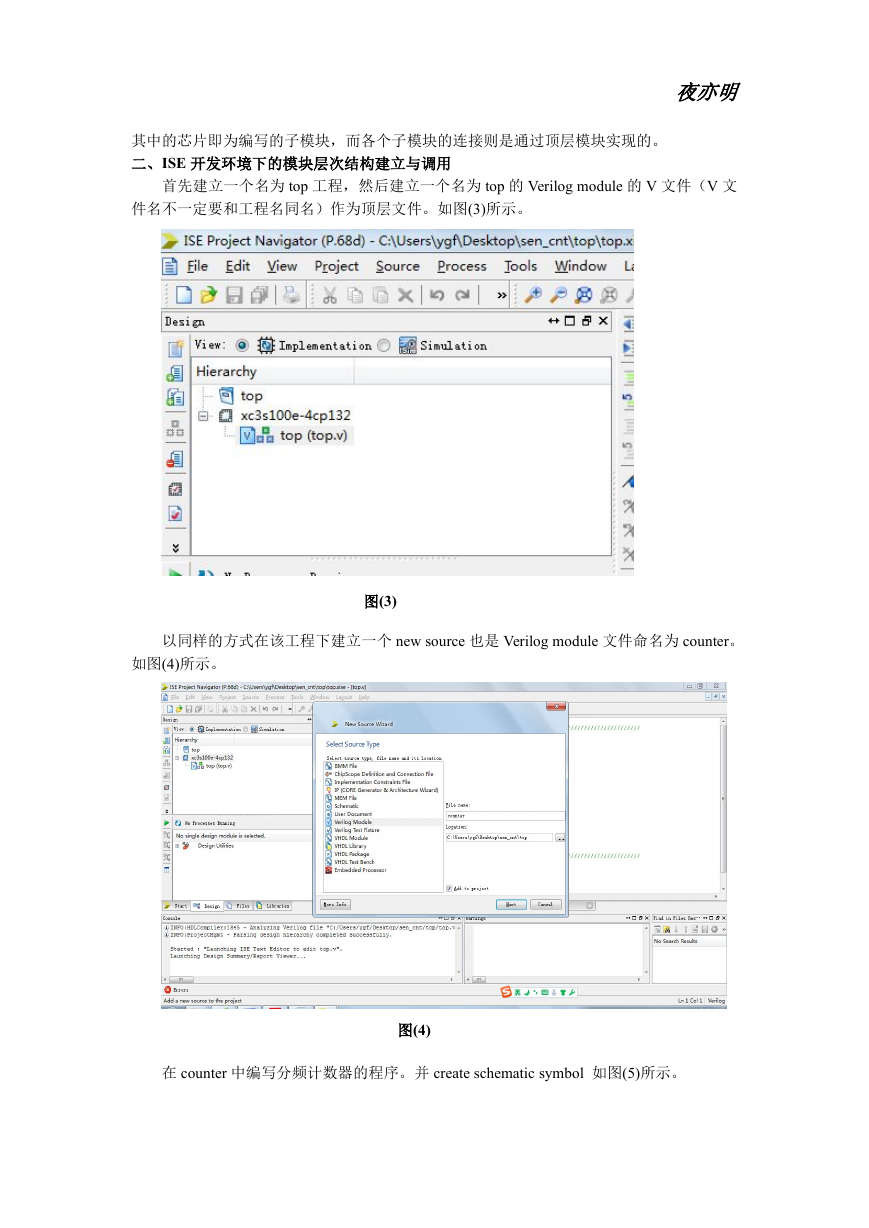

夜亦明其中的芯片即为编写的子模块,而各个子模块的连接则是通过顶层模块实现的。二、ISE开发环境下的模块层次结构建立与调用首先建立一个名为top工程,然后建立一个名为top的Verilogmodule的V文件(V文件名不一定要和工程名同名)作为顶层文件。如图(3)所示。以同样的方式在该工程下建立一个newsource也是Verilogmodule文件命名为counter。如图(4)所示。在counter中编写分频计数器的程序。并createschematicsymbol如图(5)所示。图(3)图(4)�

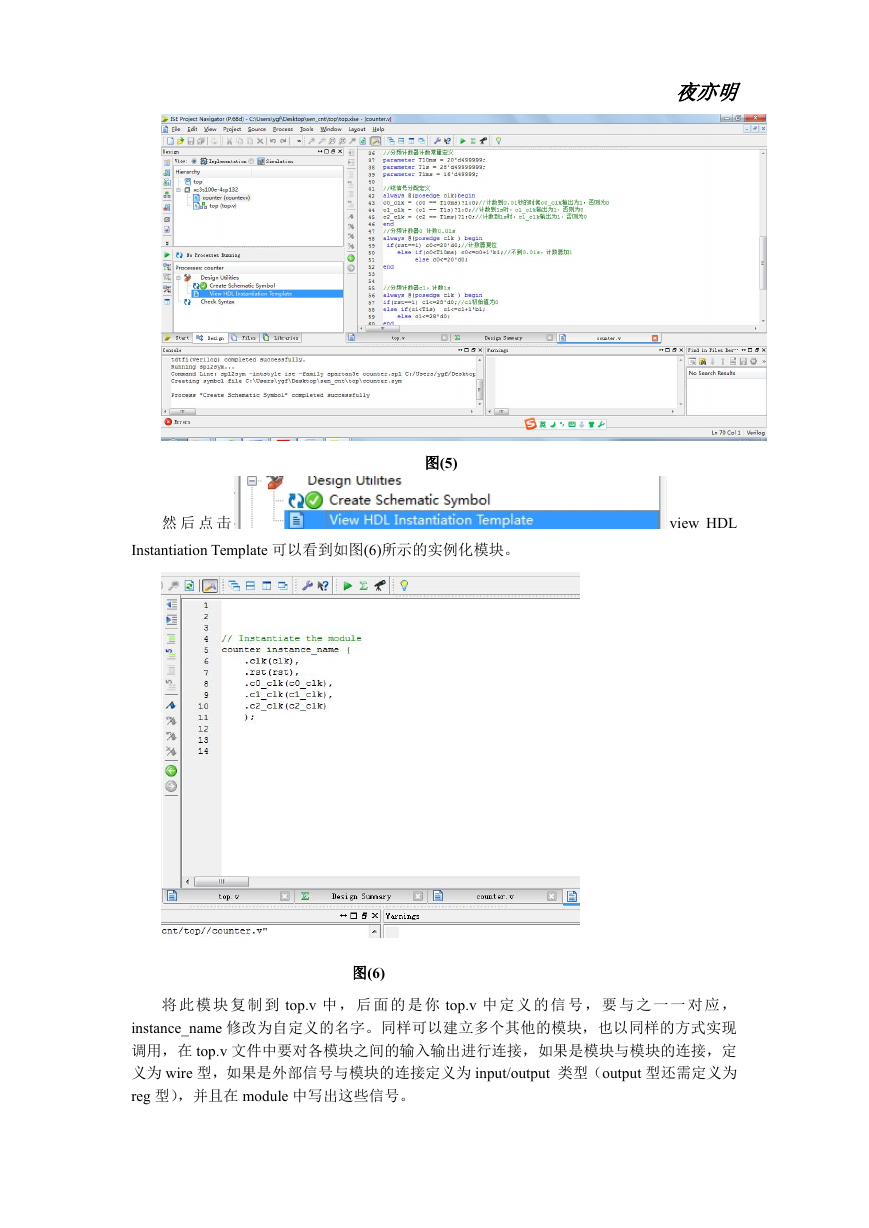

夜亦明然后点击viewHDLInstantiationTemplate可以看到如图(6)所示的实例化模块。将此模块复制到top.v中,后面的是你top.v中定义的信号,要与之一一对应,instance_name修改为自定义的名字。同样可以建立多个其他的模块,也以同样的方式实现调用,在top.v文件中要对各模块之间的输入输出进行连接,如果是模块与模块的连接,定义为wire型,如果是外部信号与模块的连接定义为input/output类型(output型还需定义为reg型),并且在module中写出这些信号。图(5)图(6)�

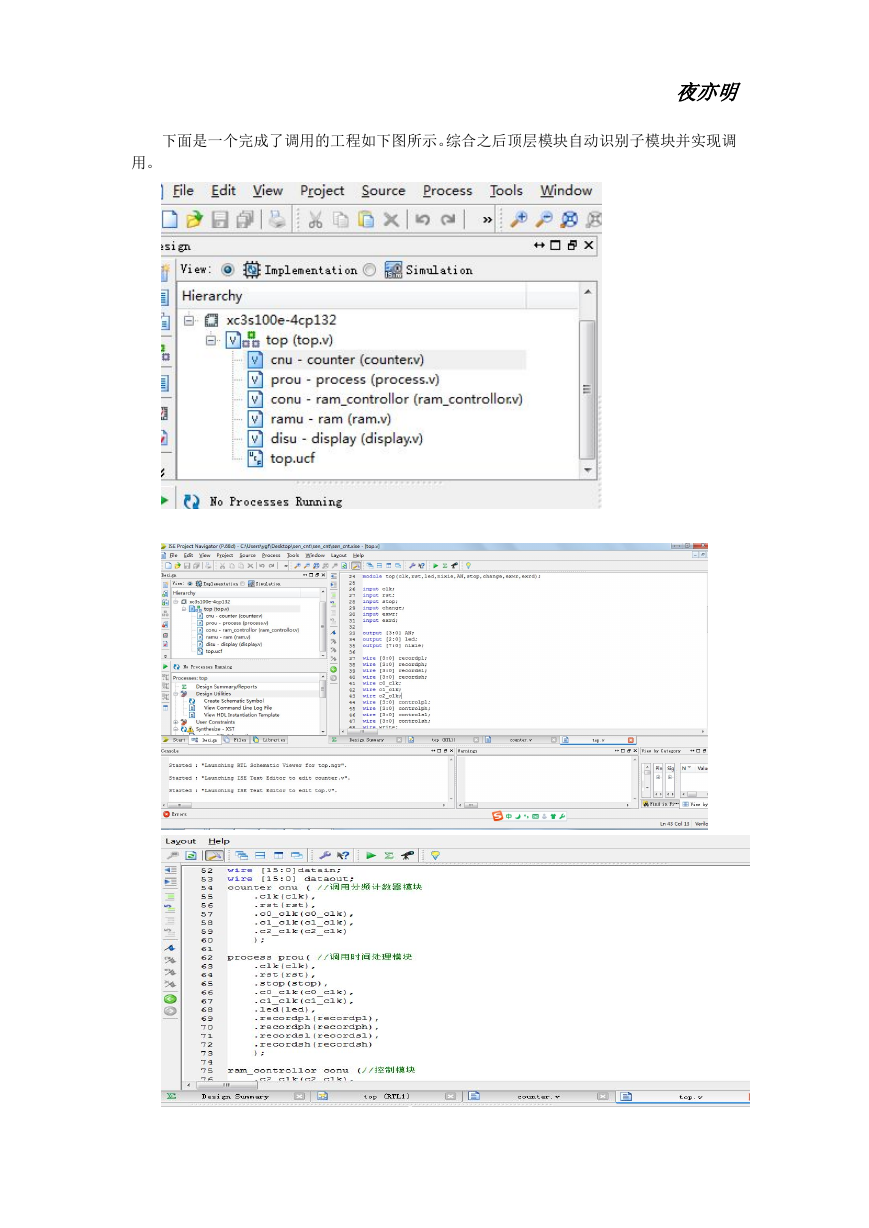

夜亦明下面是一个完成了调用的工程如下图所示。综合之后顶层模块自动识别子模块并实现调用。�

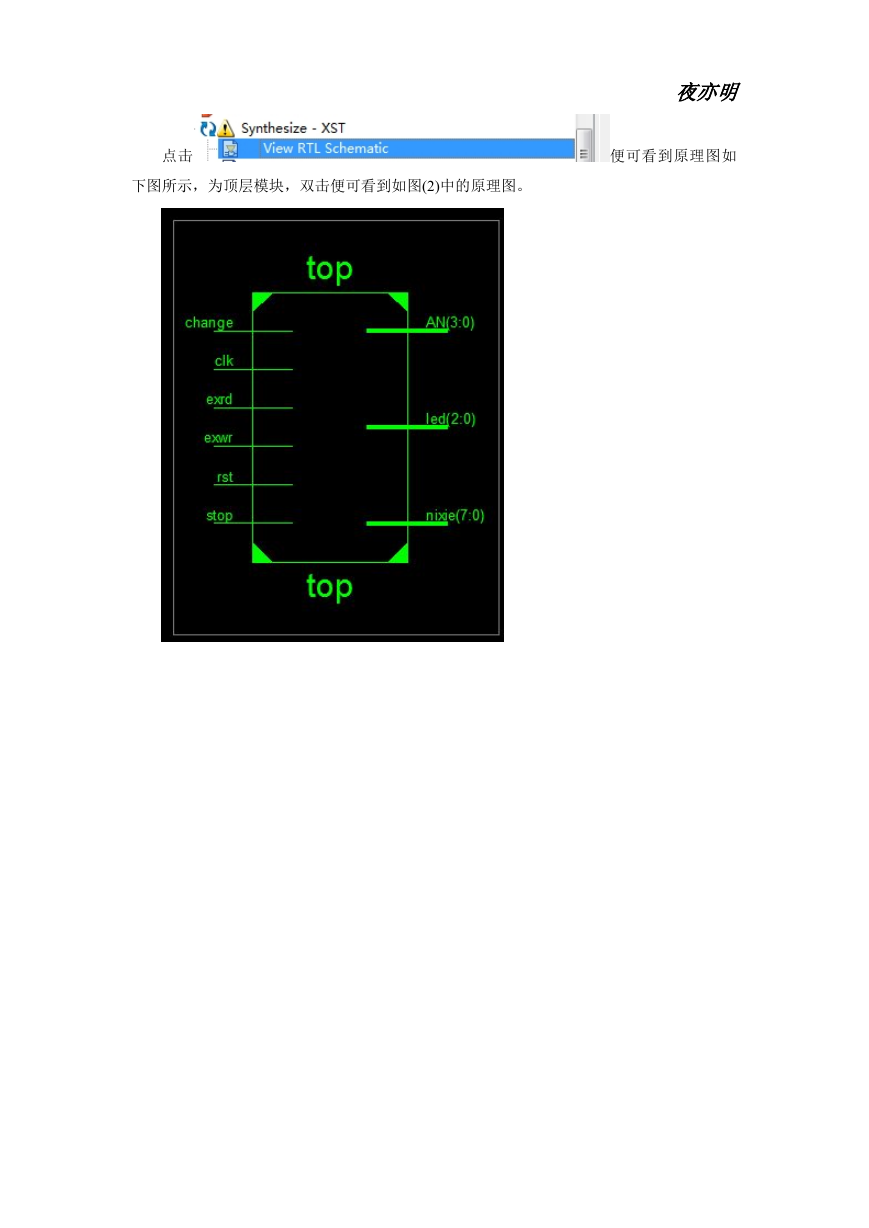

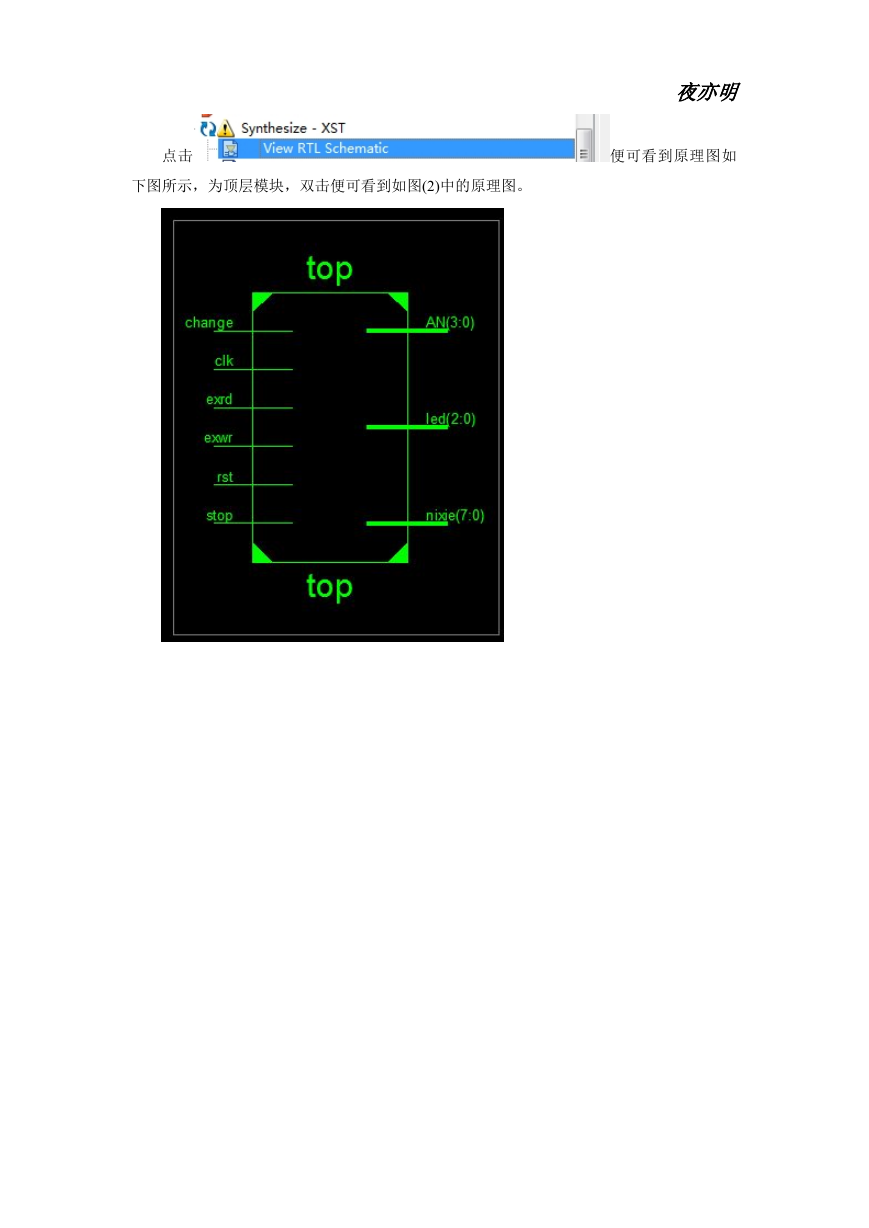

夜亦明点击便可看到原理图如下图所示,为顶层模块,双击便可看到如图(2)中的原理图。�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc