1. DDR3 不再使用 T-Balanced,只使用 fly-by。最后一个 ddr 到 vtt 端接电阻走线长度不超

过 400mil。

2.

XILINX 要求 DDR 布线必须满足

DQS 和 DQ 之间的时延不能超过±5ps,(TI 要求走线长度设定为 10mil 等长,差分

线对内等长 1mil)。

CK/CK#和控制信号线之间的时延不能超过±25ps,(TI 走线长度设定为 20mil 等长)。

CK/CK#信号必须晚于 DQS/DQS#到达每个 DDR 芯片,也就是说 CK/CK#信号要比每

个 DQS 信号长。CK 可以晚于 DQS 信号 0-1600ps 到达 DDR 芯片,但最好保持在

150ps-1600ps。当使用 DIMM 模块时,要保证板上走线和模块上走线总长度满足该

要求。

速率在 1333Mb/s 以下时,单端线走线阻抗设置为 50 欧,差分线设置为 100 欧。

当为 13333Mb/s 或更高时,单端和差分走线阻抗分别设置为 40 欧和 80 欧。(TI 只

要求走线阻抗为 50/100 欧)

在 DDR 初始化的时候,RESET_N 信号要 4.7K 下拉到 GND。(但是 TI 的开发板却将

该信号 4.7K 上拉到 VTT)。走线时同样使用 fly-by 布线,但是与其他信号无时序关

系。

3. Dqs 信号长度不超过 4500mil,Dqs 推荐在 1 个 byte lane 的中间走线。

4. 需要给 VTT 端接加去耦电容,每四个加 1 个 1uF 的电容,每 25 个加 1 个 100uF 的电容

5. VTT 端接电阻到最后一个 DDR 颗粒之间的走线不超过 400mil,VTT 端接电阻选择阻值

40 欧。

6. 由于 VTT 电流较大,(2.5-3.5A)。vref 不和 vtt 走在同一层。

�

7. VTT 走线在 150mil 以上。Vref 走线在 25mil 以上。Vref 需要与其他信号远离(25mil 以

上)。

8. Vref 的分压电阻精度在 1%,阻值在 100 到 1k 之间(首选 1K)。注:当 DDR 芯片在少于

4 个的时候才能使用分压电阻,否则需要使用 LDO。

9. Vref 和 vtt 的产生源头要靠近 DDR 颗粒。

10. CK/CK#信号末端需要端接,端接方式如图所示

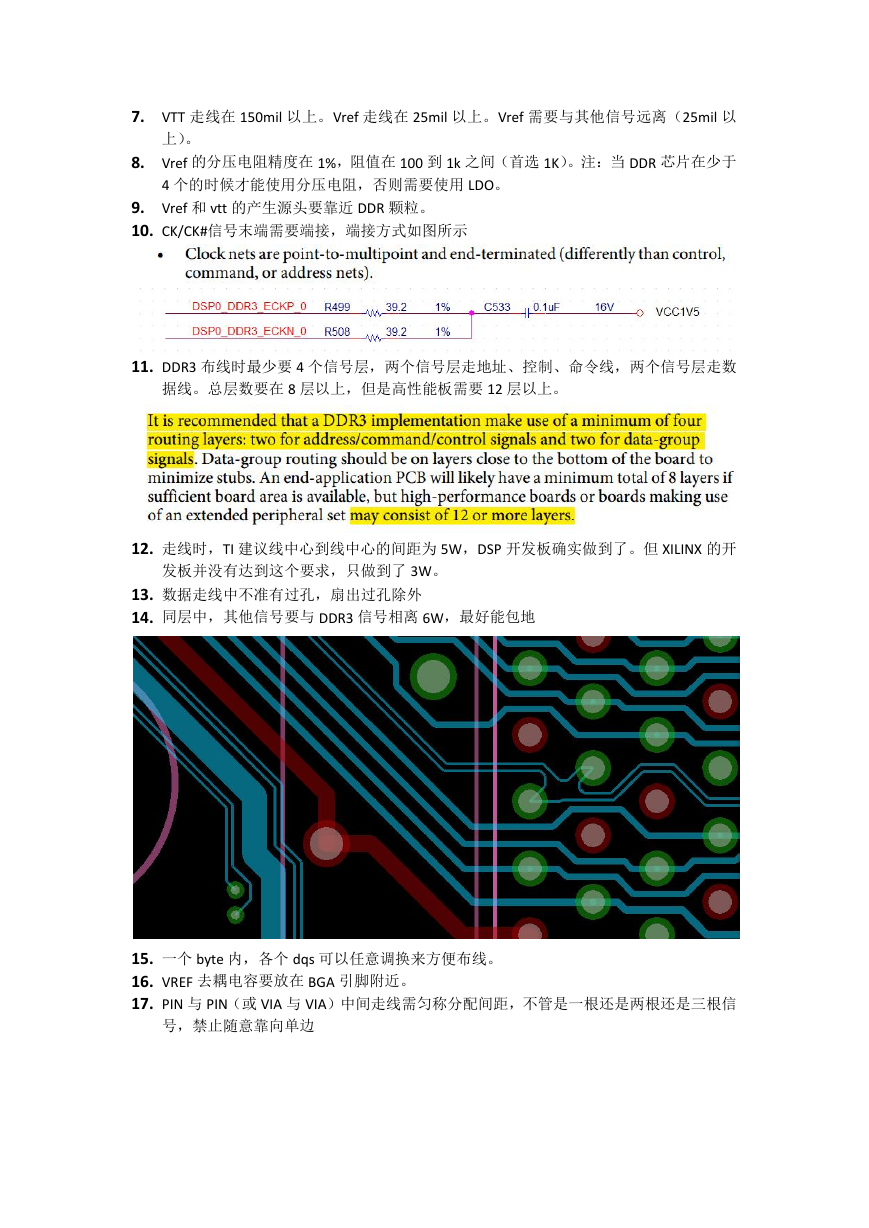

11. DDR3 布线时最少要 4 个信号层,两个信号层走地址、控制、命令线,两个信号层走数

据线。总层数要在 8 层以上,但是高性能板需要 12 层以上。

12. 走线时,TI 建议线中心到线中心的间距为 5W,DSP 开发板确实做到了。但 XILINX 的开

发板并没有达到这个要求,只做到了 3W。

13. 数据走线中不准有过孔,扇出过孔除外

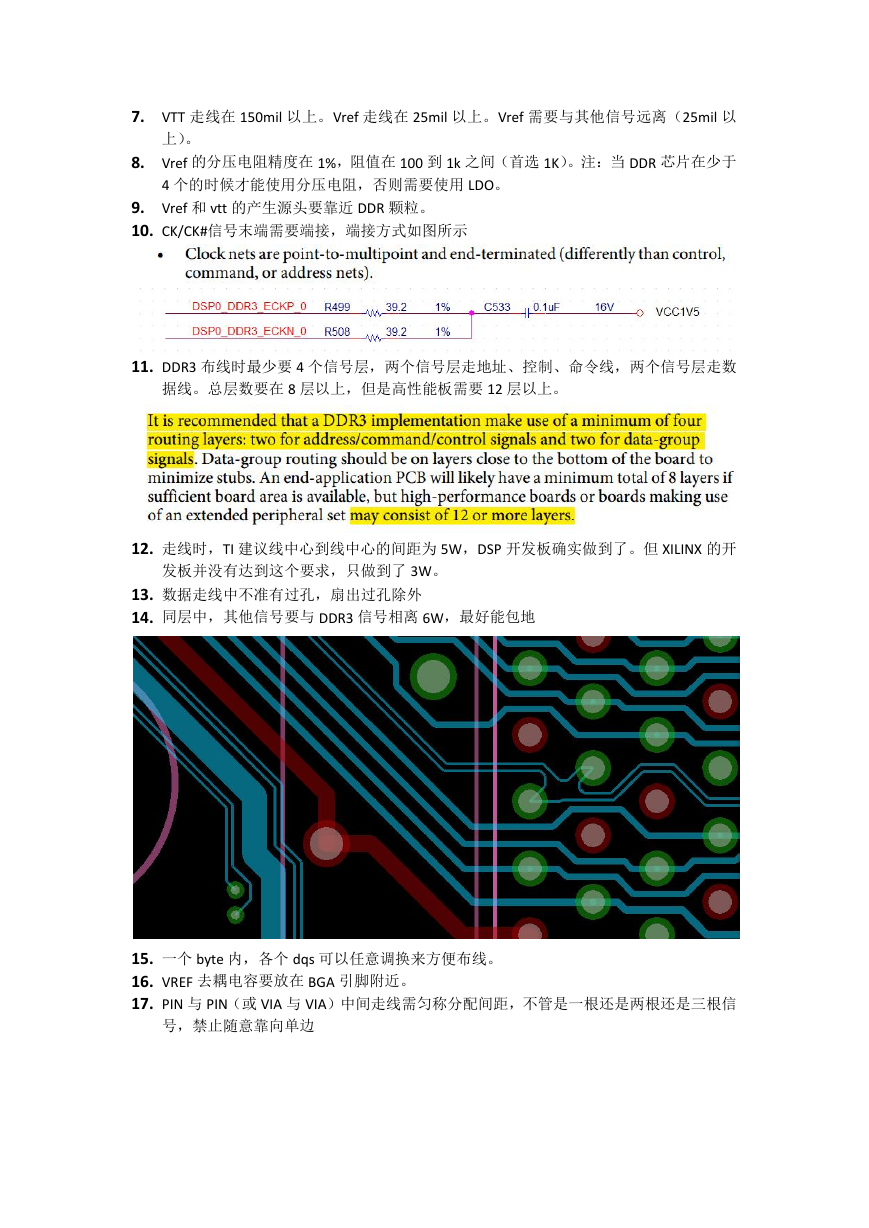

14. 同层中,其他信号要与 DDR3 信号相离 6W,最好能包地

15. 一个 byte 内,各个 dqs 可以任意调换来方便布线。

16. VREF 去耦电容要放在 BGA 引脚附近。

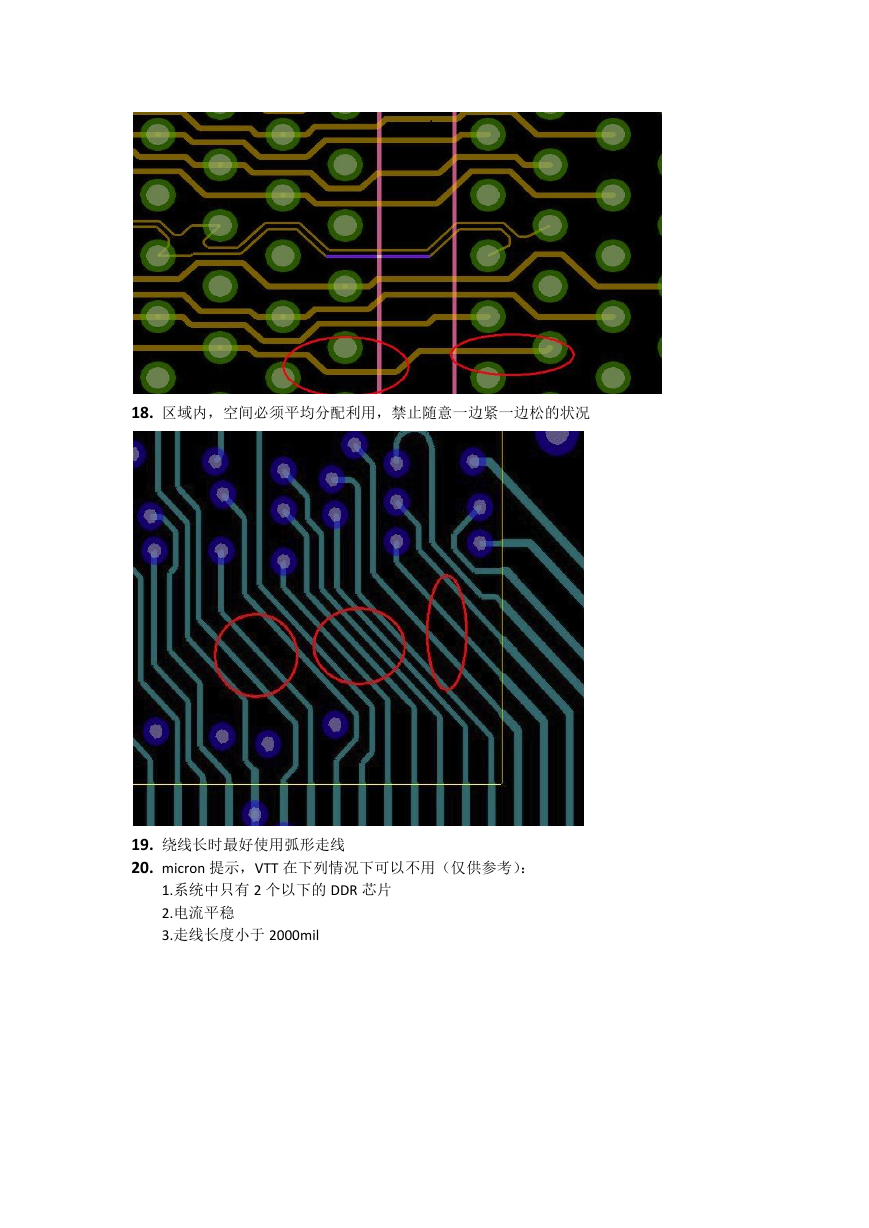

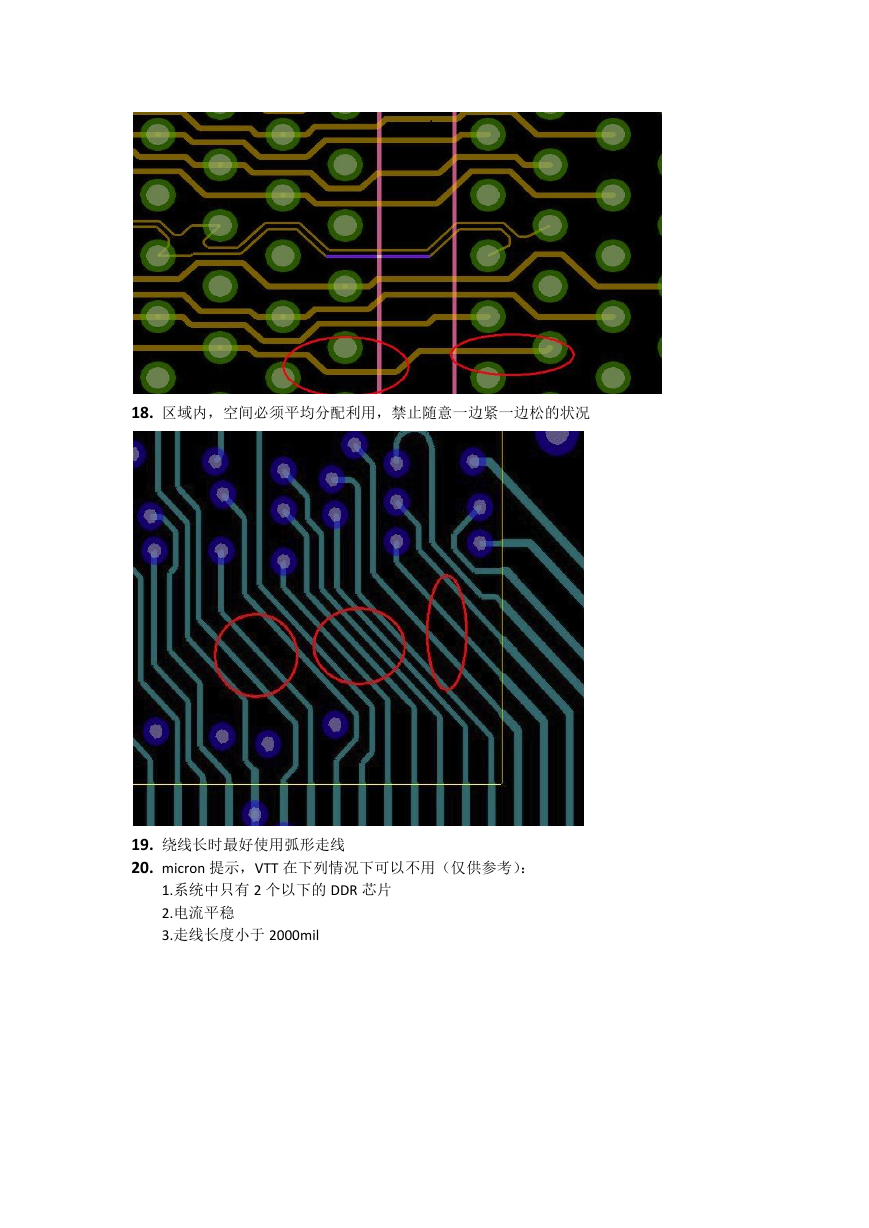

17. PIN 与 PIN(或 VIA 与 VIA)中间走线需匀称分配间距,不管是一根还是两根还是三根信

号,禁止随意靠向单边

�

18. 区域内,空间必须平均分配利用,禁止随意一边紧一边松的状况

19. 绕线长时最好使用弧形走线

20. micron 提示,VTT 在下列情况下可以不用(仅供参考):

1.系统中只有 2 个以下的 DDR 芯片

2.电流平稳

3.走线长度小于 2000mil

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc