第l7卷第6期 2007年6月 计算机技术与发展 COMPUTER TECHN()【J( Y AND DEVE[ )P~1ENT Vo1.17 NO.6 Jun. 2007 基于FPGA的VGA显示模块设计 张亚平,贺占庄 (西安微电子技术研究所,陕西西安710054) 摘 要:VGA(视频图形阵列)怍为一种标准的显示接口得到广泛的应用。文中依据VGA显示的原理,在讨论EDA软件 工具平台下的FPGA设计流程的前提下,利用VHDL作为逻辑描述的手段,在Almra公司的QuarmsII软件环境下完成 VGA模块的设计。给出了VGA模块的设计思路和顶层逻辑框图。 关键词:VGA;显示接口;EDA;FPGA;VHDL 中图分类号:TP334.7 文献标识码:A 文章编号:1673—629X(2【)()7)O6—0242—04 Design of VGA Display Module Based on FPGA ZHANG Ya—ping.HE Zhan—zhuang (Xi’an Microelectronics Technology Institute,Xi’an 710054,China) Abstract:As a stand~d display interface,VGA(Video Graphics y)is widely used.In this article,according to the principle of VGA display,completed the design of VGA module based on QuartuslI softerware environment while using VHDL as a meal'lS of logic descrip tion as well as discussed the process of the design of FPGA based on EDA softerware platfoma.Also gave the ideas of VGA module design and the top logic diagram of this modular. Key words:VGA;display interface;EDA;FPGA;VHDL 0 引 言 现代电子设计技术的核心是EDA(Electronic De— sign Automation)技术。EDA技术依赖功能强大的计 算机系统,在EDA软件工具平台上,采用自上而下 (Top Down)的设计方法,以硬件描述语言(Hardware Description Language,HDL)为系统逻辑描述的主要手 段完成系统设计。EDA设计方法比较显著的特点有 如下几个:高级设计语言,系统级仿真和系统级综合优 化方法,模块化设计和增量设计方法。而FPGA/ CPLD具有功能强大,开发过程投资小、周期短,可反 复编程修改,保密性好,开发工具智能化等特点。随着 电子工艺的不断改进,低成本的FPGA/CPLD器件推 陈出新,促使FPGA/CPLD成为当今硬件设计的首选 方式之一u J。使用EDA软件工具平台和VHDL进行 设计,利用可编程器件 /CPLD实现的VGA显示 控制模块在工业现场中有许多实际应用。 1 FPGA原理及设计流程 FPGA/CPLD,DSP和CPU被称为未来数字电路 收稿日期:2006—09—07 作者简介:张亚平(1977一),男,甘肃天水人,硕士研究生,研究方 向为计算机应用;贺占庄,研究员,研究方向为计算机控制技术。 系统的3块基石,也是目前硬件设计研究的热点。FP— GA继承了ASIC(Application Specified Integrated Cir— cult)的大规模、高集成度、高可靠性的优点,又克服了 普通ASIC设计周期长、投资大、灵活性差的缺点。并 且,随着制造工艺的不断提高,FPGA芯片的规模也越 来越大。现在,单片逻辑门数已逾千万。芯片规模的 增大也使得所能实现的功能越来越强。这都使得FP— GA/CPLD设计技术成为当今高级硬件工程师和IC工 程师的必备技能。 1.1 FPGA原理 CPLD,FPGA是在PAL(Programmable Array Log— ic)、GAL(Generic PAL)等基础上发展起来的一种具有 丰富’的可编程I/O引脚、逻辑宏单元、门电路以及 RAM空间的可编程逻辑器件,几乎所有应用门阵列、 PLD和中小规模通用数字集成电路的场合均可应用 FPGA和CPLD器件。CPLD的设计采用E2CMOS工 艺,其基本逻辑单元是由一些与、或阵列加上触发器构 成的;而FPGA的设计采用SRAM工艺,其基本逻辑 单元是基于查找表来设计的。 查找表(Look—Up—Table)简称为LUT,I UT本 质上就是一个RAM,实现将输入信号的各种组合功能 以一定的次序写入RAM中,然后在输入信号的作用 下,输出特定的函数运算结果。目前FPGA中多使用 维普资讯 http://www.cqvip.com �

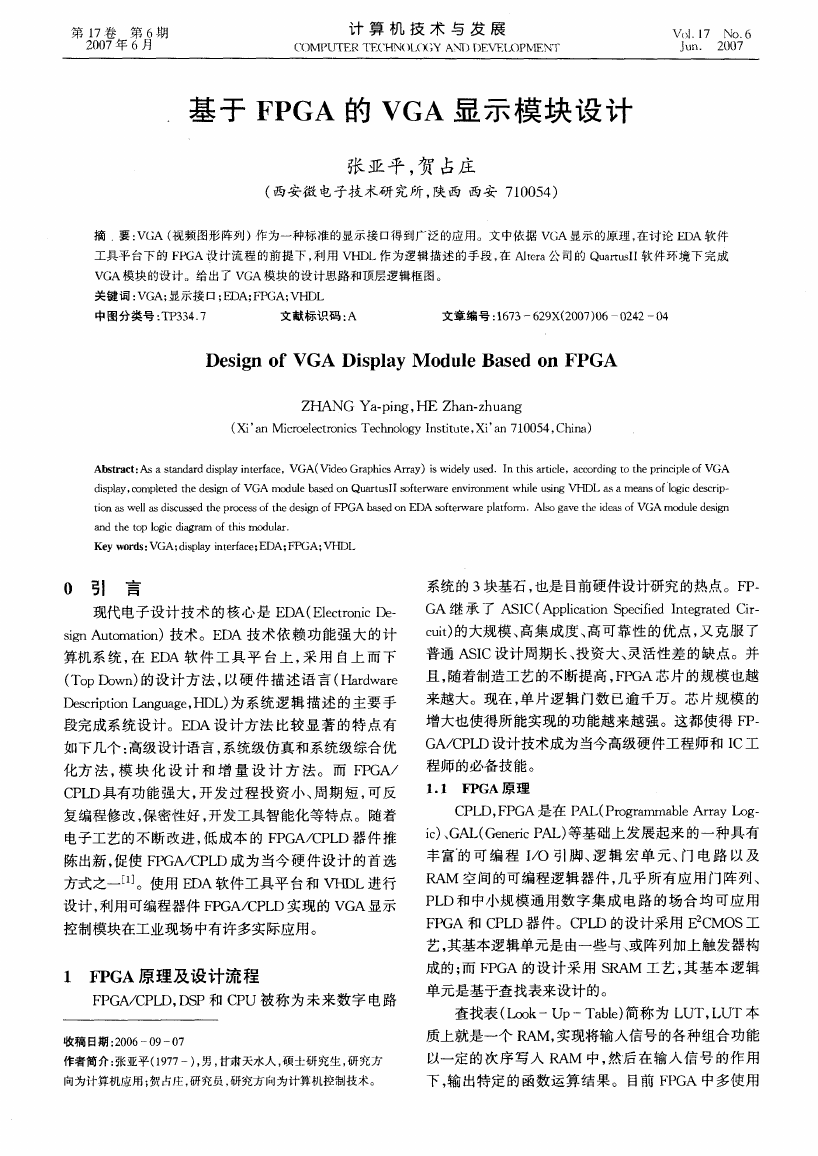

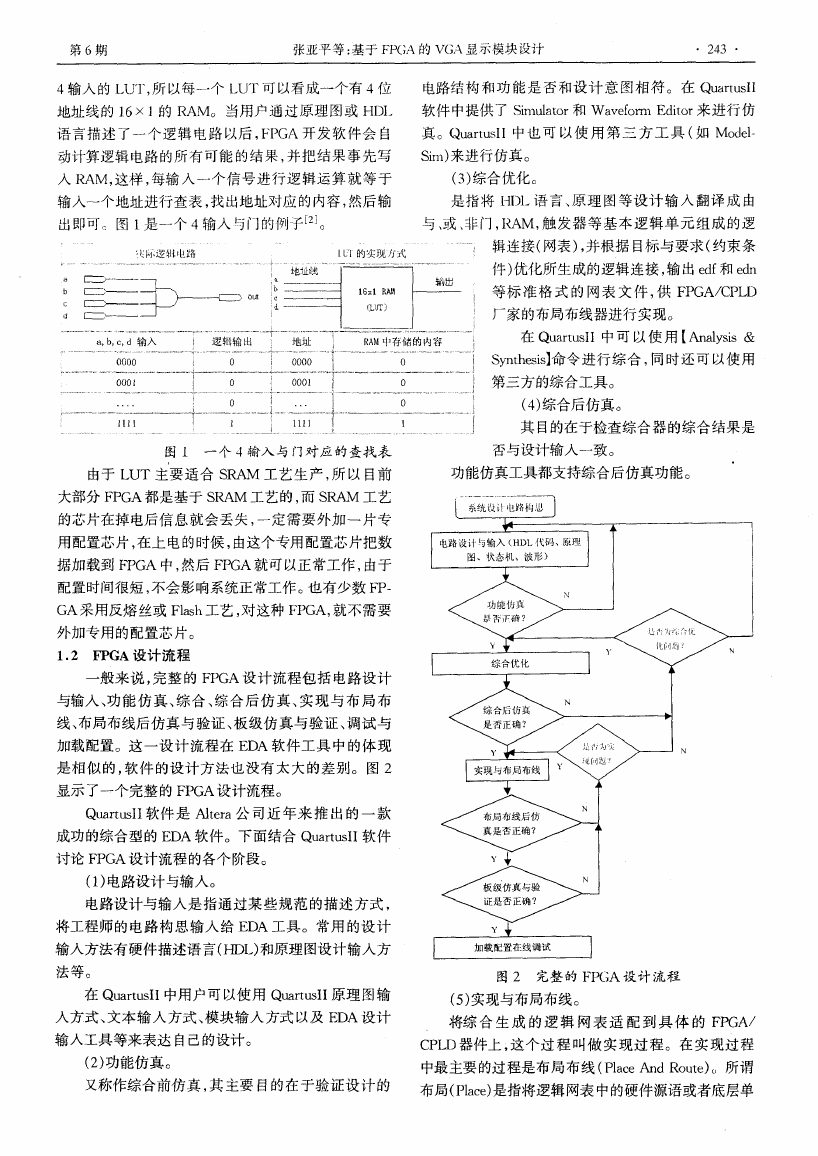

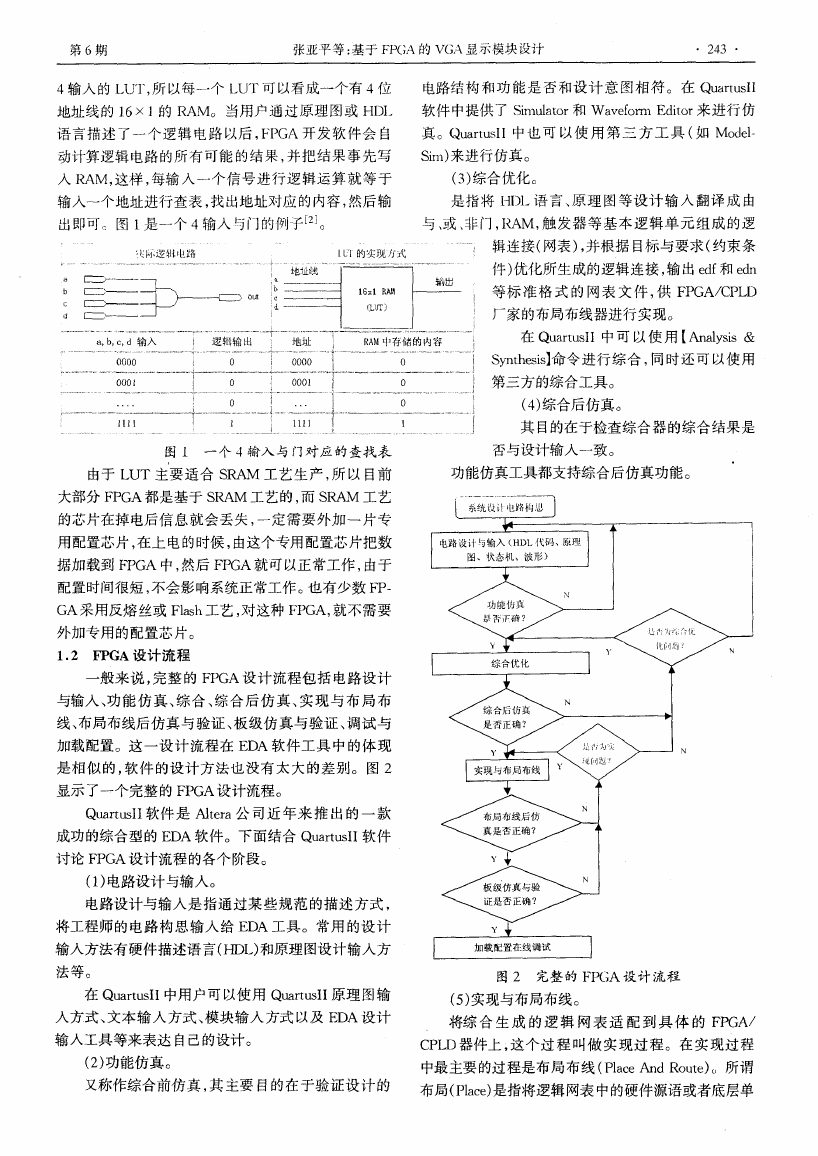

第6期 张亚平等:基于FPGA的VGA显示模块没计 ·243· 4输入的LU r,所以每一个L uT可以看成~个有4位 地址线的16×1的RAM。当用户通过原理图或HDI 语言描述了一个逻辑电路以后,H GA开发软件会自 动计算逻辑电路的所有可能的结果,并把结果事先写 入RAM,这样,每输入一个信号进行逻辑运算就等于 输入一 -一个地址进行查表,找出地址对应的内容,然后输 出即可。图l是一个4输入 门的例子¨7 J。 【t/I的实现方式 电路结构和功能是否和设计意图相符。在Quartusll 软件中提供了Simulator和Wavefoml Editor来进行仿 真。QuartusII中也可以使用第三方工具(如Model— Sim)来进行仿真。 (3)综合优化。 是指将HD1 语言、原理图等设计输入翻译成由 与、或、非门,ILAM,触发器等基本逻辑单元组成的逻 一 辑连接(网表),并根据目标与要求(约束条 …~… 件)优化所生成的逻辑连接,输出edf和edn 图l 一个4输入与门对应的查找表 由于LUT主要适合SRAM工艺生产,所以目前 大部分FPGA都是基于SRAM工艺的,而S 工艺 的芯片在掉电后信息就会丢失,一定需要外加一片专 用配置芯片,在上电的时候,由这个专用配置芯片把数 据加载到FPGA中,然后FPGA就可以正常工作,由于 配置时间很短,不会影响系统正常工作。也有少数FP— GA采用反熔丝或Flash工艺,对这种FPGA,就不需要 外加专用的配置芯片。 1.2 FPGA设计流程 一般来说,完整的FPGA设计流程包括电路设计 与输入、功能仿真、综合、综合后仿真、实现与布局布 线、布局布线后仿真与验证、板级仿真与验证、调试与 加载配置。这一设计流程在EDA软件工具中的体现 是相似的,软件的设计方法也没有太大的差别。图2 显示了一个完整的FPGA设计流程。 QuartuslI软件是Ahera公司近年来推出的一款 成功的综合型的EDA软件。下面结合QuartuslI软件 讨论FPGA设计流程的各个阶段。 (1)电路设计与输入。 电路设计与输入是指通过某些规范的描述方式, 将工程师的电路构思输入给EDA工具。常用的设计 输入方法有硬件描述语言(}Ⅱ)L)和原理图设计输入方 法等。 在Quartusll中用户可以使用Quartusll原理图输 入方式、文本输入方式、模块输入方式以及EDA设计 输入工具等来表达自己的设计。 (2)功能仿真。 又称作综合前仿真,其主要目的在于验证设计的 等标准格式的网表文件,供FPGA/CPLD 厂家的布局布线器进行实现。 在QuartuslI中可以使用【Analysis& Synthesis]命令进行综合,同时还可以使用 第三方的综合工具。 (4)综合后仿真。 其目的在于检查综合器的综合结果是 否与设计输入一致。 功能仿真工具都支持综合后仿真功能。 图2完整的FPGA设计流程 (5)实现与布局布线。 将综合生成的逻辑网表适配到具体的FPGA/ CPLD器件上,这个过程叫做实现过程。在实现过程 中最主要的过程是布局布线(Place And Route)。所谓 布局(Place)是指将逻辑网表中的硬件源语或者底层单 维普资讯 http://www.cqvip.com �

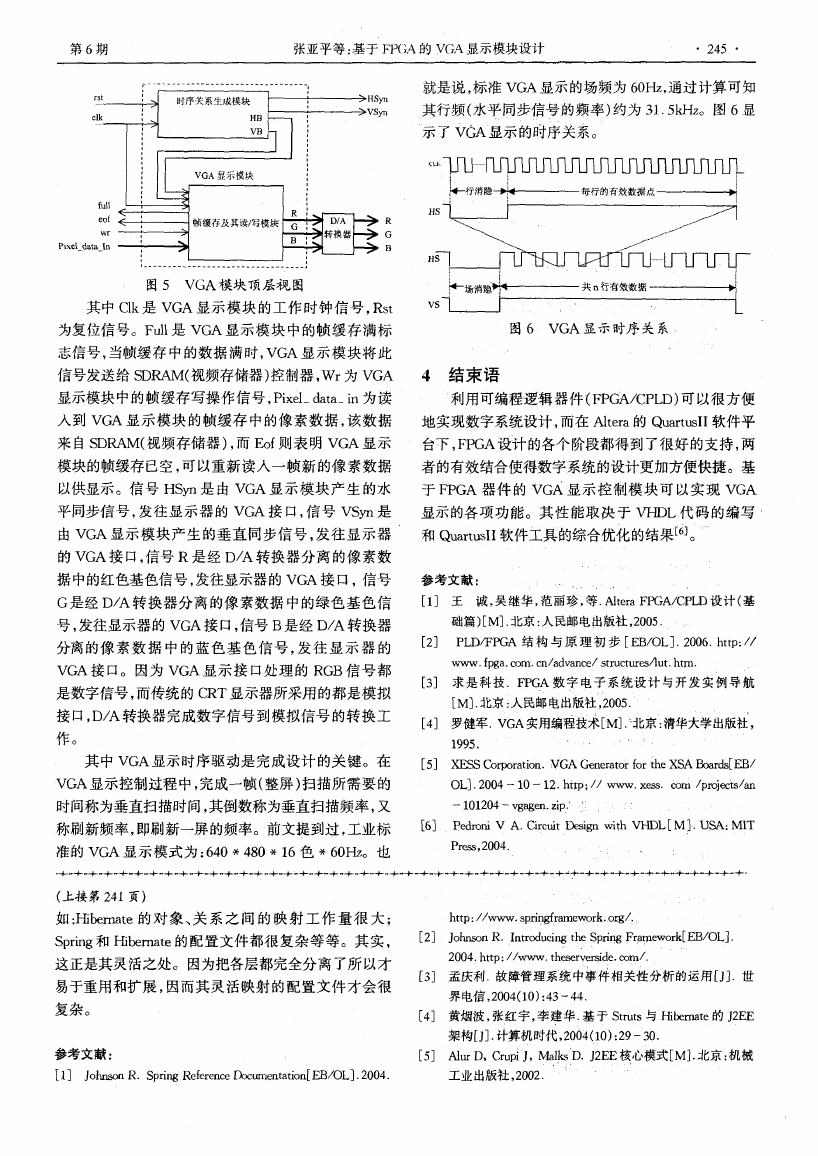

·244· 计算机技术与发展 第l7卷 元合理地适配到FPGA内部的固有硬件结构上。所谓 布线(Route)是指根据布局的拓扑结构,利用FtK~A内 部的各种连线资源,合理正确连接各个元件的过程。 QuartusII中提供了【Fitter】、【AssignmentEditor】、 【FloorplanEditor】、【ChipEditor】、【增量布局布线】等功 能进行实现与布局布线。 (6)布局布线后仿真与验证。 又称为时序仿真或者后仿真。其主要目的在于发 现时序违规(TimingViolation),即不满足时序约束条件 或者器件固有时序规则(建立时间、保持时间等)的情 况。 在QuartuslI中有内嵌的时序分析工具完成静态 时序分析(Static Timing Analyzer);也可以使用第三方 工具进行时序分析与验证。 (7)板级仿真与验证。 目的是为了分析高速设计的信号完整性、电磁干 扰(EMI)等电路特性。 (8)加载配置与在线调试。 将生成的配置文件写入到FPGA/CPLD芯片中进 行测试。 · 在QuartuslI中通过Assemble(生成编程文件)、 Programmer(建立包含设计所有器件名称和选项的链 式文件)、转换编程文件等功能支持此步骤。 2 VGA显示原理 vGA(Video Graphics Array)作为一种标准的显示 接口得到了广泛的应用。VGA在任何时刻都必须工 作在某一显示模式之下,其显示模式分为字符显示模 式和图形显示模式。而在应用中,讨论的都是图形显 示模式。 VGA的图形模式分为三类:CGA、EGA兼容的图 形模式;标准的VGA图形模式;VGA扩展图形模式。 后两种图形模式统称为VGA图形模式。文中基于标 准VGA模式来实现。工业标准的VGA显示模式为: 640*480*16色*60Hz。 常见的彩色显示器一般都是由CRT(阴极射线 管)构成,每一个像素的色彩由R(红,Red)、G(绿, Green)、B(蓝,Blue)三基色构成。显示时采用的是逐 行扫描的方式。由VGA显示模块产生的水平同步信 号和垂直同步信号控制阴极射线管中的电子枪产生电 子束,轰击涂有荧光粉的屏幕,产生RGB三基色,于显 示屏上合成一个彩色像素点。图3表示的是VGA显 示模块与CRT显示器的控制框图【3l。 电子束扫描一幅屏幕图像上的各个点的过程称为 屏幕扫描。现在显示器都是通过光栅扫描方式来进行 图3 VGA显示模块与CRT显示器的控制框图 屏幕扫描。在光栅扫描方式下,电子束按照固定的路 径扫过整个屏幕,在扫描过程中通过电子束的通断强 弱来控制电子束所经过的每个点是否显示或显示的颜 色。电子枪在VGA显示模块产生的行同步、场同步 等控制信号的作用下进行包括水平扫描、水平回扫、垂 直扫描、垂直回扫等过程。光栅扫描的路径通常为:从 上到下扫过每一行,在每一行中从左到右地进行扫描。 其过程如下:电子束从屏幕左上角开始向右扫,当到达 屏幕的右边缘时,电子束关闭(水平消隐),并快速返回 屏幕左边缘(水平回扫),然后在下一条扫描线上开始 新的一次水平扫描。一旦所有的水平扫描均告完成, 电子束在屏幕的右下角结束并关闭(垂直消隐),然后 迅速返回到屏幕的左上角(垂直回扫),开始下一次光 栅扫描。图4显示了光栅扫描过程。 图4光栅扫描过程 垂 直 扫 描 3 VGA显示模块设计 VGA显示模块的设计,实质就是完成VGA显示 卡的功能:(1)在一定的工作频率下,产生正确的时序 关系(工作时钟信号,HSyn一水平同步信号,VSyn一垂 直同步信号,消隐信号之间的关系);(2)在正确时序的 控制下读出帧缓存中的像素数据,同时在当前帧显示 完毕时,向SDRAM控制器发信号,使SDRAM控制器 能够及时刷新帧缓存中的像素数据。图5是VGA显 示模块顶层视图l .5 J。 维普资讯 http://www.cqvip.com �

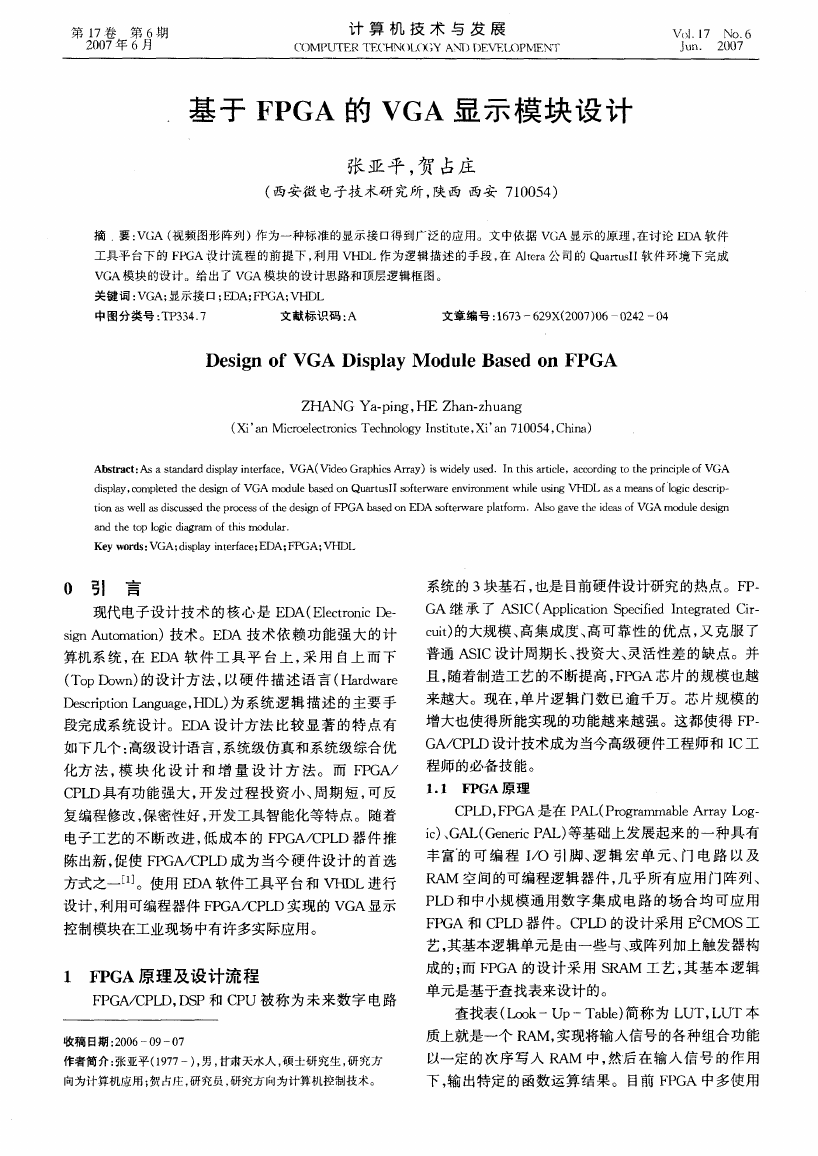

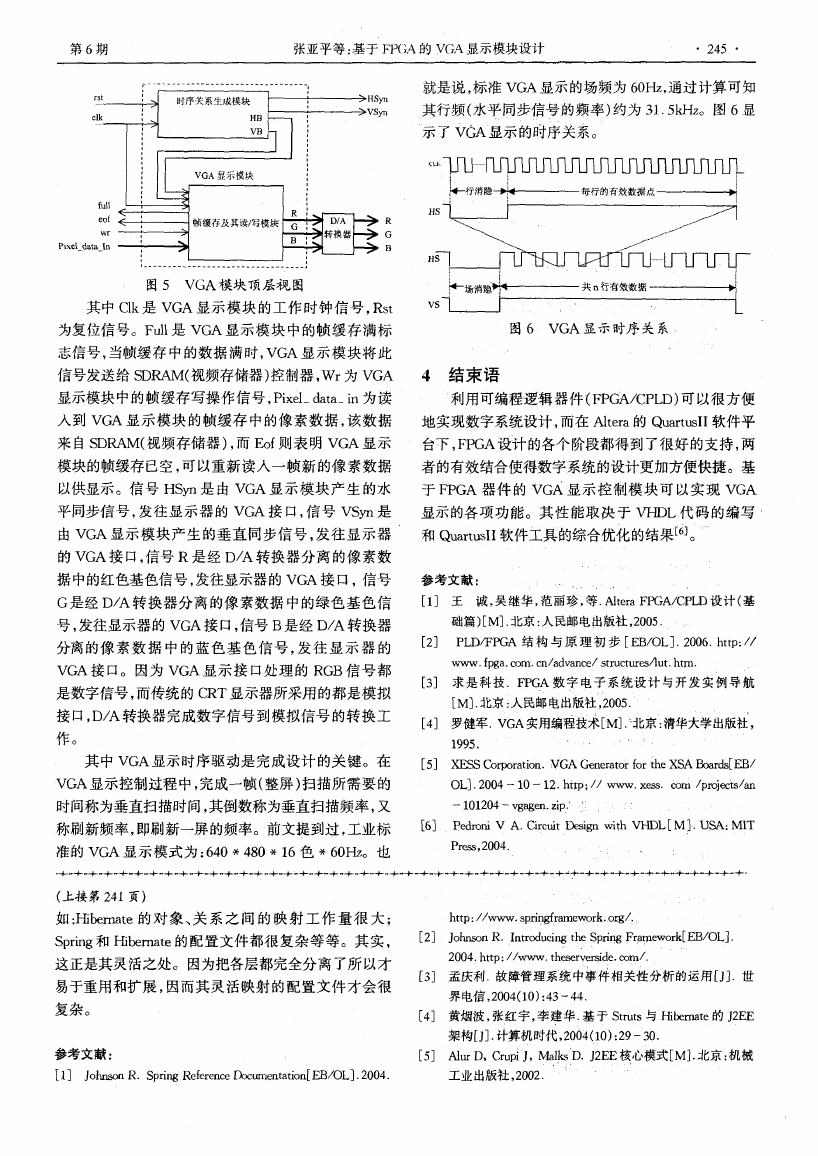

第6期 张亚平等:基于FPGA的VGA显示模块设计 ·245· 图5 VGA模块顶层视图 其中Clk是VGA显示模块的工作时钟信号,Rst 为复位信号。Full是VGA显示模块中的帧缓存满标 志信号,当帧缓存中的数据满时,VGA显示模块将此 信号发送给SDRAM(视频存储器)控制器,Wr为VGA 显示模块中的帧缓存写操作信号,Pixel_data—in为读 入到VGA显示模块的帧缓存中的像素数据,该数据 来自SlDRAM(视频存储器),而Eof则表明VGA显示 模块的帧缓存已空,可以重新读入一帧新的像素数据 以供显示。信号HSyn是由VGA显示模块产生的水 平同步信号,发往显示器的VGA接口,信号VSyn是 由VGA显示模块产生的垂直同步信号,发往显示器 的VGA接口,信号R是经D/A转换器分离的像素数 据中的红色基色信号,发往显示器的VGA接口,信号 G是经D/A转换器分离的像素数据中的绿色基色信 号,发往显示器的VGA接口,信号B是经D/A转换器 分离的像素数据中的蓝色基色信号,发往显示器的 VGA接口。因为VGA显示接口处理的RGB信号都 是数字信号,而传统的CRT显示器所采用的都是模拟 接口,D/A转换器完成数字信号到模拟信号的转换工 作。 其中VGA显示时序驱动是完成设计的关键。在 VGA显示控制过程中,完成一帧(整屏)扫描所需要的 时间称为垂直扫描时间,其倒数称为垂直扫描频率,又 称刷新频率,即刷新一屏的频率。前文提到过,工业标 准的Ⅵ3A显示模式为:640*480*16色*60Hz。也 ·+一—-卜-+一—-卜一—卜-——+-一—-卜一+一+ (上接第241页) 如:Hibernate的对象、关系之间的映射工作量很大; Spring和Hibernate的配置文件都很复杂等等。其实, 这正是其灵活之处。因为把各层都完全分离了所以才 易于重用和扩展,因而其灵活映射的配置文件才会很 复杂。 参考文献: [1]Johnson R.Spring Reference Documentation[EB/OL].2004. 就是说,标准VGA显示的场频为60Hz,通过计算可知 其行频(水平同步信号的频率)约为31.5kHz。图6显 示了VGA显示的时序关系。 图6 VGA显示时序关系 4结束语 利用可编程逻辑器件(FPGA/CPLD)可以很方便 地实现数字系统设计,而在Altera的QuartusII软件平 台下,FPGA设计的各个阶段都得到了很好的支持,两 者的有效结合使得数字系统的设计更加方便快捷。基 于FPGA器件的VGA显示控制模块可以实现VGA 显示的各项功能。其性能取决于、1∞L代码的编写 和QuartusII软件工具的综合优化的结果 J。 参考文献: [1]王诚,吴继华,范丽珍,等.Altem FPGA/CPLD设计(基 础篇)[M].北京:人民邮电出版社,2005. [2]PLD/FPGA结构与原理初步[EB/OL].2006.http:// vnⅣw.fpga.com.cn/advance/structures/lut.htm. [3] 求是科技.FPGA数字电子系统设计与开发实例导航 [M].北京:人民邮电出版社,2005. [4]罗健军.VGA实用编程技术[M]. 北京:清华大学出版社, 1995. 。。 [5]XESS Corporation.VGA Generator for the XSABoards[EB/ 0L].2004—10—12.http;//www.xe&5.Com/pro]ects/an 一101204~vgagen.zip. [6]Pedroni V A.Circuit Design with VHDL[M].USA:MIT Press,2004. http:, .spring'framework.org/. [2]Johnson R.Introducing the Spnng Framework[EB/OL]. 2004.http:, .theserverside.corn/. [3]孟庆利.故障管理系统中事件相关性分析的运用[J].世 界电信,2004(10):43—44. [4]黄烟波,张红宇,李建华.基于Struts与Hibernate的J2EE 架构[J].计算机时代;2004(10):29—30. [5] ur D,Crupi J,Malks D.J2EE核心模式[M].北京:机械 工业出版社,2002. 维普资讯 http://www.cqvip.com �

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc