第一章 数字信号处理、计算、程序、 算法和硬线逻辑的基本概念

1.1 数字信号处理

1.2 计算(Computing)

1.3 算法和数据结构

1.4 编程语言和程序

1.5 系统结构和硬线逻辑

1.6 设计方法学

1.7 专用硬线逻辑与微处理器的比较

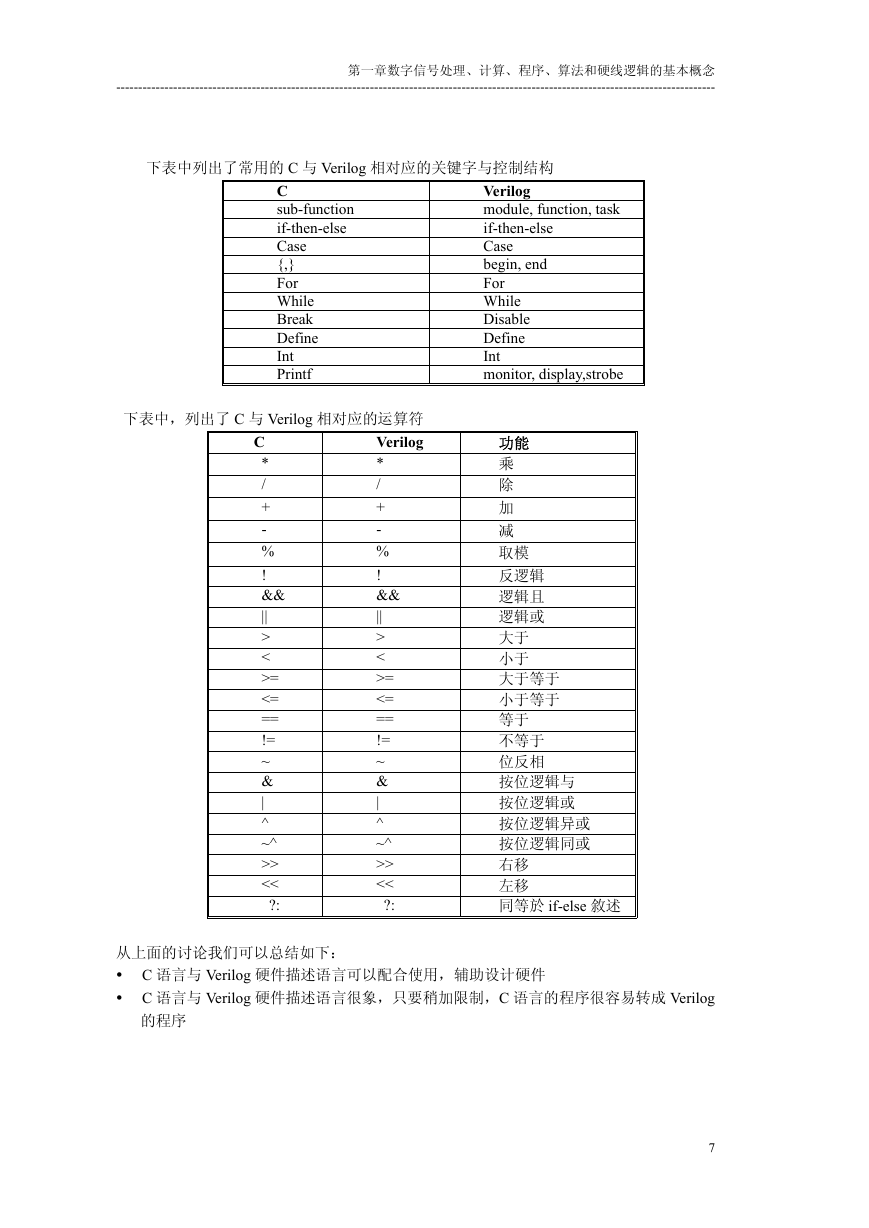

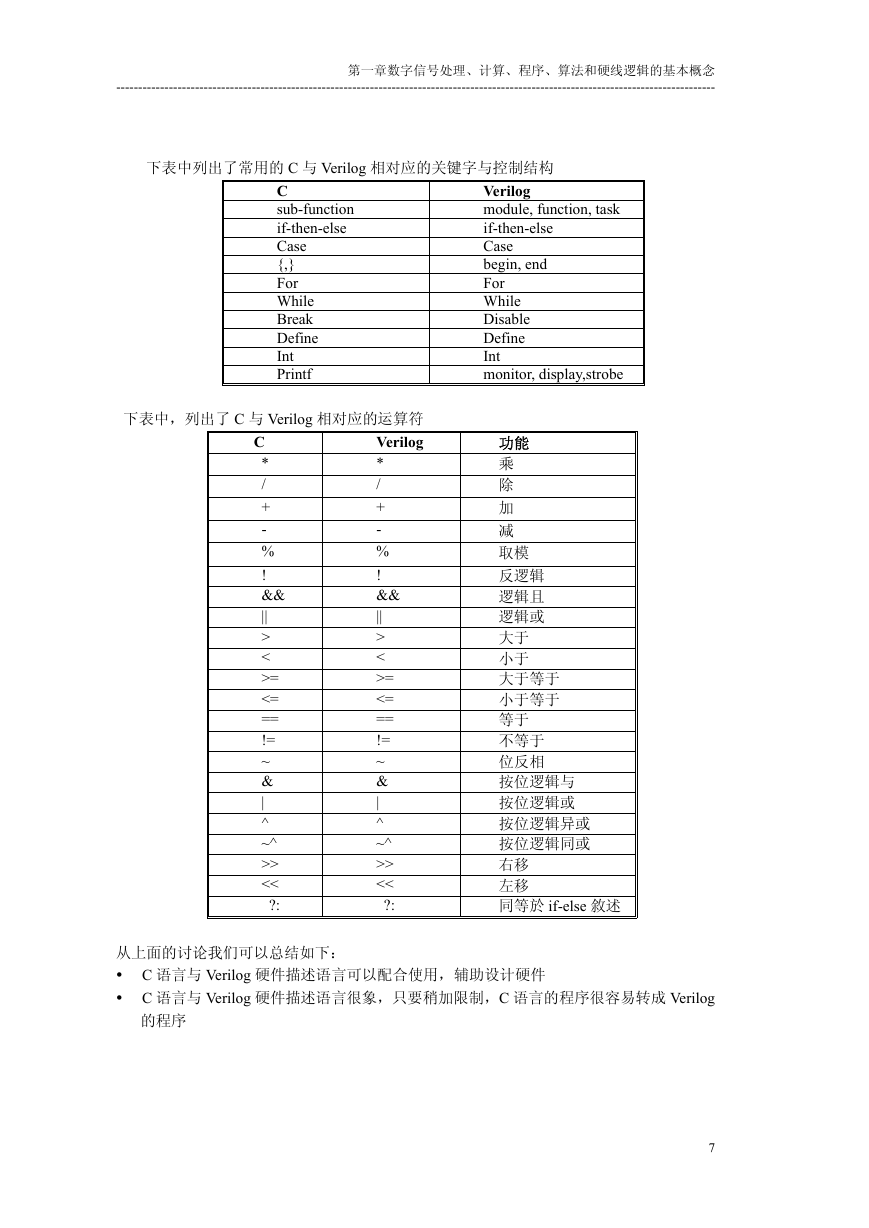

1.8 C 语言与硬件描述语言在算法运算电路设计的关系和作用

第二章 Verilog HDL设计方法概述

2.1.硬件描述语言HDL

2.2.Verilog HDL的历史

2.3.Verilog HDL和 VHDL的比较

2.4. Verilog HDL目前的应用情况和适用的设计

2.5.采用Verilog HDL设计复杂数字电路的优点

2.6.采用硬件描述语言(Verilog HDL)的设计流程简介

2.7.小结

2.8 思考题

第三章 Verilog HDL的基本语法

3.1.简单的Verilog HDL模块

3.1.1.简单的Verilog HDL程序介绍

3.1.2.模块的结构

3.1.3.模块的端口定义

3.1.4.模块内容

3.2.数据类型及其常量、变量

3.2.1.常量

一.数字

二.参数(Parameter)型

3.2.2 变量

一. wire型

二. reg型

三. memory型

3.3. 运算符及表达式

3.3.1.基本的算术运算符

3.3.2.位运算符

3.3.3 逻辑运算符

3.3.4.关系运算符

3.3.5.等式运算符

3.3.6.移位运算符

3.3.7.位拼接运算符

3.3.8.缩减运算符

3.3.9.优先级别

3.3.10.关键词

3.4 赋值语句和块语句

3.4.1 赋值语句

3.4.2 块语句

一.顺序块

二. 并行块

三. 块名

四. 起始时间和结束时间

3.5.条件语句

3.5.1. if_else语句

3.5.2. case语句

3.5.3.由于使用条件语句不当在设计中生成了原本没想到有的锁存器

3.6.循环语句

3.6.1.forever语句

3.6.2.repeat语句

3.6.3.while语句

3.6.4.for语句

3.7.结构说明语句

3.7.1.initial语句

3.7.2.always语句

3.7.3.task和function说明语句

一.task和function说明语句的不同点

二. task说明语句

三.function说明语句

3.8.系统函数和任务

3.8.1.$display和$write任务

3.8.2.系统任务$monitor

3.8.3.时间度量系统函数$time

3.8.4.系统任务$finish

3.8.5.系统任务$stop

3.8.6.系统任务$readmemb和$readmemh

3.8.7.系统任务 $random

3.9.编译预处理

3.9.1.宏定义 `define

3.9.2.“文件包含”处理`include

3.9.3.时间尺度 `timescale

3.9.4.条件编译命令`ifdef、`else、`endif

3.10.小结

3.11.思考题

第四章 不同抽象级别的Verilog HDL模型

4.1.门级结构描述

4.1.1.与非门、或门和反向器等及其说明语法

4.1.2.用门级结构描述D触发器

4.1.3.由已经设计成的模块来构成更高一层的模块

4.1.4 用户定义的原语(UDP)

4.2.Verilog HDL的行为描述建模

4.2.1仅用于产生仿真测试信号的Verilog HDL行为描述建模

4.2.2.Verilog HDL建模在TOP-DOWN设计中的作用和行为建模的可综合性问题

4.3.用Verilog HDL建模进行TOP-DOWN设计的实例

4.4.小结

4.5.思考题

第五章 基本运算逻辑和它们的 Verilog HDL 模型

5.1 加法器

5.2 乘法器

5.3 比较器

5.4 多路器

5.5 总线和总线操作

5.6 流水线(pipeline)

第六章 运算和数据流动控制逻辑

6 6..1 数字逻辑电路的种类:

6.2 数字逻辑电路的构成

6.3 数据流动的控制

6.4 为什么在 Verilog HDL 设计中一定要用同步而不能用异步时序逻辑

第七章 有限状态机和可综合风格的Verilog HDL

7.1.有限状态机

7.1.1用Verilog HDL语言设计可综合的状态机的指导原则

7.1.2典型的状态机实例

7.1.3.综合的一般原则

7.2. 可综合风格的Verilog HDL模块实例

7.2.1.组合逻辑电路设计实例

7.2.2. 时序逻辑电路设计实例

7.2.3.状态机的置位与复位

7.2.3.1. 状态机的异步置位与复位

7.2.3.2. 状态机的同步置位与复位

7.2.4.深入理解阻塞和非阻塞赋值的不同

阻塞赋值

非阻塞赋值

Verilog 模块编程要点

Verilog 的层次化事件队列

自触发 always 块

移位寄存器模型

阻塞赋值及一些简单的例子

原则 1 :时序电路建模时,用非阻塞赋值

原则 2 :锁存器电路建模时,用非阻塞赋值

原则 3 :用 always 块描述组合逻辑时,应采用阻塞赋值语句

原则 4:在同一个 always 块中描述时序和组合逻辑混合电路时,用非阻塞赋值

原则 5:不要在同一个 always 块中同时使用阻塞和非阻塞赋值

原则 6:严禁在多个 always 块中对同一个变量赋值

原则 7:用$strobe 系统任务来显示用非阻塞赋值的变量值

总结:

7.2.5. 复杂时序逻辑电路设计实践

[例1] 一个简单的状态机设计--序列检测器

[例2]EEPROM读写器件的设计

1. 二线制I C CMOS 串行EEPROM的简单介绍

2. I 2 C (Inter Integrated Circuit)总线特征介绍

3. 二线制I 2 C CMOS 串行EEPROM读写操作

1) EEPROM 的写操作(字节编程方式)

2)二线制I C CMOS 串行EEPROM 的读操作

4. EEPROM的Verilog HDL 程序

1) EEPROM的行为模型

2 ) EEPROM读写器的可综合的Verilog HDL模型

3 ) EEPROM的信号源模块和顶层模块

思考题:

第八章 可综合的VerilogHDL设计实例

简化的RISC CPU设计简介

8.1.什么是CPU?

8.2. RISC CPU结构

8.2.1时钟发生器

8.2.2 指令寄存器

8.2.3.累加器

8.2.4.算术运算器

8.2.5.数据控制器

8.2.6.地址多路器

8.2.7.程序计数器

8.2.8.状态控制器

8.2.9.外围模块

8.3. RISC_CPU 操作和时序

8.3.1.系统的复位和启动操作

8.3.2.总线读操作

8.3.3写总线操作

8.4.RISC_CPU寻址方式和指令系统

8.5. RISC_CPU模块的调试

8.5.1. RISC_CPU模块的前仿真

8.5.2. RISC_CPU模块的综合

8.5.3.RISC_CPU模块的优化和布局布线

思考题

第九章 虚拟器件和虚拟接口模型

9.1 虚拟器件和虚拟接口模块的供应商

9.2 虚拟模块的设计

例 1]. 模数转换器 AD7886 仿真模型(虚拟模块)的设计

9.3 虚拟接口模块的实例

[例 1].“商业化”的虚拟模块之一:Intel USART 8251A

[例 2]. “商业化”的虚拟模块之二: Intel 8085a 微处理器的行为描述模块

思考题:

第十章 设计练习进阶

练习一.简单的组合逻辑设计

练习二. 简单时序逻辑电路的设计

练习三. 利用条件语句实现较复杂的时序逻辑电路

练习四. 设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别

练习五. 用 always 块实现较复杂的组合逻辑电路

练习六. 在 Verilog HDL 中使用函数

练习七. 在 Verilog HDL 中使用任务(task)

练习八. 利用有限状态机进行复杂时序逻辑的设计

练习九.利用状态机的嵌套实现层次结构化设计

练习十. 通过模块之间的调用实现自顶向下的设计

练习十一. 简单卷积器的设计

附录一:A/D 转换器的 Verilog HDL 模型和建立模型所需要的技术参数

附录二. 2K*8 位 异步 CMOS 静态 RAM HM-65162 模型

练习十二 利用 SRAM 设计一个 FIFO

参考资料

作者编后记

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc