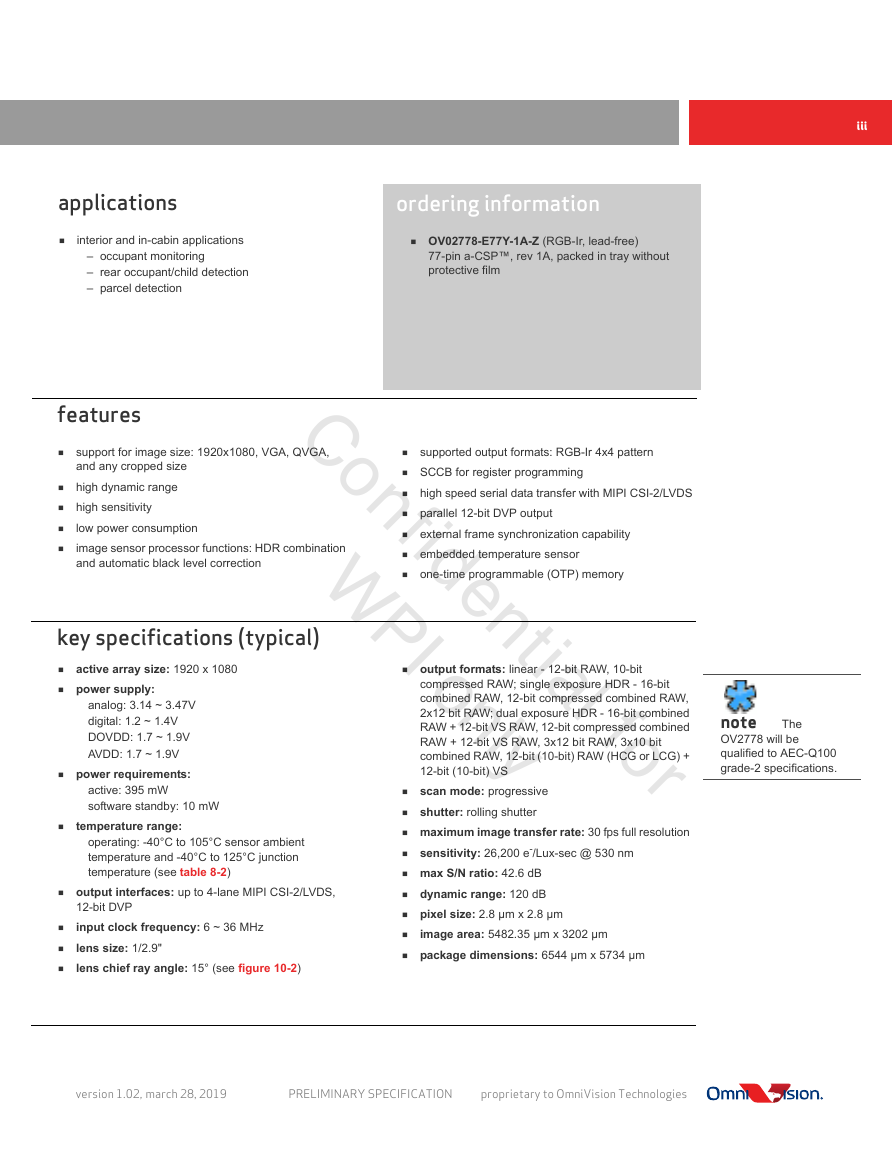

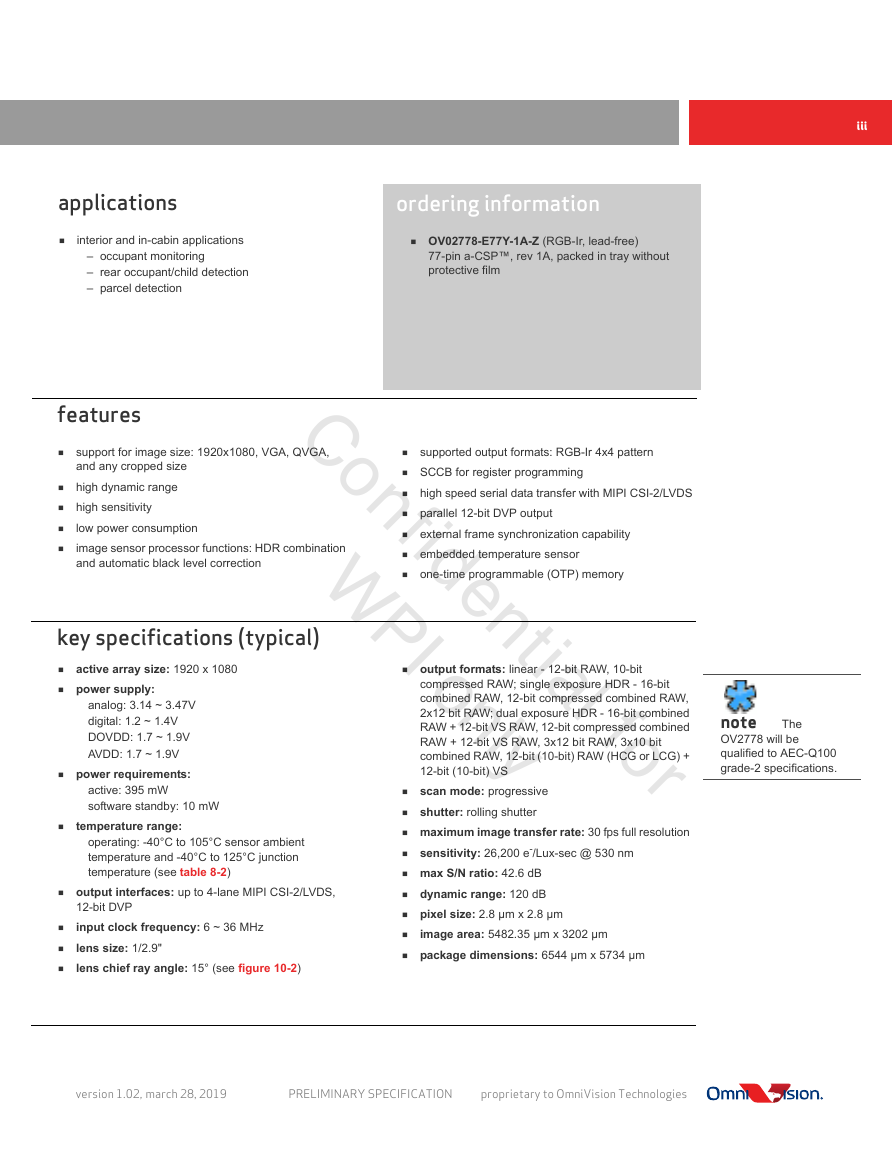

applications

features

key specifications (typical)

table of contents

list of figures

list of tables

1 application system

1.1 overview

1.1.1 typical OV2778 standalone camera

figure 1-1 standalone camera block diagram for automotive applications

1.1.2 typical OV2778 multi-camera system

figure 1-2 multi-camera block diagram

1.2 signal description and pin assignment

figure 1-3 pin diagram

table 1-1 signal descriptions (sheet 1 of 3)

table 1-2 pin states under various conditions (sheet 1 of 2)

table 1-3 GPIO control registers (sheet 1 of 2)

table 1-4 pad equivalent circuit (sheet 1 of 2)

1.3 reference design

figure 1-4 OV2778 MIPI reference schematic

figure 1-5 OV2778 DVP reference schematic

1.3.1 external components

figure 1-6 OV2778 power supplies and recommended external decoupling

1.3.2 power on reset (POR) generation

1.4 power up sequence/ boot sequence

figure 1-7 power on timing diagram

table 1-5 power on timing

1.4.1 power down sequence

1.4.2 operating modes

1.4.3 activation sequence

1.4.4 deactivation sequence

1.4.5 early activation

2 sensor architecture

figure 2-1 OV2778 block diagram

3 image sensor core

figure 3-1 sensor core block diagram

3.1 pixel array structure

figure 3-2 pixel array region RGB-Ir filter layout

figure 3-3 exposures and captures diagram

figure 3-4 integration time diagram

3.2 pixel array access

figure 3-5 pixel array access diagram

3.3 mirror and flip

table 3-1 register setting for mirror

figure 3-6 horizontal mirror and vertical flip samples

3.4 frame timing and maximum frame rate

figure 3-7 row address versus time graph

figure 3-8 frame output timing diagram

table 3-2 supported output formats and frame rates for MIPI/LVDS

table 3-3 supported output formats and frame rates for DVP

table 3-4 timing control registers (sheet 1 of 2)

3.5 exposure control

table 3-5 exposure control registers

3.6 black level calibration (BLC)

3.6.1 advanced operation of the BLC

table 3-6 BLC control registers (sheet 1 of 5)

3.7 PLL

figure 3-9 PLL1 control diagram

figure 3-10 PLL2 control diagram

table 3-7 PLL control registers (sheet 1 of 2)

3.8 temperature sensor

table 3-8 temperature sensor registers

4 image processor

figure 4-1 image processor block diagram

4.1 test pattern

4.1.1 analog color bar overlay

figure 4-2 color bar types

4.1.2 digital test patterns

figure 4-3 vertical bars test pattern

figure 4-4 vertical bars with vertical gradient test pattern

figure 4-5 vertical bars with horizontal gradient test pattern

figure 4-6 vertical bars with diagonal gradient test pattern

figure 4-7 vertical bars with rolling line test pattern

figure 4-8 random image test pattern

figure 4-9 color squares test pattern

figure 4-10 black and white squares test pattern

figure 4-11 chart test pattern

table 4-1 test pattern control registers

4.2 HDR combine principle

figure 4-12 HDR combine principle diagram

table 4-2 combine control registers

5 image output interface

5.1 image output format

table 5-1 image output format summary

table 5-2 interface control register

table 5-3 register setting for different output formats

5.2 data compression algorithm

5.2.1 16b to 12b

figure 5-1 16-bit to 12-bit PWL compression

5.2.2 12b to 10b

figure 5-2 12-bit to 10-bit PWL compression

5.3 HDR output

5.3.1 MIPI

figure 5-3 non-staggered HDR with MIPI virtual channel diagram

figure 5-4 non-staggered HDR with MIPI virtual channel detail diagram

figure 5-5 staggered HDR with MIPI virtual channel diagram

figure 5-6 staggered HDR with MIPI virtual channel detail diagram

figure 5-7 non-staggered HDR without MIPI virtual channel overview diagram

figure 5-8 non-staggered HDR without MIPI virtual channel detail diagram

figure 5-9 staggered HDR without MIPI virtual channel overview diagram

figure 5-10 staggered HDR without MIPI virtual channel detail diagram

table 5-4 supported output formats and frame rates for MIPI

table 5-5 MIPI RAW image data types

figure 5-11 12b linear mode diagram

figure 5-12 10b linear mode diagram

figure 5-13 16b DCG + 12b dual HDR diagram

figure 5-14 12b compressed DCG + 12b dual HDR diagram

figure 5-15 3x12b (3x10b) DCG dual HDR diagram

figure 5-16 12b (10b) RAW DCG (HCG or LCG) + 12b (10b) VS dual HDR diagram

figure 5-17 16b DCG single HDR diagram

figure 5-18 12b compressed DCG single HDR diagram

figure 5-19 2x12b DCG single HDR diagram

table 5-6 MIPI control registers (sheet 1 of 10)

5.3.2 LVDS

figure 5-20 staggered HDR with LVDS dedicated lane (4-lane) diagram

figure 5-21 staggered HDR with LVDS dedicated lane (2-lane) diagram

table 5-7 supported output formats and frame rates for LVDS

figure 5-22 12 bits linear mode diagram

figure 5-23 10 bits linear mode diagram

figure 5-24 16b DCG + 12b dual HDR diagram

figure 5-25 12b compressed DCG + 12b dual HDR diagram

figure 5-26 3x12b (3x10b) DCG dual HDR diagram

figure 5-27 12b (10b) RAW DCG (HCG or LCG) + 12b (10b) VS dual HDR diagram

figure 5-28 16b DCG single HDR diagram

figure 5-29 12b compressed DCG single HDR diagram

figure 5-30 2x12b DCG single HDR diagram

table 5-8 LVDS control registers

5.3.3 DVP

figure 5-31 DVP diagram

figure 5-32 DVP setup/hold time diagram

table 5-9 DVP setup/hold time

figure 5-33 DVP timing diagram

figure 5-34 staggered HDR with DVP diagram

table 5-10 supported output formats and frame rates for DVP

figure 5-35 12 bits linear mode diagram

figure 5-36 10 bits linear mode diagram

figure 5-37 12b RAW DCG (HCG or LCG) + 12b VS diagram

figure 5-38 single exposure HDR diagram

figure 5-39 2x12b DCG single HDR diagram

table 5-11 DVP control registers (sheet 1 of 2)

5.4 instructions for backend control

5.4.1 VS data path delay

figure 5-40 sensor frame control signals diagram

table 5-12 VS data path delay register s

5.5 register writing

5.5.1 suggestion for writing register value just after VSYNC or FS

5.6 embedded data

5.6.1 embedded data format at output

figure 5-41 embedded data layout diagram

table 5-13 embedded data registers

5.7 group hold

table 5-14 group hold control registers (sheet 1 of 2)

5.8 cyclic redundancy check

5.8.1 embedded data

5.8.2 SCCB communication

table 5-15 SCCB CRC registers

6 SCCB interface

6.1 SCCB timing

figure 6-1 SCCB interface timing

table 6-1 SCCB interface timing specifications

6.2 direct access mode

6.2.1 message format

figure 6-2 message type

6.2.2 read / write operation

figure 6-3 SCCB single read from random location

figure 6-4 SCCB single read from current location

figure 6-5 SCCB sequential read from random location

figure 6-6 SCCB sequential read from current location

figure 6-7 SCCB single write to random location

figure 6-8 SCCB sequential write to random location

7 OTP memory

7.1 OTP memory map

table 7-1 OTP memory map overview

8 operating specifications

8.1 absolute maximum ratings

table 8-1 absolute maximum ratings

8.2 functional temperature

table 8-2 functional temperature

8.3 DC characteristics

table 8-3 DC characteristics (-40°C < TJ < 125°C)

8.4 AC characteristics

table 8-4 timing characteristics

9 mechanical specifications

9.1 physical specifications

figure 9-1 package specifications

table 9-1 package dimensions

9.2 IR reflow specifications

figure 9-2 IR reflow ramp rate requirements

table 9-2 reflow conditions

9.3 protective film specifications

figure 9-3 protective film specifications

10 optical specifications

10.1 sensor array center

figure 10-1 sensor array center

10.2 lens chief ray angle (CRA)

figure 10-2 chief ray angle (CRA)

table 10-1 CRA versus image height plot (sheet 1 of 2)

appendix A register table

A.1 module name and address range

A.2 device control registers

revision history

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc