1

2

3

4

5

6

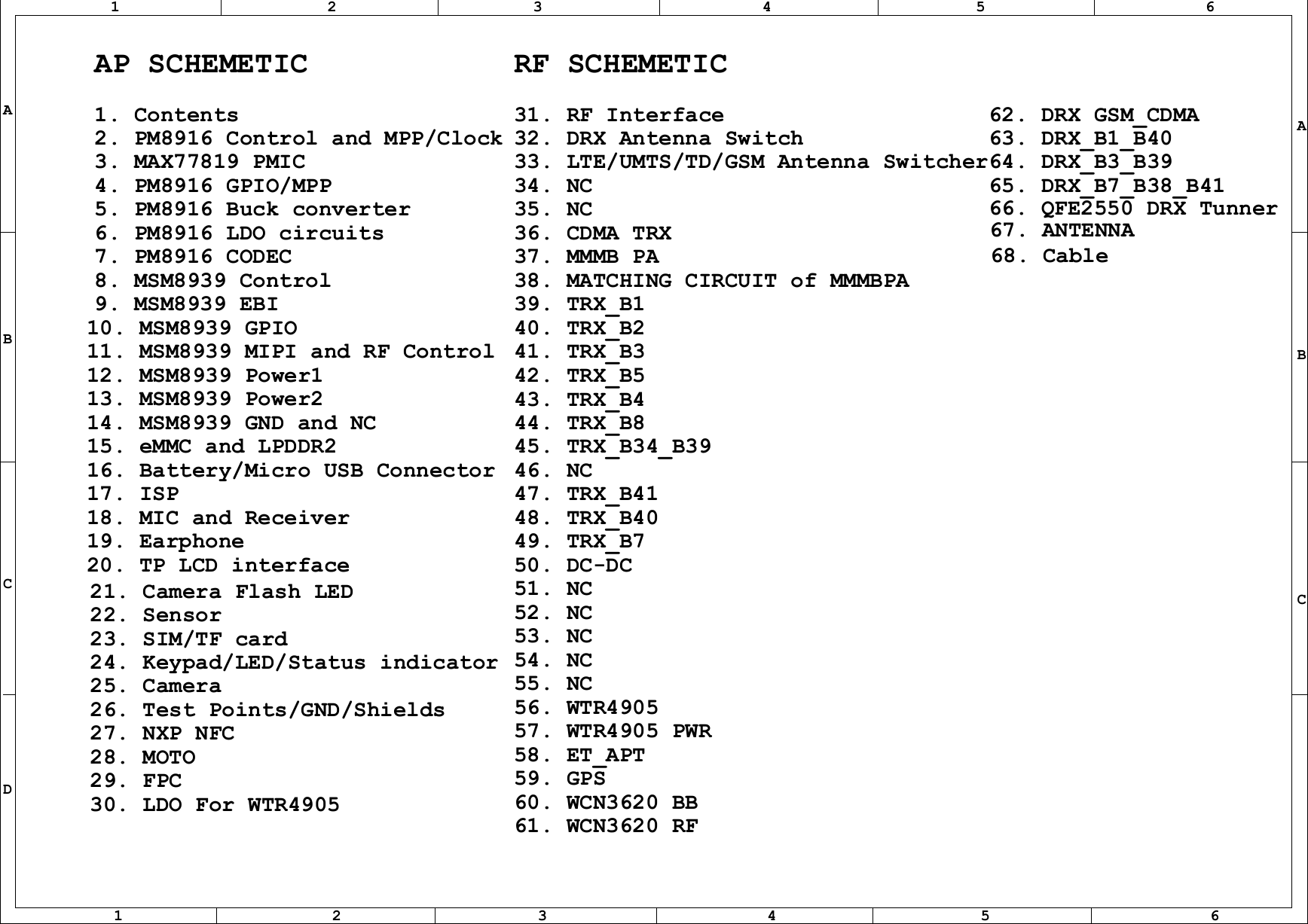

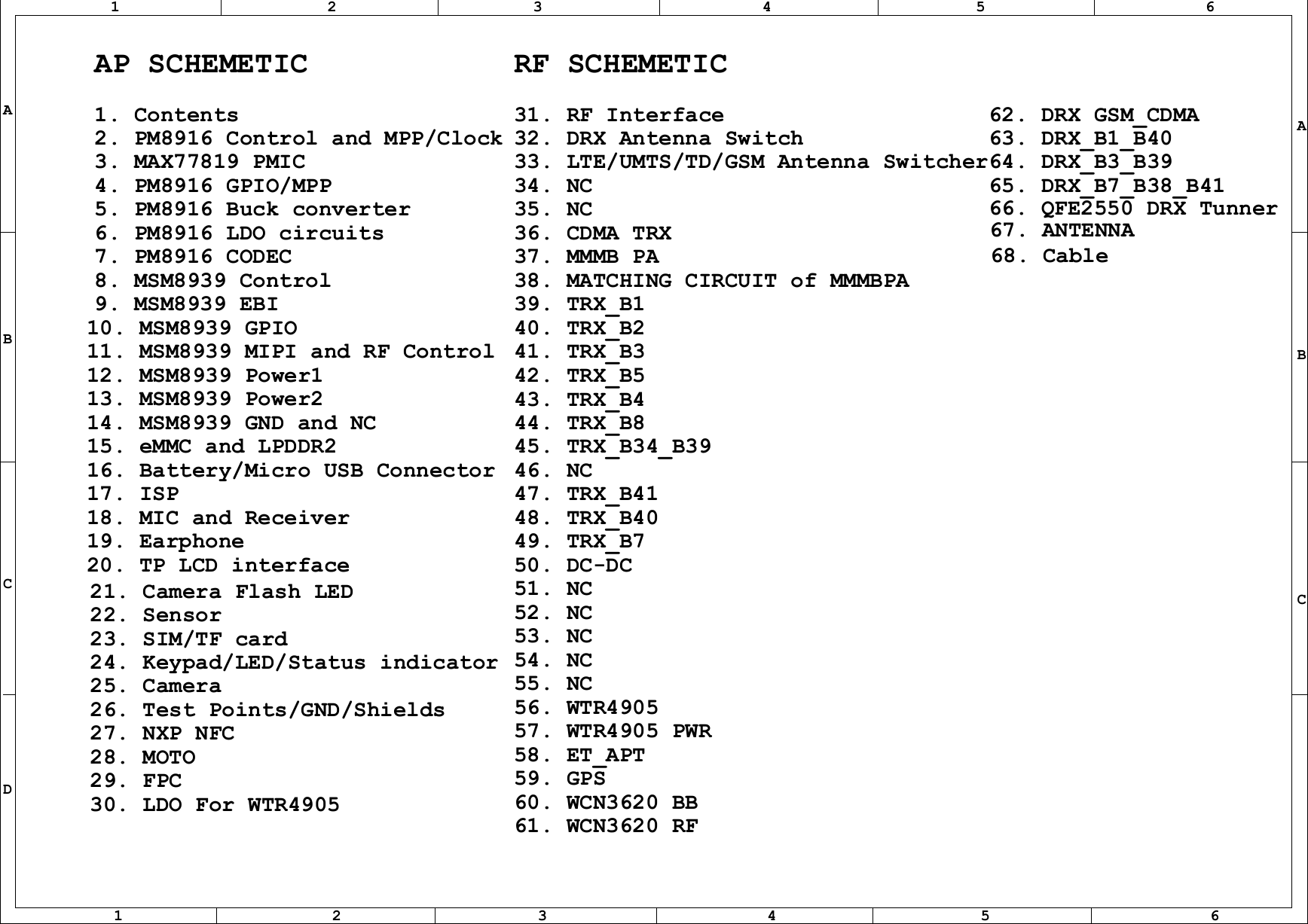

AP SCHEMETIC

RF SCHEMETIC

A

B

C

D

1. Contents

2. PM8916 Control and MPP/Clock

3. MAX77819 PMIC

4. PM8916 GPIO/MPP

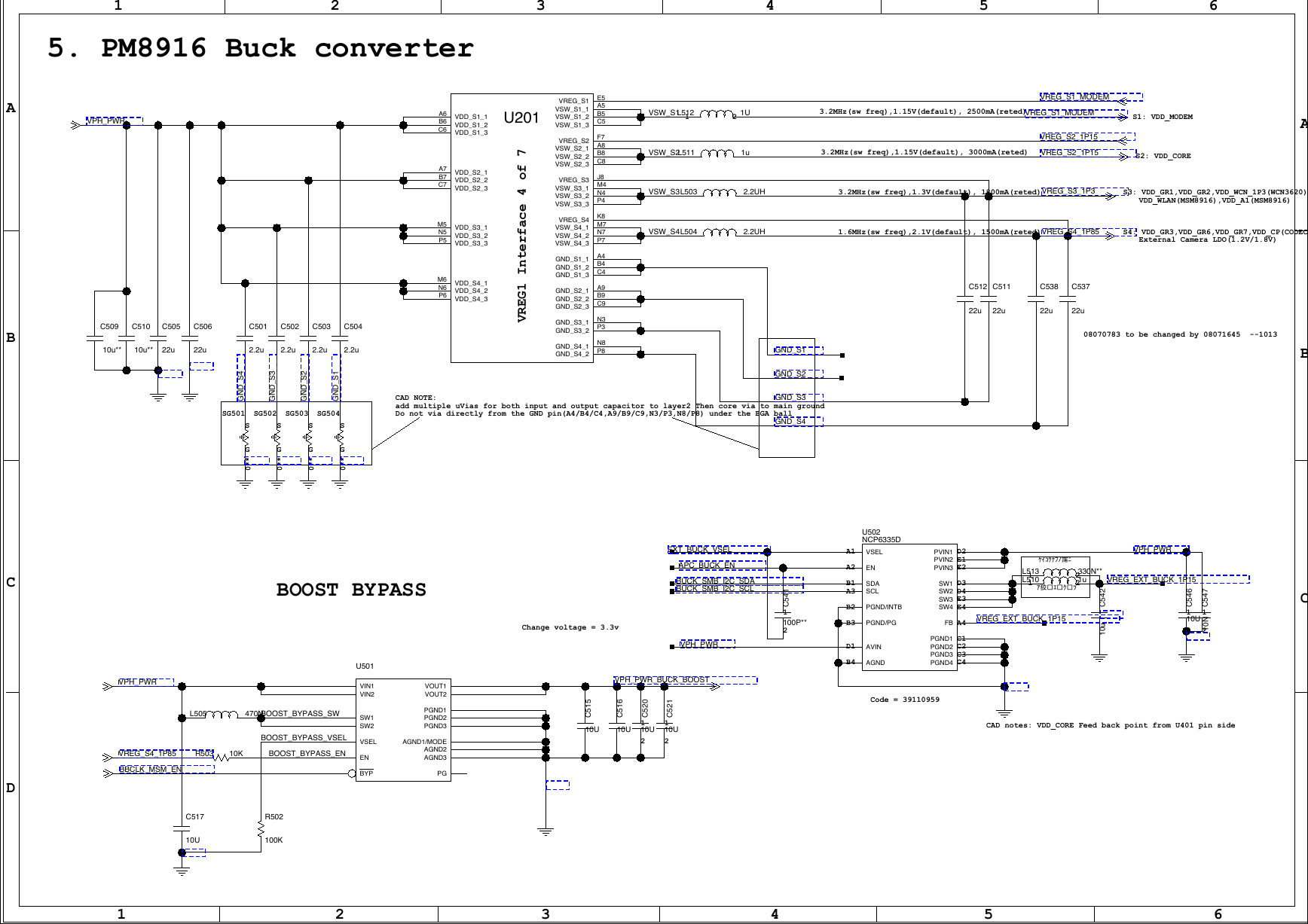

5. PM8916 Buck converter

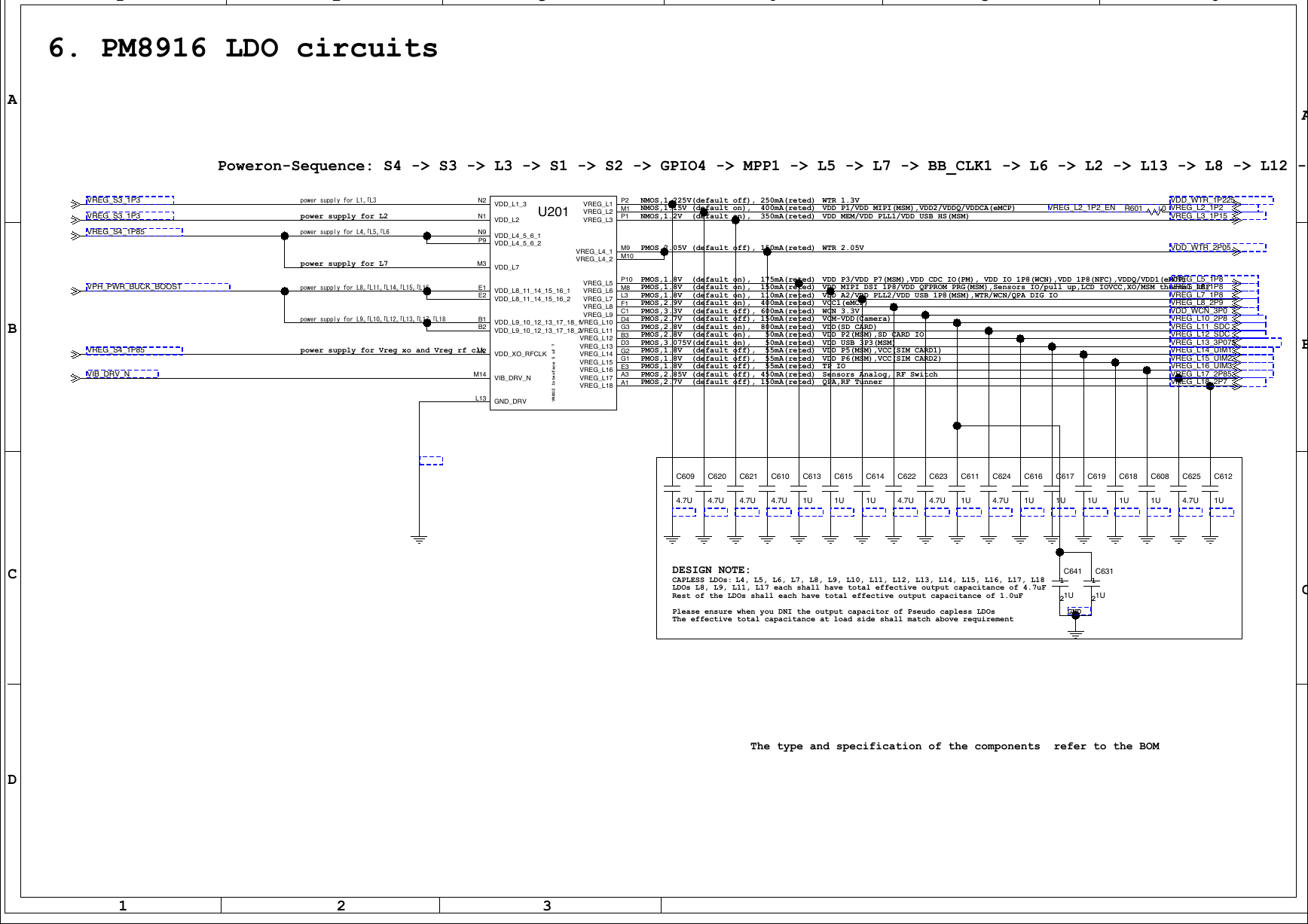

6. PM8916 LDO circuits

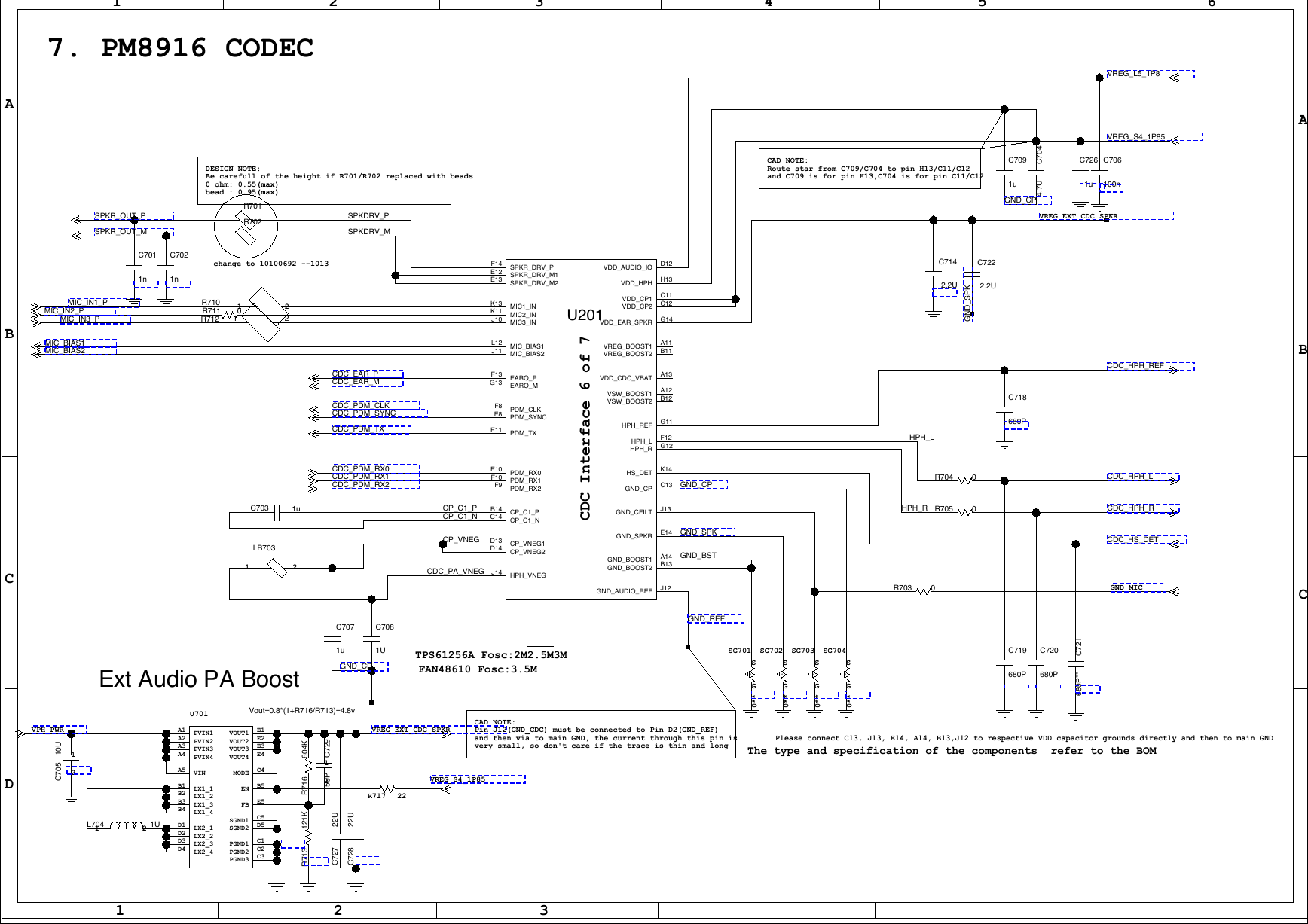

7. PM8916 CODEC

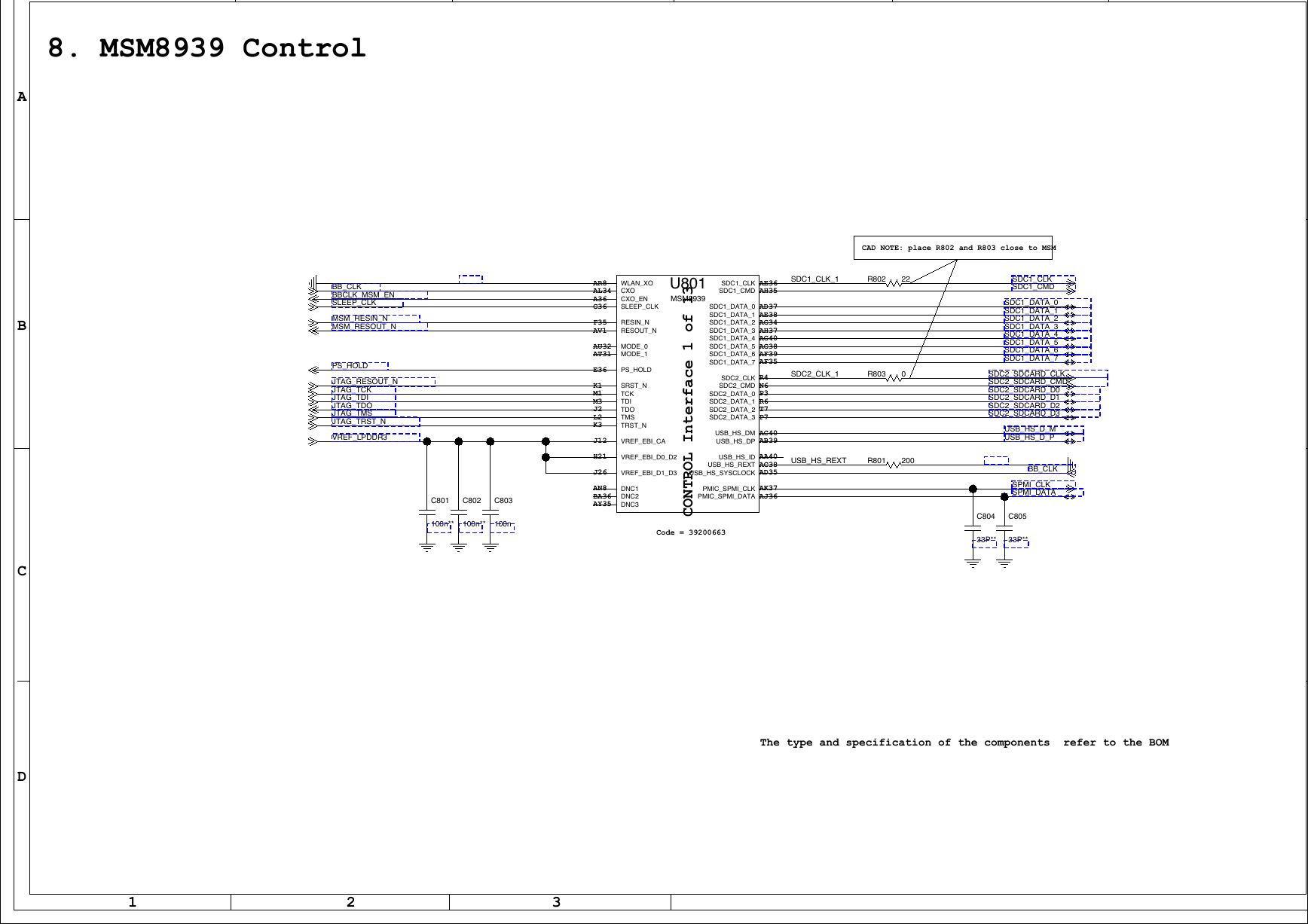

8. MSM8939 Control

9. MSM8939 EBI

10. MSM8939 GPIO

11. MSM8939 MIPI and RF Control

12. MSM8939 Power1

13. MSM8939 Power2

14. MSM8939 GND and NC

15. eMMC and LPDDR2

16. Battery/Micro USB Connector

17. ISP

18. MIC and Receiver

19. Earphone

20. TP LCD interface

21. Camera Flash LED

22. Sensor

23. SIM/TF card

24. Keypad/LED/Status indicator

25. Camera

26. Test Points/GND/Shields

27. NXP NFC

28. MOTO

29. FPC

30. LDO For WTR4905

62. DRX GSM_CDMA

63. DRX_B1_B40

64. DRX_B3_B39

65. DRX_B7_B38_B41

66. QFE2550 DRX Tunner

67. ANTENNA

68. Cable

31. RF Interface

32. DRX Antenna Switch

33. LTE/UMTS/TD/GSM Antenna Switcher

34. NC

35. NC

36. CDMA TRX

37. MMMB PA

38. MATCHING CIRCUIT of MMMBPA

39. TRX_B1

40. TRX_B2

41. TRX_B3

42. TRX_B5

43. TRX_B4

44. TRX_B8

45. TRX_B34_B39

46. NC

47. TRX_B41

48. TRX_B40

49. TRX_B7

50. DC-DC

51. NC

52. NC

53. NC

54. NC

55. NC

56. WTR4905

57. WTR4905 PWR

58. ET_APT

59. GPS

60. WCN3620 BB

61. WCN3620 RF

A

B

C

1

2

3

4

5

6

�

1

2

3

4

5

6

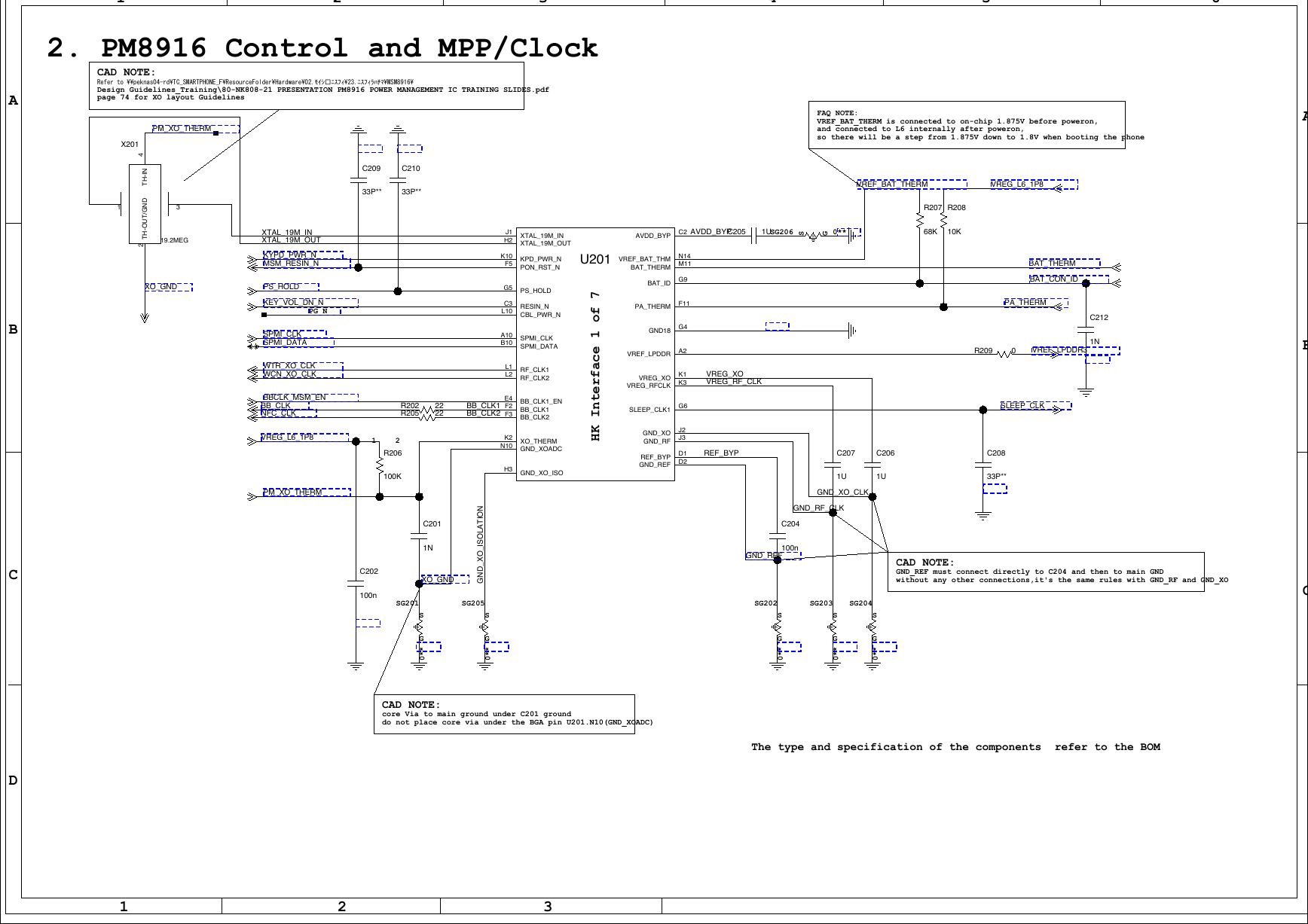

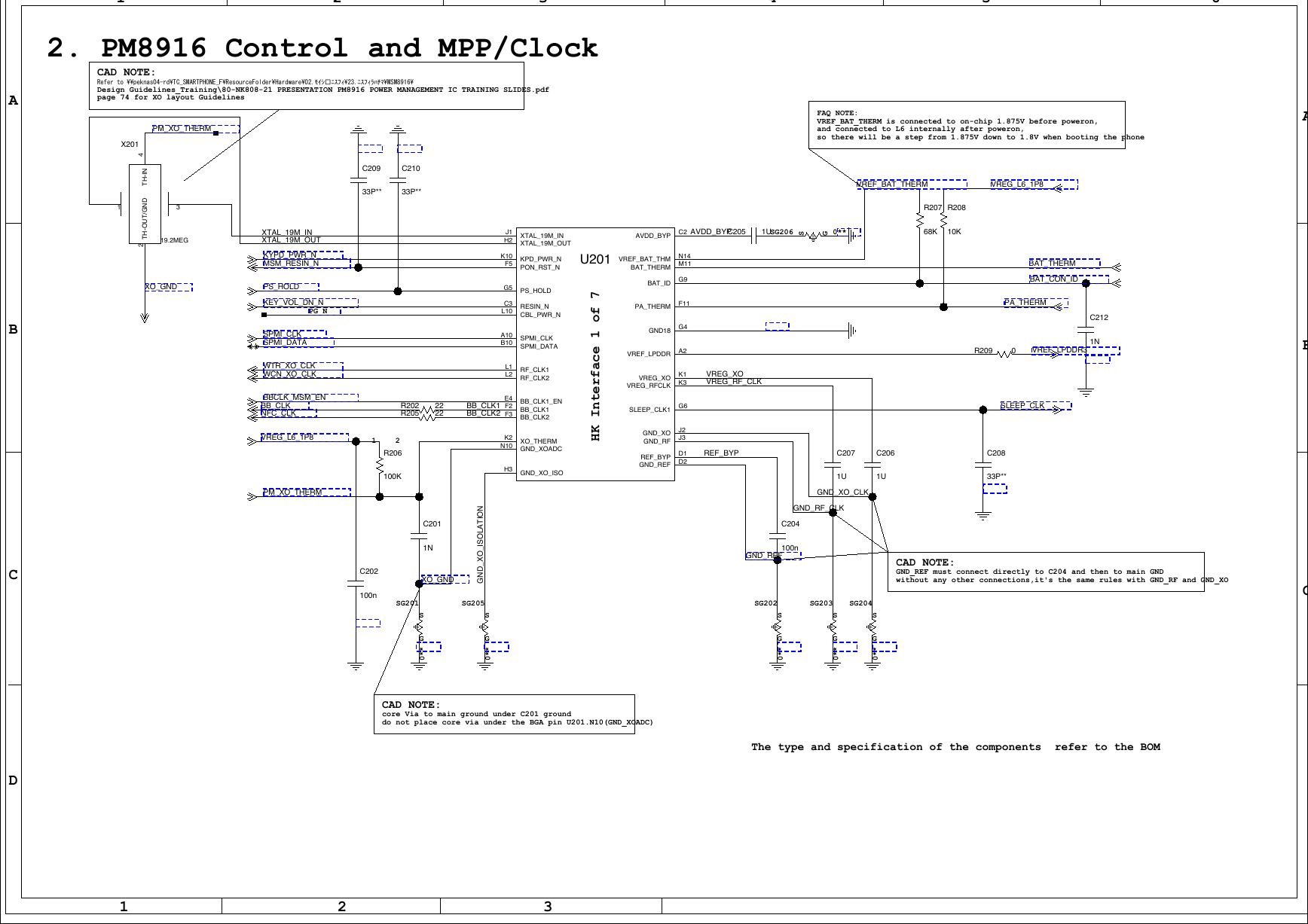

2. PM8916 Control and MPP/Clock

CAD NOTE:

Refer to ¥¥peknas04-rd¥TC_SMARTPHONE_F¥ResourceFolder¥Hardware¥02.モイシニスフィ¥23.ニスフィラハチマ¥MSM8916¥

Design Guidelines_Training\80-NK808-21 PRESENTATION PM8916 POWER MANAGEMENT IC TRAINING SLIDES.pdf

page 74 for XO layout Guidelines

PM_XO_THERM

X201

4

N

I

-

H

T

C209

C210

33P**

33P**

FAQ NOTE:

VREF_BAT_THERM is connected to on-chip 1.875V before poweron,

and connected to L6 internally after poweron,

so there will be a step from 1.875V down to 1.8V when booting the phone

J1 XTAL_19M_IN

H2

XTAL_19M_OUT

AVDD_BYP

C2

AVDD_BYP

C205

1U

SG206 S G

S

VREF_BAT_THERM

VREG_L6_1P8

0**

R207

R208

68K

10K

1

/

D

N

G

T

U

O

H

T

-

2

3

19.2MEG

XO_GND

XTAL_19M_IN

XTAL_19M_OUT

KYPD_PWR_N

MSM_RESIN_N

PS_HOLD

KEY_VOL_DN_N

PG_N

SPMI_CLK

SPMI_DATA

WTR_XO_CLK

WCN_XO_CLK

BBCLK_MSM_EN

BB_CLK

NFC_CLK

VREG_L6_1P8

PM_XO_THERM

K10

F5

G5

C3

L10

A10

B10

L1

L2

E4

F2

F3

K2

N10

H3

KPD_PWR_N

PON_RST_N

U201

VREF_BAT_THM

BAT_THERM

7

f

o

1

e

c

a

f

r

e

t

n

I

K

H

PS_HOLD

RESIN_N

CBL_PWR_N

SPMI_CLK

SPMI_DATA

RF_CLK1

RF_CLK2

BB_CLK1_EN

BB_CLK1

BB_CLK2

XO_THERM

GND_XOADC

GND_XO_ISO

BAT_ID

PA_THERM

GND18

VREF_LPDDR

VREG_XO

VREG_RFCLK

SLEEP_CLK1

GND_XO

GND_RF

REF_BYP

GND_REF

N14

M11

G9

F11

G4

A2

K1

K3

G6

J2

J3

D1

D2

R202

R205

22

22

BB_CLK1

BB_CLK2

1

2

R206

100K

C201

1N

XO_GND

I

N

O

T

A

L

O

S

I

_

O

X

_

D

N

G

C202

100n

BAT_THERM

BAT_CON_ID

PA_THERM

C212

1N

R209

0

VREF_LPDDR3

SLEEP_CLK

C208

33P**

CAD NOTE:

GND_REF must connect directly to C204 and then to main GND

without any other connections,it's the same rules with GND_RF and GND_XO

VREG_XO

VREG_RF_CLK

REF_BYP

C207

C206

1U

1U

GND_XO_CLK

GND_RF_CLK

C204

100n

GND_REF

SG201

SG205

SG202

SG203

SG204

S

S

G

*

*

0

S

S

G

*

*

0

S

S

G

*

*

0

S

S

S

S

G

*

*

0

G

*

*

0

CAD NOTE:

core Via to main ground under C201 ground

do not place core via under the BGA pin U201.N10(GND_XOADC)

The type and specification of the components refer to the BOM

A

B

C

A

B

C

D

1

2

3

�

A

B

C

D

1

2

3

4

5

6

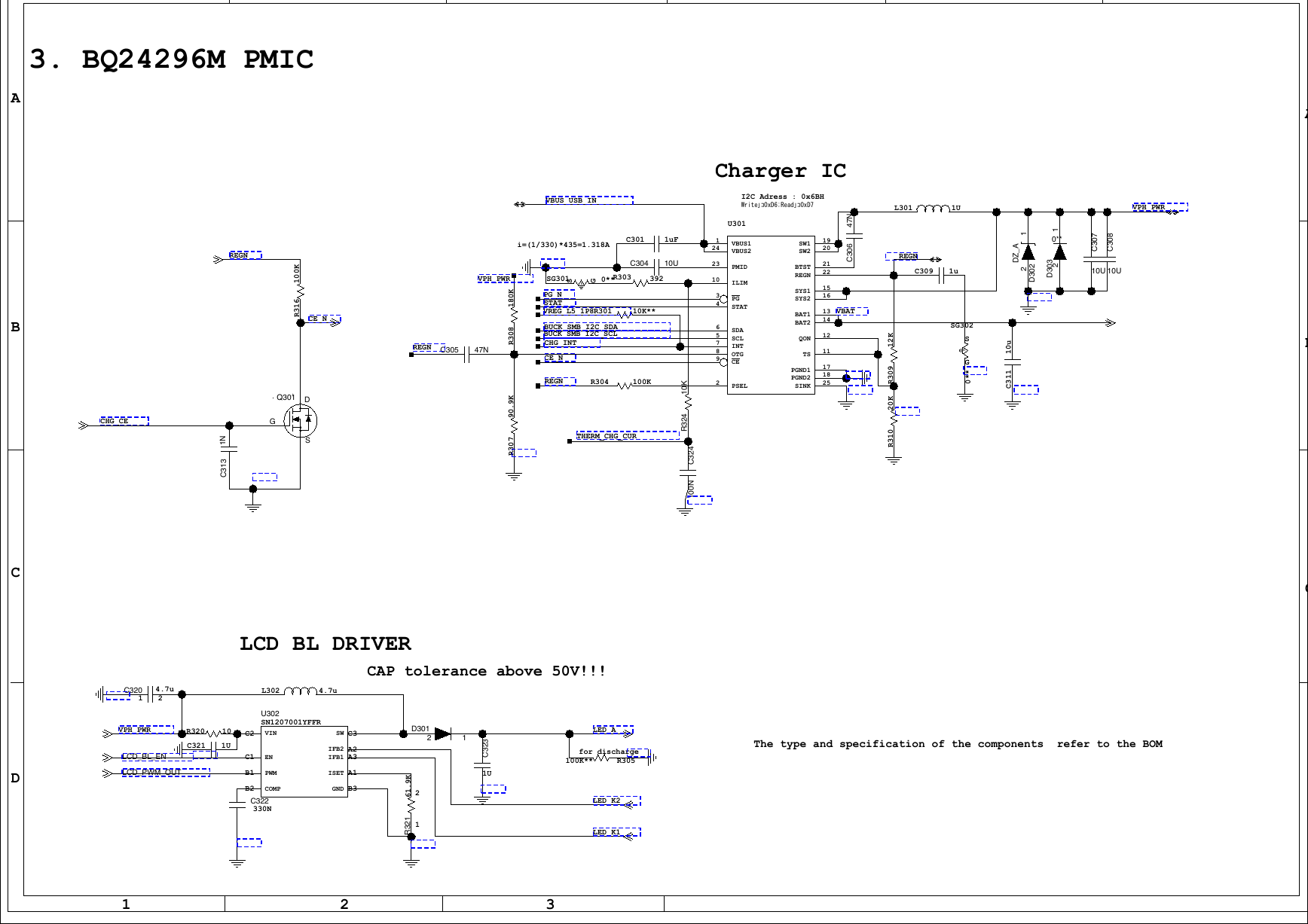

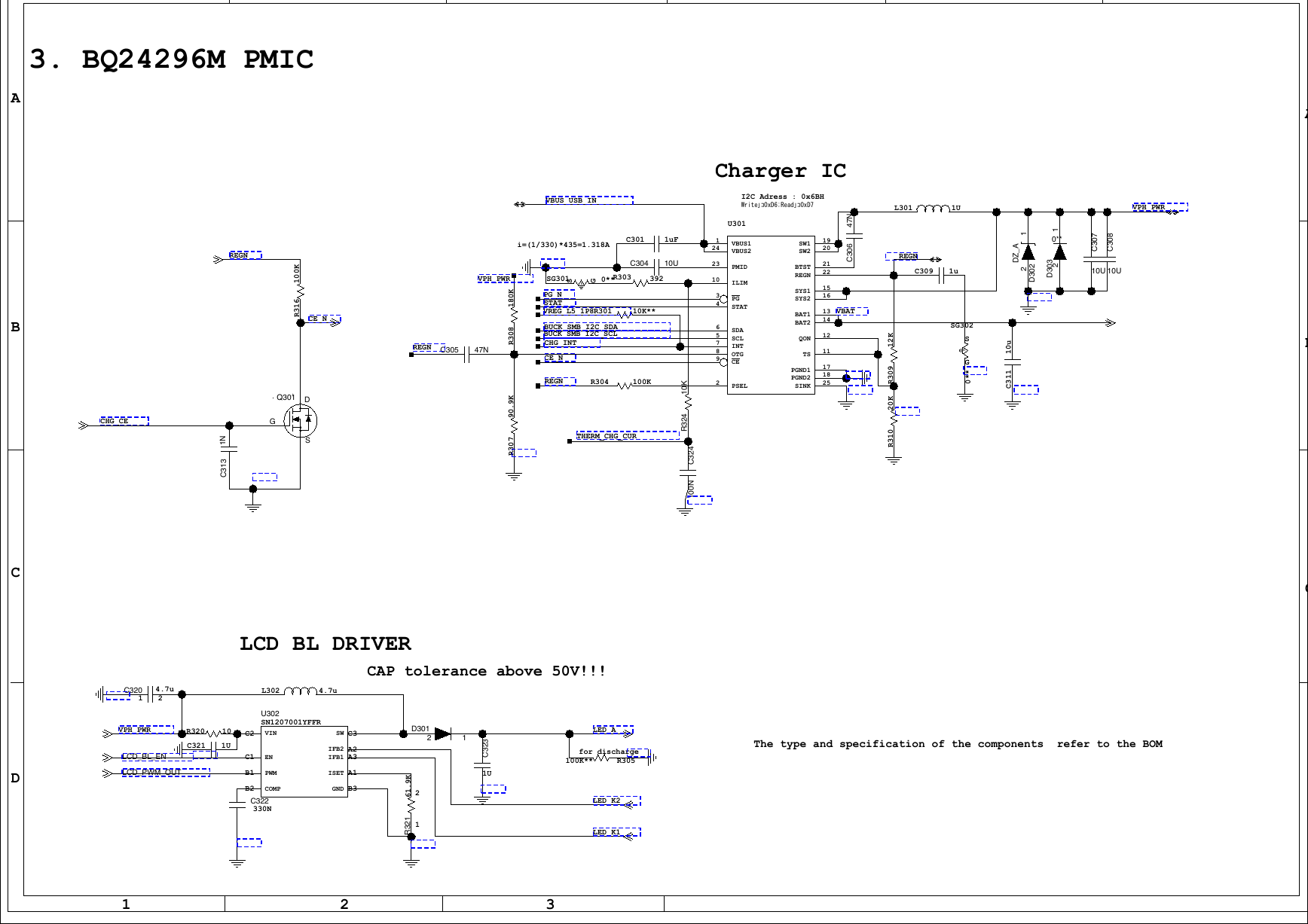

3. BQ24296M PMIC

REGN

K

0

0

1

6

1

3

R

CE_N

CHG_CE

Q301

D

G

S

N

1

3

1

3

C

VBUS_USB_IN

i=(1/330)*435=1.318A

C301

1uF

C304

10U

VPH_PWR

SG301S G

S

0**R303

392

REGN

C305

47N

PG_N

STAT

VREG_L5_1P8

R301

BUCK_SMB_I2C_SDA

BUCK_SMB_I2C_SCL

CHG_INT

10K**

CE_N

REGN

R304

100K

THERM_CHG_CUR

K

0

8

1

8

0

3

R

K

9

.

0

9

7

0

3

R

K

0

1

4

2

3

R

4

2

3

C

N

0

0

1

Charger IC

I2C Adress : 0x6BH

Write」コ0xD6;Read」コ0xD7

U301

VBUS1

VBUS2

PMID

ILIM

PG

STAT

SDA

SCL

INT

OTG

CE

PSEL

1

24

23

10

3

4

6

5

7

8

9

2

N

7

4

6

0

3

C

VBAT

SW1

SW2

BTST

REGN

SYS1

SYS2

BAT1

BAT2

QON

TS

PGND1

PGND2

SINK

19

20

21

22

15

16

13

14

12

11

17

18

25

L301

1U

VPH_PWR

REGN

C309

1u

1

A

_

Z

D

2

2

0

3

D

1

0**

2

3

0

3

D

7

0

3

C

8

0

3

C

10U

10U

SG302

S

S

G

*

*

0

u

0

1

1

1

3

C

K

2

1

9

0

3

R

K

0

2

0

1

3

R

A

B

C

LCD BL DRIVER

CAP tolerance above 50V!!!

C320

1

4.7u

2

L302

4.7u

VPH_PWR

R320

C321

10

1U

LCD_BL_EN

LCD_PWM_OUT

U302

SN1207001YFFR

VIN

EN

PWM

COMP

C2

C1

B1

B2

C322

330N

SW

C3

IFB2

IFB1

A2

A3

ISET

A1

GND

B3

3

2

3

C

1U

D301

2

1

K

9

.

1

6

1

2

3

R

2

1

LED_A

for discharge

R305

100K**

LED_K2

LED_K1

1

2

3

The type and specification of the components refer to the BOM

�

A

B

C

D

1

2

3

4

5

6

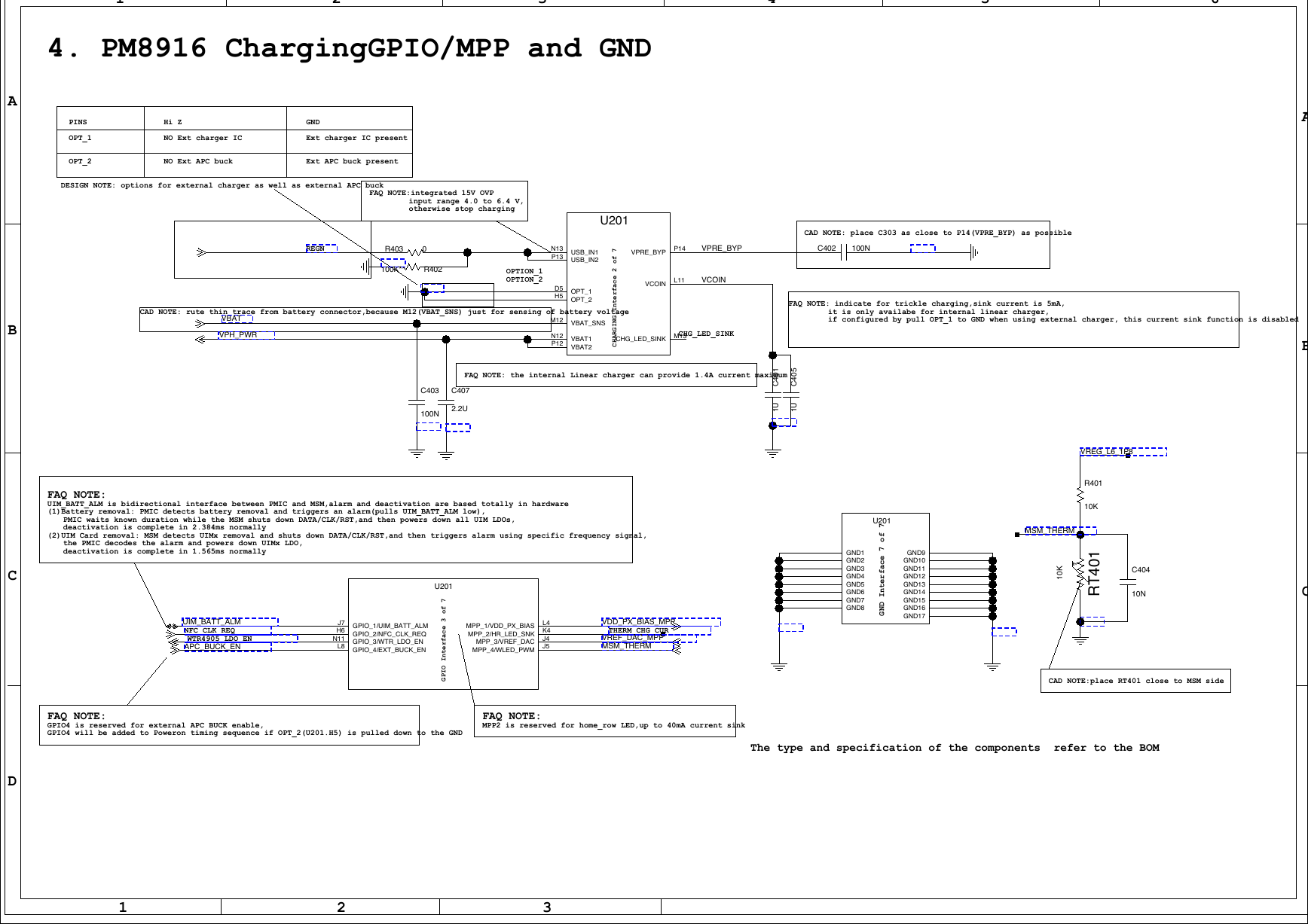

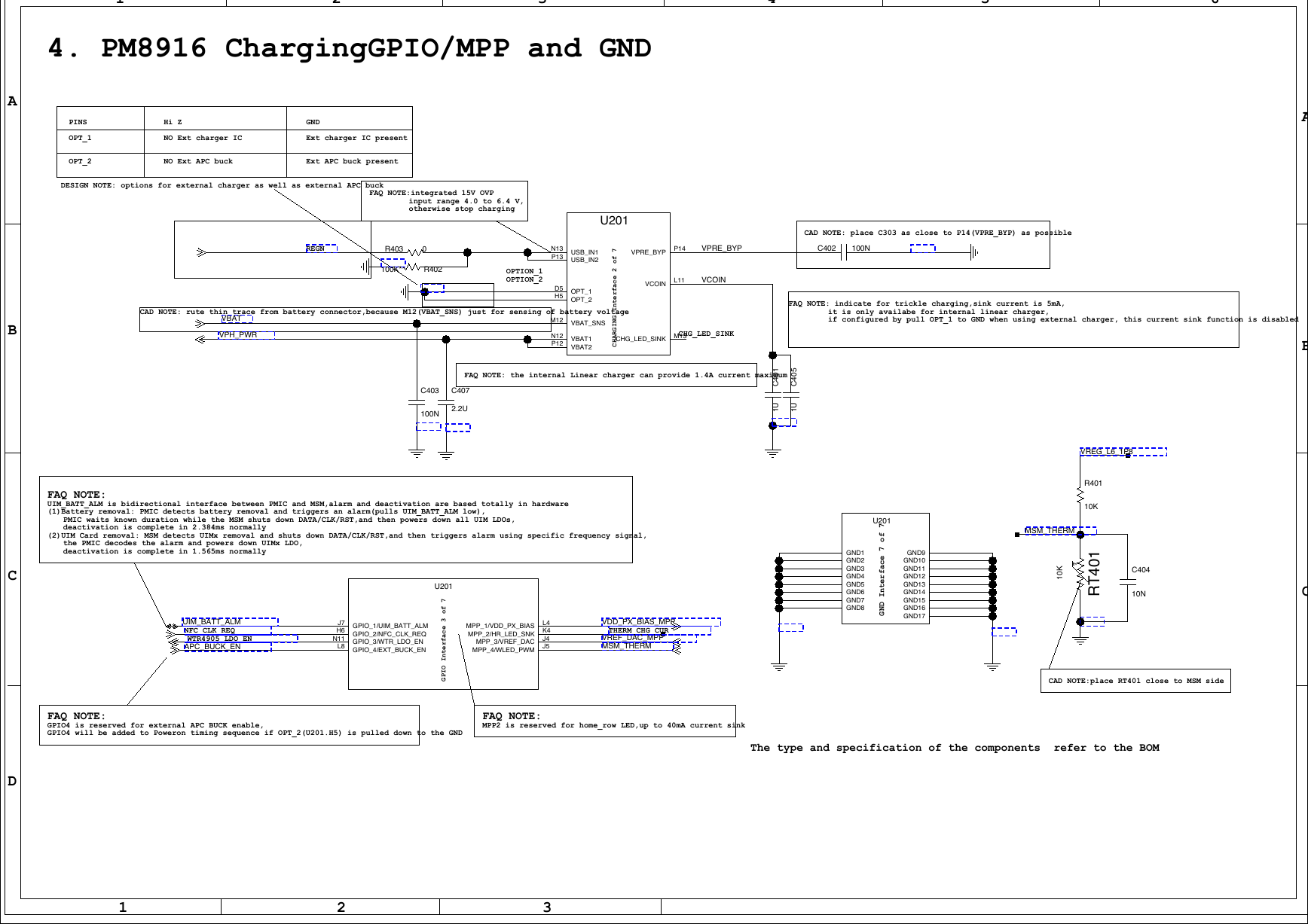

4. PM8916 ChargingGPIO/MPP and GND

PINS

OPT_1

OPT_2

Hi Z

GND

NO Ext charger IC

Ext charger IC present

NO Ext APC buck

Ext APC buck present

DESIGN NOTE: options for external charger as well as external APC buck

FAQ NOTE:integrated 15V OVP

input range 4.0 to 6.4 V,

otherwise stop charging

U201

CAD NOTE: place C303 as close to P14(VPRE_BYP) as possible

CAD NOTE: rute thin trace from battery connector,because M12(VBAT_SNS) just for sensing of battery voltage

VBAT

VPH_PWR

FAQ NOTE: indicate for trickle charging,sink current is 5mA,

it is only availabe for internal linear charger,

if configured by pull OPT_1 to GND when using external charger, this current sink function is disabled

CHG_LED_SINK

M13

REGN

R403

0

100K**

R402

OPTION_1

OPTION_2

N13 USB_IN1

P13

USB_IN2

D5

H5

OPT_1

OPT_2

VPRE_BYP

P14

VPRE_BYP

C402

100N

VCOIN

L11

VCOIN

7

f

o

2

e

c

a

f

r

e

t

n

I

G

N

I

G

R

A

H

C

M12

N12

P12

VBAT_SNS

VBAT1

VBAT2

CHG_LED_SINK

FAQ NOTE: the internal Linear charger can provide 1.4A current maximum

1

0

4

C

5

0

4

C

C403

C407

2.2U

100N

FAQ NOTE:

UIM_BATT_ALM is bidirectional interface between PMIC and MSM,alarm and deactivation are based totally in hardware

(1)Battery removal: PMIC detects battery removal and triggers an alarm(pulls UIM_BATT_ALM low),

PMIC waits known duration while the MSM shuts down DATA/CLK/RST,and then powers down all UIM LDOs,

deactivation is complete in 2.384ms normally

(2)UIM Card removal: MSM detects UIMx removal and shuts down DATA/CLK/RST,and then triggers alarm using specific frequency signal,

the PMIC decodes the alarm and powers down UIMx LDO,

deactivation is complete in 1.565ms normally

UIM_BATT_ALM

NFC_CLK_REQ

WTR4905_LDO_EN

APC_BUCK_EN

J7 GPIO_1/UIM_BATT_ALM

H6

GPIO_2/NFC_CLK_REQ

N11

GPIO_3/WTR_LDO_EN

L8

GPIO_4/EXT_BUCK_EN

U201

7

f

o

3

e

c

a

f

r

e

t

n

I

O

I

P

G

MPP_1/VDD_PX_BIAS

MPP_2/HR_LED_SNK

MPP_3/VREF_DAC

MPP_4/WLED_PWM

L4

K4

J4

J5

VDD_PX_BIAS_MPP

THERM_CHG_CUR

VREF_DAC_MPP

MSM_THERM

U

1

U

1

U201

7

f

o

7

e

c

a

f

r

e

t

n

I

D

N

G

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

VREG_L6_1P8

R401

10K

1

0

4

T

R

MSM_THERM

T

K

0

1

C404

10N

CAD NOTE:place RT401 close to MSM side

FAQ NOTE:

GPIO4 is reserved for external APC BUCK enable,

GPIO4 will be added to Poweron timing sequence if OPT_2(U201.H5) is pulled down to the GND

FAQ NOTE:

MPP2 is reserved for home_row LED,up to 40mA current sink

The type and specification of the components refer to the BOM

1

2

3

A

B

C

�

1

2

3

4

5

6

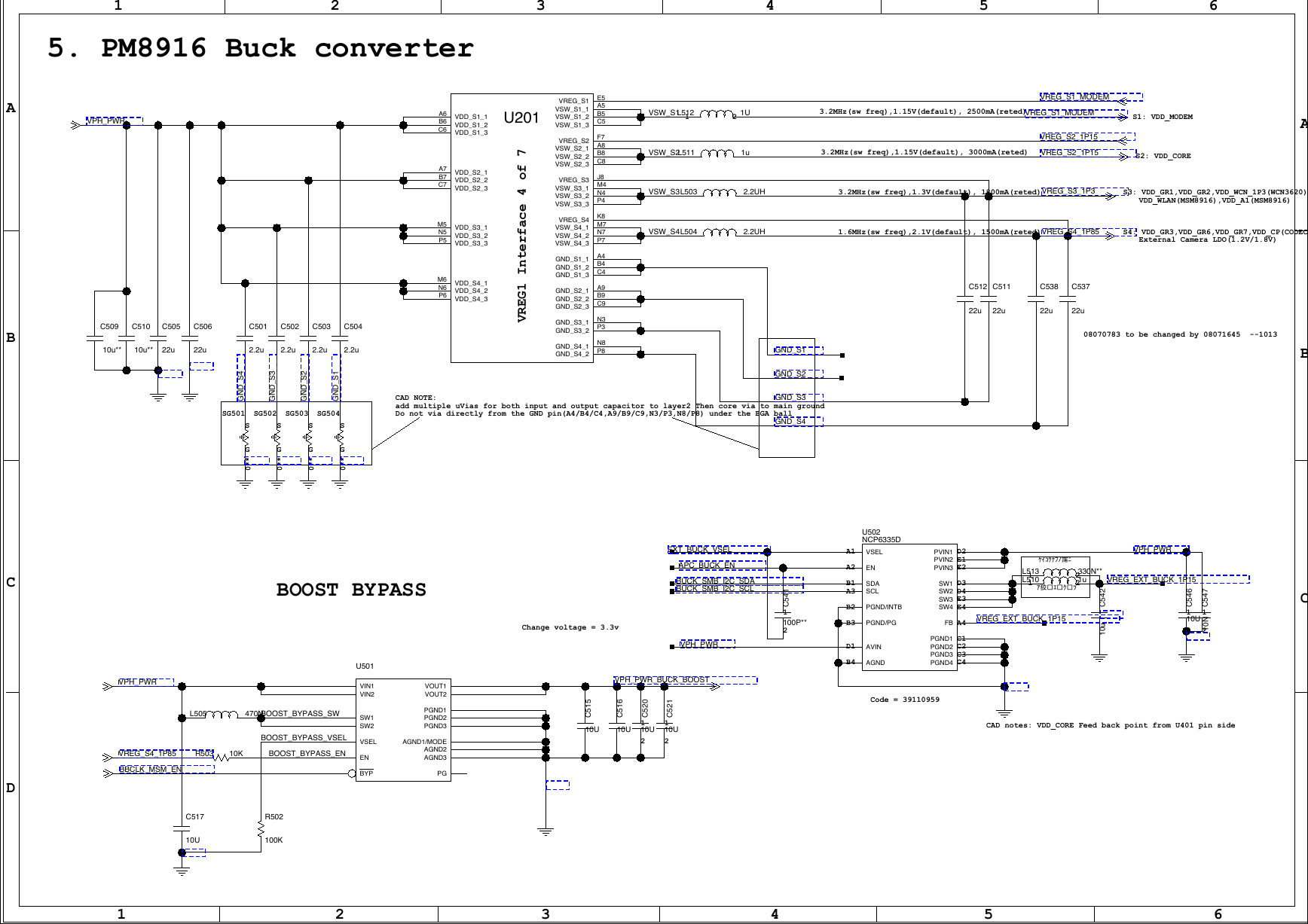

5. PM8916 Buck converter

VSW_S1

L512

1

1U2

3.2MHz(sw freq),1.15V(default), 2500mA(reted)

VREG_S1_MODEM

S1: VDD_MODEM

VREG_S1_MODEM

A

VSW_S2

L511

1u

3.2MHz(sw freq),1.15V(default), 3000mA(reted)

VREG_S2_1P15

S2: VDD_CORE

VREG_S2_1P15

VSW_S3

L503

2.2UH

3.2MHz(sw freq),1.3V(default), 1800mA(reted)

VREG_S3_1P3

S3: VDD_GR1,VDD_GR2,VDD_WCN_1P3(WCN3620)

VDD_WLAN(MSM8916),VDD_A1(MSM8916)

VSW_S4

L504

2.2UH

1.6MHz(sw freq),2.1V(default), 1500mA(reted)

VREG_S4_1P85

S4: VDD_GR3,VDD_GR6,VDD_GR7,VDD_CP(CODEC)

External Camera LDO(1.2V/1.8V)

C512

C511

C538

C537

22u

22u

22u

22u

08070783 to be changed by 08071645 --1013

GND_S1

GND_S2

CAD NOTE:

add multiple uVias for both input and output capacitor to layer2 Then core via to main ground

Do not via directly from the GND pin(A4/B4/C4,A9/B9/C9,N3/P3,N8/P8) under the BGA ball

GND_S3

GND_S4

B

C

A6 VDD_S1_1

B6

VDD_S1_2

C6

VDD_S1_3

U201

A7

B7

C7

M5

N5

P5

M6

N6

P6

VDD_S2_1

VDD_S2_2

VDD_S2_3

VDD_S3_1

VDD_S3_2

VDD_S3_3

VDD_S4_1

VDD_S4_2

VDD_S4_3

7

f

o

4

e

c

a

f

r

e

t

n

I

1

G

E

R

V

VREG_S1

VSW_S1_1

VSW_S1_2

VSW_S1_3

VREG_S2

VSW_S2_1

VSW_S2_2

VSW_S2_3

VREG_S3

VSW_S3_1

VSW_S3_2

VSW_S3_3

VREG_S4

VSW_S4_1

VSW_S4_2

VSW_S4_3

GND_S1_1

GND_S1_2

GND_S1_3

GND_S2_1

GND_S2_2

GND_S2_3

GND_S3_1

GND_S3_2

GND_S4_1

GND_S4_2

E5

A5

B5

C5

F7

A8

B8

C8

J8

M4

N4

P4

K8

M7

N7

P7

A4

B4

C4

A9

B9

C9

N3

P3

N8

P8

VPH_PWR

C509

C510

C505

C506

C501

C502

C503

C504

10u**

10u**

22u

22u

2.2u

2.2u

2.2u

2.2u

4

S

_

D

N

G

3

S

_

D

N

G

2

S

_

D

N

G

1

S

_

D

N

G

SG501

SG502

SG503

SG504

S

S

S

S

S

S

S

S

G

*

*

0

G

*

*

0

G

*

*

0

G

*

*

0

A

B

C

D

EXT_BUCK_VSEL

APC_BUCK_EN

BUCK_SMB_I2C_SDA

BUCK_SMB_I2C_SCL

1

4

5

C

1

100P**

2

Change voltage = 3.3v

VPH_PWR

VPH_PWR_BUCK_BOOST

5

1

5

C

6

1

5

C

10U

10U

0

2

5

C

1

10U

2

1

2

5

C

1

10U

2

U502

NCP6335D

VSEL

EN

SDA

SCL

PGND/INTB

PGND/PG

AVIN

AGND

A1

A2

B1

A3

B2

B3

D1

B4

PVIN1

PVIN2

PVIN3

SW1

SW2

SW3

SW4

D2

E1

E2

D3

D4

E3

E4

FB

A4

PGND1

PGND2

PGND3

PGND4

C1

C2

C3

C4

Code = 39110959

BOOST BYPASS

VPH_PWR

L505

470N

BOOST_BYPASS_SW

VREG_S4_1P85

R503

10K

BOOST_BYPASS_EN

BOOST_BYPASS_VSEL

BBCLK_MSM_EN

U501

VIN1

VIN2

SW1

SW2

VSEL

EN

BYP

VOUT1

VOUT2

PGND1

PGND2

PGND3

AGND1/MODE

AGND2

AGND3

PG

C517

10U

R502

100K

ケイコクナフノ霈ニ

VPH_PWR

L513

L510

1

1

ア狡エクツ

VREG_EXT_BUCK_1P15

330N**

2

1u2

VREG_EXT_BUCK_1P15

2

4

5

C

u

0

1

6

4

5

C

1

10U

2

7

4

5

C

1

N

0

2

1

CAD notes: VDD_CORE Feed back point from U401 pin side

1

2

3

4

5

6

�

A

B

C

D

1

2

3

4

5

6

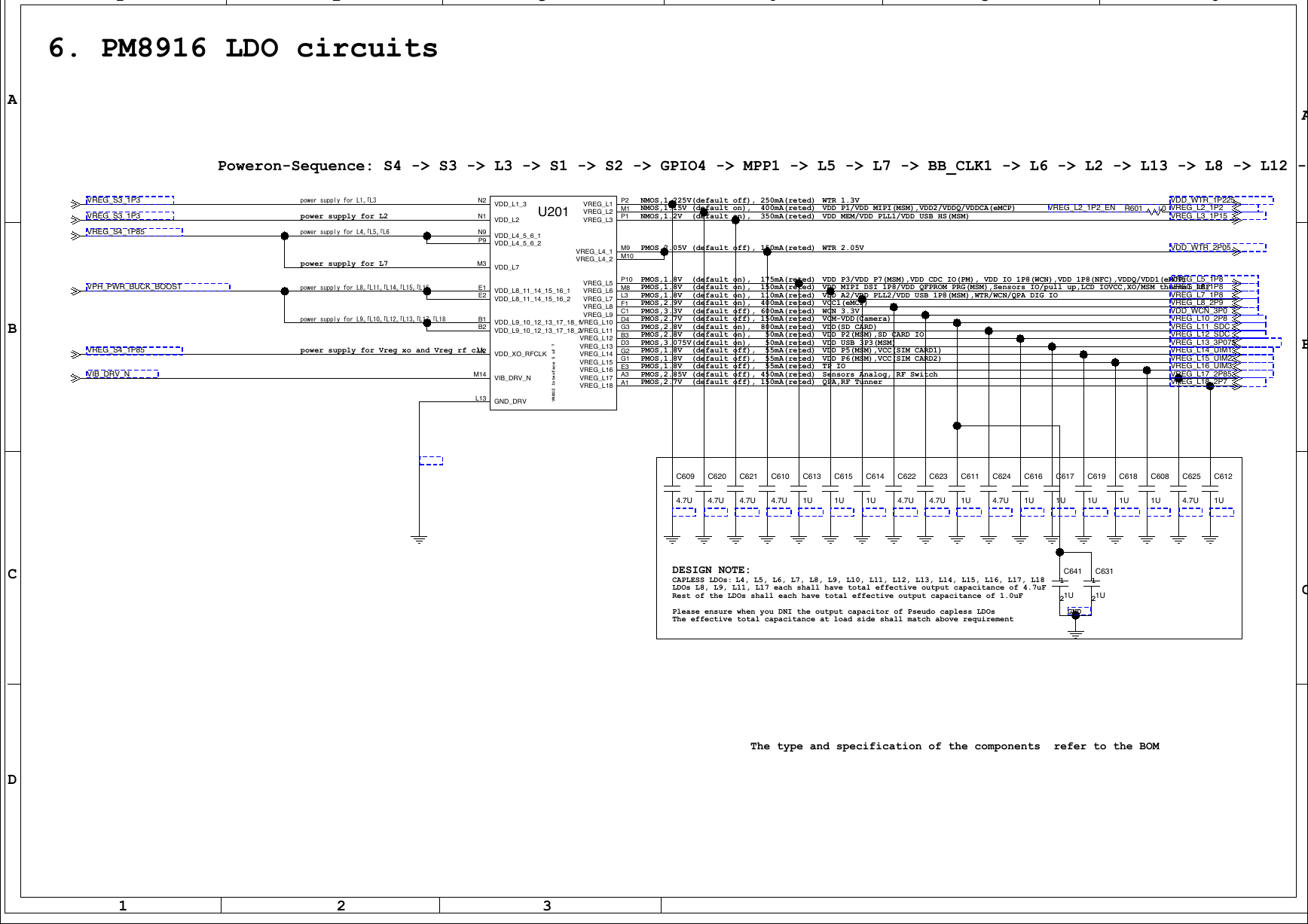

6. PM8916 LDO circuits

Poweron-Sequence: S4 -> S3 -> L3 -> S1 -> S2 -> GPIO4 -> MPP1 -> L5 -> L7 -> BB_CLK1 -> L6 -> L2 -> L13 -> L8 -> L12 -> L11

A

N2 VDD_L1_3

N1

VDD_L2

U201

VREG_L1

VREG_L2

VREG_L3

P2

M1

P1

NMOS,1.225V(default off), 250mA(reted)

NMOS,1.15V (default on), 400mA(reted)

NMOS,1.2V (default on), 350mA(reted)

WTR 1.3V

VDD_P1/VDD_MIPI(MSM),VDD2/VDDQ/VDDCA(eMCP)

VDD_MEM/VDD_PLL1/VDD_USB_HS(MSM)

VREG_L2_1P2_EN

R601

0

VDD_WTR_1P225

VREG_L2_1P2

VREG_L3_1P15

VDD_WTR_2P05

VREG_L4_1

VREG_L4_2

M9

M10

PMOS,2.05V (default off), 150mA(reted)

WTR 2.05V

VDD_P3/VDD_P7(MSM),VDD_CDC_IO(PM), VDD_IO_1P8(WCN),VDD_1P8(NFC),VDDQ/VDD1(eMCP)

PMOS,1.8V (default on), 175mA(reted)

PMOS,1.8V (default on), 150mA(reted) VDD_MIPI_DSI_1P8/VDD_QFPROM_PRG(MSM),Sensors IO/pull up,LCD IOVCC,XO/MSM thermal REF

PMOS,1.8V (default on), 110mA(reted) VDD_A2/VDD_PLL2/VDD_USB_1P8(MSM),WTR/WCN/QPA DIG IO

PMOS,2.9V (default on), 400mA(reted) VCC1(eMCP)

PMOS,3.3V (default off), 600mA(reted) WCN 3.3V

PMOS,2.7V (default off), 150mA(reted) VCM-VDD(Camera)

PMOS,2.8V (default on), 800mA(reted)

PMOS,2.8V (default on), 50mA(reted)

PMOS,3.075V(default on), 50mA(reted)

PMOS,1.8V (default off), 55mA(reted) VDD_P5(MSM),VCC(SIM CARD1)

PMOS,1.8V (default off), 55mA(reted) VDD_P6(MSM),VCC(SIM CARD2)

PMOS,1.8V (default off), 55mA(reted) TP IO

PMOS,2.85V (default off), 450mA(reted)

PMOS,2.7V (default off), 150mA(reted)

VREG_L5_1P8

VREG_L6_1P8

VREG_L7_1P8

VREG_L8_2P9

VDD_WCN_3P0

VREG_L10_2P8

VREG_L11_SDC

VREG_L12_SDC

VREG_L13_3P075

VREG_L14_UIM1

VREG_L15_UIM2

VREG_L16_UIM3

VREG_L17_2P85

VREG_L18_2P7

VDD(SD CARD)

VDD_P2(MSM),SD CARD IO

VDD_USB_3P3(MSM)

Sensors Analog, RF Switch

QPA,RF Tunner

C609

C620

C621

C610

C613

C615

C614

C622

C623

C611

C624

C616

C617

C619

C618

C608

C625

C612

4.7U

4.7U

4.7U

4.7U

1U

1U

1U

4.7U

4.7U

1U

4.7U

1U

1U

1U

1U

1U

4.7U

1U

DESIGN NOTE:

CAPLESS LDOs: L4, L5, L6, L7, L8, L9, L10, L11, L12, L13, L14, L15, L16, L17, L18

LDOs L8, L9, L11, L17 each shall have total effective output capacitance of 4.7uF

Rest of the LDOs shall each have total effective output capacitance of 1.0uF

Please ensure when you DNI the output capacitor of Pseudo capless LDOs

The effective total capacitance at load side shall match above requirement

C641

1

C631

1

1U

2

1U

2

GND

The type and specification of the components refer to the BOM

B

C

N9

P9

M3

E1

E2

B1

B2

VDD_L4_5_6_1

VDD_L4_5_6_2

VDD_L7

VDD_L8_11_14_15_16_1

VDD_L8_11_14_15_16_2

VDD_L9_10_12_13_17_18_1

VDD_L9_10_12_13_17_18_2

VREG_L5

VREG_L6

VREG_L7

VREG_L8

VREG_L9

VREG_L10

VREG_L11

VREG_L12

VREG_L13

VREG_L14

VREG_L15

VREG_L16

VREG_L17

VREG_L18

P10

M8

L3

F1

C1

D4

G3

B3

D3

G2

G1

E3

A3

A1

VREG_S3_1P3

VREG_S3_1P3

VREG_S4_1P85

power supply for L1。「L3

power supply for L2

power supply for L4。「L5。「L6

power supply for L7

VPH_PWR_BUCK_BOOST

power supply for L8。「L11。「L14。「L15。「L16

power supply for L9。「L10。「L12。「L13。「L17。「L18

VREG_S4_1P85

VIB_DRV_N

power supply for Vreg_xo and Vreg_rf_clk

M2

VDD_XO_RFCLK

M14

L13

VIB_DRV_N

GND_DRV

7

f

o

5

e

c

a

f

r

e

t

n

I

2

G

E

R

V

1

2

3

�

1

2

3

4

5

6

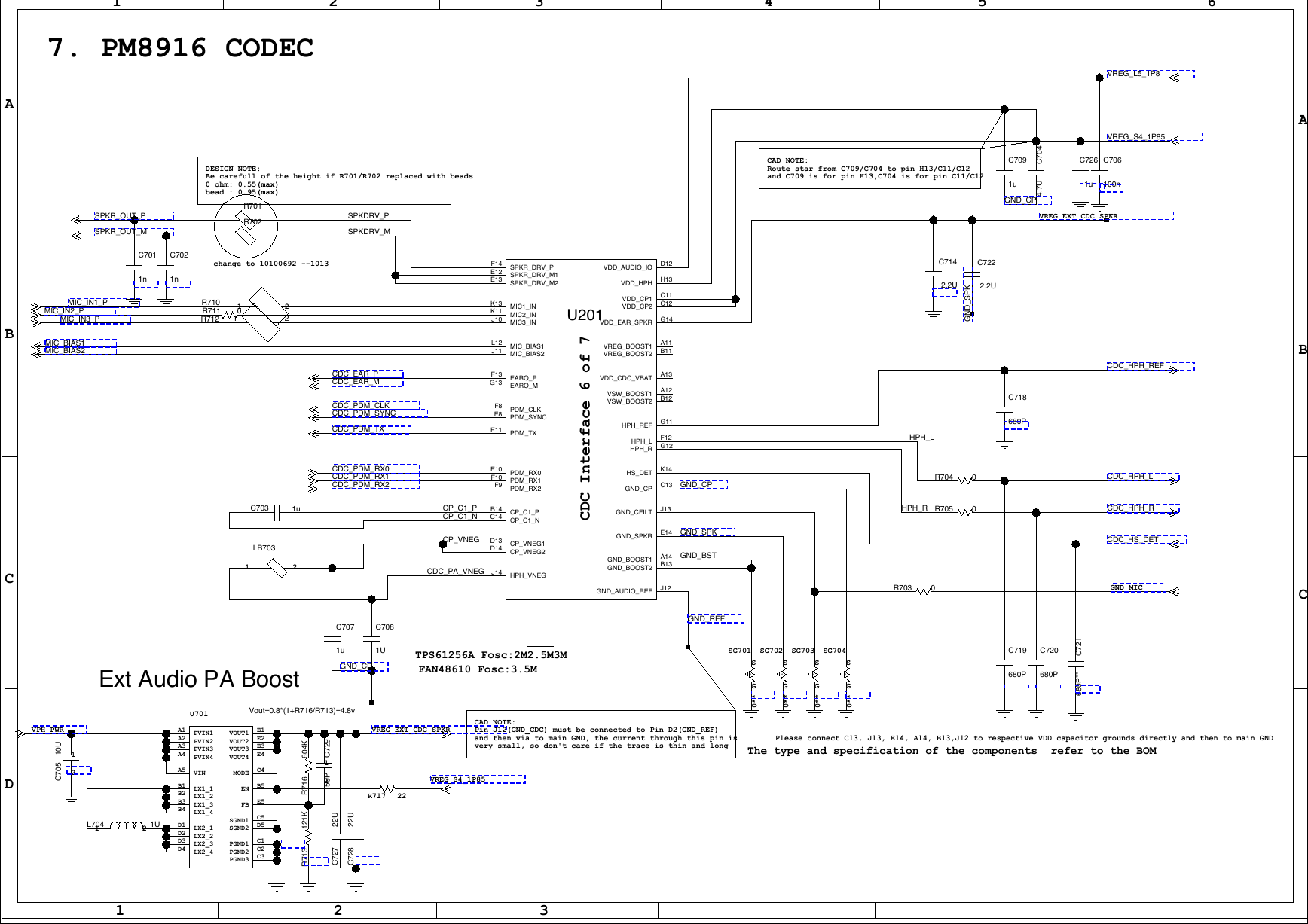

7. PM8916 CODEC

A

DESIGN NOTE:

Be carefull of the height if R701/R702 replaced with beads

0 ohm: 0.55(max)

bead : 0.95(max)

SPKR_OUT_P

SPKR_OUT_M

R701

R702

SPKDRV_P

SPKDRV_M

C701

C702

1n

1n

change to 10100692 --1013

R710

R711

R712

1

0

1

2

2

MIC_IN1_P

MIC_IN2_P

MIC_IN3_P

B

MIC_BIAS1

MIC_BIAS2

C

D

VPH_PWR

U

0

1

5

0

7

C

1

2

C703

1u

LB703

1

2

Ext Audio PA Boost

CAD NOTE:

Route star from C709/C704 to pin H13/C11/C12

and C709 is for pin H13,C704 is for pin C11/C12

4

0

7

C

C709

1u

U

7

4

.

GND_CP

VREG_L5_1P8

VREG_S4_1P85

C726

C706

1u

100n

C714

C722

2.2U

2.2U

K

P

S

_

D

N

G

C718

680P

HPH_L

R704

HPH_R

R705

0

0

VREG_EXT_CDC_SPKR

CDC_HPH_REF

CDC_HPH_L

CDC_HPH_R

CDC_HS_DET

R703

0

GND_MIC

SG701

SG702

SG703

SG704

S

S

S

S

S

S

S

S

G

*

*

0

G

*

*

0

G

*

*

0

G

*

*

0

C719

C720

680P

680P

1

2

7

C

*

*

P

0

8

6

A

B

C

F14 SPKR_DRV_P

E12

SPKR_DRV_M1

E13

SPKR_DRV_M2

K13

K11

J10

L12

J11

F13

G13

F8

E8

E11

E10

F10

F9

B14

C14

D13

D14

MIC1_IN

MIC2_IN

MIC3_IN

MIC_BIAS1

MIC_BIAS2

EARO_P

EARO_M

PDM_CLK

PDM_SYNC

PDM_TX

PDM_RX0

PDM_RX1

PDM_RX2

CP_C1_P

CP_C1_N

CP_VNEG1

CP_VNEG2

CP_C1_P

CP_C1_N

CP_VNEG

CDC_EAR_P

CDC_EAR_M

CDC_PDM_CLK

CDC_PDM_SYNC

CDC_PDM_TX

CDC_PDM_RX0

CDC_PDM_RX1

CDC_PDM_RX2

CDC_PA_VNEG

J14

HPH_VNEG

C707

C708

1u

1U

GND_CP

TPS61256A Fosc:2M2.5M3M

FAN48610 Fosc:3.5M

D12

H13

C11

C12

G14

A11

B11

A13

A12

B12

G11

F12

G12

K14

C13

GND_CP

VDD_AUDIO_IO

VDD_HPH

VDD_CP1

VDD_CP2

U201

VDD_EAR_SPKR

VREG_BOOST1

VREG_BOOST2

VDD_CDC_VBAT

VSW_BOOST1

VSW_BOOST2

HPH_REF

HPH_L

HPH_R

HS_DET

GND_CP

7

f

o

6

e

c

a

f

r

e

t

n

I

C

D

C

GND_CFILT

J13

GND_SPKR

E14

GND_SPK

GND_BST

GND_BOOST1

GND_BOOST2

GND_AUDIO_REF

A14

B13

J12

GND_REF

Vout=0.8*(1+R716/R713)=4.8v

U701

A1 PVIN1

A2

PVIN2

A3

PVIN3

A4

PVIN4

VOUT1

VOUT2

VOUT3

VOUT4

A5

B1

B2

B3

B4

D1

D2

D3

D4

VIN

MODE

LX1_1

LX1_2

LX1_3

LX1_4

LX2_1

LX2_2

LX2_3

LX2_4

EN

FB

SGND1

SGND2

PGND1

PGND2

PGND3

L704

1

1U

2

1

E1

E2

E3

E4

C4

B5

E5

C5

D5

C1

C2

C3

K

4

0

6

6

1

7

R

K

1

2

1

3

1

7

R

9

2

7

C

1

P

2

6

5

U

2

2

U

2

2

7

2

7

C

8

2

7

C

2

VREG_EXT_CDC_SPKR

CAD NOTE:

Pin J12(GND_CDC) must be connected to Pin D2(GND_REF)

and then via to main GND, the current through this pin is

very small, so don't care if the trace is thin and long

Please connect C13, J13, E14, A14, B13,J12 to respective VDD capacitor grounds directly and then to main GND

The type and specification of the components refer to the BOM

VREG_S4_1P85

R717

22

3

�

A

B

C

D

1

2

3

4

5

6

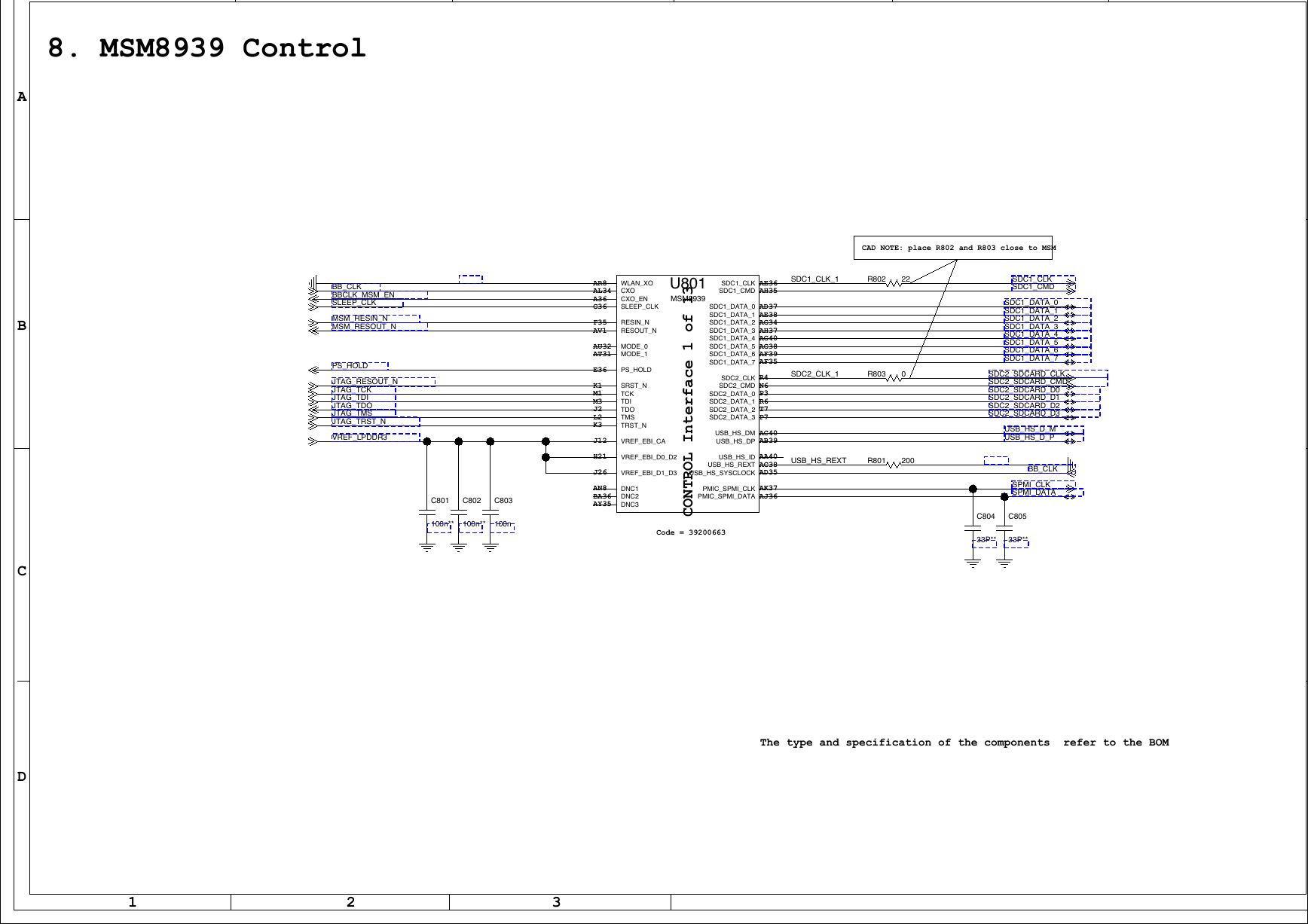

8. MSM8939 Control

CAD NOTE: place R802 and R803 close to MSM

BB_CLK

BBCLK_MSM_EN

SLEEP_CLK

MSM_RESIN_N

MSM_RESOUT_N

PS_HOLD

JTAG_RESOUT_N

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST_N

VREF_LPDDR3

C801

C802

C803

100n**

100n**

100n

U801

MSM8939

SDC1_CLK_1

R802

22

SDC2_CLK_1

R803

0

SDC1_CLK

SDC1_CMD

AE36

AH35

SDC1_DATA_0

SDC1_DATA_1

SDC1_DATA_2

SDC1_DATA_3

SDC1_DATA_4

SDC1_DATA_5

SDC1_DATA_6

SDC1_DATA_7

AD37

AE38

AG34

AH37

AG40

AG38

AF39

AF35

SDC2_CLK

SDC2_CMD

SDC2_DATA_0

SDC2_DATA_1

SDC2_DATA_2

SDC2_DATA_3

R4

N6

P3

R6

T7

P7

USB_HS_DM

USB_HS_DP

AC40

AB39

USB_HS_ID

USB_HS_REXT

USB_HS_SYSCLOCK

AA40

AC38

AD35

USB_HS_REXT

R801

200

PMIC_SPMI_CLK

PMIC_SPMI_DATA

AK37

AJ36

AR8

AL34

A36

G36

F35

AV1

WLAN_XO

CXO

CXO_EN

SLEEP_CLK

RESIN_N

RESOUT_N

AU32

AT31

MODE_0

MODE_1

E36

PS_HOLD

K1

M1

M3

J2

L2

K3

J12

H21

J26

SRST_N

TCK

TDI

TDO

TMS

TRST_N

VREF_EBI_CA

VREF_EBI_D0_D2

VREF_EBI_D1_D3

AN8

BA36

AY35

DNC1

DNC2

DNC3

3

1

f

o

1

e

c

a

f

r

e

t

n

I

L

O

R

T

N

O

C

Code = 39200663

SDC1_CLK

SDC1_CMD

SDC1_DATA_0

SDC1_DATA_1

SDC1_DATA_2

SDC1_DATA_3

SDC1_DATA_4

SDC1_DATA_5

SDC1_DATA_6

SDC1_DATA_7

SDC2_SDCARD_CLK

SDC2_SDCARD_CMD

SDC2_SDCARD_D0

SDC2_SDCARD_D1

SDC2_SDCARD_D2

SDC2_SDCARD_D3

USB_HS_D_M

USB_HS_D_P

BB_CLK

SPMI_CLK

SPMI_DATA

C804

C805

33P**

33P**

The type and specification of the components refer to the BOM

1

2

3

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc