Copyright and Warranty Notice

The information in this document is subject to change without notice and does not

represent a commitment on part of the vendor, who assumes no liability or

responsibility for any errors that may appear in this manual.

No warranty or representation, either expressed or implied, is made with respect to

the quality, accuracy or fitness for any particular part of this document. In no event

shall the manufacturer be

indirect, special, incidental or

consequential damages arising from any defect or error in this manual or product.

liable for direct,

Product names appearing in this manual are for identification purpose only and

trademarks and product names or brand names appearing in this document are

property of their respective owners.

This document contains materials protected under International Copyright Laws. All

rights reserved. No part of this manual may be reproduced, transmitted or

transcribed without the expressed written permission of the manufacturer and

authors of this manual.

If you do not properly set the motherboard settings causing the motherboard to

malfunction or fail, we cannot guarantee any responsibility.

�

�

CX6 Motherboard User’s Manual

Chapter 1. Introduction of CX6 Features

1-1. Features of this Motherboard

1-2. Specifications

1-3. Layout Diagram

1-4. The System Block Diagram

Chapter 2. Installing the Motherboard

2-1. Installing the Motherboard to the Chassis

2-2. Installation of the Pentium II/III CPU

2-3. Installing System Memory

2-4. Connectors, Headers and Switches

Chapter 3. Introduction of The BIOS

3-1. CPU Soft Menu™ II

3-2. Standard CMOS Features Setup Menu

3-3. Advanced BIOS Features Setup Menu

3-4. Advanced Chipset Features Setup Menu

3-5. Integrated Peripherals

3-6. Power Management Setup Menu

3-7. PnP/PCI Configurations

3-8. PC Health Status

3-9. Load Fail-Safe Defaults

3-10. Load Optimized Defaults

3-11. Set Password

3-12. Save & Exit Setup

3-13. Exit Without Saving

Table of Contents

1-1

1-1

1-6

1-9

1-10

2-1

2-2

2-3

2-4

2-7

3-1

3-4

3-8

3-13

3-18

3-21

3-27

3-35

3-38

3-40

3-40

3-41

3-42

3-43

MN-170-2A0-41

Rev. 1.00

�

Appendix A Intel INF Installation Utility for Windows® 98 SE

Appendix B Installing the Audio Driver for Windows® 98 SE

Appendix C Installing the Audio Drivers for the Windows® NT

Appendix D BIOS Flashing User Instructions

Appendix E Installing the HighPoint XStore Pro Utility

Appendix F Hardware Monitoring Function (Installing the

Winbond Hardware Doctor Utility)

Appendix G Installation Guide for Suspend to RAM

Appendix H Troubleshooting (Need Assistance?)

Appendix I

How to Get Technical Support

�

Introduction of CX6 Features

1-1

Chapter 1. Introduction of CX6 Features

1-1.Features of this Motherboard

This motherboard is designed for the new generation of CPUs. It supports the Intel SLOT1

structure (Pentium II/III processor), up to 1GB of memory, super I/O, and Green PC

functions. The motherboard provides high performance for server systems and meets the

requirements for future multimedia desktop systems.

The CX6 uses the new generation Intel® 820 chipset (Camino) for more efficiency and high

integration of the system. What are the main features of the Intel® Camino chipset? Its

structure is shown in Figure 1-2.

133 MHz System Bus

! The Intel® 820 platform supports the new 133 MHz system bus

" Up to 33% increased peak bandwidth over the Intel® 440BX platform.

AGP 4x Graphics

! Up to 1GB/Sec transfer rate

" Twice the peak bandwidth of AGP 2x of the 440BX AGPset

! Broad industry support for AGP 4x from all leading graphics IHVs

" NVIDIA, 3Dfx, S3, ATI, Intel, Matrox, etc.

RDRAM Memory

! Provides memory bandwidth to keep up with ever increasing application demands

" Faster processors, graphics, and I/O

! RDRAM delivers up to 3x the effective bandwidth of PC100 SDRAM

" 1.6 GByte/sec for PC800 RDRAM

! RDRAM provides the required headroom for further application improvement

" Constant Computing

" More realistic environments

" Platform longevity and stability

The Intel® 820 chipset is a combination of three chips: the FW82820, FW82801 and

FW82802. The FW82820 is called MCH chip (Memory Controller Hub), FW82801 is

called ICH chip (I/O Controller Hub), FW82802 is called FWH chip (FirmWare Hub).

MCH (Memory Controller Hub)

The MCH provides the host interface, DRAM interface, I/O interface, and AGP interface in

a Camino platform. Camino MCH is optimized for the Katmai or Coppermine processor. It

supports a single channel of direct Rambus memory technology. Its AGP interface is fully

compliant with AGP 2.0 specification. Communication to ICH is over a private interface or

the hub interface (link). The Camino MCH contains the following functionality:

User’s Manual

➠

➠

➠

�

1-2

Chapter1

Supports the Katmai and Coppermine processors at 100/133MHz for Slot 1

Supports an IOQ (In-Order Queue) depth of 6

GTL+ host bus supporting 32-bit host addressing

Single Direct Rambus channel optimized for 300, 356 and 400 MHz operation

1GB DRAM supported with 256Mbit memory technology

AGP 2.0 interface with 1x/2x/4x data transfer and 2x/4x fast write capability

The hub interface (link) to ICH

Fully optimized data paths and buffering

Distributed arbitration for highly concurrent operation

ACPI 1.0 power management compliant

ICH (I/O Controller Hub)

The ICH is a highly integrated multifunctional component supporting the following

functions and capabilities:

PCI Rev. 2.2 compliant with support for 33MHz PCI operations

Supports up to 6 Req/Gnt pairs (PCI Slots)

Integrated IDE controller with Ultra DMA/66 support

USB host interface with support for 2 USB ports

AC '97 2.1 compliant link for audio and telephony CODECs

Firmware Hub (FWH) interface support

FWH (FirmWare Hub)

The FWH component is part of several integrated Intel® chipsets. The FWH is key to

enabling future security and manageability infrastructures for the PC platform. The device

operates under the FWH interface/protocol. The hardware features of this device include a

Random Number Generator (RNG), five General Purpose Inputs (GPIs), register-based

block locking, and hardware-based locking. An integrated combination of logic features and

non-volatile memory enables better protection for the storage/update of platform code/data,

adds platform flexibility through additional GPIs and allows for quicker introduction of new

security/manageability features into the current and future Intel® architecture platform. It's

available in 8Mbit (82802AC), 4Mbit (82802AB), and 2Mbit (82802AA) densities. It uses

the 32L PLCC or 40L TSOP industry standard packages.

AMR (Audio/Modem Riser)

The CX6 has one AMR slot onboard, called the Audio/Modem Riser (AMR) slot. The

Audio/Modem Riser is an open industry-standard specification that defines a hardware

CX6

➠

➠

➠

➠

➠

➠

➠

➠

➠

➠

➠

➠

➠

➠

➠

➠

�

Introduction of CX6 Features

1-3

scalable Original Equipment Manufacturer (OEM) motherboard riser board and interface,

which supports both audio and modem functions. The specification's main objective is to

reduce the baseline implementation cost of audio and modem functionality. In accordance

with PC user's demands for feature-rich PCs, combined with the industry's current trend

towards lower cost PCs, all of theses functions are built into the motherboard. But

motherboard integration of the modem subsystem has been problematic to date, in large part

due to FCC and other international telecom certification processes that may delay the

introduction of a motherboard. Resolving the homologation/certification issue for modems

is one of the AMR specification's key objectives.

In the future, not only OEM motherboards will have an AMR design, the AMR card will

appear in the market and you can make a choice in buying this kind of card according to your

budget. But your motherboard must have an AMR slot to be able to plug an AMR card. The

CX6 insures this expansibility for this issue.

Yamaha YMF752-S audio chip

YMF752 is an AC’97 Audio CODEC LSI, which is fully compliant with the industry

standard “Audio CODEC ’97” component specification (Revision 2.1).

YMF752 includes a SRC (Sampling Rate Converter) for support variable sampling rate,

which can work the A/D and D/A converter at different rate. YMF752 has an AC-Link serial

interface, which can be used with digital controller LSI. Therefore, YMF752 is the best

audio solution for both laptops and desktop PCs as well as AMR (Audio Modem Riser) and

MDC (Mobile Daughter Card).

YMF752 also supports low power consumption while normal operating and allows for

controlling the power down mode.

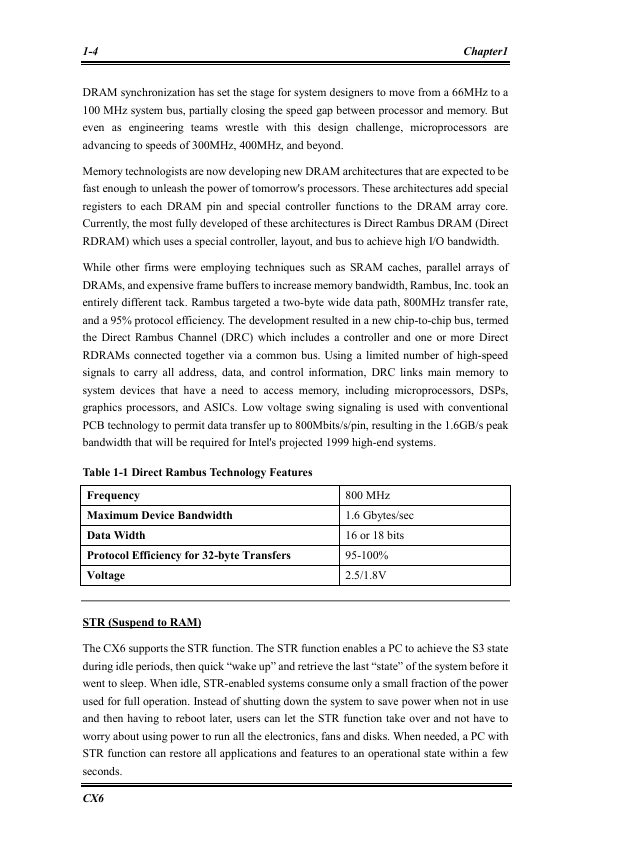

Direct Rambus Technology

During the past few years, computer main memory has become the speed bottleneck that has

blocked improved system performance. This is true despite the fact that DRAM densities

have been accelerating sharply from yesterday's 1Kbit per chip to today's 64Mbit devices.

While that aspect of DRAM technology has advanced by a factor of 1,000 in the past 10

years, the time it takes to access main memory has improved by only a factor of five. The

result is that memory bandwidth, the number of bytes per second that can be moved across

memory I/O, has been hobbled. That sluggish performance improvement is now a severe

drag on systems powered by microprocessors that have improved CPU performance 200

fold in the same timeframe.

User’s Manual

�

1-4

Chapter1

DRAM synchronization has set the stage for system designers to move from a 66MHz to a

100 MHz system bus, partially closing the speed gap between processor and memory. But

even as engineering teams wrestle with this design challenge, microprocessors are

advancing to speeds of 300MHz, 400MHz, and beyond.

Memory technologists are now developing new DRAM architectures that are expected to be

fast enough to unleash the power of tomorrow's processors. These architectures add special

registers to each DRAM pin and special controller functions to the DRAM array core.

Currently, the most fully developed of these architectures is Direct Rambus DRAM (Direct

RDRAM) which uses a special controller, layout, and bus to achieve high I/O bandwidth.

While other firms were employing techniques such as SRAM caches, parallel arrays of

DRAMs, and expensive frame buffers to increase memory bandwidth, Rambus, Inc. took an

entirely different tack. Rambus targeted a two-byte wide data path, 800MHz transfer rate,

and a 95% protocol efficiency. The development resulted in a new chip-to-chip bus, termed

the Direct Rambus Channel (DRC) which includes a controller and one or more Direct

RDRAMs connected together via a common bus. Using a limited number of high-speed

signals to carry all address, data, and control information, DRC links main memory to

system devices that have a need to access memory, including microprocessors, DSPs,

graphics processors, and ASICs. Low voltage swing signaling is used with conventional

PCB technology to permit data transfer up to 800Mbits/s/pin, resulting in the 1.6GB/s peak

bandwidth that will be required for Intel's projected 1999 high-end systems.

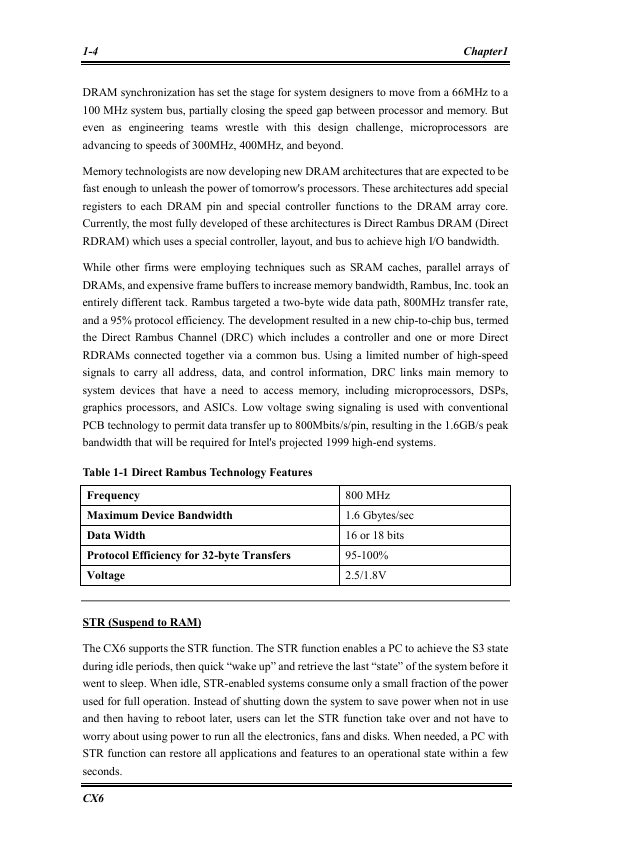

Table 1-1 Direct Rambus Technology Features

Frequency

Maximum Device Bandwidth

Data Width

Protocol Efficiency for 32-byte Transfers

Voltage

800 MHz

1.6 Gbytes/sec

16 or 18 bits

95-100%

2.5/1.8V

STR (Suspend to RAM)

The CX6 supports the STR function. The STR function enables a PC to achieve the S3 state

during idle periods, then quick “wake up” and retrieve the last “state” of the system before it

went to sleep. When idle, STR-enabled systems consume only a small fraction of the power

used for full operation. Instead of shutting down the system to save power when not in use

and then having to reboot later, users can let the STR function take over and not have to

worry about using power to run all the electronics, fans and disks. When needed, a PC with

STR function can restore all applications and features to an operational state within a few

seconds.

CX6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc