Title Page

Copyright Page

Dedication

About the Authors

Acknowledgments

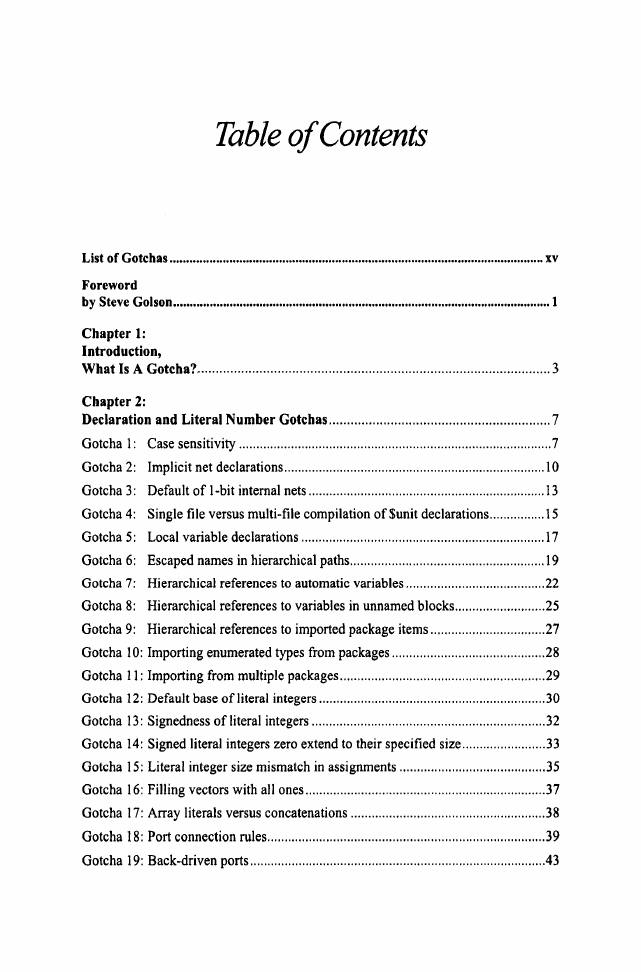

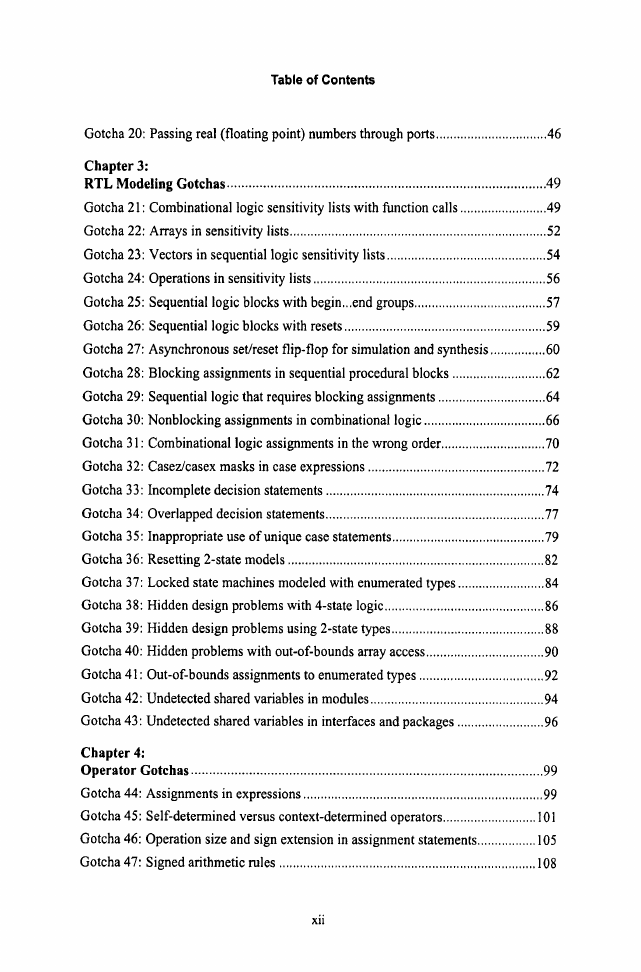

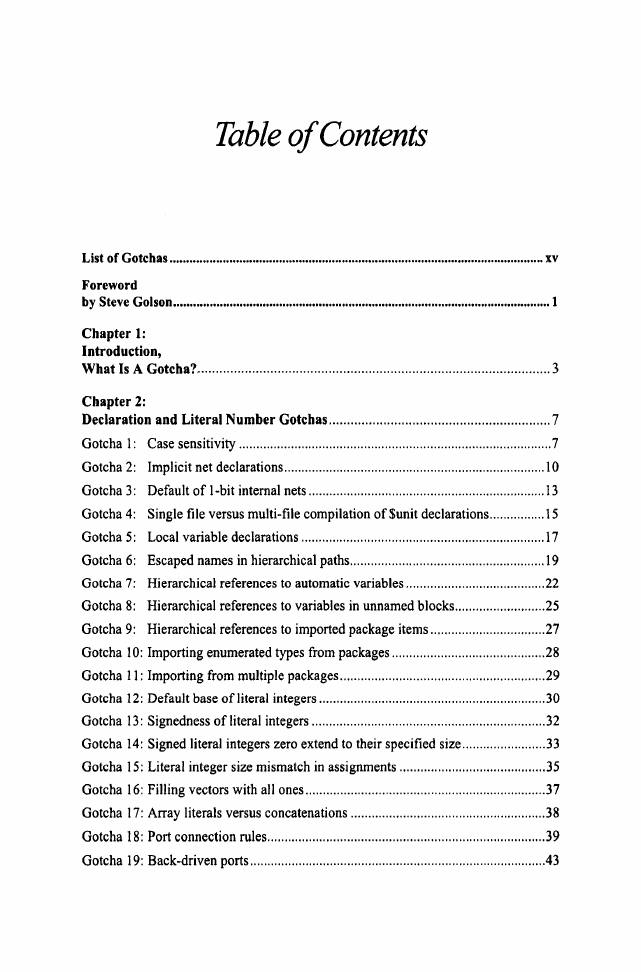

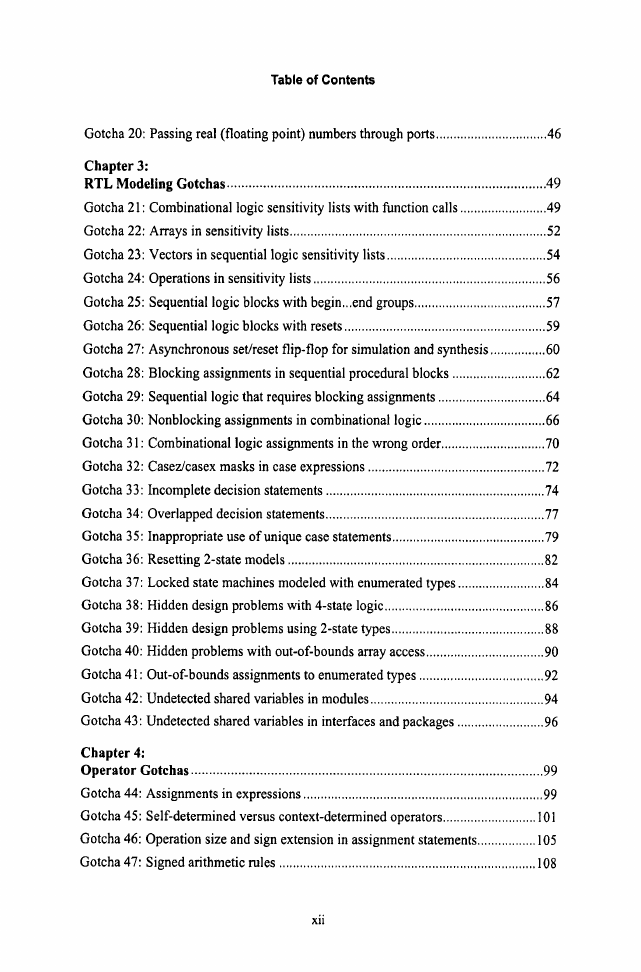

Table of Contents

List of Gotchas

Foreword by Steve Golson

Chapter 1 Introduction, What Is A Gotcha?

What are Verilog and System Verilog?

What is a Gotcha?

The Verilog and System Verilog standards

Chapter 2 Declaration and Literal Number Gotchas

Gotcha 1: Case sensitivity

Gotcha 2: Implicit net declarations

Gotcba 3: Default of 1-bit internal nets

Gotcha 4: Single file versus multi-file compilation of $unit declarations

Gotcha 5: Local variable declarations

Gotcha 6: Escaped names in hierarchical paths

Gotcha 7: Hierarchical references to automatic variables

Gotcha 8: Hierarchical references to variables in unnamed blocks

Gotcha 9: Hierarchical references to imported package items

Gotcha 10: Importing enumerated types from packages

Gotcha 11: Importing from multiple packages

Gotcha 12: Default base of literal integers

Gotcha 13: Signedness of literal integers

Gotcha 14: Signed literal integers zero extend to their specified size

Gotcha 15: Literal integersize mismatch in assignments

Gotcha 16: Filling vectors with all ones

Gotcha 17: Array literals versus concatenations

Gotcha 18: Port connection rules

Gotcha 19: Back-driven ports

Gotcha 20: Passing real (floating point) numbers through ports

Chapter 3 RTL Modeling Gotchas

Gotcha 21: Combinational logic sensitivity lists with function calls

Gotcha 22: Arrays in sensitivity lists

Gotcha 23: Vectors in sequential logic sensitivity lists

Gotcha 24: Operations in sensitivity lists

Gotcha 25: Sequential logic blocks with begin...end groups

Gotcha 26: Sequential logic blocks with resets

Gotcha 27: Asynchronous set/reset flip-flop for simulation and synthesis

Gotcha 28: Blocking assignments in sequential procedural blocks

Gotcha 29: Sequential logic that requires blocking assignments

Gotcha 30: Nonblocking assignments in combinational logic

Gotcha 31: Combinational logic assignments in the wrong order

Gotcha 32: Casez/casex masks in case expressions

Gotcha 33: Incomplete decision statements

Gotcha 34: Overlapped decision statements

Gotcha 35: Inappropriate use of unique case statements

Gotcha 36: Resetting 2-state models

Gotcha 37: Locked state machines modeled with enumerated types

Gotcha 38: Hidden design problems with 4-state logic

Gotcha 39: Hidden design problems using 2-state types

Gotcha 40: Hidden problems with out-or-bounds array access

Gotcha 41: Out-or-bounds assignments to enumerated types

Gotcha 42: Undetected shared variables in modules

Gotcha 43: Undetected shared variables in interfaces and packages

Chapter 4 Operator Gotchas

Gotcha 44: Assignments in expressions

Gotcha 45: Self-determined versus context-determined operators

Gotcha 46: Operation size and sign extension in assignment statements

Gotcha 47: Signed arithmetic rules

Gotcha 48: Bit-select and part-select operations

Gotcha 49: Increment, decrement and assignment operators

Gotcha 50: Pre-increment versus post-increment operations

Gotcha 51: Modifying a variable multiple times in onestatement

Gotcha 52: Operator evaluation short circuiting

Gotcha 53: The not operator ( ! ) versus the invert operator ( ~ )

Gotcha 54: Array method operations

Gotcha 55: Array method operations on an array subset

Chapter 5 General Programming Gotchas

Gotcha 56: Verifying asynchronous and synchronous reset at time zero

Gotcha 57: Nested if ...else blocks

Gotcha 58: Evaluation of equality with 4-state values

Gotcha 59: Event trigger race conditions

Gotcha 60: Using semaphores for synchronization

Gotcha 61: Using mailboxes for synchronization

Gotcha 62: Triggering on clocking blocks

Gotcha 63: Misplaced semicolons after decision statements

Gotcha 64: Misplaced semicolons in for loops

Gotcha 65: Infinite for loops

Gotcha 66: Locked simulation due to concurrent for loops

Gotcha 67: Referencing for loop control variables

Gotcha 68: Default function return size

Gotcha 69: Task/function arguments with default values

Gotcha 70: Continuous assignments with delays cancel glitches

Chapter 6 Object Oriented and Multi-Threaded Programming Gotchas

Gotcha 71: Programming statements in a class

Gotcha 72: Using interfaces with object-oriented testbenches

Gotcha 73: All objects in mailbox come out with the same values

Gotcha 74: Passing handles to methods using input versus ref arguments

Gotcha 75: Constructing an array of objects

Gotcha 76: Static tasks and functions are not re-entrant

Gotcha 77: Static versus automatic variable initialization

Gotcha 78: Forked programming threads need automatic variables

Gotcha 79: Disable fork kills too many threads

Gotcha 80: Disabling a statement block stops more than intended

Gotcha 81: Simulation exits prematurely, before tests complete

Chapter 7 Randomization, Coverage and Assertion Gotchas

Gotcha 82: Variables declared with rand are not getting randomized

Gotcha 83: Undetected randomization failures

Gotcha 84: $assertoff could disable randomization

Gotcha 85: Boolean constraints on more than two random variables

Gotcha 86: Unwanted negative values in random values

Gotcha 87: Coverage reports default to groups, not bins

Gotcha 88: Coverage is always reported as 0%

Gotcha 89: The coverage report lumps all instances together

Gotcha 90: Covergroup argument directions are sticky

Gotcha 91: Assertion pass statements execute with a vacuous success

Gotcha 92: Concurrent assertions in procedural blocks

Gotcha 93: Mismatch in assert...else statements

Gotcha 94: Assertions that cannot fail

Chapter 8 Tool Compatibility Gotchas

Gotcha 95: Default simulation time units and precision

Gotcha 96: Package chaining

Gotcha 97: Random number generator is not consistent across tools

Gotcha 98: Loading memories modeled with aIways_latch/always_ff

Gotcha 99: Non-standard language extensions

Gotcha 100: Array literals versus concatenations

Gotcha 101: Module ports that pass floating point values (real types)

Index

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc