基于 IEEE1801(UPF)标准的低功耗设计实现流程

Thursday, November 18, 2010

Low-power Implementation Flow Based IEEE1801 (UPF)

郭军, 廖水清, 张剑景

华为通信技术有限公司

jguo@huawei.com

liaoshuiqing@huawei.com

zhangjianjing@huawei.com

Abstract

Power consumption is becoming an increasingly important aspect of ASIC design. There are several

different approaches that can be used to reduce power. However, it is important to use these low-power

technology more effectively in IC design implementation and verification flow. In our latest low-power chip,

we completed full implementation and verification flow from RTL to GDSII successfully and effectively by

adopting IEEE1801 Unified Power Format (UPF). This paper will focus on UPF application in design

implementation with Synopsys low power solution. It will highlight that how to describe our low-power

intent using UPF and how to complete the design flow. This paper first illustrates current low-power

methodology and UPF’s concept. Then, it discussed UPF application in detail. Finally, it gives our

conclusion.

Key words: IEEE1801, UPF, Low-Power, Shut-Down, Power Gating, Isolation, IC-Compiler

摘要

目前除了时序和面积,功耗已经成为集成电路设计中日益关注的因素。当前有很多种降低功耗的方法,为

了在设计实现流程中更加有效的利用各种低功耗的设计方法,我们在最近一款芯片的设计实现以及验证流

程中,使用了基于 IEEE1801 标准 Unified Power Format(UPF)的完整技术,成功的完成了从 RTL 到

GDSII 的全部过程,并且芯片制造回来成功的完成了测试。本文就其中的设计实现部分进行了详细探讨,

重点介绍如何用 UPF 把我们的低功耗意图描述出来以及如何用 Synopsys 工具实现整个流程,希望给大家

以启发。本文先介绍目前常用的低功耗设计的一些方法特别是用 power-gating 的方法来控制静态功耗以及

UPF 的实现方法,然后阐述 UPF 在我们设计流程中的应用,并在介绍中引入了一些我们的设计经验,最

后给出我们的结论。

关键字:IEEE1801, UPF,低功耗, 电源关断,Power-Gating, Isolation, IC-Compiler

1. 简介

1.1 深亚微米设计面临的挑战

随着工艺特征尺寸的缩小以及复杂度的提高,IC 设计面临了很多挑战:速度越来越高,面积不断增大,噪

声现象更加严重等。其中,功耗问题尤为突出,工艺进入 130nm 以下节点后,单位面积上的功耗密度急剧

上升,已经达到封装、散热、以及底层设备所能支持的极限。随着工艺进一步达到 90nm 以下,漏电流呈

指数级增加(如图1所示),在某些 65nm 设计中,漏电流已经和动态电流一样大,曾经可以忽略的静态

功耗成为功耗的主要部分。功耗已成为继传统二维要素(速度、面积)之后的第三维要素。

�

图 1: 静态功耗与工艺特征尺寸的关系

另外,目前飞速发展的手持电子设备市场,为了增强自身产品的竞争力,也对低功耗提出了越来越高的要

求;其次散热问题、可靠性问题也要求 IC 的功耗越小越好;最后全球都在倡导绿色环保科技理念,保护环

境,节约能源。这些都要求 IC 设计时必须采用低功耗技术,以有效应对这些挑战。

1.2 目前低功耗设计常用的方法

如图2所示,影响功耗的因素有电压、漏电流、工作频率、有效电容等。可以通过降低工作电压、减少翻

转负载以及降低电路翻转率等来降低动态功耗;通过减少工作电压以及减少漏

图 2: 影响功耗的因素

电流来降低静态功耗。当前,业界采用了各种方法来降低芯片的动态功耗和静态功耗。如图 3 所示,传统

的低功耗技术有时钟关断(Clock-Gating),多域值电压库(Multi-threshold libraries)等;较新的技术有

多电压(Multi-Voltage),电源关断(MTCMOS Power Gating),带状态保持功能的电源关断(Power Gating

with State Retention),动态电压频率调整(Dynamic Voltage and Frequency Scaling),低电压待机

(Low-Vdd Standby)等。

�

图 3: 低功耗技术示例

1.3 控制静态漏电的方法

1.3.1 电路优化(Gate-level Optimization)

在设计实现过程中,自动化的综合和布局布线工具可以根据电路的时序特征,来综合优化每条路径中用到

的所有标准单元的时序,面积以及功耗。根据负载将非关键路径中的标准单元切换到具有较小驱动能力的

单元,由于输出电容减小,可以减小动态功耗;同时,由于标准单元 MOS 管和电容变小,静态漏电流也

同时减小。除了变化驱动能力之外,还可以通过优化电路中的逻辑单元、移动单元物理位置等方法来达到

降低功耗的目的。

1.3.2 多域值电压库 (Multi-Threshold)

如图4所示,高域值电压的标准单元漏电流小但速度慢,低域值电压的标准单元则速度快但漏电流大。所

以采用多域值电压库作为设计实现的目标库,在设计中尽可能多地用高域值电压的标准单元,仅在关键路

径上为了满足时序要求采用低域值电压的标准单元,这样就可以最大限度地减小标准单元的漏电流,从而

降低静态功耗。

图 4: 漏电流、单元速度与阈值电压三者之间的关系

1.3.3 电源关断 (Power-Gating)

�

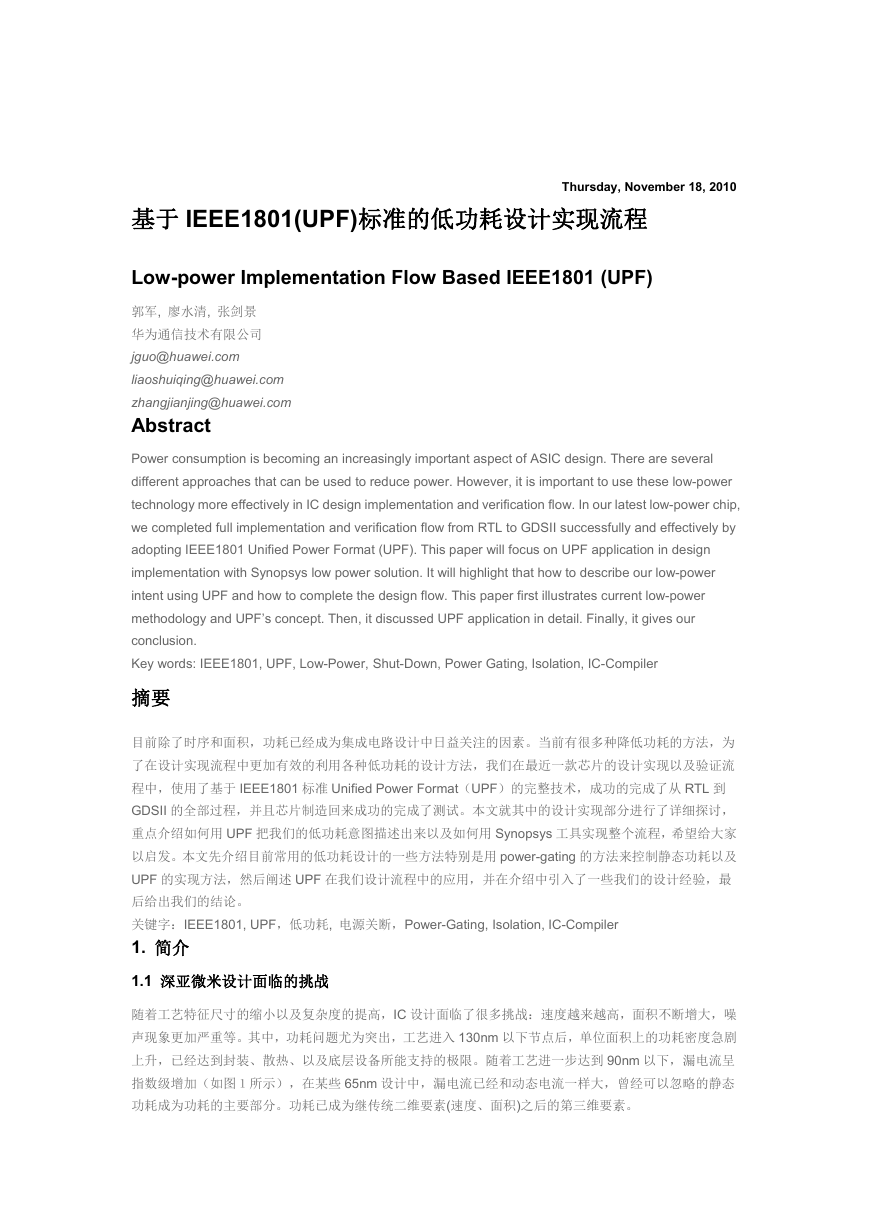

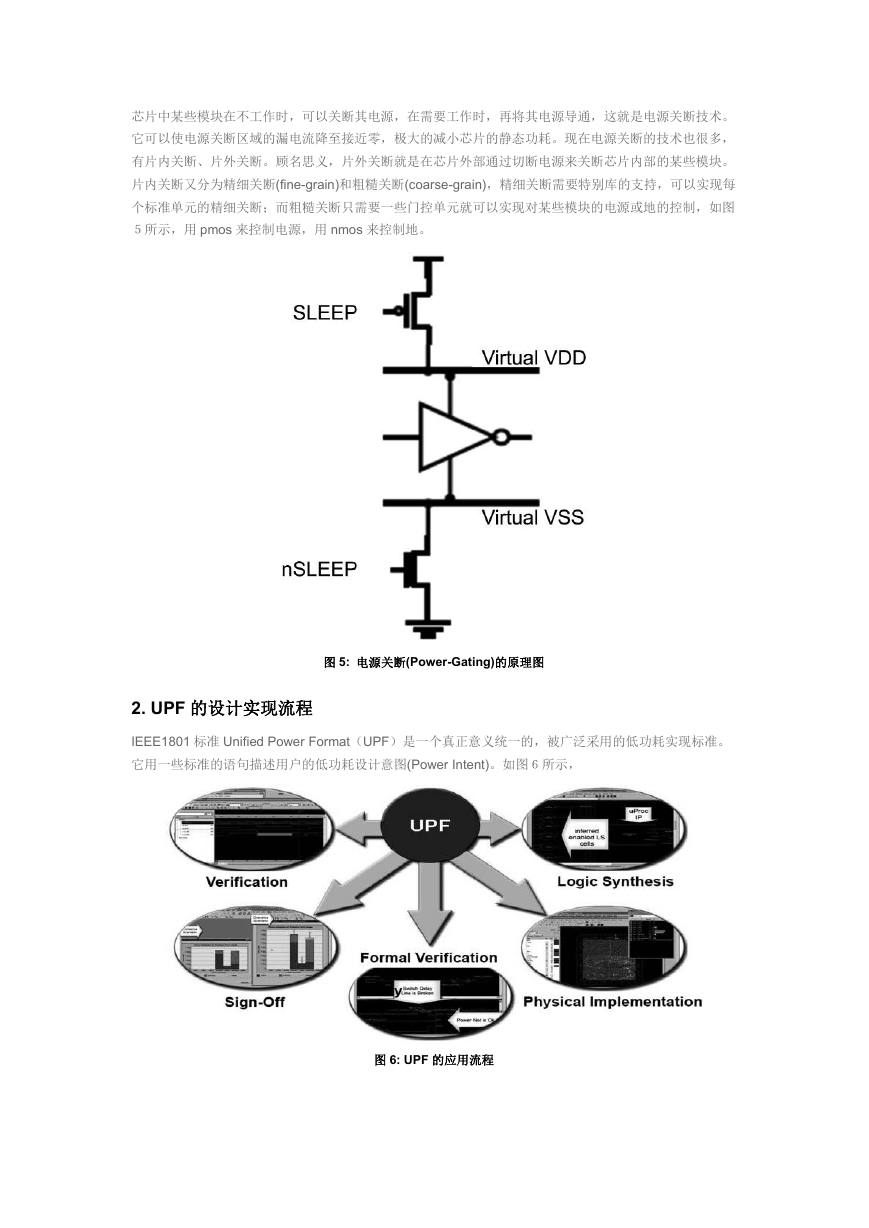

芯片中某些模块在不工作时,可以关断其电源,在需要工作时,再将其电源导通,这就是电源关断技术。

它可以使电源关断区域的漏电流降至接近零,极大的减小芯片的静态功耗。现在电源关断的技术也很多,

有片内关断、片外关断。顾名思义,片外关断就是在芯片外部通过切断电源来关断芯片内部的某些模块。

片内关断又分为精细关断(fine-grain)和粗糙关断(coarse-grain),精细关断需要特别库的支持,可以实现每

个标准单元的精细关断;而粗糙关断只需要一些门控单元就可以实现对某些模块的电源或地的控制,如图

5所示,用 pmos 来控制电源,用 nmos 来控制地。

图 5: 电源关断(Power-Gating)的原理图

2. UPF 的设计实现流程

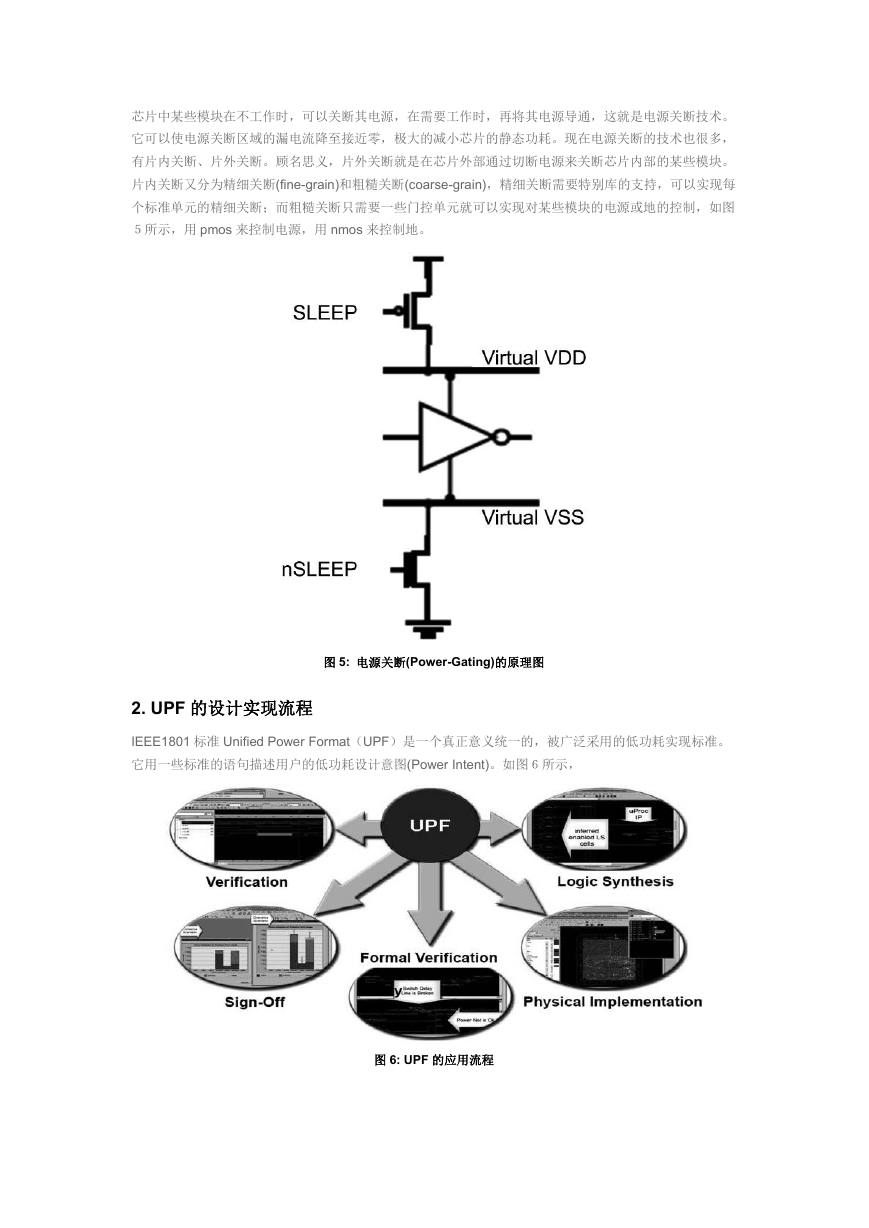

IEEE1801 标准 Unified Power Format(UPF)是一个真正意义统一的,被广泛采用的低功耗实现标准。

它用一些标准的语句描述用户的低功耗设计意图(Power Intent)。如图6所示,

图 6: UPF 的应用流程

�

有了这样一个统一的 UPF 文件,逻辑综合、物理实现、仿真验证、等效性检查以及最后的 sign-off 流程就

可以按照 UPF 中对低功耗设计意图的描述来完成整个 IC 设计实现验证流程。这样贯穿于整个流程的低功

耗意图来源于同一个文件,这种一致性可以大大降低低功耗设计的风险性。并且 UPF 对低功耗设计提供了

开放的,多厂商工具支持的流程和解决方案。众多支持 UPF 标准的 EDA 供应商的产品证明了它是一个互

操作性强的标准。

2.1 Synopsys 基于 UPF 的低功耗设计流程

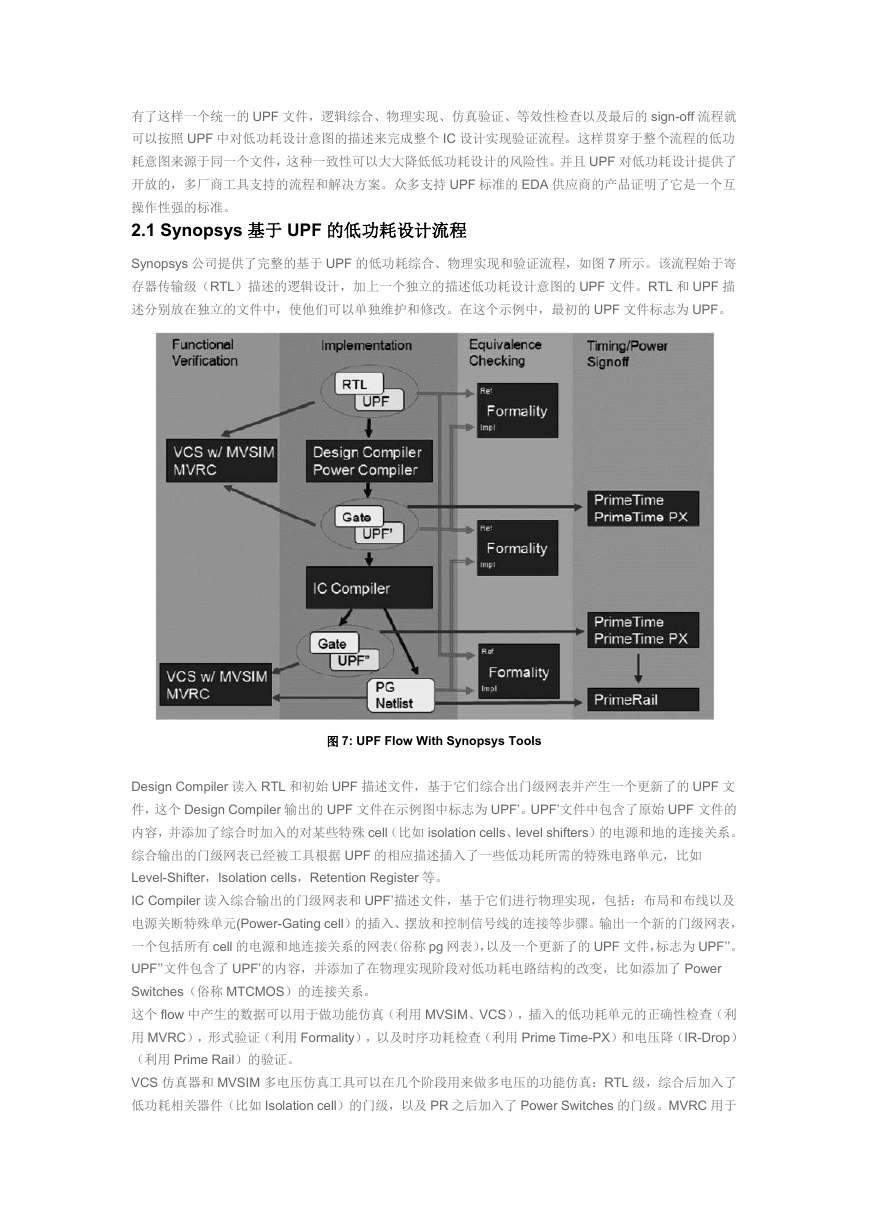

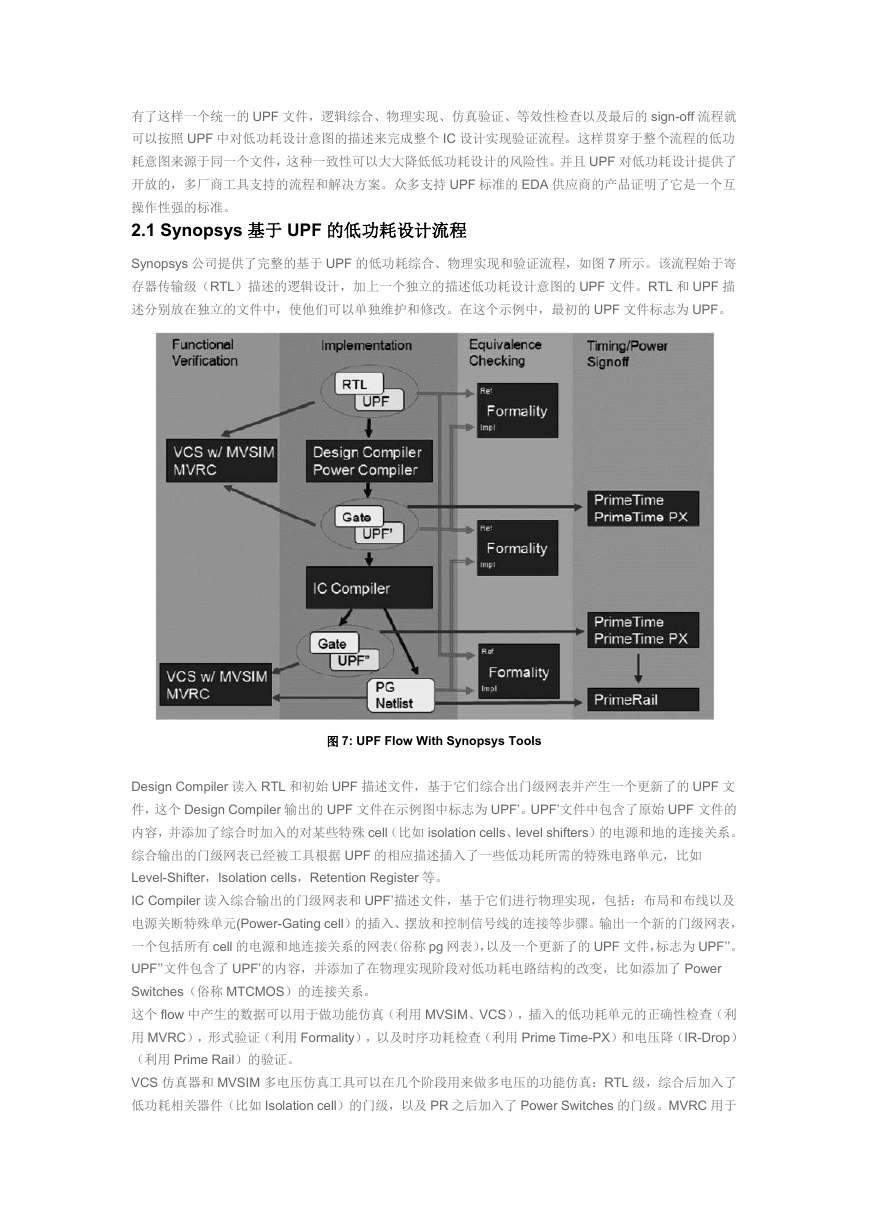

Synopsys 公司提供了完整的基于 UPF 的低功耗综合、物理实现和验证流程,如图 7 所示。该流程始于寄

存器传输级(RTL)描述的逻辑设计,加上一个独立的描述低功耗设计意图的 UPF 文件。RTL 和 UPF 描

述分别放在独立的文件中,使他们可以单独维护和修改。在这个示例中,最初的 UPF 文件标志为 UPF。

图 7: UPF Flow With Synopsys Tools

Design Compiler 读入 RTL 和初始 UPF 描述文件,基于它们综合出门级网表并产生一个更新了的 UPF 文

件,这个 Design Compiler 输出的 UPF 文件在示例图中标志为 UPF’。UPF’文件中包含了原始 UPF 文件的

内容,并添加了综合时加入的对某些特殊 cell(比如 isolation cells、level shifters)的电源和地的连接关系。

综合输出的门级网表已经被工具根据 UPF 的相应描述插入了一些低功耗所需的特殊电路单元,比如

Level-Shifter,Isolation cells,Retention Register 等。

IC Compiler 读入综合输出的门级网表和 UPF’描述文件,基于它们进行物理实现,包括:布局和布线以及

电源关断特殊单元(Power-Gating cell)的插入、摆放和控制信号线的连接等步骤。输出一个新的门级网表,

一个包括所有 cell 的电源和地连接关系的网表(俗称 pg 网表),以及一个更新了的 UPF 文件,标志为 UPF’’。

UPF’’文件包含了 UPF’的内容,并添加了在物理实现阶段对低功耗电路结构的改变,比如添加了 Power

Switches(俗称 MTCMOS)的连接关系。

这个 flow 中产生的数据可以用于做功能仿真(利用 MVSIM、VCS),插入的低功耗单元的正确性检查(利

用 MVRC),形式验证(利用 Formality),以及时序功耗检查(利用 Prime Time-PX)和电压降(IR-Drop)

(利用 Prime Rail)的验证。

VCS 仿真器和 MVSIM 多电压仿真工具可以在几个阶段用来做多电压的功能仿真:RTL 级,综合后加入了

低功耗相关器件(比如 Isolation cell)的门级,以及 PR 之后加入了 Power Switches 的门级。MVRC 用于

�

检查多电压设计的规则是否正确实现,包括电源连接关系、电源结构、电源一致性等等,也适用于流程中

的各个步骤。

Prime Time 读入 DC 或 ICC 输出的门级网表以及对应的 UPF 文件。它利用 UPF 文件中的信息建立一个虚

拟的电源网络模型,并将电压值反标到每个器件的电源端口,进行带电源信息的时序检查。

Prime Rail 是基于带 UPF 信息的版图进行电压降以及电迁移的分析。如果设计中有电源关断单元,它还可

以分析相关关断电路的瞬态电流以及动态的电压降分布。来帮助判断这些电源关断单元是否插入合理以及

是否需要插入 De-cap 单元。

2.2 UPF 所需要的特殊单元库

基于 UPF 的设计流程与传统流程相比,需要一些库中特殊单元的支持以及对传统的 DB 时序库添加电源地

的信息。特殊单元包括 Level-shifter,Isolation Cell,电源关断单元(Power Gating, 也叫 MTCMOS),

Retention-Register,以及 Always-on 单元。下面分别阐述:

2.2.1 Level-Shifter 和 Isolation Cell

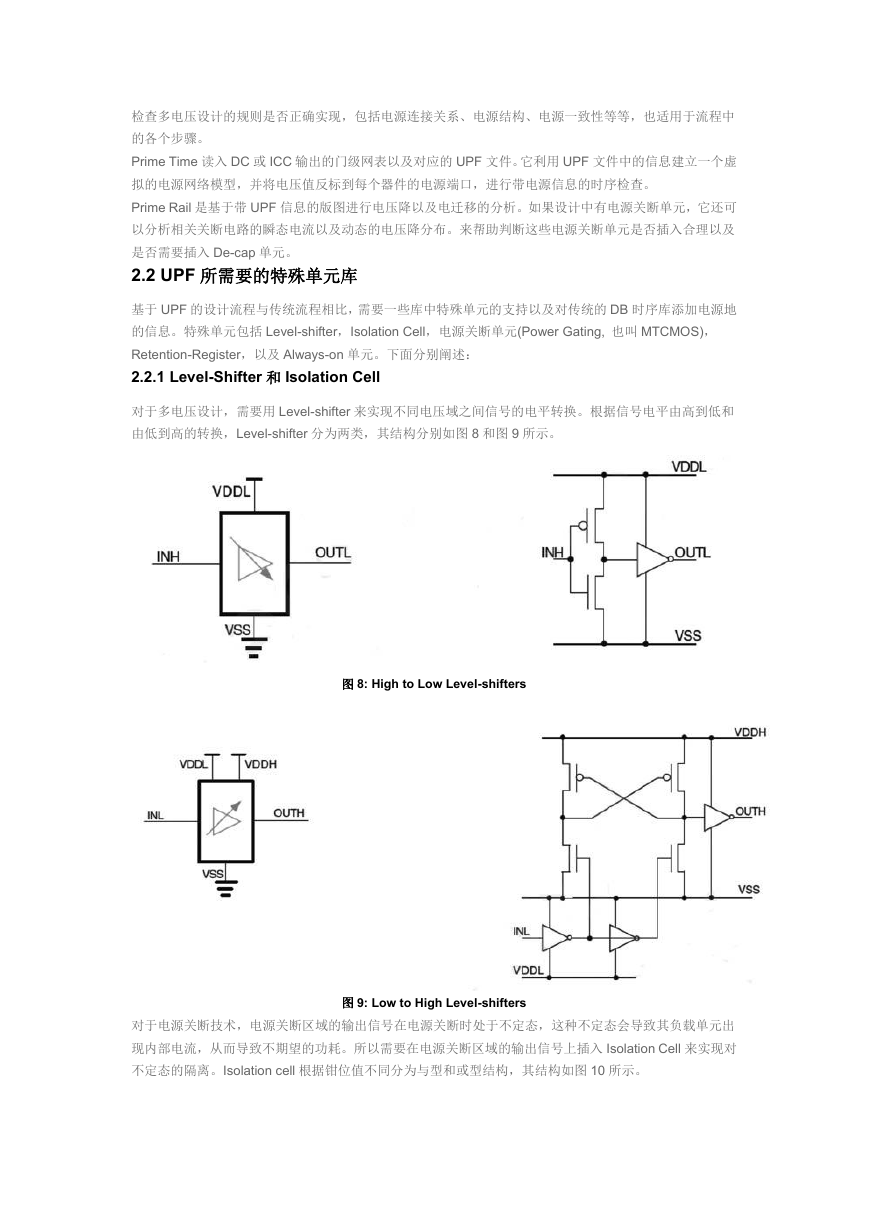

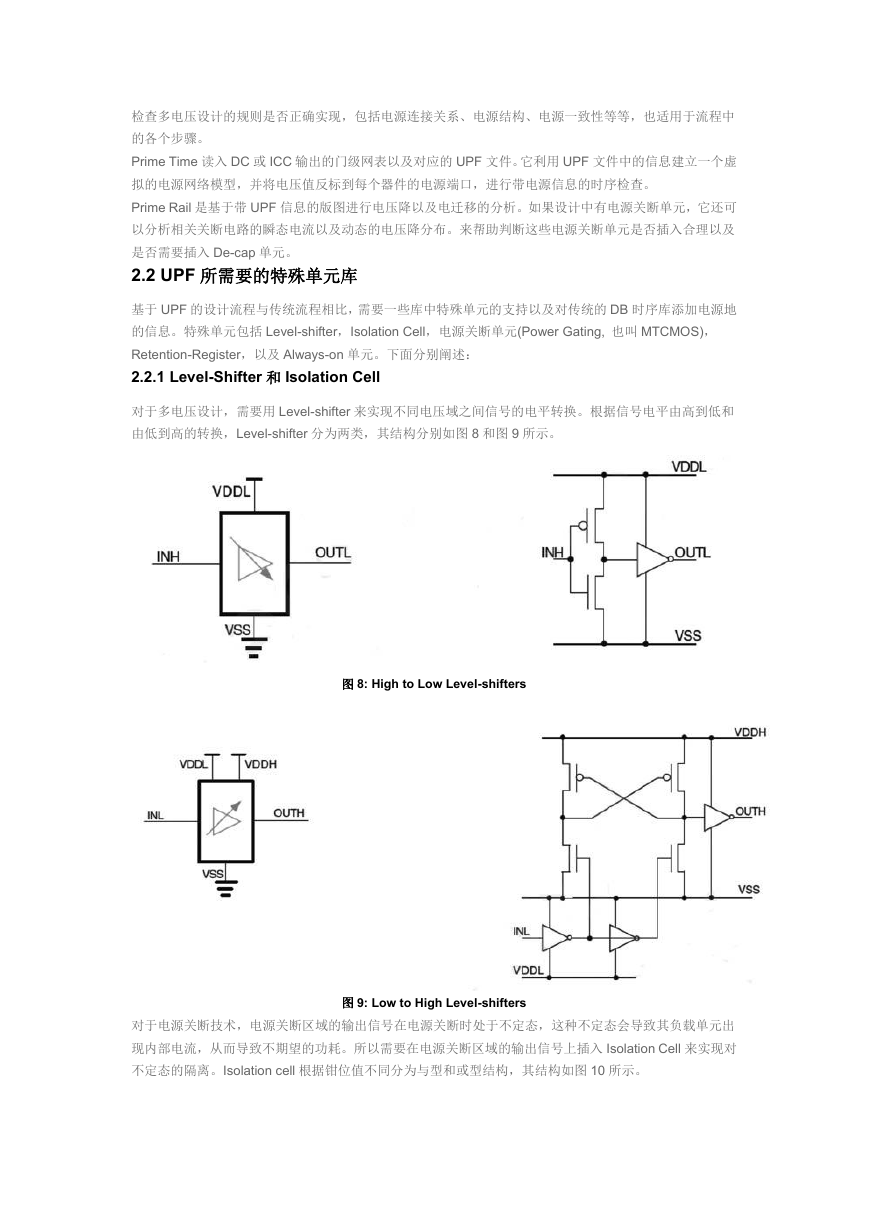

对于多电压设计,需要用 Level-shifter 来实现不同电压域之间信号的电平转换。根据信号电平由高到低和

由低到高的转换,Level-shifter 分为两类,其结构分别如图 8 和图 9 所示。

图 8: High to Low Level-shifters

图 9: Low to High Level-shifters

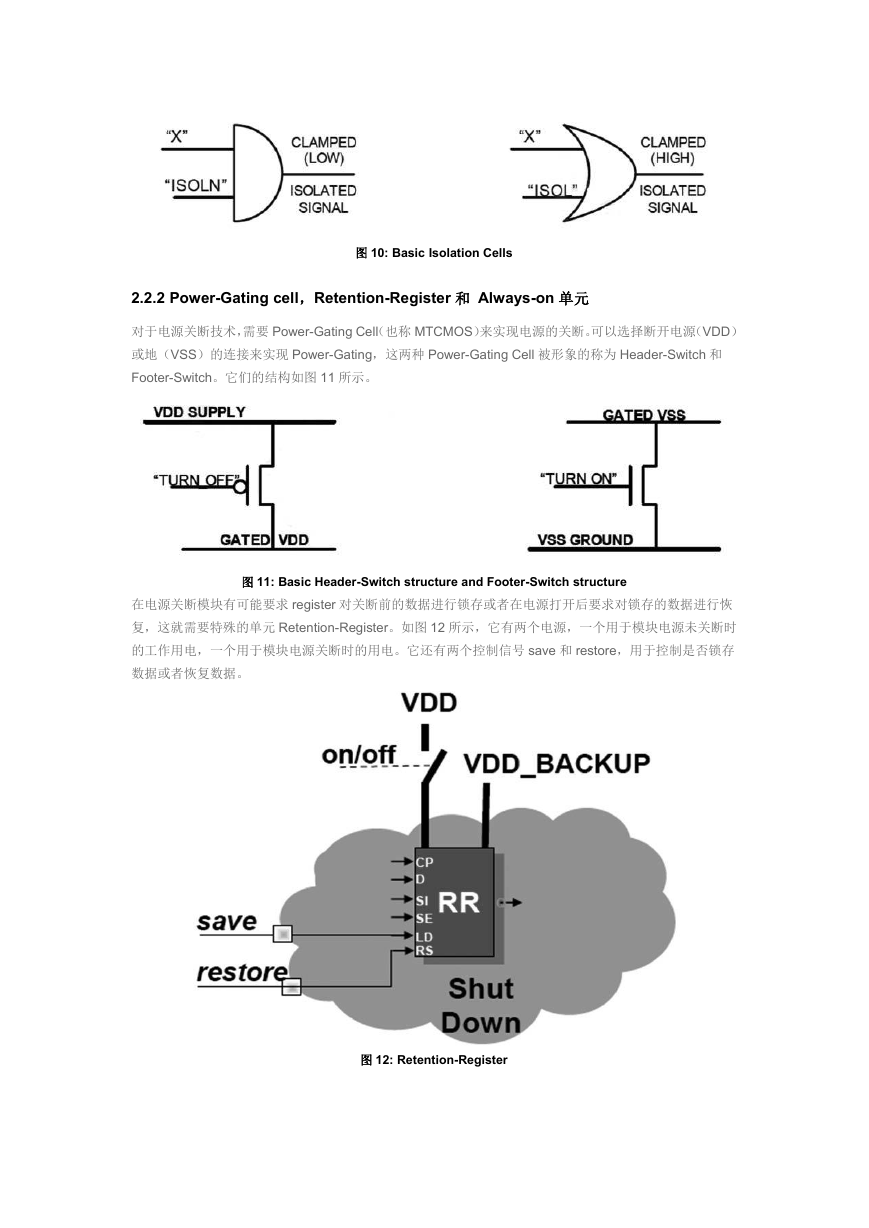

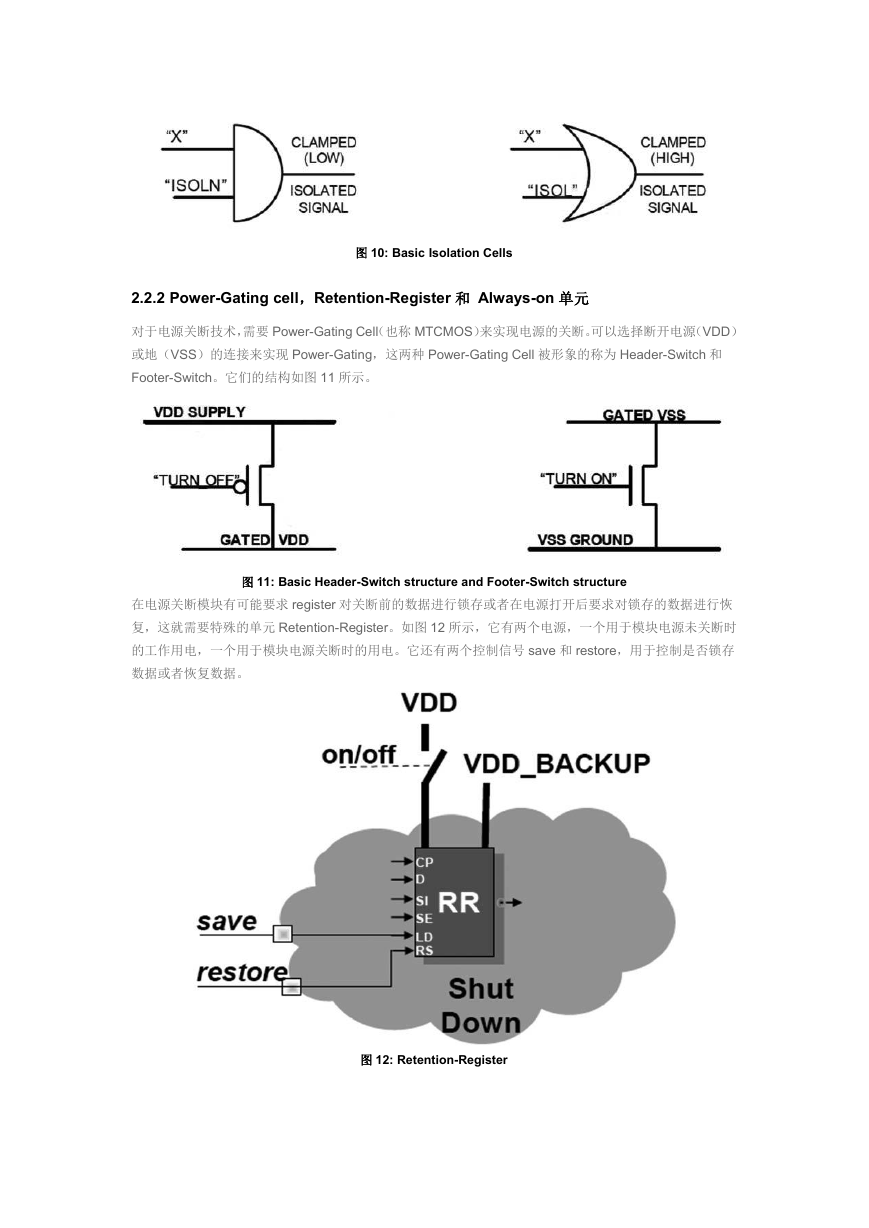

对于电源关断技术,电源关断区域的输出信号在电源关断时处于不定态,这种不定态会导致其负载单元出

现内部电流,从而导致不期望的功耗。所以需要在电源关断区域的输出信号上插入 Isolation Cell 来实现对

不定态的隔离。Isolation cell 根据钳位值不同分为与型和或型结构,其结构如图 10 所示。

�

图 10: Basic Isolation Cells

2.2.2 Power-Gating cell,Retention-Register 和 Always-on 单元

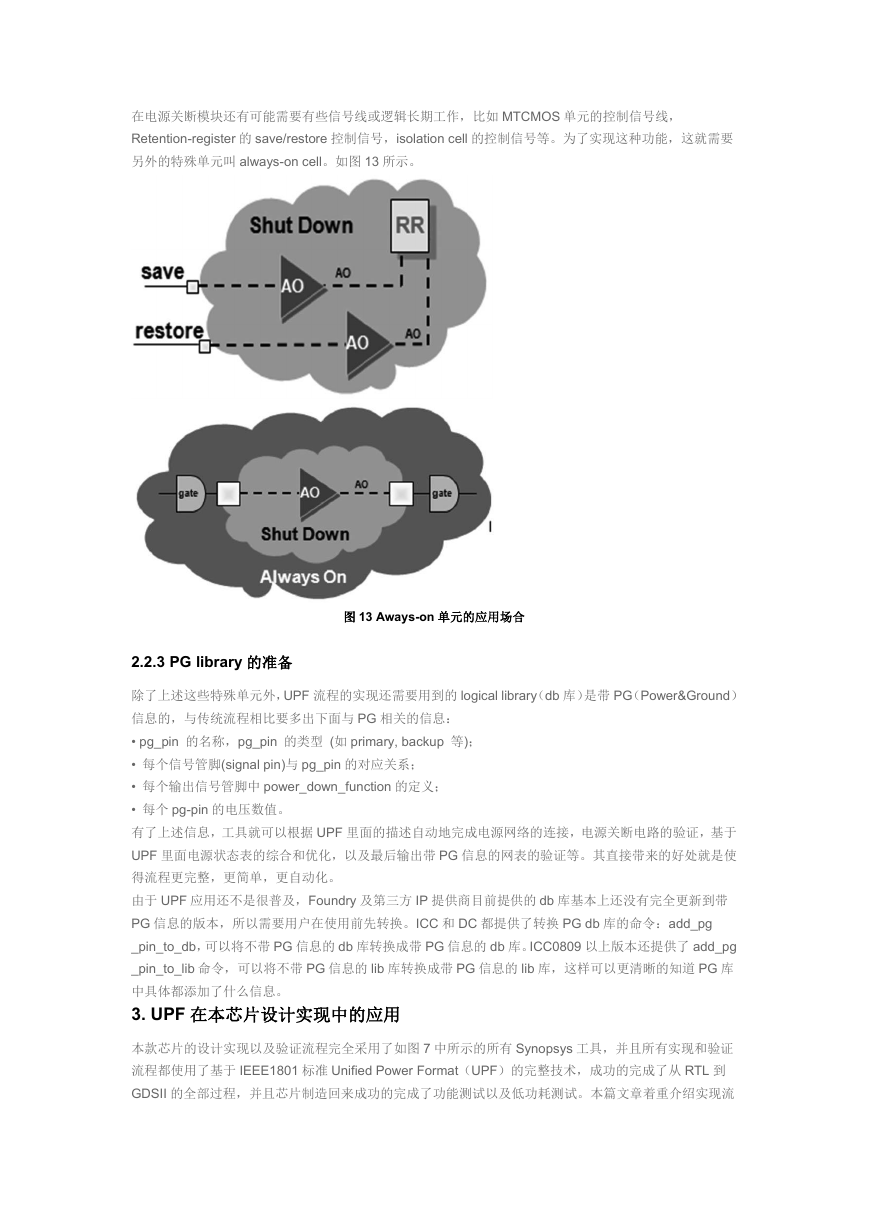

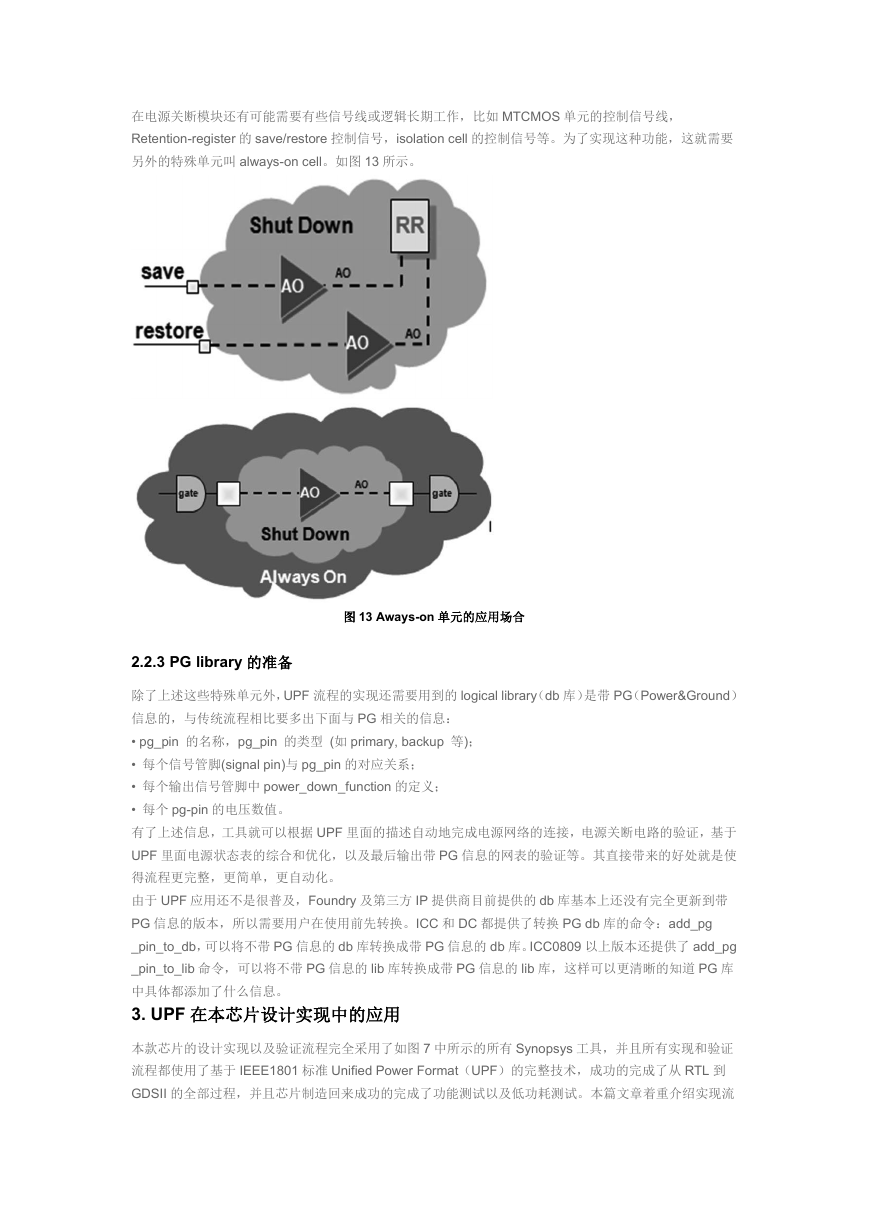

对于电源关断技术,需要 Power-Gating Cell(也称 MTCMOS)来实现电源的关断。可以选择断开电源(VDD)

或地(VSS)的连接来实现 Power-Gating,这两种 Power-Gating Cell 被形象的称为 Header-Switch 和

Footer-Switch。它们的结构如图 11 所示。

图 11: Basic Header-Switch structure and Footer-Switch structure

在电源关断模块有可能要求 register 对关断前的数据进行锁存或者在电源打开后要求对锁存的数据进行恢

复,这就需要特殊的单元 Retention-Register。如图 12 所示,它有两个电源,一个用于模块电源未关断时

的工作用电,一个用于模块电源关断时的用电。它还有两个控制信号 save 和 restore,用于控制是否锁存

数据或者恢复数据。

图 12: Retention-Register

�

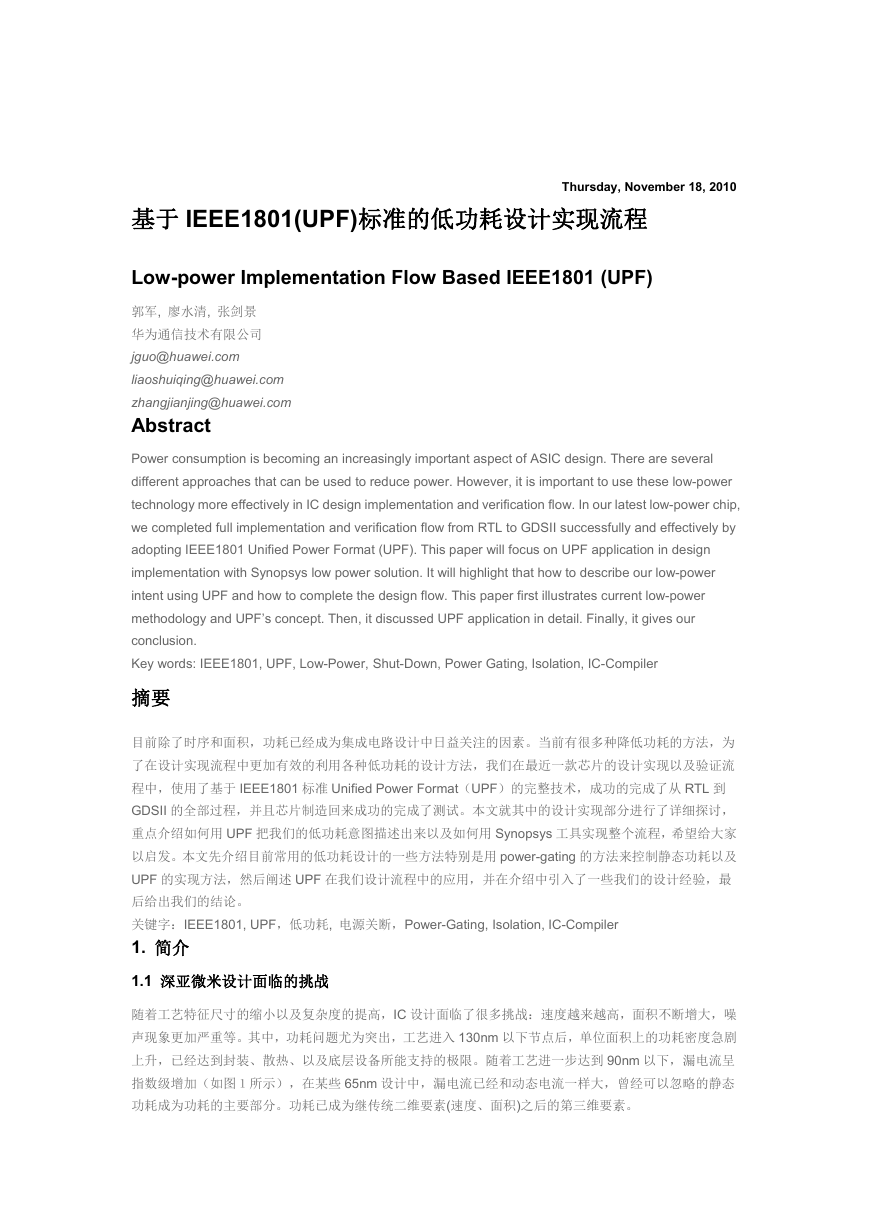

在电源关断模块还有可能需要有些信号线或逻辑长期工作,比如 MTCMOS 单元的控制信号线,

Retention-register 的 save/restore 控制信号,isolation cell 的控制信号等。为了实现这种功能,这就需要

另外的特殊单元叫 always-on cell。如图 13 所示。

图 13 Aways-on 单元的应用场合

2.2.3 PG library 的准备

除了上述这些特殊单元外,UPF 流程的实现还需要用到的 logical library(db 库)是带 PG(Power&Ground)

信息的,与传统流程相比要多出下面与 PG 相关的信息:

• pg_pin 的名称,pg_pin 的类型 (如 primary, backup 等);

• 每个信号管脚(signal pin)与 pg_pin 的对应关系;

• 每个输出信号管脚中 power_down_function 的定义;

• 每个 pg-pin 的电压数值。

有了上述信息,工具就可以根据 UPF 里面的描述自动地完成电源网络的连接,电源关断电路的验证,基于

UPF 里面电源状态表的综合和优化,以及最后输出带 PG 信息的网表的验证等。其直接带来的好处就是使

得流程更完整,更简单,更自动化。

由于 UPF 应用还不是很普及,Foundry 及第三方 IP 提供商目前提供的 db 库基本上还没有完全更新到带

PG 信息的版本,所以需要用户在使用前先转换。ICC 和 DC 都提供了转换 PG db 库的命令:add_pg

_pin_to_db,可以将不带 PG 信息的 db 库转换成带 PG 信息的 db 库。ICC0809 以上版本还提供了 add_pg

_pin_to_lib 命令,可以将不带 PG 信息的 lib 库转换成带 PG 信息的 lib 库,这样可以更清晰的知道 PG 库

中具体都添加了什么信息。

3. UPF 在本芯片设计实现中的应用

本款芯片的设计实现以及验证流程完全采用了如图 7 中所示的所有 Synopsys 工具,并且所有实现和验证

流程都使用了基于 IEEE1801 标准 Unified Power Format(UPF)的完整技术,成功的完成了从 RTL 到

GDSII 的全部过程,并且芯片制造回来成功的完成了功能测试以及低功耗测试。本篇文章着重介绍实现流

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc