您 的 论 文 得 到 两 院 院 士 关 注

文章编号:1008- 0570(2007)04- 2- 0219- 02

P LD CP LD FP GA 应 用

基于 FPGA 的 MFSK 调制电路设计与仿真

Des ig n an d Sim u latio n o f MFSK Mo d u latio n Circu it Bas ed o n FPGA

( 蚌埠中国人民解放军汽车管理学院) 杨 大 柱

YANG DAZHU

摘要: 数 字 调 制 解 调 技 术 在 数 字 通 信 中 占 有 非 常 重 要 的 地 位 , 数 字 通 信 技 术 与 FPGA 的 结 合 是 现 代 通 信 系 统 发 展 的 一 个 必

然 趋 势 。 文 中 介 绍 了 MFSK 调 制 解 调 的 原 理 , 并 基 于 FPGA 实 现 了 MFSK 调 制 电 路,仿 真 结 果 表 明 了 该 设 计 的 正 确 性 。

关键词:MFSK; FPGA; 调制;解调

中图分类号:TN919 文献标识码:A

Abstr act: Technology of digital modulation and demodulation plays a important role in digital communication system, the combination

of digital communication technology and FPGA is a certainly trend .The paper introduces the principle of MFSK modulation and de-

modulation, the modulation circuit are also be realized based on FPGA. The simulation result provides the correction of the design.

Key wor ds: MFSK, FPGA, modulation, demodulation

数 字 信 号 传 输 系 统 分 为 基 带 传 输 系 统 和 频 带 传 输 系 统.频

带 传 输 系 统 也 叫 数 字 调 制 系 统 。 数 字 调 制 信 号 又 称 为 键 控 信

号, 数 字调 制 过 程中 处 理 的是 数 字 信号, 而 载 波有 振 幅 、频率 和

相 位 3 个 变 量, 且二 进 制 的信 号 只 有高 低 电 平两 个 逻 辑量 1 和

0, 所 以调 制 的 过程 可 用 键控 的 方 法由 基 带 信号 对 载 频信 号 的

振幅 、频 率 及相 位 进 行调 制, 最 基本 的 方 法有 3 种: 正 交幅 度 调

制(QAM)、频 移 键 控(FSK)、相 移 键 控(PSK).根 据 所 处 理 的 基 带 信

号 的 进 制 不 同 分 为 二 进 制 和 多 进 制 调 制(M 进 制).多 进 制 数 字

调制与二进制相比, 其频谱利用率更高。本文研究了基于 FPGA

的 MFSK (多 频 键 控) 调 制 电 路 的 实 现 方 法 , 并 给 出 了 MAX+

PLUSII环境下的仿真结果。

1 MFSK 简 介

MFSK 系 统 是 2FSK(二 频 键 控)系 统 的 推 广,该 系 统 有 M 个

不同的载波频率可供选择, 每一个载波频率对应一个 M 进制码

元 信 息 , 即 用 多 个 频 率 不 同 的 正 弦 波 分 别 代 表 不 同 的 数 字 信

号, 在某一码元时间内只发送其中一个频率。MFSK 信号可表示

为:

( 1)

式( 1) 中

ωi 为 载 波 角 频 率 , 通 常 采 用 相 位 不 连 续 的 振 荡 频 率 , 这 样

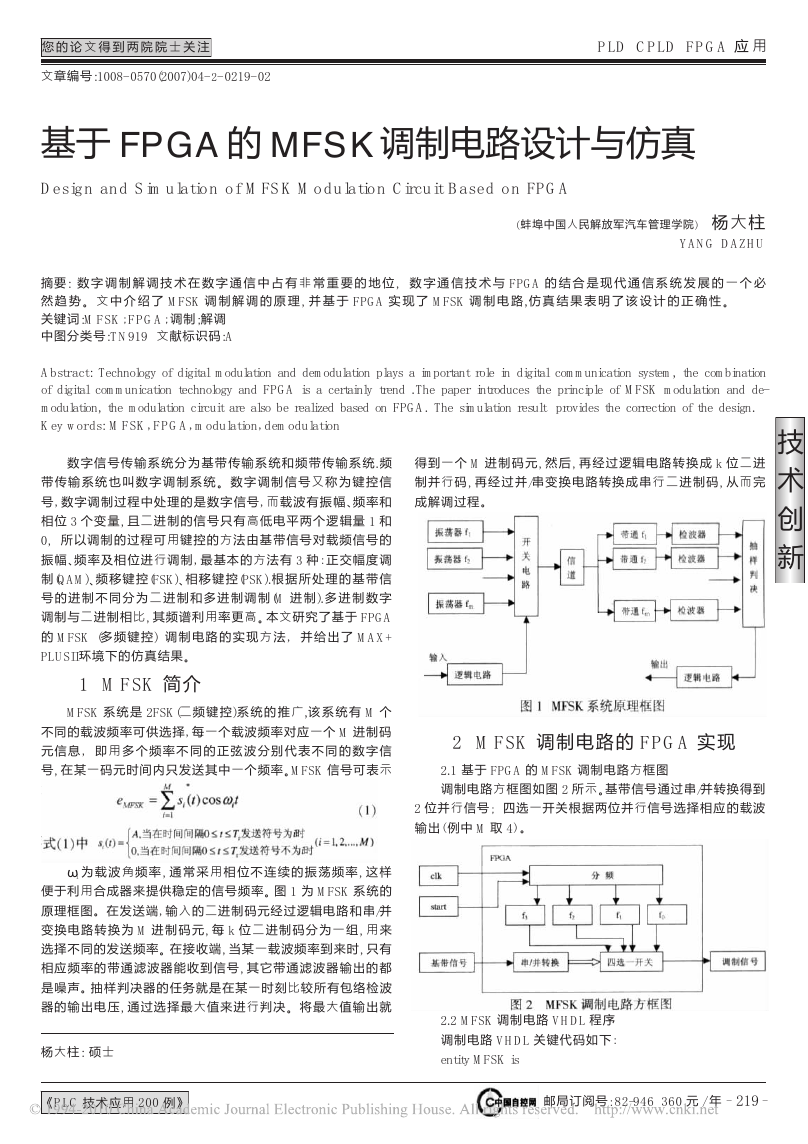

便于利用合成器来提供稳定的信号频率。图 1 为 MFSK 系统的

原理框图。在发送端, 输入的二进制码元经过逻辑电 路 和 串/并

变 换 电 路 转 换 为 M 进 制 码 元, 每 k 位 二 进 制 码 分 为 一 组 , 用 来

选择不同的发送频率。在接收端, 当某一载波频率到来时, 只有

相应 频 率的 带 通 滤波 器 能 收到 信 号, 其它 带 通 滤波 器 输 出的 都

是噪声。抽样判决器的任务就是在某一时刻比较所有包络检波

器的 输 出电 压, 通 过选 择 最 大值 来 进 行判 决 。将 最大 值 输 出 就

杨大柱: 硕士

《PLC 技术应用 200 例》

得到 一 个 M 进 制 码 元, 然 后 , 再 经 过 逻 辑 电 路 转 换 成 k 位 二 进

制并 行 码 , 再 经 过 并/串 变 换 电 路 转 换 成 串 行 二 进 制 码 , 从 而 完

成解调过程。

图 1 MFSK 系统原理框图

2 MFSK 调 制 电 路 的 FPGA 实 现

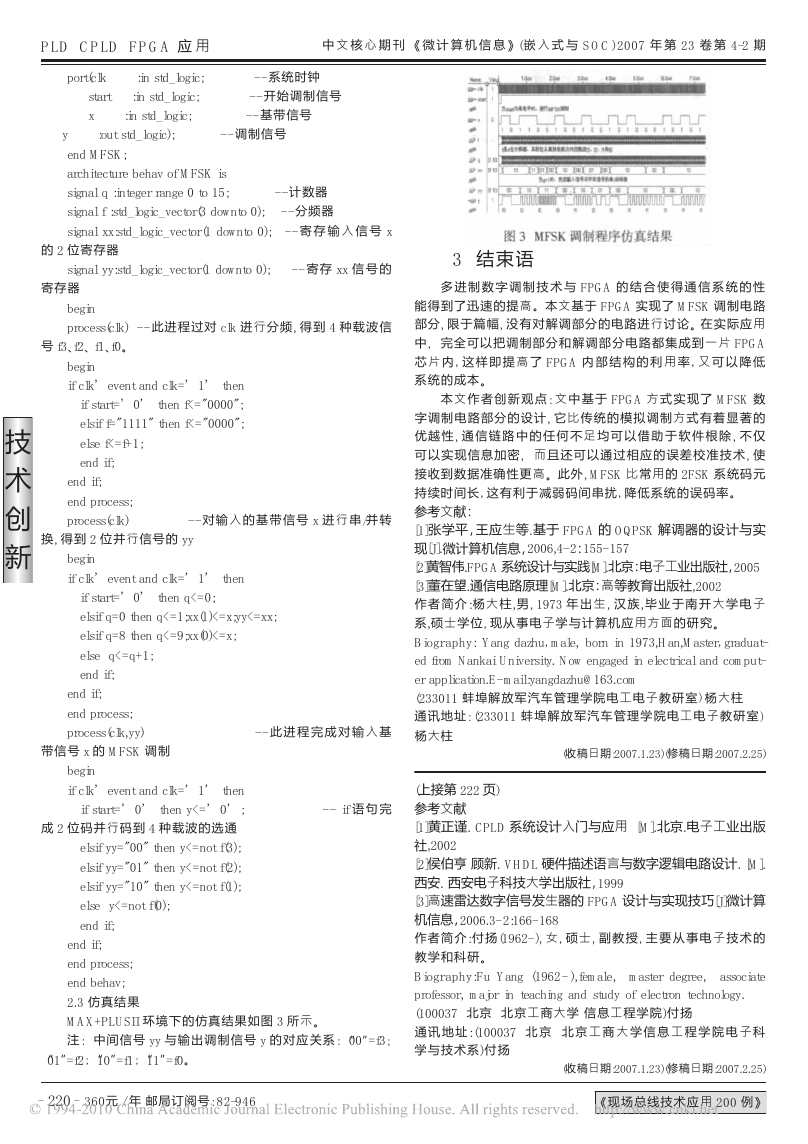

2.1 基于 FPGA 的 MFSK 调制电路方框图

调制电路方框图如图 2 所示。基带信号通过串/并转换得到

2 位并行信号; 四选一开关根据两位并行信号选择相 应 的 载波

输出( 例中 M 取 4) 。

图 2 MFSK 调制电路方框图

2.2 MFSK 调制电路 VHDL 程序

调制电路 VHDL 关键代码如下:

entity MFSK is

邮局订阅号: 82-946 360 元 / 年

-

219

-

技

术

创

新

�

P LD CP LD FP GA 应 用

中 文 核 心 期 刊 《 微 计 算 机 信 息 》( 嵌 入 式 与 SOC )2007 年 第 23 卷 第 4-2 期

port(clk

start

x

:in std_logic;

:in std_logic;

:in std_logic;

- - 系统时钟

- - 开始调制信号

- - 基带信号

- - 调制信号

:out std_logic);

y

end MFSK;

architecture behav of MFSK is

signal q :integer range 0 to 15;

signal f :std_logic_vector(3 downto 0);

signal xx:std_logic_vector(1 downto 0);

- - 计数器

- - 分频器

- - 寄 存 输 入 信 号 x

的 2 位寄存器

signal yy:std_logic_vector(1 downto 0);

- - 寄 存 xx 信 号 的

寄存器

begin

process(clk) - - 此进 程 过对 clk 进 行 分频, 得 到 4 种载 波 信

号 f3、f2、f1、f0。

begin

if clk' event and clk=' 1'

then

then f<="0000";

if start=' 0'

elsif f="1111" then f<="0000";

else f<=f+1;

end if;

end if;

end process;

process(clk)

- - 对 输 入 的 基 带 信 号 x 进 行 串/并 转

换, 得到 2 位并行信号的 yy

begin

if clk' event and clk=' 1'

then

then q<=0;

if start=' 0'

elsif q=0 then q<=1;xx(1)<=x;yy<=xx;

elsif q=8 then q<=9;xx(0)<=x;

else q<=q+1;

end if;

技

术

创

新

end if;

end process;

process(clk,yy)

带信号 x 的 MFSK 调制

begin

if clk' event and clk=' 1'

if start=' 0'

then y<=' 0'

- - 此 进 程 完 成 对 输 入 基

- - if 语 句 完

then

;

成 2 位码并行码到 4 种载波的选通

elsif yy="00" then y<=not f(3);

elsif yy="01" then y<=not f(2);

elsif yy="10" then y<=not f(1);

else y<=not f(0);

end if;

end if;

end process;

end behav;

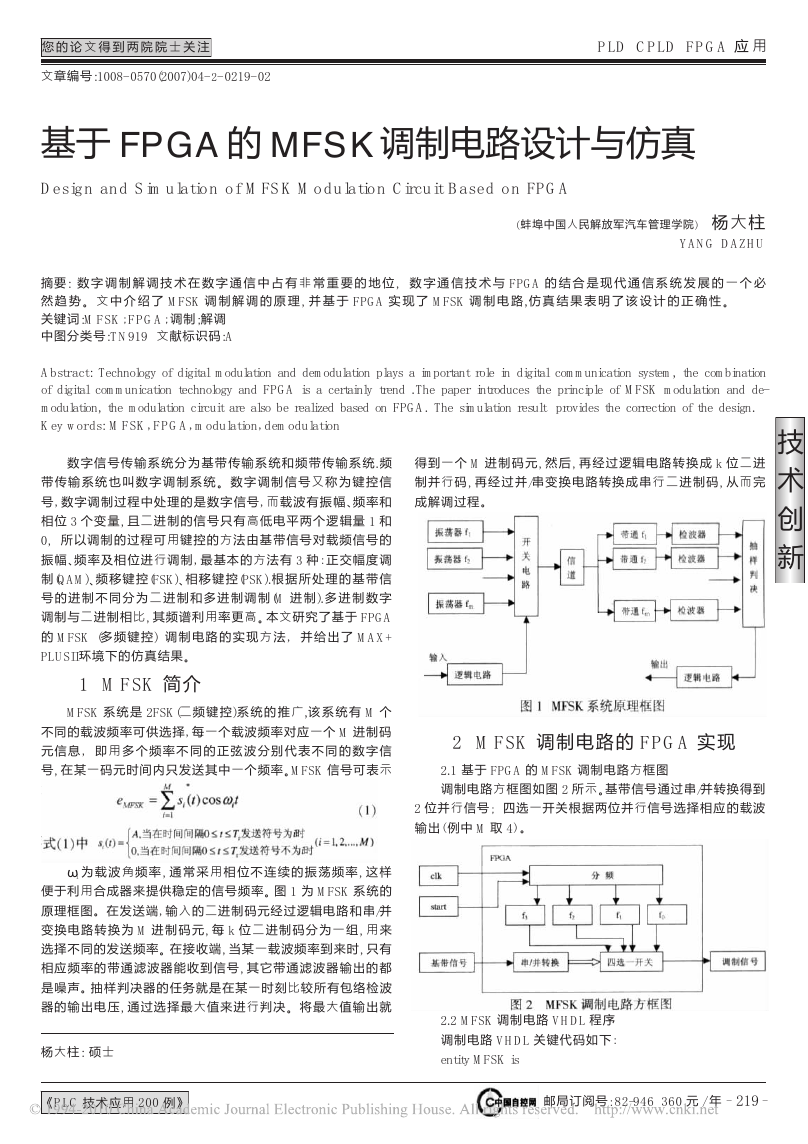

2.3 仿真结果

MAX+PLUSII 环境下的仿真结果如图 3 所示。

注: 中间信号 yy 与 输 出调 制 信 号 y 的 对 应 关系: “00”=f3;

“01”=f2; “10”=f1; “11”=f0。

-

220

-

360元 / 年 邮局订阅号: 82-946

图 3 MFSK 调制程序仿真结果

3 结 束 语

多 进 制 数 字 调 制 技 术 与 FPGA 的 结 合 使 得 通 信 系 统 的 性

能得到了迅速的提高。本文基于 FPGA 实现了 MFSK 调制电路

部分, 限于篇幅, 没有对解调部分的电路进行讨论。在实际应用

中, 完全可以把调制部 分 和 解调 部 分 电路 都 集 成到 一 片 FPGA

芯 片 内 , 这 样 即 提 高 了 FPGA 内 部 结 构 的 利 用 率 , 又 可 以 降 低

系统的成本。

本 文 作 者 创 新 观 点: 文 中 基 于 FPGA 方 式 实 现 了 MFSK 数

字 调制 电 路 部分 的 设 计, 它 比 传 统的 模 拟 调制 方 式 有着 显 著 的

优 越 性 , 通 信 链 路 中 的 任 何 不 足 均 可 以 借 助 于 软 件 根 除 , 不 仅

可 以 实现 信 息 加密, 而 且 还可 以 通 过相 应 的 误差 校 准 技术 , 使

接收到数据准确性更高。此外, MFSK 比常用的 2FSK 系统码元

持续时间长, 这有利于减弱码间串扰, 降低系统的误码率。

参考文献:

[1]张学平,王应生等.基于 FPGA 的 OQPSK 解调器的设计与实

现[J].微计算机信息,2006,4- 2:155- 157

[2]黄智伟.FPGA 系统设计与实践[M].北京:电子工业出版社,2005

[3]董在望.通信电路原理[M].北京:高等教育出版社,2002

作 者 简 介: 杨 大 柱,男 , 1973 年 出 生 , 汉 族,毕 业 于 南 开 大 学 电 子

系,硕士学位, 现从事电子学与计算机应用方面的研究。

Biogr aphy: Yang dazhu, male, born in 1973,Han,Master, graduat-

ed from Nankai University. Now engaged in electrical and comput-

er application.E- mail:yangdazhu@163.com

(233011 蚌埠解放军汽车管理学院电工电子教研室) 杨大柱

通讯地址: (233011 蚌埠 解 放军 汽 车 管理 学 院 电工 电 子 教研 室)

杨大柱

(收稿日期:2007.1.23)(修稿日期:2007.2.25)

(上接第 222 页)

参考文献

[1]黄正谨. CPLD 系统设计入门与应用 [M].北京.电子工业出版

社,2002

[2]侯伯亨 顾新. VHDL 硬件描述语言与数字逻辑电路设计. [M].

西安. 西安电子科技大学出版社,1999

[3]高速雷达数字信号发生器的 FPGA 设计与实现技巧[J]微计算

机信息,2006.3- 2:166- 168

作者 简 介: 付 扬(1962- ), 女, 硕士, 副 教 授, 主 要 从 事 电 子 技 术 的

教学和科研。

Biogr aphy:Fu Yang (1962- ),female, master degree,

professor, major in teaching and study of electron technology.

(100037 北京 北京工商大学 信息工程学院)付扬

通 讯 地 址:(100037 北 京 北 京 工 商 大 学 信 息 工 程 学 院 电 子 科

学与技术系)付扬

associate

(收稿日期:2007.1.23)(修稿日期:2007.2.25)

《现场总线技术应用 200 例》

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc