1,DSP+FPGA 实时信号处理系统

2,FPGA+DSP 实时三维图像信息处理系统

3,采用 FPGA+DSP 结构的多通道高速数据采集与实时图像处理系统的设计与实现方案

4,基于 DSP 与 FPGA 的蓝牙数据采集系统设计

5,基于 DSP 和 FPGA 的通用图像处理平台设计

6,基于 FPGA+ DSP 的实时图像处理系统设计与实现

7,基于 DSP 的实时图像目标搜索与跟踪系统设计

1,DSP+FPGA 实时信号处理系统

实时信号处理系统要求必须具有处理大数据量的能力,以保证系统的实时性;其次对系统的

体积、功耗、稳定性等也有较严格的要求。实时信号处理算法中经常用到对图象的求和、求

差运算,二维梯度运算,图象分割及区域特征提取等不同层次、不同种类的处理。其中有的

运算本身结构比较简单,但是数据量大,计算速度要求高;有些处理对速度并没有特殊的要

求,但计算方式和控制结构比较复杂,难以用纯硬件实现。因此,实时信号处理系统是对运

算速度要求高、运算种类多的综合性信息处理系统。

1 信号处理系统的类型与常用处理机结构

根据信号处理系统在构成、处理能力以及计算问题到硬件结构映射方法的不同,将现代

信号处理系统分为三大类:

·指令集结构(ISA)系统。在由各种微处理器、DSP处理器或专用指令集处理器

等组成的信号处理系统中,都需要通过系统中的处理器所提供的指令系统(或微代码)来描

述各种算法,并在指令部件的控制下完成对各种可计算问题的求解。

·硬连线结构系统。主要是指由专用集成电路(ASIC)构成的系统,其基本特征是

功能固定、通常用于完成特定的算法,这种系统适合于实现功能固定和数据结构明确的计算

问题。不足之处主要在于:设计周期长、成本高,且没有可编程性,可扩展性差。

·可重构系统。基本特征是系统中有一个或多个可重构器件(如FPGA),可重构处

理器之间或可重构处理器与ISA结构处理器之间通过互连结构构成一个完整的计算系统。

从系统信号处理系统的构成方式来看,常用的处理机结构有下面几种:单指令流单数据

流(SISD)、单指令流多数据流(SIMD)、多指令流多数据流(MIMD)。

·SISD结构通常由一个处理器和一个存贮器组成,它通过执行单一的指令流对单一

的数据流进行操作,指令按顺序读取,数据在每一时刻也只能读取一个。弱点是单片处理器

处理能力有限,同时,这种结构也没有发挥数据处理中的并行性潜力,所以在实时系统或高

速系统中,很少采用SISD结构。

· SIMD结构系统由一个控制器、多个处理器、多个存贮模块和一个互连网络组成。

所有“活动的”处理器在同一时刻执行同一条指令,但每个处理器执行这条指令时所用的数

据是从它本身的存储模块中读取的。对操作种类多的算法,当要求存取全局数据或对于不同

的数据要求做不同的处理时,它是无法独立胜任的。另外,SIMD 一般都要求有较多的

处理单元和极高的I/O吞吐率,如果系统中没有足够多的适合SIMD 处理的任务,采

用SIMD 是不合算的。

· MIMD结构就是通常所指的多处理机,典型的MIMD系统由多台处理机、多个存

储模块和一个互连网络组成,每台处理机执行自己的指令,操作数也是各取各的。MIMD

结构中每个处理器都可以单独编程,因而这种结构的可编程能力是最强的。但由于要用大量

的硬件资源解决可编程问题,硬件利用率不高。

2 DSP+ASIC结构

随着大规模可编程器件的发展,采用DSP+ASIC结构的信号处理系统显示出了其

�

优越性,正逐步得到重视。与通用集成电路相比,ASIC芯片具有体积小、重量轻、

功耗低、可靠性高等几个方面的优势,而且在大批量应用时,可降低成本。

现场可编程门阵列(FPGA)是在专用ASIC的基础上发展出来的,它克服了专用

ASIC不够灵活的缺点。与其他中小规模集成电路相比,其优点主要在于它有很强的灵活

性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改和维护很方便。目前,FP

GA的容量已经跨过了百万门级,使得FPGA成为解决系统级设计的重要选择方案之一。

DSP+FPGA结构最大的特点是结构灵活,有较强的通用性,适于模块化设计,从

而能够提高算法效率;同时其开发周期较短,系统易于维护和扩展,适合于实时信号处理。

实时信号处理系统中,低层的信号预处理算法处理的数据量大,对处理速度的要求高,

但运算结构相对比较简单,适于用FPGA进行硬件实现,这样能同时兼顾速度及灵活性。

高层处理算法的特点是所处理的数据量较低层算法少,但算法的控制结构复杂,适于用运算

速度高、寻址方式灵活、通信机制强大的DSP芯片来实现。

3 线性流水阵列结构

在我们的工作中,设计并实现了一种实时信号处理结构。它采用模块化设计和线性流水

阵列结构(图1)。

这种线性流水阵列结构具有如下特点:

·接口简单。各处理单元(PU)之间采用统一

的外部接口。

·易于扩充和维护。各个PU的内部结构完全相

同,而且外部接口统一,所以系统很容易根据需要

进行硬件的配置和扩充。当某个模块出现故障时,

也易于更换。

·处理模块的规范结构能够支持多种处理模式,

可以适应不同的处理算法。

每个PU的核心由DSP芯片和可重构器件F

PGA组成,另外还包括一些外围的辅助电路,如

存储器、先进先出(FIFO)器件及FLASH ROM等(图2)。可重构器件电路与

DSP处理器相连,利用DSP处理器强大的I/O功能实现单元电路内部和各个单元之间

的通信。从DSP的角度来看,可重构器件FPGA相当于它的宏功能协处理器(Co-p

rocessor)。

PU中的其他电路辅助核心电路进行工作。DSP和FPGA各自带有RAM,用于存

放处理过程所需要的数据及中间结果。FLASH ROM中存储了DSP的执行程序和F

PGA的配置数据。先进先出(FIFO)器件则用于实现信号处理中常用到的一些操作,

如延时线、顺序存储等。

每个PU单独做成一块PCB,各级PU之间通过插座与底板相连。底板的结构很简单,主

要由几个串连的插座构成,其作用是向各个PU提供通信通道和电源供应。可以根据需要安

排底板上插座的个数,组成多级线性阵列结构。这种模块化设计的突出优点在于,它使得对

系统的功能扩充和维护变得非常简单。需要时,只要插上或更换PU电路板,就可以实现系

统的扩展和故障的排除。每一级PU中的DSP都有通信端口与前级和后级PU电路板相

连,可以很方便地控制和协调它们之间的工作。

4 应用实例

我们应用上述线性流水阵列结构实现了一个实时目标检测系统,该系统的任务主要是接

收摄像头输出的灰度图象,经预处理、编码、直线拟合和目标识别后,输出结果到PC机显

�

示。在这个任务中,预处理模块包括抽样、卷积和编码等步骤,属于低层的处理,其运算数

据量大,但运算结构较规则,适于用FPGA进行纯硬件实现;而直线拟合及目标识别等高

层图象处理算法,所处理的数据量相对较少,但要用到多种数据结构,其控制也复杂得多,

我们用DSP编程来实现。

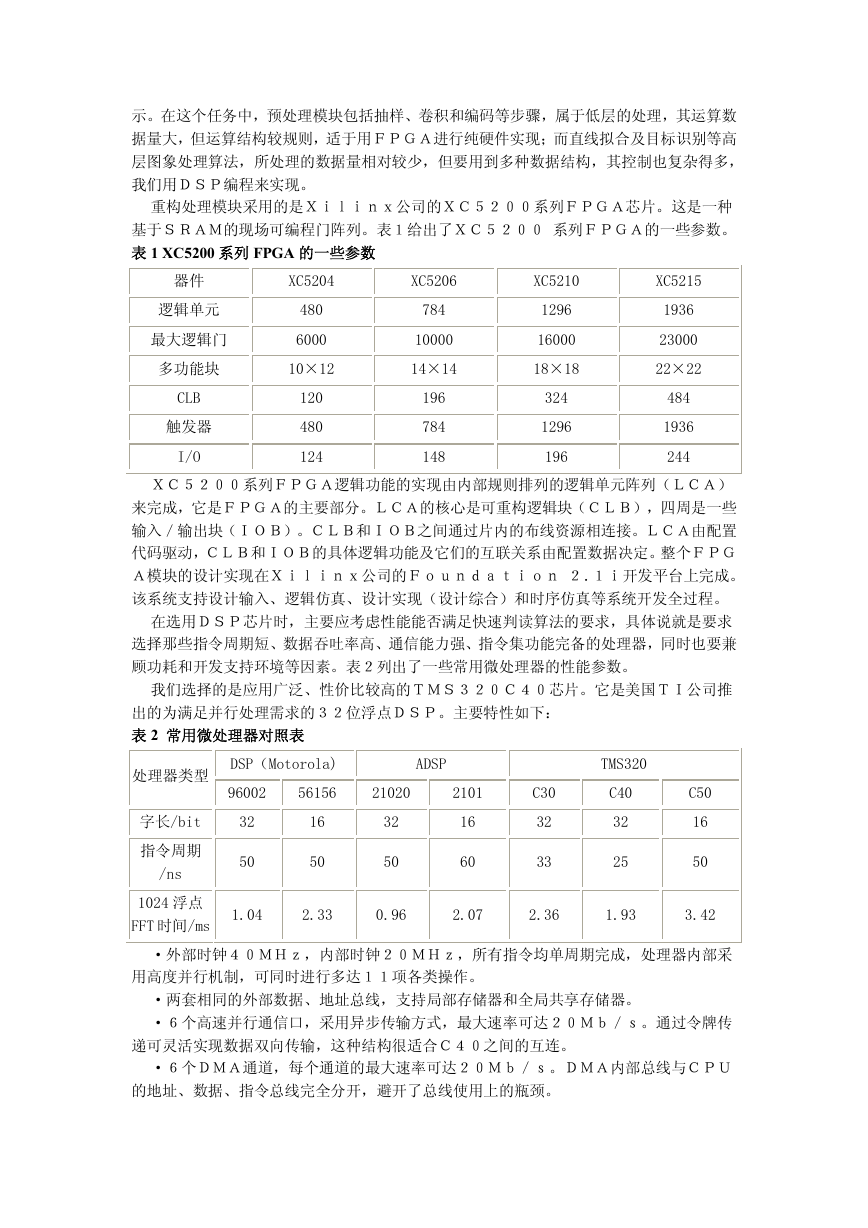

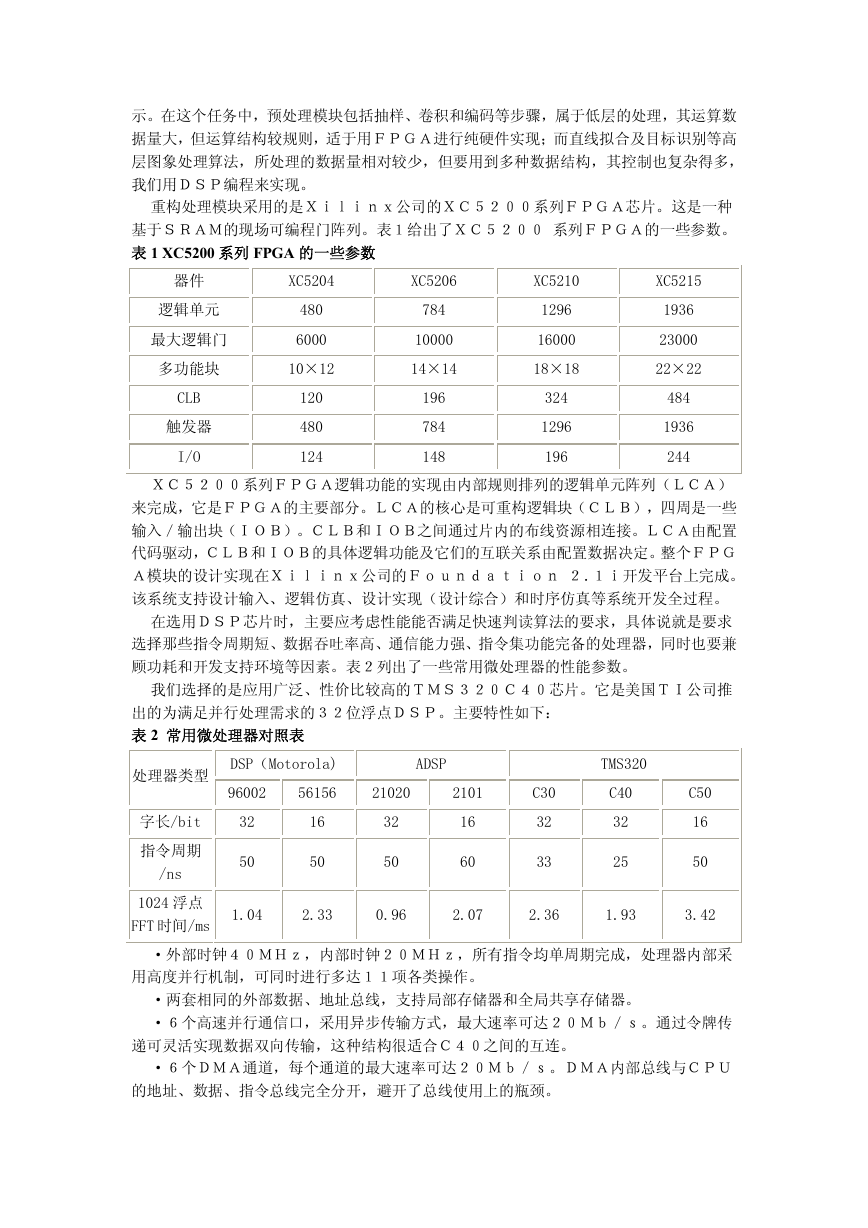

重构处理模块采用的是Xilinx公司的XC5200系列FPGA芯片。这是一种

基于SRAM的现场可编程门阵列。表1给出了XC5200 系列FPGA的一些参数。

表 1 XC5200 系列 FPGA 的一些参数

器件

XC5204

XC5206

XC5210

XC5215

逻辑单元

最大逻辑门

480

6000

多功能块

10×12

CLB

触发器

I/O

120

480

124

784

10000

14×14

196

784

148

1296

16000

1936

23000

18×18

22×22

324

1296

196

484

1936

244

XC5200系列FPGA逻辑功能的实现由内部规则排列的逻辑单元阵列(LCA)

来完成,它是FPGA的主要部分。LCA的核心是可重构逻辑块(CLB),四周是一些

输入/输出块(IOB)。CLB和IOB之间通过片内的布线资源相连接。LCA由配置

代码驱动,CLB和IOB的具体逻辑功能及它们的互联关系由配置数据决定。整个FPG

A模块的设计实现在Xilinx公司的Foundation 2.1i开发平台上完成。

该系统支持设计输入、逻辑仿真、设计实现(设计综合)和时序仿真等系统开发全过程。

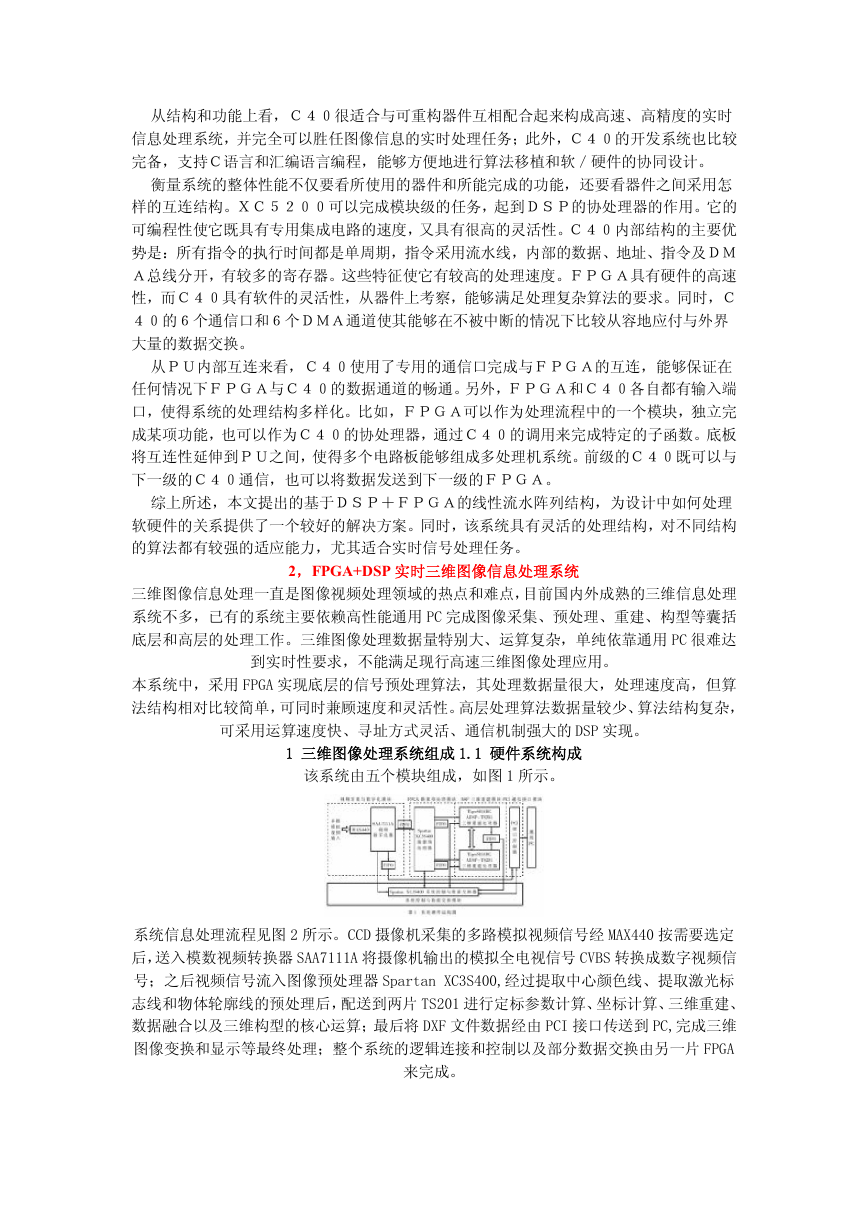

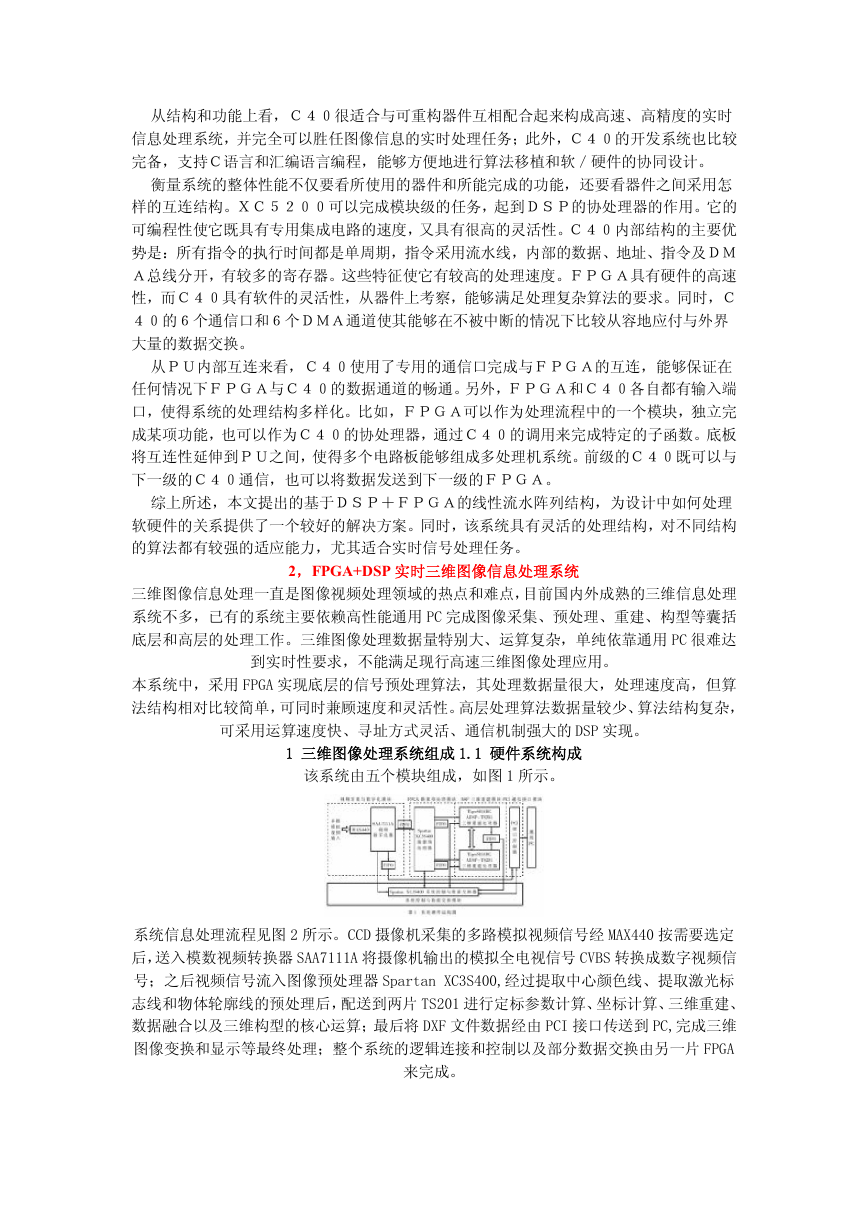

在选用DSP芯片时,主要应考虑性能能否满足快速判读算法的要求,具体说就是要求

选择那些指令周期短、数据吞吐率高、通信能力强、指令集功能完备的处理器,同时也要兼

顾功耗和开发支持环境等因素。表2列出了一些常用微处理器的性能参数。

我们选择的是应用广泛、性价比较高的TMS320C40芯片。它是美国TI公司推

出的为满足并行处理需求的32位浮点DSP。主要特性如下:

表 2 常用微处理器对照表

处理器类型

DSP(Motorola)

ADSP

96002

56156

21020

2101

字长/bit

32

指令周期

/ns

50

16

50

32

50

16

60

TMS320

C40

32

C50

16

C30

32

33

25

50

2.36

1.93

3.42

2.33

0.96

2.07

1.04

1024 浮点

FFT 时间/ms

·外部时钟40MHz,内部时钟20MHz,所有指令均单周期完成,处理器内部采

用高度并行机制,可同时进行多达11项各类操作。

·两套相同的外部数据、地址总线,支持局部存储器和全局共享存储器。

·6个高速并行通信口,采用异步传输方式,最大速率可达20Mb/s。通过令牌传

递可灵活实现数据双向传输,这种结构很适合C40之间的互连。

·6个DMA通道,每个通道的最大速率可达20Mb/s。DMA内部总线与CPU

的地址、数据、指令总线完全分开,避开了总线使用上的瓶颈。

�

从结构和功能上看,C40很适合与可重构器件互相配合起来构成高速、高精度的实时

信息处理系统,并完全可以胜任图像信息的实时处理任务;此外,C40的开发系统也比较

完备,支持C语言和汇编语言编程,能够方便地进行算法移植和软/硬件的协同设计。

衡量系统的整体性能不仅要看所使用的器件和所能完成的功能,还要看器件之间采用怎

样的互连结构。XC5200可以完成模块级的任务,起到DSP的协处理器的作用。它的

可编程性使它既具有专用集成电路的速度,又具有很高的灵活性。C40内部结构的主要优

势是:所有指令的执行时间都是单周期,指令采用流水线,内部的数据、地址、指令及DM

A总线分开,有较多的寄存器。这些特征使它有较高的处理速度。FPGA具有硬件的高速

性,而C40具有软件的灵活性,从器件上考察,能够满足处理复杂算法的要求。同时,C

40的6个通信口和6个DMA通道使其能够在不被中断的情况下比较从容地应付与外界

大量的数据交换。

从PU内部互连来看,C40使用了专用的通信口完成与FPGA的互连,能够保证在

任何情况下FPGA与C40的数据通道的畅通。另外,FPGA和C40各自都有输入端

口,使得系统的处理结构多样化。比如,FPGA可以作为处理流程中的一个模块,独立完

成某项功能,也可以作为C40的协处理器,通过C40的调用来完成特定的子函数。底板

将互连性延伸到PU之间,使得多个电路板能够组成多处理机系统。前级的C40既可以与

下一级的C40通信,也可以将数据发送到下一级的FPGA。

综上所述,本文提出的基于DSP+FPGA的线性流水阵列结构,为设计中如何处理

软硬件的关系提供了一个较好的解决方案。同时,该系统具有灵活的处理结构,对不同结构

的算法都有较强的适应能力,尤其适合实时信号处理任务。

2,FPGA+DSP 实时三维图像信息处理系统

三维图像信息处理一直是图像视频处理领域的热点和难点,目前国内外成熟的三维信息处理

系统不多,已有的系统主要依赖高性能通用 PC 完成图像采集、预处理、重建、构型等囊括

底层和高层的处理工作。三维图像处理数据量特别大、运算复杂,单纯依靠通用 PC 很难达

到实时性要求,不能满足现行高速三维图像处理应用。

本系统中,采用 FPGA 实现底层的信号预处理算法,其处理数据量很大,处理速度高,但算

法结构相对比较简单,可同时兼顾速度和灵活性。高层处理算法数据量较少、算法结构复杂,

可采用运算速度快、寻址方式灵活、通信机制强大的 DSP 实现。

1 三维图像处理系统组成 1.1 硬件系统构成

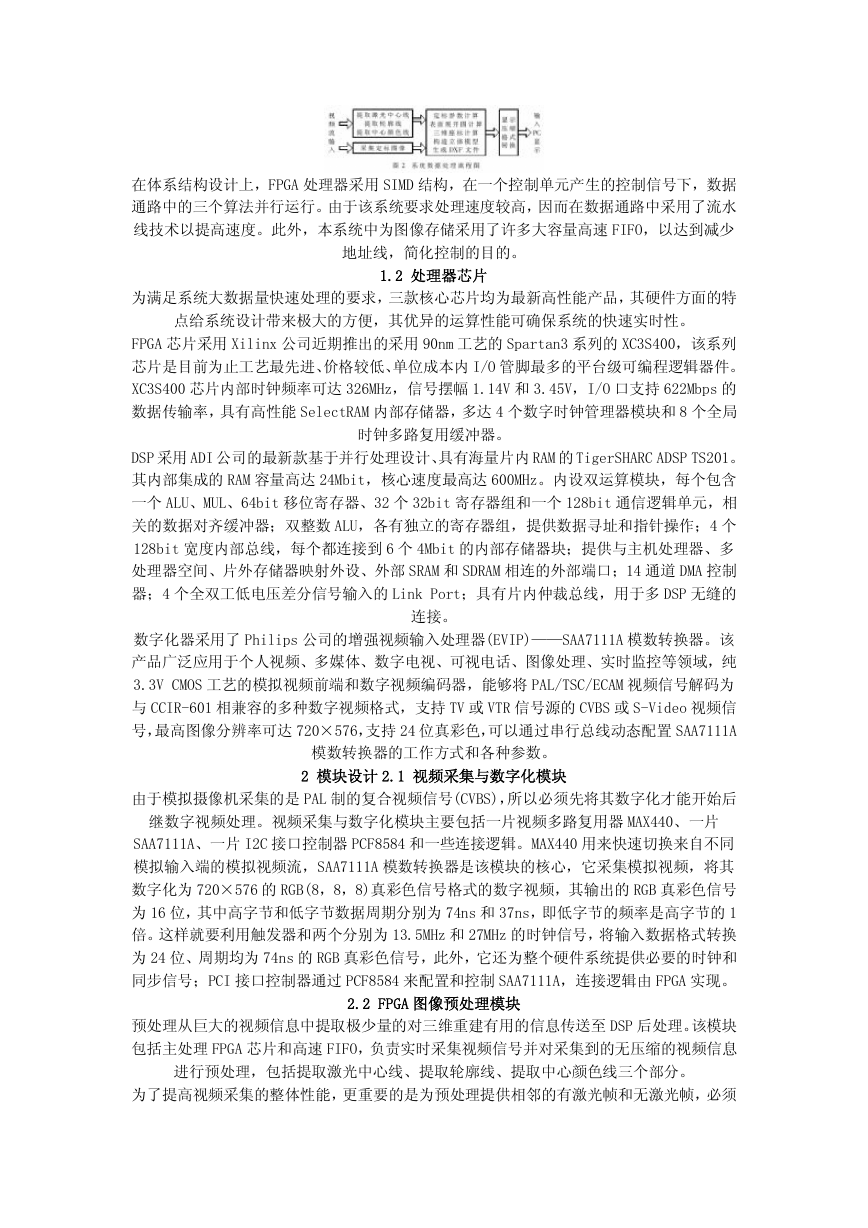

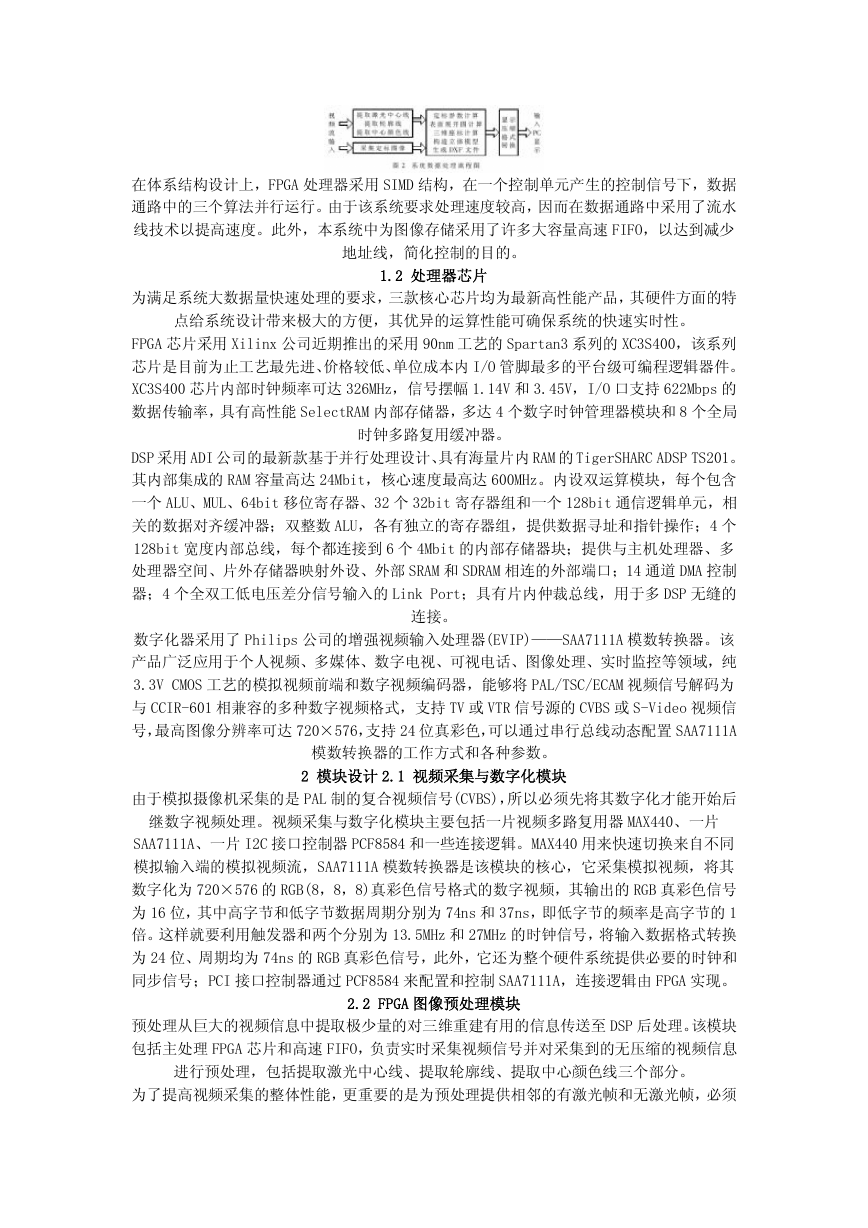

该系统由五个模块组成,如图 1 所示。

系统信息处理流程见图 2 所示。CCD 摄像机采集的多路模拟视频信号经 MAX440 按需要选定

后,送入模数视频转换器 SAA7111A 将摄像机输出的模拟全电视信号 CVBS 转换成数字视频信

号;之后视频信号流入图像预处理器 Spartan XC3S400,经过提取中心颜色线、提取激光标

志线和物体轮廓线的预处理后,配送到两片 TS201 进行定标参数计算、坐标计算、三维重建、

数据融合以及三维构型的核心运算;最后将 DXF 文件数据经由 PCI 接口传送到 PC,完成三维

图像变换和显示等最终处理;整个系统的逻辑连接和控制以及部分数据交换由另一片 FPGA

来完成。

�

在体系结构设计上,FPGA 处理器采用 SIMD 结构,在一个控制单元产生的控制信号下,数据

通路中的三个算法并行运行。由于该系统要求处理速度较高,因而在数据通路中采用了流水

线技术以提高速度。此外,本系统中为图像存储采用了许多大容量高速 FIFO,以达到减少

地址线,简化控制的目的。

1.2 处理器芯片

为满足系统大数据量快速处理的要求,三款核心芯片均为最新高性能产品,其硬件方面的特

点给系统设计带来极大的方便,其优异的运算性能可确保系统的快速实时性。

FPGA 芯片采用 Xilinx 公司近期推出的采用 90nm 工艺的 Spartan3 系列的 XC3S400,该系列

芯片是目前为止工艺最先进、价格较低、单位成本内 I/O 管脚最多的平台级可编程逻辑器件。

XC3S400 芯片内部时钟频率可达 326MHz,信号摆幅 1.14V 和 3.45V,I/O 口支持 622Mbps 的

数据传输率,具有高性能 SelectRAM 内部存储器,多达 4 个数字时钟管理器模块和 8 个全局

时钟多路复用缓冲器。

DSP 采用 ADI 公司的最新款基于并行处理设计、具有海量片内 RAM 的 TigerSHARC ADSP TS201。

其内部集成的 RAM 容量高达 24Mbit,核心速度最高达 600MHz。内设双运算模块,每个包含

一个 ALU、MUL、64bit 移位寄存器、32 个 32bit 寄存器组和一个 128bit 通信逻辑单元,相

关的数据对齐缓冲器;双整数 ALU,各有独立的寄存器组,提供数据寻址和指针操作;4 个

128bit 宽度内部总线,每个都连接到 6 个 4Mbit 的内部存储器块;提供与主机处理器、多

处理器空间、片外存储器映射外设、外部 SRAM 和 SDRAM 相连的外部端口;14 通道 DMA 控制

器;4 个全双工低电压差分信号输入的 Link Port;具有片内仲裁总线,用于多 DSP 无缝的

连接。

数字化器采用了 Philips 公司的增强视频输入处理器(EVIP)——SAA7111A 模数转换器。该

产品广泛应用于个人视频、多媒体、数字电视、可视电话、图像处理、实时监控等领域,纯

3.3V CMOS 工艺的模拟视频前端和数字视频编码器,能够将 PAL/TSC/ECAM 视频信号解码为

与 CCIR-601 相兼容的多种数字视频格式,支持 TV 或 VTR 信号源的 CVBS 或 S-Video 视频信

号,最高图像分辨率可达 720×576,支持 24 位真彩色,可以通过串行总线动态配置 SAA7111A

模数转换器的工作方式和各种参数。

2 模块设计 2.1 视频采集与数字化模块

由于模拟摄像机采集的是 PAL 制的复合视频信号(CVBS),所以必须先将其数字化才能开始后

继数字视频处理。视频采集与数字化模块主要包括一片视频多路复用器 MAX440、一片

SAA7111A、一片 I2C 接口控制器 PCF8584 和一些连接逻辑。MAX440 用来快速切换来自不同

模拟输入端的模拟视频流,SAA7111A 模数转换器是该模块的核心,它采集模拟视频,将其

数字化为 720×576 的 RGB(8,8,8)真彩色信号格式的数字视频,其输出的 RGB 真彩色信号

为 16 位,其中高字节和低字节数据周期分别为 74ns 和 37ns,即低字节的频率是高字节的 1

倍。这样就要利用触发器和两个分别为 13.5MHz 和 27MHz 的时钟信号,将输入数据格式转换

为 24 位、周期均为 74ns 的 RGB 真彩色信号,此外,它还为整个硬件系统提供必要的时钟和

同步信号;PCI 接口控制器通过 PCF8584 来配置和控制 SAA7111A,连接逻辑由 FPGA 实现。

2.2 FPGA 图像预处理模块

预处理从巨大的视频信息中提取极少量的对三维重建有用的信息传送至 DSP 后处理。该模块

包括主处理 FPGA 芯片和高速 FIFO,负责实时采集视频信号并对采集到的无压缩的视频信息

进行预处理,包括提取激光中心线、提取轮廓线、提取中心颜色线三个部分。

为了提高视频采集的整体性能,更重要的是为预处理提供相邻的有激光帧和无激光帧,必须

�

通过视频帧缓存首先暂存无激光帧。缓存由 3 片 AverLogic 公司的 AL422B 及一些由 FPGA

实现的连接逻辑组成;当前端模块输出无激光帧时,SA7111A 控制 3 片 AL422B 写操作,将

其存入 FIFO;当前端输出有激光帧时,后端的视频处理模块控制 3 片 AL422B 进行读操作,

读出暂存在其中的无激光帧数据。预处理 FPGA 将读取的无激光帧和有激光帧进行相减运算。

输出同样采用 3 组缓存分别用来暂存激光样条数据、目标轮廓线数据和图像中心线数据;所

有模块均采用同步时钟控制,同步时钟采用由 SAA7111A 模数转换器产生的 LLC2 信号。为了

提高系统速度,算法复杂、耗时较长的计算过程进行了流水线处理。

2.3 DSP 三维重建模块

为了应对三维图像大数据量复杂高速运算的需要,这里采用了两片 TigerSHARC 201 芯片并

行三维重建运算。由控制 FPGA 对两片 DSP 所要处理的图像进行任务分配,DSP 结合预处理

FPGA 存入 FIFO 的数据和 PCI 总线所给处理参数进行定标参数计算、坐标计算、三维重建和

构型。由于 TS201 内部集成的总线仲裁机制,双 DSP 可以实现无缝连接,大大减小了多 DSP

协调工作的设计难度。DSP 间的连接是依靠其拥有的全双工 LinkPort,它采用 LVDS(低电

平差分信号)输入数据。链路口能独立或同时工作,在时钟的上升沿和下降沿锁存数据。链

路时钟频率最高可以与处理器核相同,高达 500MHz,每个链路能完成 500Mbps 的单向数据

传输。每个 DSP 的 4 个 LinkPort 合起来最大的通透率为 4.0Gbps。连线短且简单,不需要

额外的辅助电路,且可有效防止连线长引起的信号畸变。LinkPort 传输协议由控制 FPGA 完

成。

2.4 PCI 通信接口模块

根据三维信息获取系统的速度传输要求,采用 PCI 接口完成该系统与通用 PC 的信息交互。

PCI 接口控制器是硬件部分的控制中心和数据交换中心,它接收设备驱动程序的命令和数

据,配置和控制系统的各个模块使其协调工作,完成系统任务;它还负责将采集到和处理后

的数据通过 PCI 总线转送给通用 PC。本系统采用 PLX 公司的 32bit/33MHz PCI9030 作为接

口芯片,串行 EEPROM-FM93CS56L 电可擦除只读存储器保存 PCI9030 的配置信息。

2.5 系统控制与数据交换模块

控制单元对处理器的数据处理单元和输入数据格式转换单元以及所有 FIFO 存储器产生控

制,与预处理 FPGA 配合完成 DSP 的 LinkPort 协议。由于数据处理单元中为流水处理,在控

制单元的设计中要特别注意由流水线产生的固定周期的延时,延时的周期数等于相应流水线

的级数。控制单元还与 PCI 接口连接,接收来自主计算机的控制信号和背景阈值等信息。控

制 FPGA 还是 SAA7111A、PCI 接口和 DSP 之间的图像和信息交换的桥梁,为其提供所需要的

参数和数据信息。

3 软件设计与实现 3.1 图像预处理算法

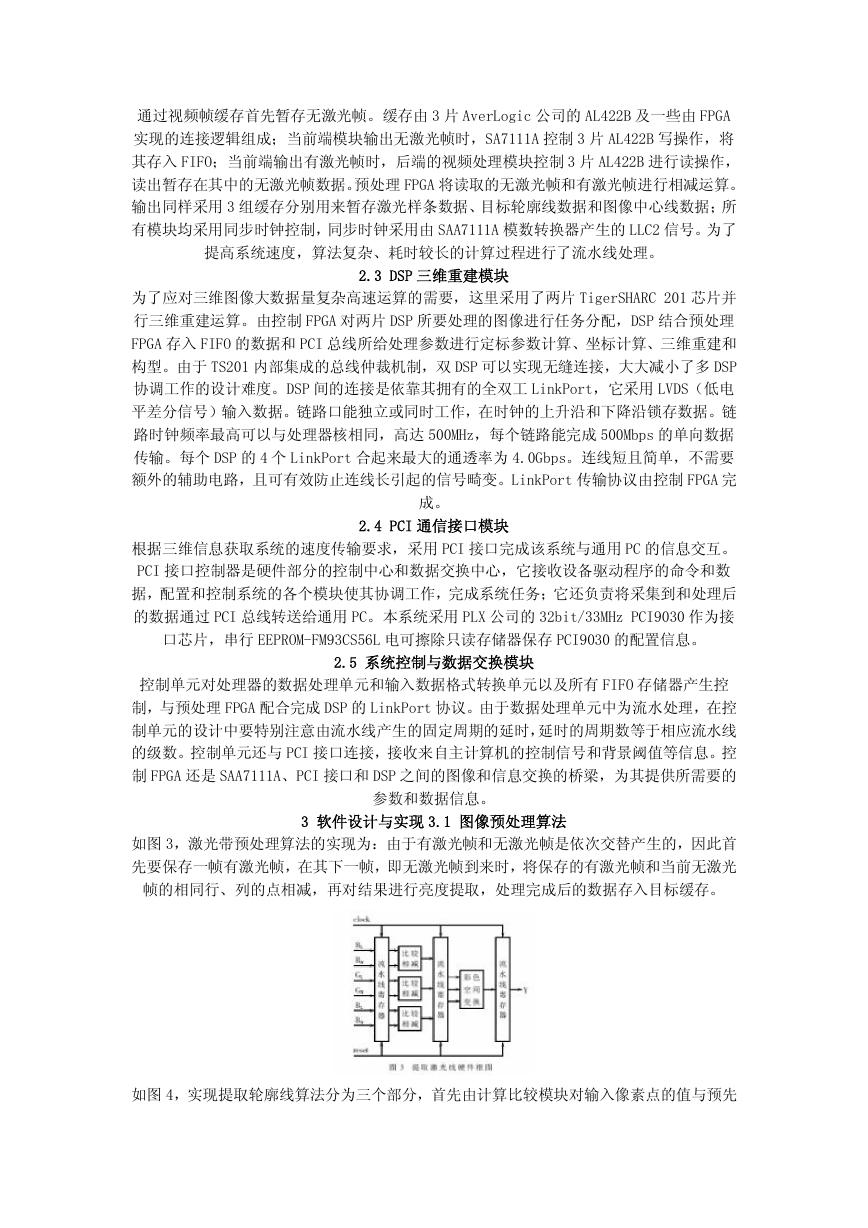

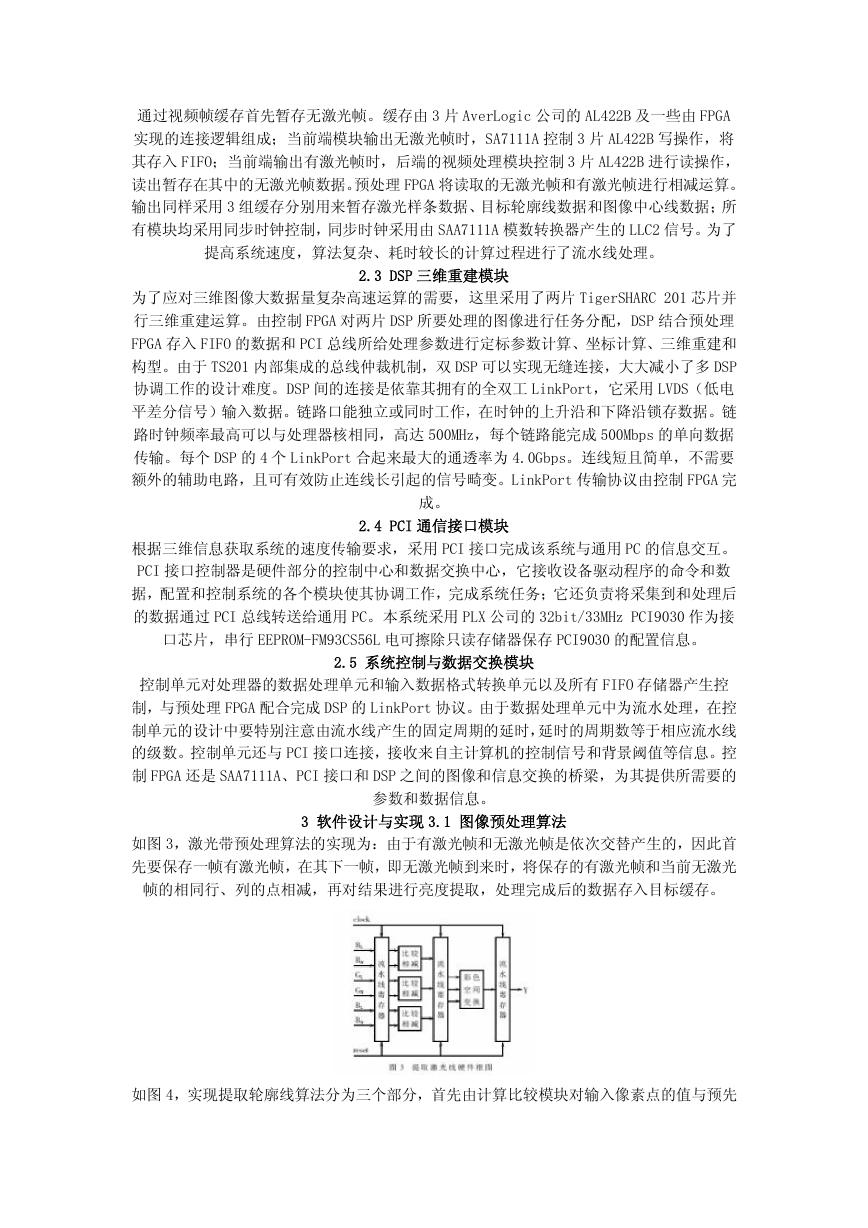

如图 3,激光带预处理算法的实现为:由于有激光帧和无激光帧是依次交替产生的,因此首

先要保存一帧有激光帧,在其下一帧,即无激光帧到来时,将保存的有激光帧和当前无激光

帧的相同行、列的点相减,再对结果进行亮度提取,处理完成后的数据存入目标缓存。

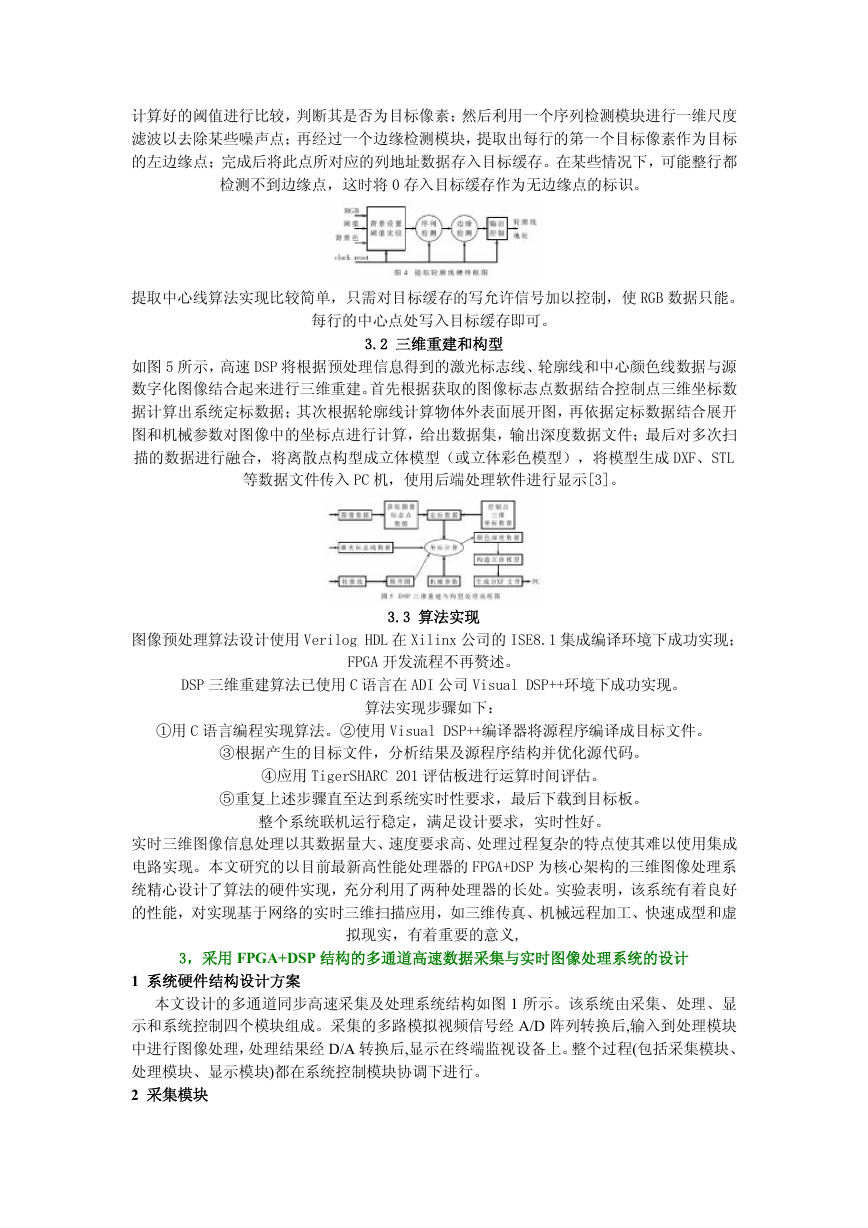

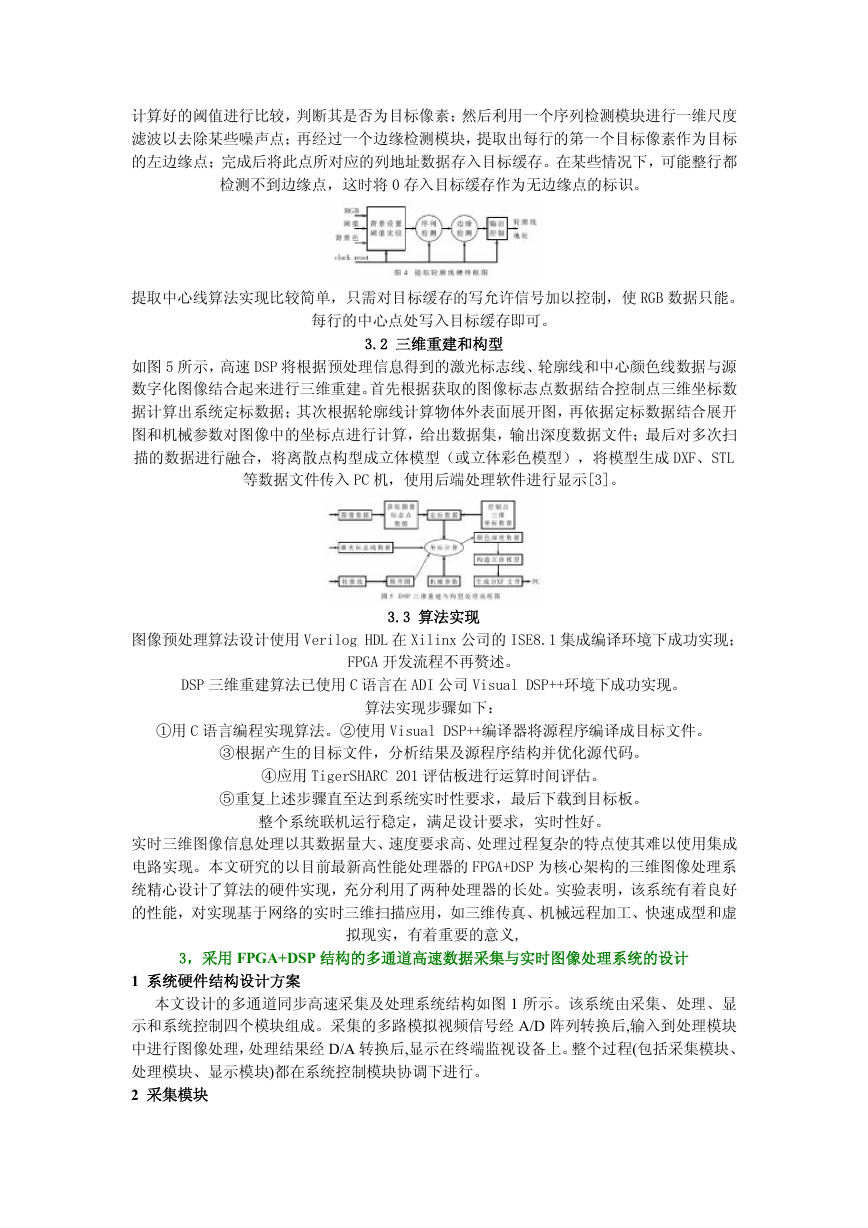

如图 4,实现提取轮廓线算法分为三个部分,首先由计算比较模块对输入像素点的值与预先

�

计算好的阈值进行比较,判断其是否为目标像素;然后利用一个序列检测模块进行一维尺度

滤波以去除某些噪声点;再经过一个边缘检测模块,提取出每行的第一个目标像素作为目标

的左边缘点;完成后将此点所对应的列地址数据存入目标缓存。在某些情况下,可能整行都

检测不到边缘点,这时将 0 存入目标缓存作为无边缘点的标识。

提取中心线算法实现比较简单,只需对目标缓存的写允许信号加以控制,使 RGB 数据只能。

每行的中心点处写入目标缓存即可。

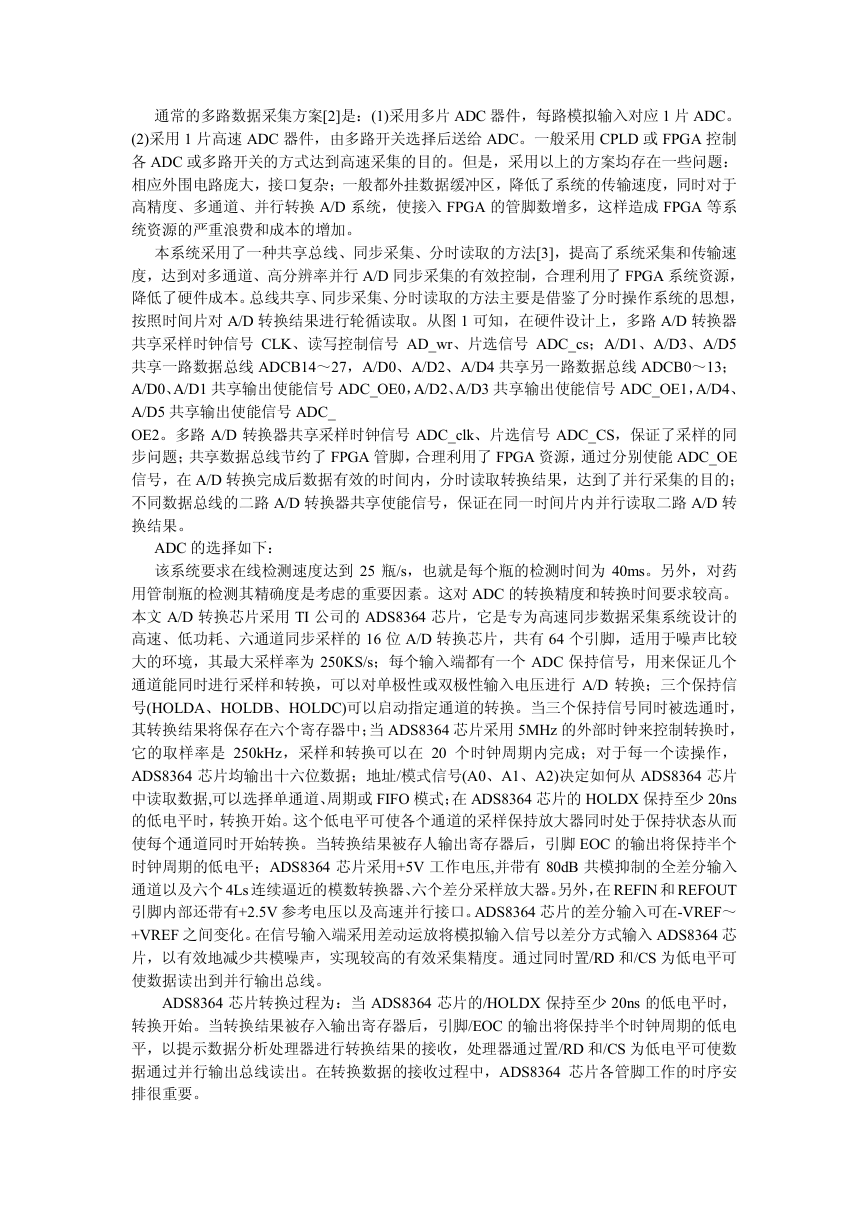

3.2 三维重建和构型

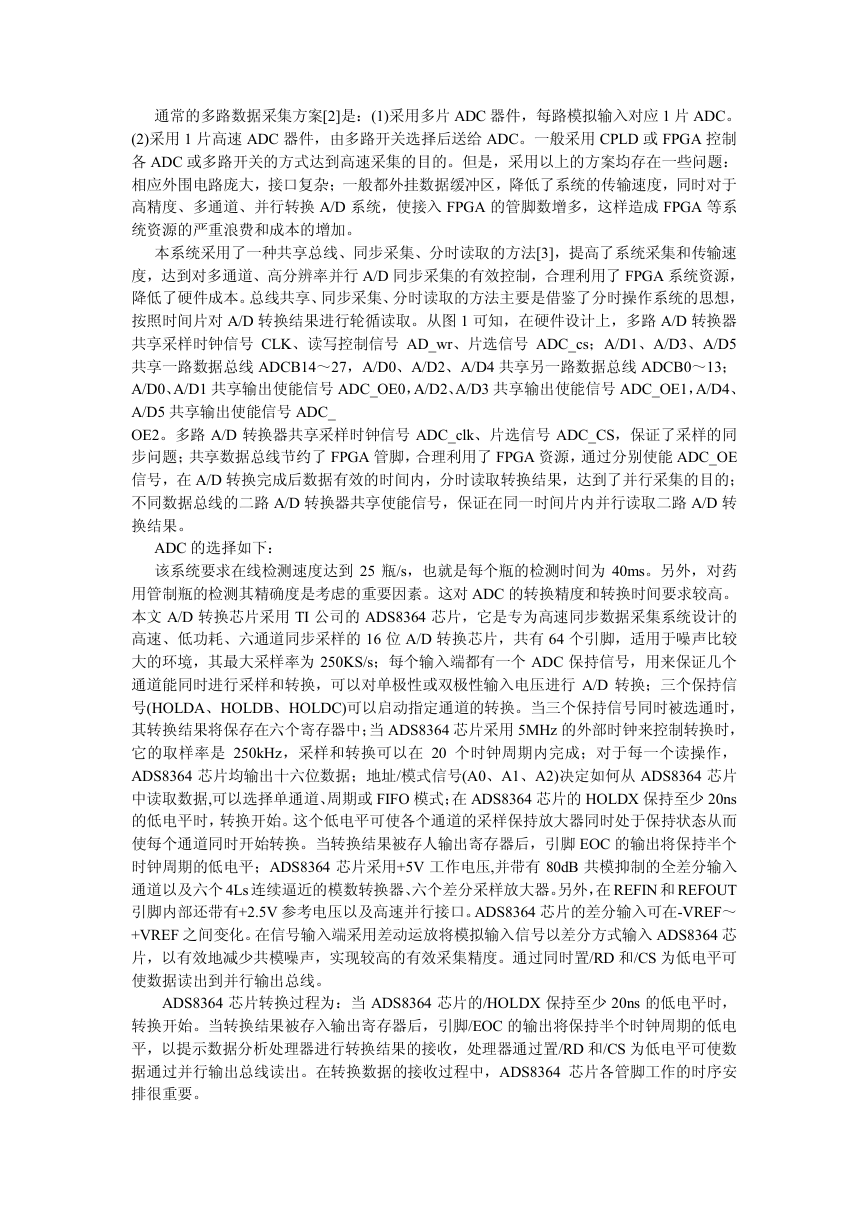

如图 5 所示,高速 DSP 将根据预处理信息得到的激光标志线、轮廓线和中心颜色线数据与源

数字化图像结合起来进行三维重建。首先根据获取的图像标志点数据结合控制点三维坐标数

据计算出系统定标数据;其次根据轮廓线计算物体外表面展开图,再依据定标数据结合展开

图和机械参数对图像中的坐标点进行计算,给出数据集,输出深度数据文件;最后对多次扫

描的数据进行融合,将离散点构型成立体模型(或立体彩色模型),将模型生成 DXF、STL

等数据文件传入 PC 机,使用后端处理软件进行显示[3]。

3.3 算法实现

图像预处理算法设计使用 Verilog HDL 在 Xilinx 公司的 ISE8.1 集成编译环境下成功实现;

DSP 三维重建算法已使用 C 语言在 ADI 公司 Visual DSP++环境下成功实现。

FPGA 开发流程不再赘述。

①用 C 语言编程实现算法。②使用 Visual DSP++编译器将源程序编译成目标文件。

算法实现步骤如下:

③根据产生的目标文件,分析结果及源程序结构并优化源代码。

④应用 TigerSHARC 201 评估板进行运算时间评估。

⑤重复上述步骤直至达到系统实时性要求,最后下载到目标板。

整个系统联机运行稳定,满足设计要求,实时性好。

实时三维图像信息处理以其数据量大、速度要求高、处理过程复杂的特点使其难以使用集成

电路实现。本文研究的以目前最新高性能处理器的 FPGA+DSP 为核心架构的三维图像处理系

统精心设计了算法的硬件实现,充分利用了两种处理器的长处。实验表明,该系统有着良好

的性能,对实现基于网络的实时三维扫描应用,如三维传真、机械远程加工、快速成型和虚

拟现实,有着重要的意义,

3,采用 FPGA+DSP 结构的多通道高速数据采集与实时图像处理系统的设计

1 系统硬件结构设计方案

本文设计的多通道同步高速采集及处理系统结构如图 1 所示。该系统由采集、处理、显

示和系统控制四个模块组成。采集的多路模拟视频信号经 A/D 阵列转换后,输入到处理模块

中进行图像处理,处理结果经 D/A 转换后,显示在终端监视设备上。整个过程(包括采集模块、

处理模块、显示模块)都在系统控制模块协调下进行。

2 采集模块

�

通常的多路数据采集方案[2]是:(1)采用多片 ADC 器件,每路模拟输入对应 1 片 ADC。

(2)采用 1 片高速 ADC 器件,由多路开关选择后送给 ADC。一般采用 CPLD 或 FPGA 控制

各 ADC 或多路开关的方式达到高速采集的目的。但是,采用以上的方案均存在一些问题:

相应外围电路庞大,接口复杂;一般都外挂数据缓冲区,降低了系统的传输速度,同时对于

高精度、多通道、并行转换 A/D 系统,使接入 FPGA 的管脚数增多,这样造成 FPGA 等系

统资源的严重浪费和成本的增加。

本系统采用了一种共享总线、同步采集、分时读取的方法[3],提高了系统采集和传输速

度,达到对多通道、高分辨率并行 A/D 同步采集的有效控制,合理利用了 FPGA 系统资源,

降低了硬件成本。总线共享、同步采集、分时读取的方法主要是借鉴了分时操作系统的思想,

按照时间片对 A/D 转换结果进行轮循读取。从图 1 可知,在硬件设计上,多路 A/D 转换器

共享采样时钟信号 CLK、读写控制信号 AD_wr、片选信号 ADC_cs;A/D1、A/D3、A/D5

共享一路数据总线 ADCB14~27,A/D0、A/D2、A/D4 共享另一路数据总线 ADCB0~13;

A/D0、A/D1 共享输出使能信号 ADC_OE0,A/D2、A/D3 共享输出使能信号 ADC_OE1,A/D4、

A/D5 共享输出使能信号 ADC_

OE2。多路 A/D 转换器共享采样时钟信号 ADC_clk、片选信号 ADC_CS,保证了采样的同

步问题;共享数据总线节约了 FPGA 管脚,合理利用了 FPGA 资源,通过分别使能 ADC_OE

信号,在 A/D 转换完成后数据有效的时间内,分时读取转换结果,达到了并行采集的目的;

不同数据总线的二路 A/D 转换器共享使能信号,保证在同一时间片内并行读取二路 A/D 转

换结果。

ADC 的选择如下:

该系统要求在线检测速度达到 25 瓶/s,也就是每个瓶的检测时间为 40ms。另外,对药

用管制瓶的检测其精确度是考虑的重要因素。这对 ADC 的转换精度和转换时间要求较高。

本文 A/D 转换芯片采用 TI 公司的 ADS8364 芯片,它是专为高速同步数据采集系统设计的

高速、低功耗、六通道同步采样的 16 位 A/D 转换芯片,共有 64 个引脚,适用于噪声比较

大的环境,其最大采样率为 250KS/s;每个输入端都有一个 ADC 保持信号,用来保证几个

通道能同时进行采样和转换,可以对单极性或双极性输入电压进行 A/D 转换;三个保持信

号(HOLDA、HOLDB、HOLDC)可以启动指定通道的转换。当三个保持信号同时被选通时,

其转换结果将保存在六个寄存器中;当 ADS8364 芯片采用 5MHz 的外部时钟来控制转换时,

它的取样率是 250kHz,采样和转换可以在 20 个时钟周期内完成;对于每一个读操作,

ADS8364 芯片均输出十六位数据;地址/模式信号(A0、A1、A2)决定如何从 ADS8364 芯片

中读取数据,可以选择单通道、周期或 FIFO 模式;在 ADS8364 芯片的 HOLDX 保持至少 20ns

的低电平时,转换开始。这个低电平可使各个通道的采样保持放大器同时处于保持状态从而

使每个通道同时开始转换。当转换结果被存人输出寄存器后,引脚 EOC 的输出将保持半个

时钟周期的低电平;ADS8364 芯片采用+5V 工作电压,并带有 80dB 共模抑制的全差分输入

通道以及六个 4Ls 连续逼近的模数转换器、六个差分采样放大器。另外,在 REFIN 和 REFOUT

引脚内部还带有+2.5V 参考电压以及高速并行接口。ADS8364 芯片的差分输入可在-VREF~

+VREF 之间变化。在信号输入端采用差动运放将模拟输入信号以差分方式输入 ADS8364 芯

片,以有效地减少共模噪声,实现较高的有效采集精度。通过同时置/RD 和/CS 为低电平可

使数据读出到并行输出总线。

ADS8364 芯片转换过程为:当 ADS8364 芯片的/HOLDX 保持至少 20ns 的低电平时,

转换开始。当转换结果被存入输出寄存器后,引脚/EOC 的输出将保持半个时钟周期的低电

平,以提示数据分析处理器进行转换结果的接收,处理器通过置/RD 和/CS 为低电平可使数

据通过并行输出总线读出。在转换数据的接收过程中,ADS8364 芯片各管脚工作的时序安

排很重要。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc