2016 年浙江温州大学电子技术考研真题

一、填空题(每格 1 分,共 20 分)

1、二极管具有

的特性;晶体三极管具有

的能力。

2、晶 体三极管 工作在放 大区的 基本外部 条件是: 发射结电 压

,集 电结电

压

。

3、一个理想的集成运算放大器,开环放大倍数为

,输入电阻为

,输出

电阻为

,共模抑制比为

。

4、逻辑代数中最基本的运算包括

、

和

。

5、把数字量转换为模拟量的装置称为

;把模拟量转换成数字量的装置称

为

。

6、8421BCD 译码器有

个信号输入端,有

个信号输出端。

7、能累计输入脉冲数目的逻辑部件称为

,根据触发方式(所有触发器是否都用同

一个时钟脉冲触发),分为

和

。

8、把交流电变成直流电,一般需要经过变压、

、

和稳压四个环节。

二、选择题(每题 2 分,共 20 分)

1、硅二极管导通电压约为(

)。

(A)

0.2V

(B)

0.3V

(C)

0.5V

(D)

0.7V

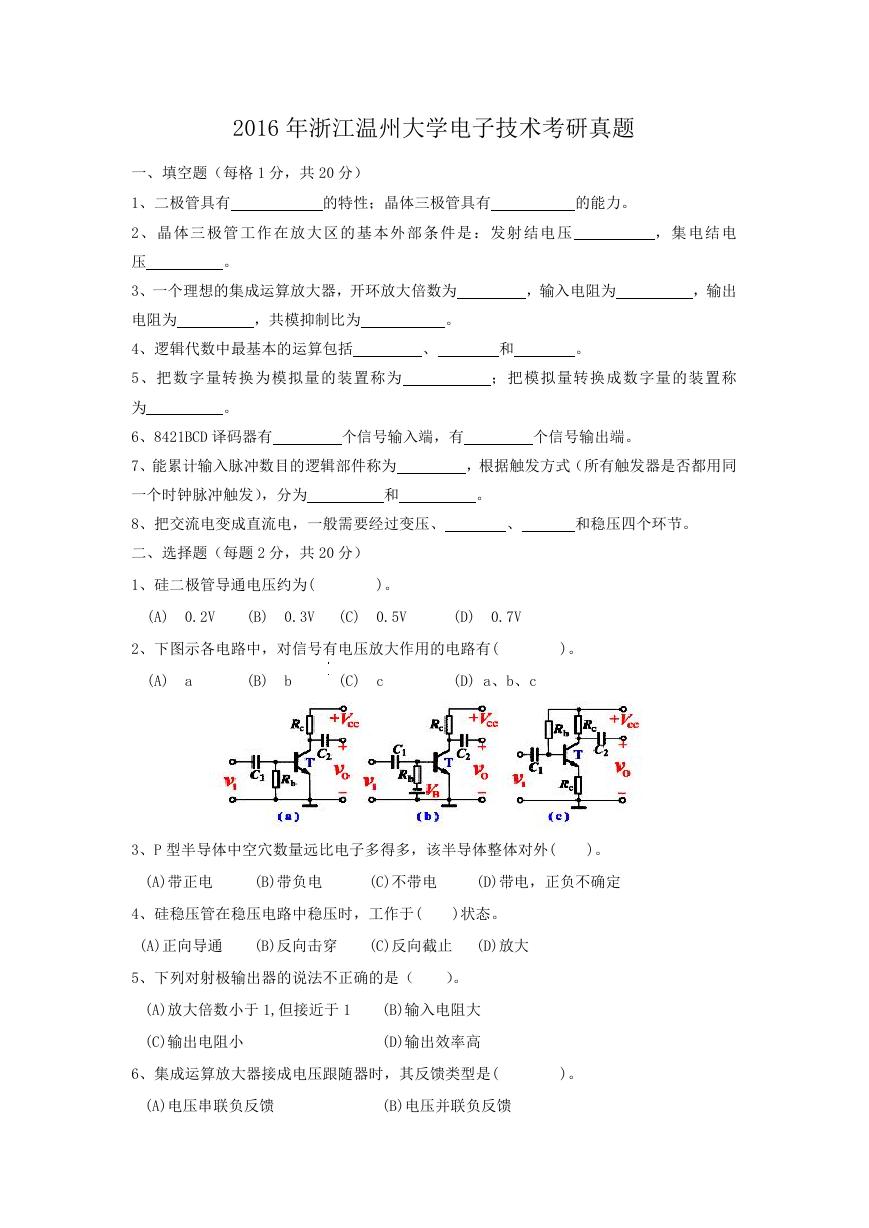

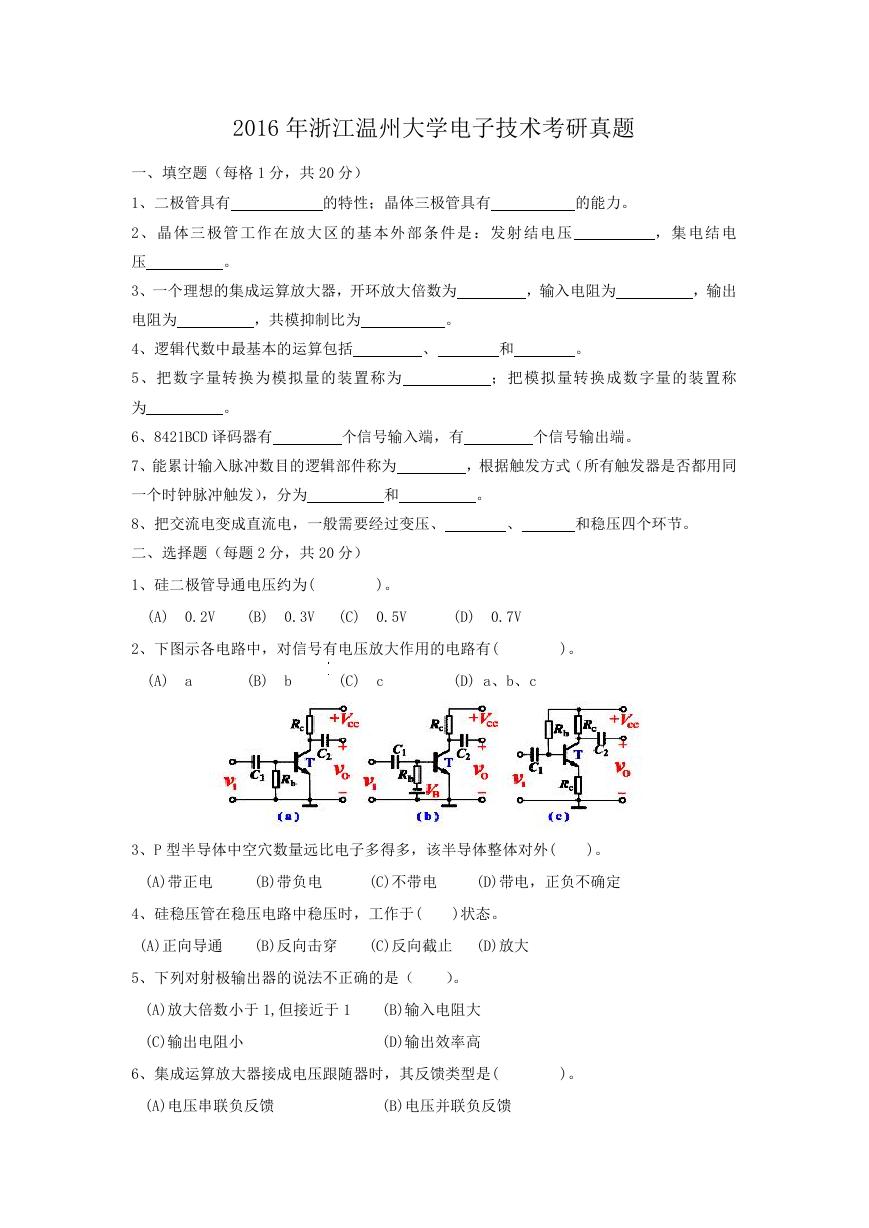

2、下图示各电路中,对信号有电压放大作用的电路有(

)。

(A)

a

(B)

b

(C)

c

(D) a、b、c

3、P 型半导体中空穴数量远比电子多得多,该半导体整体对外(

)。

(A)带正电

(B)带负电

(C)不带电

(D)带电,正负不确定

4、硅稳压管在稳压电路中稳压时,工作于(

)状态。

(A)正向导通

(B)反向击穿

(C)反向截止 (D)放大

5、下列对射极输出器的说法不正确的是(

)。

(A)放大倍数小于 1,但接近于 1

(B)输入电阻大

(C)输出电阻小

(D)输出效率高

6、集成运算放大器接成电压跟随器时,其反馈类型是(

)。

(A)电压串联负反馈

(B)电压并联负反馈

�

(C)电流串联负反馈

(D)电流并联负反馈

7、JK 触发器,当 J=1,K=1 时,具有(

)的功能。

(A)保持

(B)置 1

(C)清零

(D)翻转计数

8、在 8421 码编码中,规定二进制码 1000 代表的十进制数为(

)。

(A)9

(B)8

(C)7

(D)

6

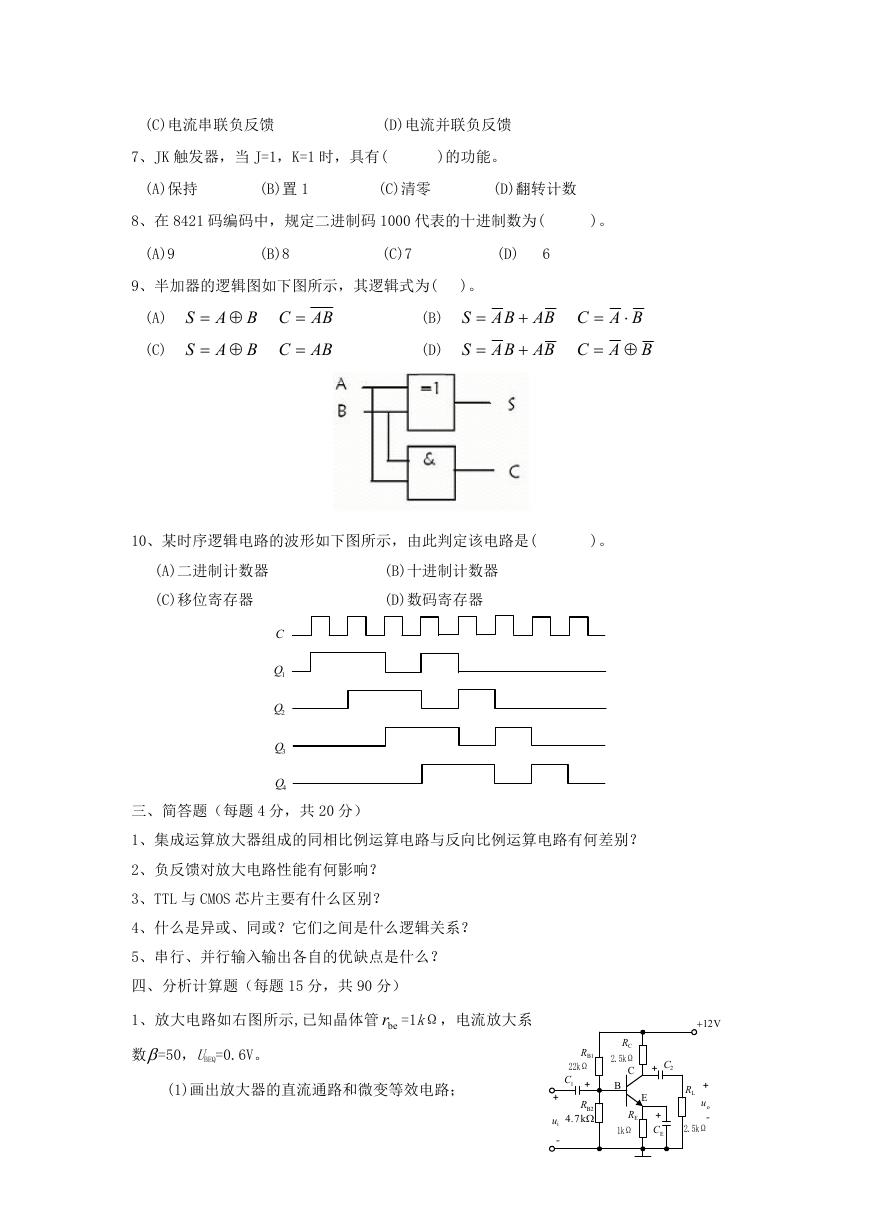

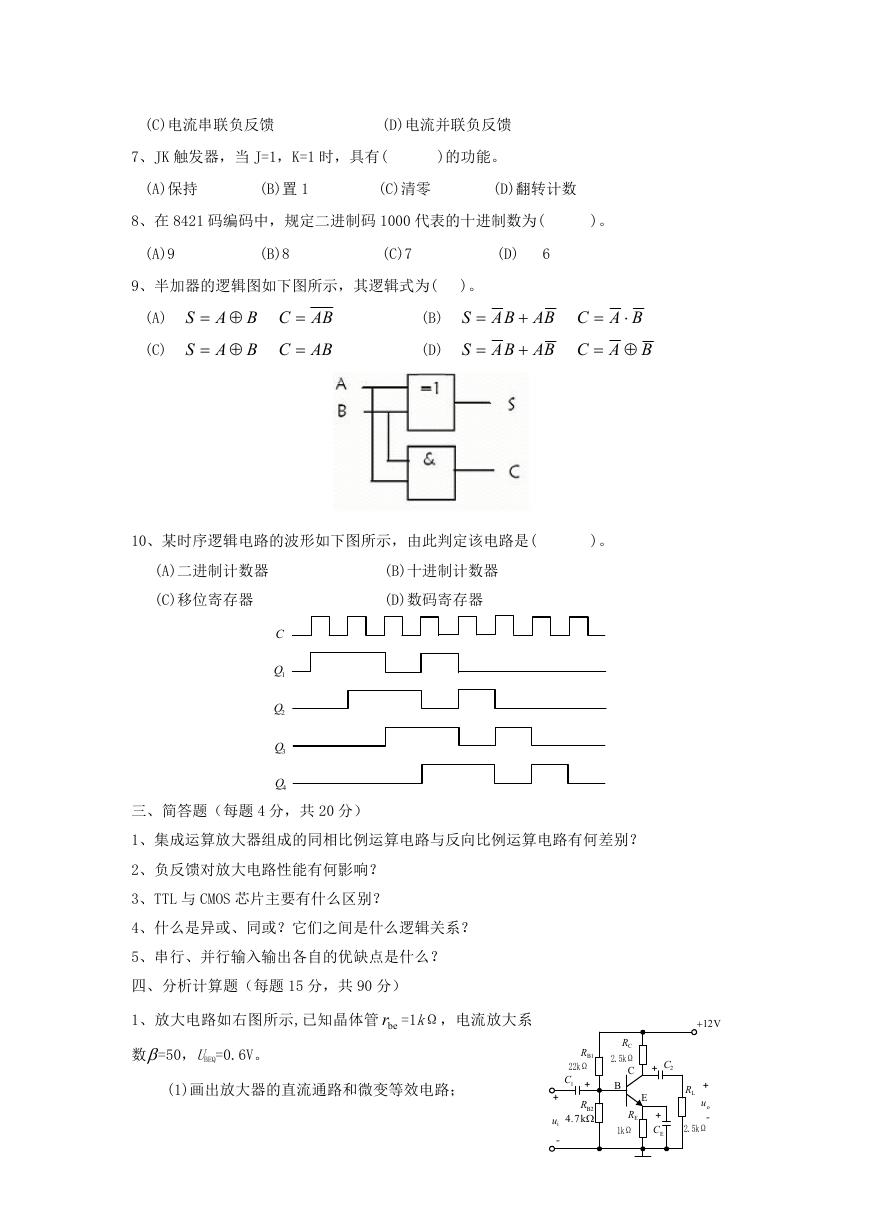

9、半加器的逻辑图如下图所示,其逻辑式为(

)。

(A)

(C)

S

S

BA

BA

C

C

AB

AB

(B)

(D)

BABAS

BABAS

BAC

AC

B

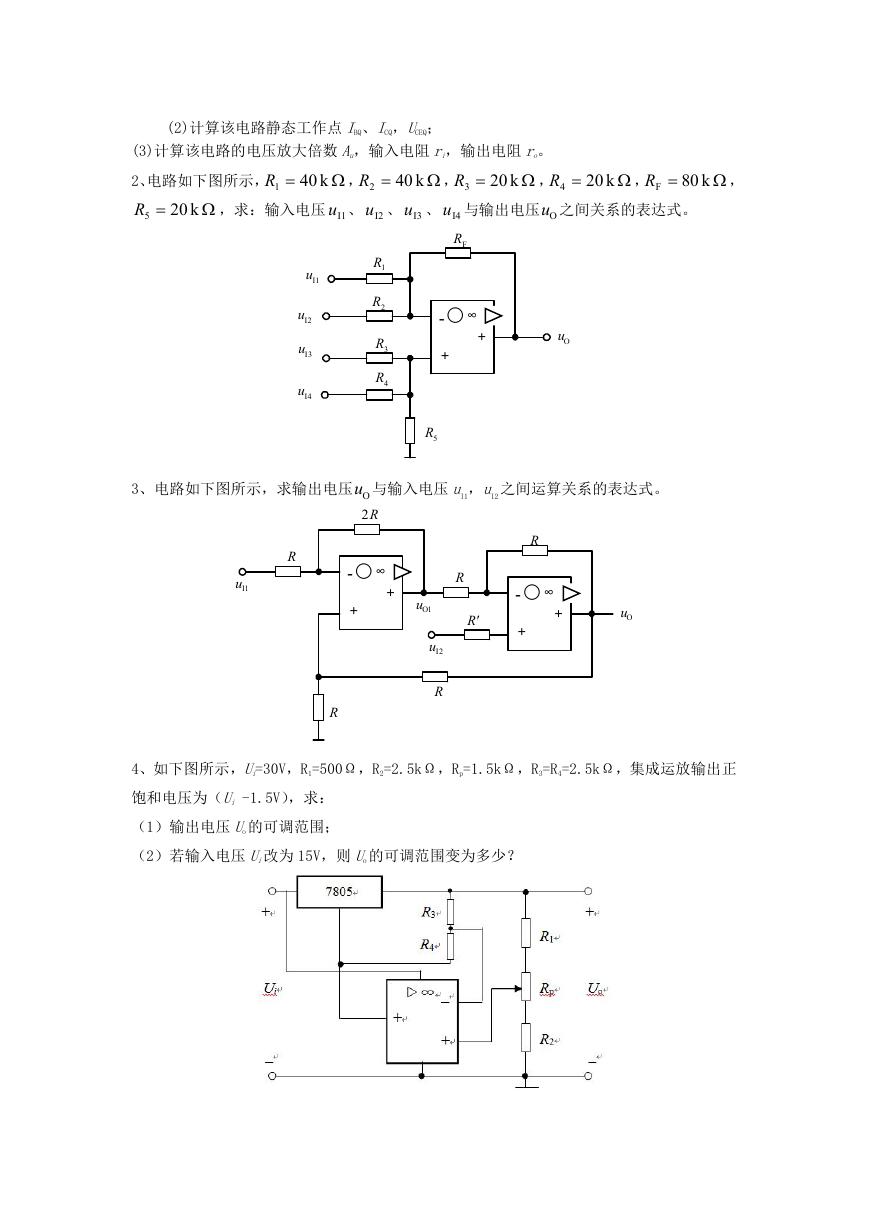

10、某时序逻辑电路的波形如下图所示,由此判定该电路是(

)。

(A)二进制计数器

(B)十进制计数器

(C)移位寄存器

(D)数码寄存器

C

Q1

Q2

Q3

Q4

三、简答题(每题 4 分,共 20 分)

1、集成运算放大器组成的同相比例运算电路与反向比例运算电路有何差别?

2、负反馈对放大电路性能有何影响?

3、TTL 与 CMOS 芯片主要有什么区别?

4、什么是异或、同或?它们之间是什么逻辑关系?

5、串行、并行输入输出各自的优缺点是什么?

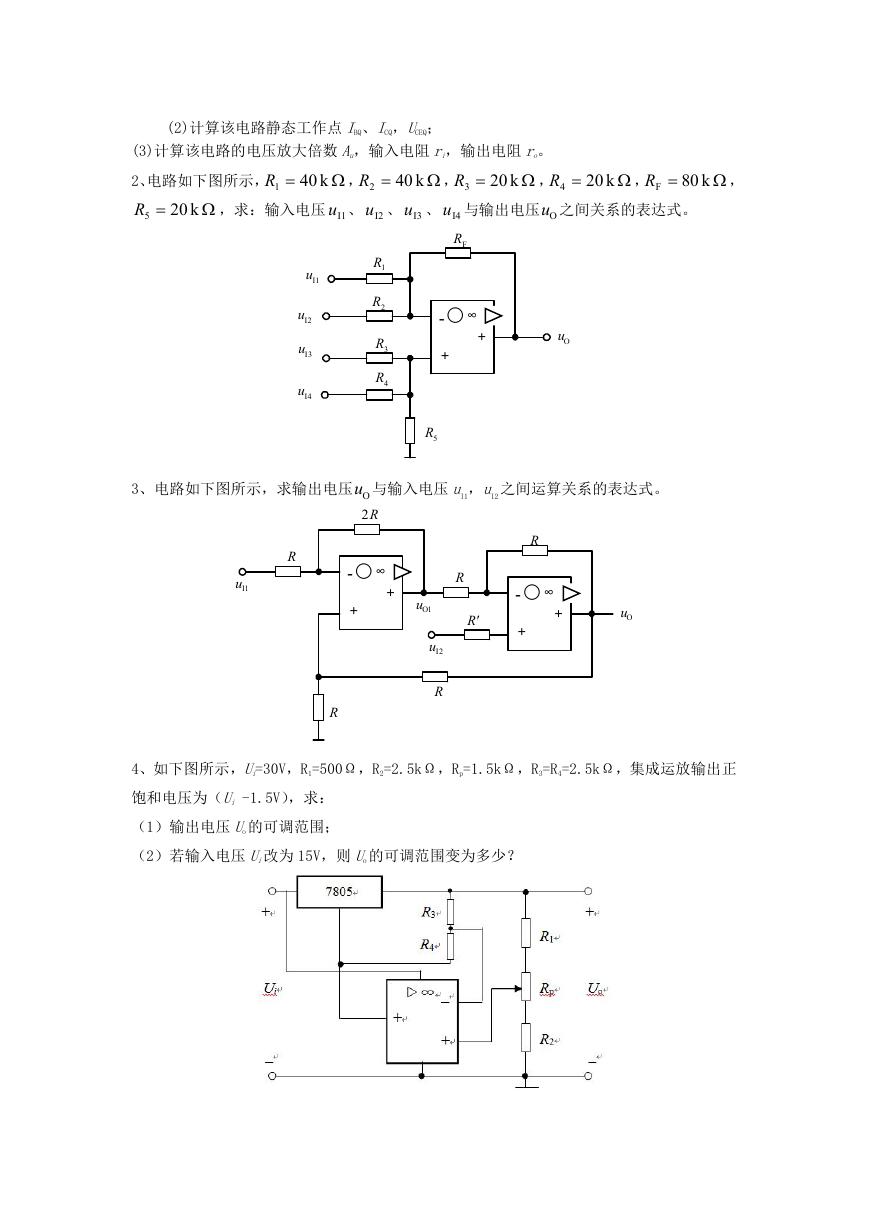

四、分析计算题(每题 15 分,共 90 分)

1、放大电路如右图所示,已知晶体管 ber =1kΩ,电流放大系

数=50,UBEQ=0.6V。

(1)画出放大器的直流通路和微变等效电路;

RC

2.5kΩ

C

B

C2

+

E

RE

1kΩ

+

CE

12V

RL

+

uo

-

2.5kΩ

RB1

22kΩ

C1 +

RB2

4 7. k

+

ui

-

�

(2)计算该电路静态工作点 IBQ、ICQ,UCEQ;

(3)计算该电路的电压放大倍数 Au,输入电阻 ri,输出电阻 ro。

1R

2、电路如下图所示,

5R

k20

k40

2R

,

k40

3R

,

k20

4R

,

k20

FR

,

k80

,

,求:输入电压 I1u 、 I2u 、 I3u 、 I4u 与输出电压uO 之间关系的表达式。

R1

R2

R3

R4

uI1

uI2

uI3

uI4

RF

∞

+

-

+

R5

uO

3、电路如下图所示,求输出电压uO 与输入电压 u

I1

,u

I2

R

uI1

2R

∞

+

-

+

R

R

R

uO1

uI2

R

之间运算关系的表达式。

R

∞

+

-

+

uO

4、如下图所示,Ui=30V,R1=500Ω,R2=2.5kΩ,Rp=1.5kΩ,R3=R4=2.5kΩ,集成运放输出正

饱和电压为(Ui -1.5V),求:

(1)输出电压 Uo 的可调范围;

(2)若输入电压 Ui改为 15V,则 Uo 的可调范围变为多少?

�

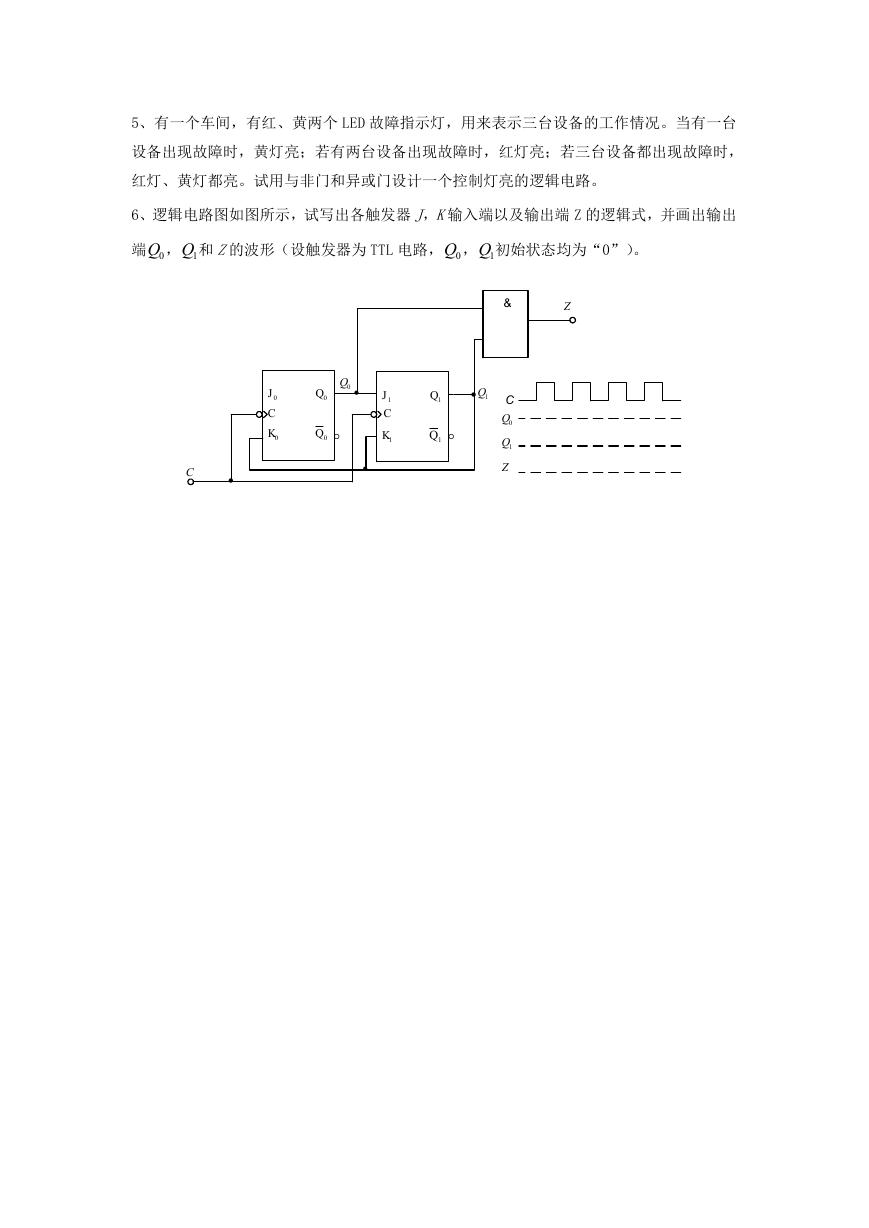

5、有一个车间,有红、黄两个 LED 故障指示灯,用来表示三台设备的工作情况。当有一台

设备出现故障时,黄灯亮;若有两台设备出现故障时,红灯亮;若三台设备都出现故障时,

红灯、黄灯都亮。试用与非门和异或门设计一个控制灯亮的逻辑电路。

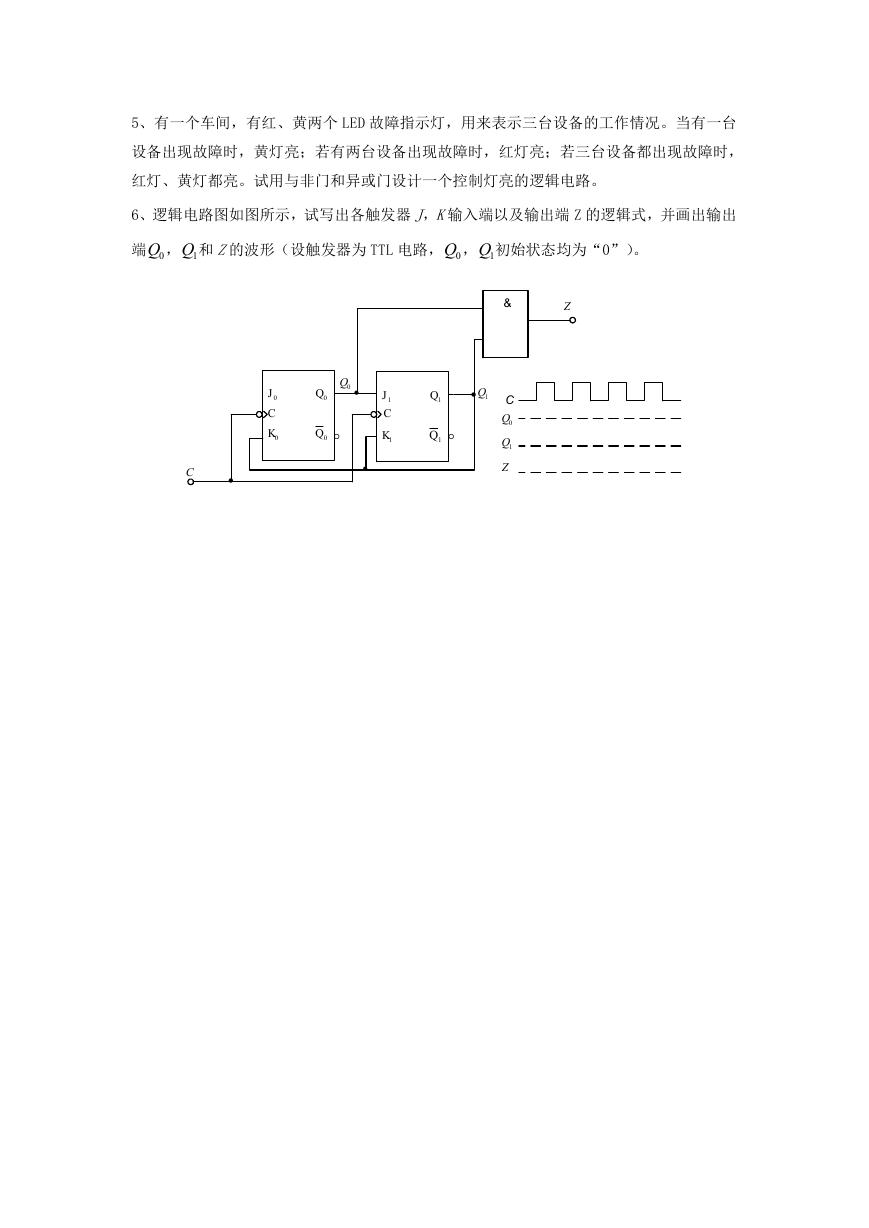

6、逻辑电路图如图所示,试写出各触发器 J,K输入端以及输出端 Z 的逻辑式,并画出输出

端Q0,Q1和 Z的波形(设触发器为 TTL 电路,Q0,Q1初始状态均为“0”)。

&

Z

J 0

C

K0

Q0

Q0

Q0

o

J 1

C

K1

Q1

Q1

Q1

o

C

Q0

Q1

Z

C

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc