The

8086Family

Users Manual

October1979

© Intel Corporation 1978, 1979

9800722-03/ $7.50

�

The

8086 Family

Users Manual

October 1979

�

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department

Intel Corporation

3065 Bowers Avenue

Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited

to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation

assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no

commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in

an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use,

duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR

7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

ICE

iCS

Imile

Intel

Intelevision

Imellee

iSBC

Library Manager

MCS

Megachassis

Micromap

Multibus

Multimodule

PROMPT

Promware

RMX

UPI

I-IScope

and the combination of ICE, iCS, iSBC, MCS, or RMX and a numerical suffix.

ii

�

Table of Contents

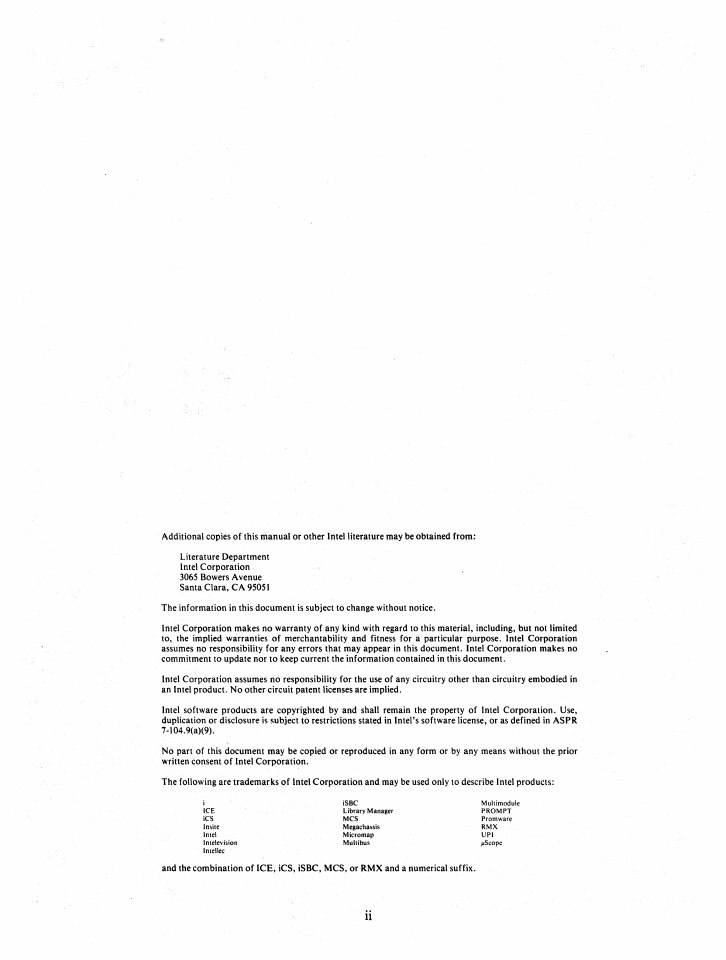

CHAPTERl

INTRODUCTION

PAGE

Manual Organization ...................... "

I-I

8086 Family Architecture. . . . . . . . . . . . . . . . . . . .. I-I

Functional Distribution. . . .. . . .. .. . . .. . . . . . .. I-I

Microprocessors. . . . . . . . . . . . . . . . . . . . . . . . .. 1-2

Interrupt Controller ....................... 1-3

Bus Interface Components. . .. . . . . . .. . . .. .. 1-3

Multiprocessing.. . . . . . . . . . . . . . . .. . ... . .. . .. 1-3

Bus Organization. . . . . . . . . . . . . . . . . . . . . . . . . .. 1-4

Local Bus ............................... 1-4

System Bus ............ , ....... " ...... " 1-5

. Processing Modules. . . . . . . . . . . . . . . . . . . . . .. 1-6

Bus Implementation Examples. . . . . . . . . . . . .. 1-6

Development Aids. . . . . . . . . . . . .. . . . .. . .. . ... 1-12

CHAPTER 2

THE 8086 AND 8088 CENTRAL

PROCESSING UNITS

Processor Overview. . . . . . . . . . . . . . . . . . . . . . . . .. 2-1

Processor Architecture. . . . . . . . . . . . . . . . . . . . . .. 2-3

Execution Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-5

Bus Interface Unit. . . . . . . . . . . . . . . . . . . . . . . . .. 2-5

General Registers. . . . . . . . . . . . . . . .. . . . . . . . . .. 2-6

Segment Registers ........................ " 2-7

Instruction Pointer ......................... 2-7

Flags ..................................... 2-7

8080/8085 Register and Flag Correspondence. .. 2-8

Mode Selection ........ , ......... '" ........ 2-8

Memory ............................. ; .... " 2-8

Storage Organization ........................ 2-8

Segmentation . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-10

Physical Address Generation. . . . . . . . . . . . . . .. 2-11

DynamicallyRelocatable Code .............. 2-13

Stack Implementation ...................... 2-14

Dedicated and Reserved Memory Locations .... 2-14

8086/8088 Memory Access Differences ........ 2-15

Input/Output .............................. 2-15

Input/Output Space ....................... 2-16

Restricted 110 Locations ................... 2-16

8086/8088 Memory Access Differences .. , ..... 2-16

Memory-Mapped I/O ...................... 2-16

Direct Memory Access. . . . . . . . . . . . . . . . . . . . .. 2-17

8089 Input/Output Processor (lOP) . . . . . . . . .. 2-17

Multiprocessing Features. . . . . . . . . . . . . . . . . . .. 2-17

Bus Lock ................................. 2-17

WAIT and TEST . . . . . . . . . . • . . . . . . . . . . . . . .. 2-18

Escape .................................... 2-19

Request/Grant Lines. . . . • . . . . . . . . . . . . . . . . .. 2-20

. Multibus™ Architecture .................... 2-21

PAGE

8289 Bus Arbiter .......................... 2-22

Processor Control and Monitoring . . . . . . . . . .. 2-22

Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-22

External Interrupts .... . . . . . . . . . . . . . . . . .. 2-22

Internal Interrupts. . . . . . . . . . . . . . . . . . . . . .. 2-24

Interrupt Pointer Table. . . . . . . . . . . . . . . . . .. 2-25

Interrupt Procedures. . . . . . . . . . . . . . . . . . . .. 2-26

Single-Step (Trap) Interrupt. . . . . . . . . . . . . .. 2-28

Breakpoint Interrupt. . . . . . . . . . . . . . . . . . . .. 2-28

System Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-29

Instruction Queue Status. . . . . . . . . . . . . . . . . . .. 2-29

Processor Halt. . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-29

Status Lines ............................ " 2-30

Instruction Set ............................. 2-30

Data Transfer Instructions. . . . . . . . . . . . . . . . .. 2-31

General Purpose Data Transfers ......... " 2-31

Address Object Transfers. . . . . . . . . . . . . . . .. 2-32

Flag Transfers ................... . . . . . .. 2-32·

Arithmetic Instructions. . . . . . . . . . . . . . . . . . . .. 2-33

Arithmetic Data Formats. . . . . . . . . . . . . . . .. 2-33

Arithmetic Instructions and Flags . . . . . . . . .. 2-34

Addition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-35

Subtraction. . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-36

Multiplication. . . . . . . . . . . . . . . . . . . . . . . . . .. 2-36

Division .......................... '" . " 2-37

Bit Manipulation Instructions . . . . . . . . . . . . . .. 2-38

Logical ......................... . . . . . .. 2-38

Shifts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-39

Rotates .............................. " 2-39

String Instructions. . . . . . . . . . . . . . . . . . . . . . . .. 2-40

Program Transfer Instructions. . . . . . . . . . . . . .. 2-43

Unconditional Transfers. . . . . . . . . . . . . . . . .. 2-43

Conditional Transfers. . . . . . . . . . . . . . . . . . .. 2-45

Iteration Control. . . . . . . . . . . . . . . . . . . . . . .. 2-45

Interrupt Instructions. . . . . . . . . . . . . . . . . . .. 2-46

Processor Control Instructions .............. 2-47

Flag Operations ......................... 2-47

External Synchronization. . . . . . . . . . . . . . . .. 2-48

No Operation. . . . . . . . . . . . . . . . . . . . . . . . . .. 2-48

Instruction Set Reference Information. . . . . . .. 2-48

Addressing Modes. . . . . . . . . . . . . . . . . . . . . . . . .. 2-68

Register and Immediate Operands. . . . . . . . . . .. 2-68

Memory Addressing Modes ............... " 2-68

The Effective Address. . . . . . . . . . . . . . . . . . .. 2-68

Direct Addressing ....................... 2-69

Register Indirect Addressing ............. " 2-69

Based Addressing. . . . . . . . . . . . . . . . . . . . . . .. 2-70

Indexed Addressing. . . . . . . . . . . . . . . . . . . . .. 2-70

iii

�

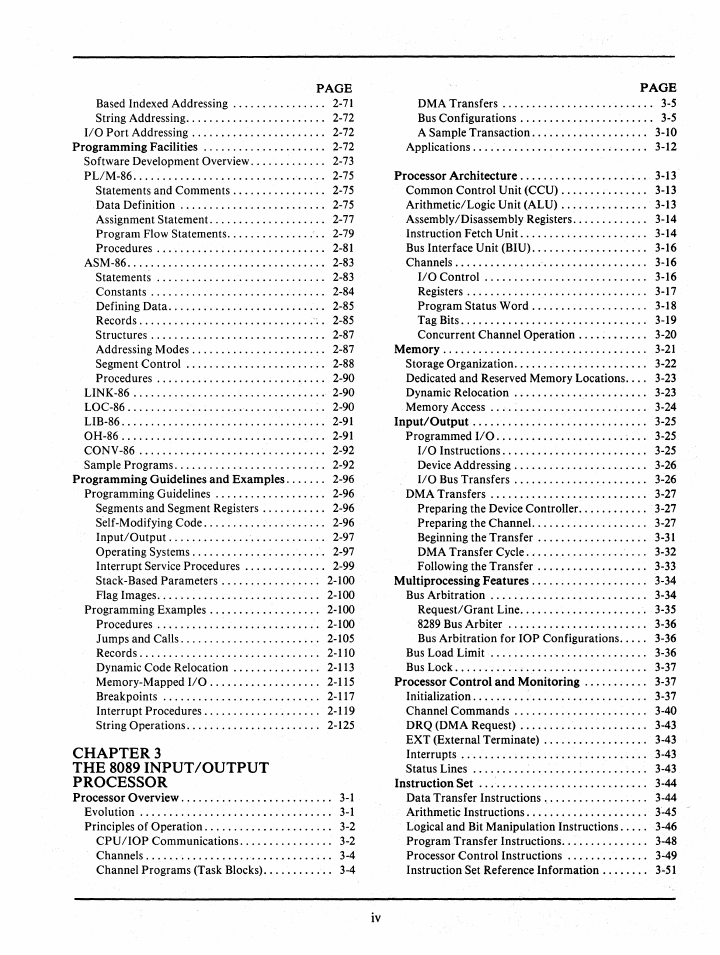

PAGE

Based Indexed Addressing ................ 2-71

String Addressing. . . . . . . . . . . . . . . . . . . . . . .. 2-72

110 Port Addressing ....................... 2-72

Programming Facilities ..................... 2-72

Software Development Overview ............. 2-73

PL/M-86 ................................. 2-75

Statements and Comments ................ 2-75

Data Definition ....................... " 2-75

Assignment Statement. . . . . . . . . . . . . . . . . . .. 2-77

Program Flow Statements ................. 2-79

Procedures. . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-81

ASM-86 .................................. 2-83

Statements ............................. 2-83

Constants . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-84

Defining Data ........................... 2-85

Records ............................... ;. 2-85

Structures .............................. 2-87

Addressing Modes ..................... ,. 2-87

Segment Control .... . . . . . . . . . . . . . . . . . . .. 2-88

Procedures. . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-90

LINK-86 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-90

LOC-86 . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . .. 2-90

LIB-86. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-91

OH-86 ................................... 2-91

CONV-86 ................................ 2-92

Sample Programs ........................ " 2-92

Programming Guidelines and Examples. . . . . .. 2-96

Programming Guidelines ..... . . . . . . . . . . . . .. 2-96

Segments and Segment Registers . . . . . . . . . .. 2-96

Self-Modifying Code ................... " 2-96

Input/Output. . . . . . . . . . . . . . . . . . . . . . . . . .. 2-97

Operating Systems. . . . . . . . . . . . . . . . . . . . . .. 2-97

Interrupt Service Procedures ... . . . . . . . . . .. 2-99

Stack-Based Parameters ................. 2-100

Flag Images ............................ 2-100

Programming Examples ................... 2-100

Procedures ............................ 2-100

Jumps and Calls ........................ 2-105

Records .............................. , 2-110

Dynamic Code Relocation ............... 2-113

Memory-Mapped 110 ................... 2-115

Breakpoints ........................... 2-117

Interrupt Procedures .................... 2-119

String Operations ....................... 2-125

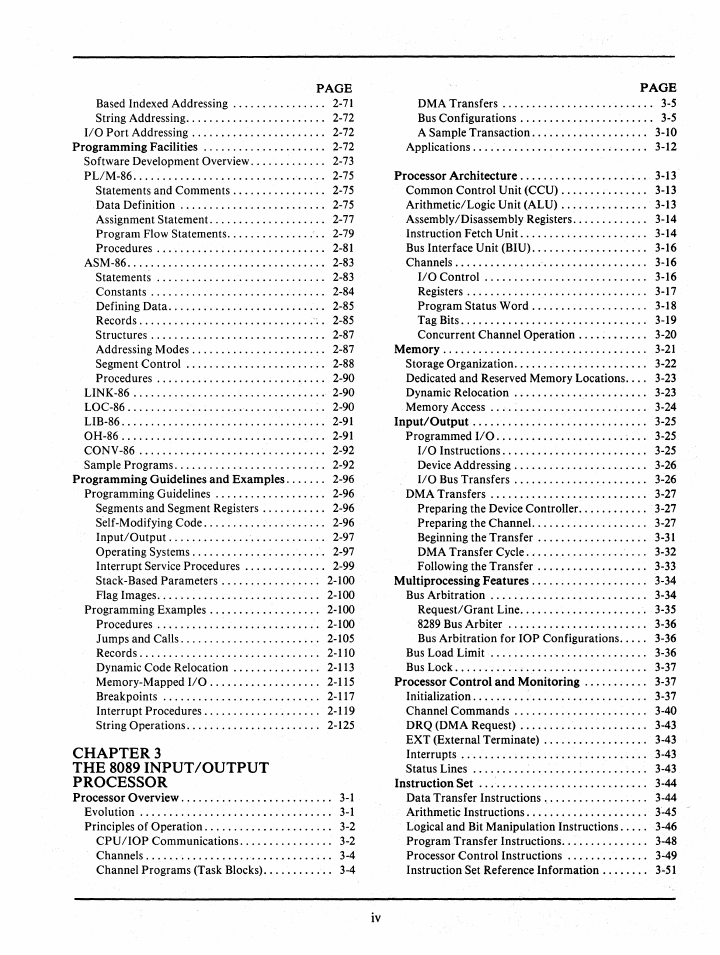

CHAPTER 3

THE 8089 INPUT/OUTPUT

PROCESSOR

Processor Overview ..... , .................... 3-1

Evolution .... . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-1

Principles of Operation ..................... , 3-2

CPU/lOP Communications ................ 3-2

Channels ..................... , .......... 3-4

Channel Programs (Task Blocks) ............ 3-4

PAGE

DMA Transfers. . . . . . . . . . . . . . . . . . . . . . . . .. 3-5

Bus Configurations. . . . . . . . . . . . . . . . . . . . . .. 3-5

A Sample Transaction. . . . . . . . . . . . . . . . . . .. 3-10

Applications ....................... , ...... 3-12

Processor Architecture ...................... 3-13

Common Control Unit (CCU) ............... 3-13

Arithmetic/Logic Unit (ALU) . .. . . . . . . . . . . .. 3-13

Assembly/Disassembly Registers ............ , 3-14

Instruction Fetch Unit ...................... 3-14

Bus Interface Unit (BIU) .................... 3-16

Channels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-16

110 Control ............................ 3-16

Registers .............................. , 3-17

Program Status Word .................... 3-18

Tag Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-19

Concurrent Channel Operation. . . . . . . . . . .. 3-20

Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-21

Storage Organization. . . . . . . . . . . . . . . . . . . . . .. 3-22

Dedicated and Reserved Memory Locations. . .. 3-23

Dynamic Relocation ....................... 3-23

Memory Access .. . . . . . . . . . . . . . . . . . . . . . . . .. 3-24

Input/Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-25

Programmed 110 ...................... ; .. , 3-25

110 Instructions. . . . . . . . . . . . . . . . . . . . . . . .. 3-25

Device Addressing ...................... , 3-26

110 Bus Transfers. . . . . . . . . . . . . . . . . . . . . .. 3-26

DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-27

Preparing the Device Controller. . . . . . . . . . .. 3-27

Preparing the Channel. . . . . . . . . . . . . . . . . . .. 3-27

Beginning the Transfer . . . . . . . . . . . . . . . . . .. 3-31

DMA Transfer Cycle. . . . . . . . . . . . . . . . . . . .. 3-32

Following the Transfer. . . . . . . . . . . . . . . . . .. 3-33

Multiprocessing Features. . . . . . . . . . . . . . . . . . .. 3-34

Bus Arbitration .......................... , 3-34

Request/Grant Line ..................... , 3-35

8289 Bus Arbiter ........................ 3-36

Bus Arbitration for lOP Configurations .... , 3-36

Bus Load Limit ... . . . . . . . . . . . . . . . . . . . . . . .. 3-36

Bus Lock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-37

Processor Control and Monitoring .......... , 3-37

Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-37

Channel Commands ...................... , 3-40

DRQ (DMA Request) . . . . . . . . . . .. . . . . . . .. .. 3-43

EXT (External Terminate) .. . . . . . . . . . . . . . . .. 3-43

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-43

Status Lines .............................. 3-43

Instruction Set " . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-44

Data Transfer Instructions. . . . . . . . . . . . . . . . .. 3-44

Arithmetic Instructions. . . . . . . . . . . . . . . . . . . .. 3-45

Logical and Bit Manipulatioll Instructions. . . .. 3-46

Program Transfer Instructions. . . . . . . . . . . . . .. 3-48

Processor Control Instructions .............. 3-49

Instruction Set Reference Information. . . . . . .. 3-51

iv

�

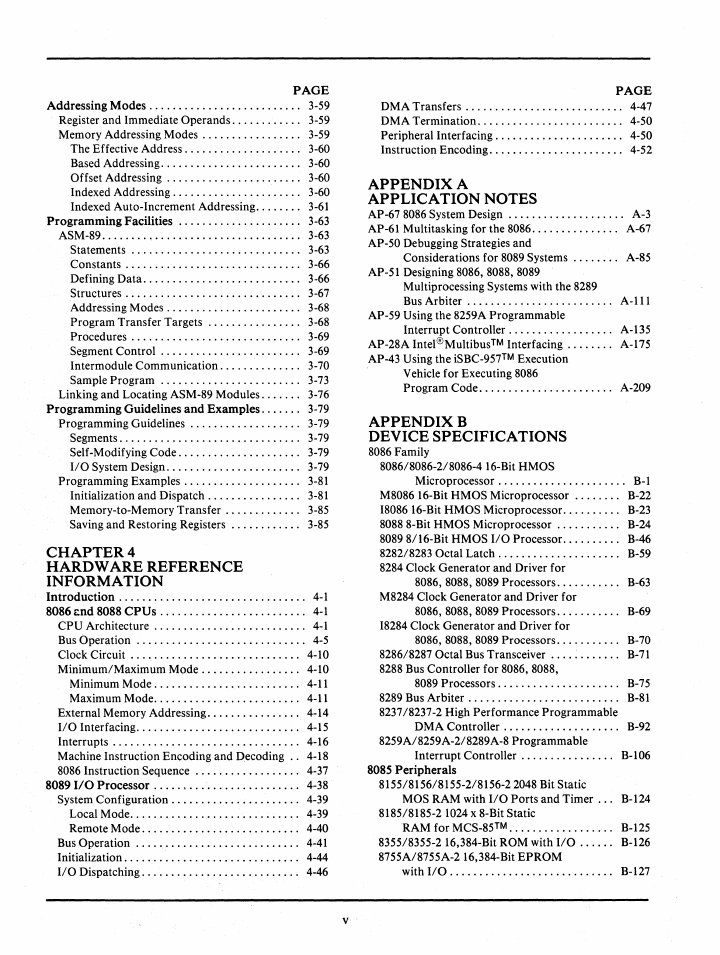

PAGE

Addressing Modes. . . . . . . . . . . . . . . . . . . . . . . . .. 3-59

Register and Immediate Operands. . . . . . . . . . .. 3-59

Memory Addressing Modes. . . . . . . . . . . . . . . .. 3-59

The Effective Address. . . . . . . . . . . . . . . . . . .. 3-60

Based Addressing ........................ 3-60

Offset Addressing. . . . . . . . . . . . . . . . . . . . . .. 3-60

Indexed Addressing. . . . . . . . . . . . . . . . . . . . .. 3 -60

Indexed Auto-Increment Addressing ........ 3-61

Programming Facilities ..................... 3-63

ASM-89. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-63

Statements ...... . . . . . . . . . . . . . . . . . . . . . .. 3-63

Constants . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-66

Defining Data .................... , ...... 3-66

Structures. . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-67

Addressing Modes. . . . . . . . . . . . . . . . . . . . . .. 3-68

Program Transfer Targets ................ 3-68

Procedures. . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-69

Segment Control .. . . . . . . . . . . . . . . . . . . . . .. 3-69

Intermodule Communication .............. 3-70

Sample Program ........................ 3-73

Linking and Locating ASM-89 Modules. . . . . .. 3-76

Programming Guidelines and Examples. . . . . .. 3-79

Programming Guidelines ........ . . . . . . . . . .. 3-79

Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-79

Self -Modifying Code. . . . . . . . . . . . . . . . . . . .. 3-79

110 System Design ....................... 3-79

Programming Examples .................... 3-81

Initialization and Dispatch. . . . . . . . . . . . . . .. 3-81

Memory-to-Memory Transfer. . . . . . . . . . . .. 3-85

Saving and Restoring Registers ............ 3-85

CHAPTER 4

HARDWARE REFERENCE

INFORM A TION

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 4-1

8086 cnd 8088 CPUs ......................... 4-1

CPU Architecture .......................... 4-1

Bus Operation ............................. 4-5

Clock Circuit ......................... , ... 4-10

Minimum/Maximum Mode ................. 4-10

Minimum Mode ........................ . 4-11

Maximum Mode ........................ . 4-11

External Memory Addressing ............... . 4-14

110 Interfacing ........................... . 4-15

Interrupts ............................... . 4-16

Machine Instruction Encoding and Decoding .. 4-18

8086 Instruction Sequence ................. . 4-37

8089 I/O Processor ..... , .................. . 4-38

System Configuration ..................... . 4-39

Local Mode ............................ . 4-39

Remote Mode .......................... . 4-40

Bus Operation ........................... . 4-41

Initialization ............................. . 4-44

I/O Dispatching .......................... . 4-46

PAGE

DMA Transfers. . . . . . . . . . . . . . . . . . . . . . . . . .. 4-47

DMA Termination ......................... 4-50

Peripheral Interfacing. . . . . . . . . . . . . . . . . . . . .. 4-50

Instruction Encoding. . . . . . . . . . . . . . . . . . . . . .. 4-52

APPENDIX A

APPLICATION NOTES

AP-67 8086 System Design .... . . . . . . . . . . . . . . .. A-3

AP-61 Multitasking for the 8086 ............... A-67

AP-50 Debugging Strategies and

Considerations for 8089 Systems ........ A-85

AP-51 Designing 8086,8088,8089

Multiprocessing Systems with the 8289

Bus Arbiter ......................... A-Ill

AP-59 Using the 8259A Programmable

Interrupt Controller .................. A-135

AP-28A Intel®Multibus TM Interfacing. . . . . . .. A-175

AP-43 Using the iSBC-957™ Execution

Vehicle for Executing 8086

Program Code ....................... A-209

APPENDIXB

DEVICE SPECIFICATIONS

8086 Family

8086/8086-2/8086-4 16-Bit HMOS

Microprocessor ...................... B-1

M8086 16-Bit HMOS Microprocessor ..... . .. B-22

18086 16-Bit HMOS Microprocessor ........ " B-23

8088 8-Bit HMOS Microprocessor. . . . . . . . . .. B-24

8089 8/16-Bit HMOS 110 Processor. ....... " B-46

8282/8283 Octal Latch. .. . . . . . . . . . . . . . . . . .. B-59

8284 Clock Generator and Driver for

8086, 8088, 8089 Processors. . . . . . . . . .. B-63

M8284 Clock Generator and Driver for

8086, 8088, 8089 Processors ......... " B-69

18284 Clock Generator and Driver for

8086,8088,8089 Processors ........... B-70

8286/8287 Octal Bus Transceiver ............ B-71

8288 Bus Controller for 8086, 8088,

8089 Processors. . . . . . . . . . . . . . . . . . . .. B-7 5

8289 Bus Arbiter ........................ " B-81

8237/8237-2 High Performance Programmable

DMA Controller. . . .. . . . . . . . . . . . . . .. B-92

8259A/8259A-2/8289A-8 Programmable

Interrupt Controller . . . . . . . . . . . . . . .. B- I 06

8085 Peripherals

8155/8156/8155-2/8156-22048 Bit Static

MOS RAM with 110 Ports and Timer ... B-124

8185/8185-2 1024 x 8-Bit Static

RAM for MCS-85™ .................. B-125

8355/8355-2 16,384-Bit ROM with 110 ...... B-126

8755A18755A-2 16,384-Bit EPROM

with I/O ............................ B-127

v

�

Standard Peripherals

PAGE

PAGE

21481024 x 4 Bit Static RAM .. " ........... B-145

8041A/8741A Universal Peripheral Interface

8-Bit Microcomputer ................. B-128

8202 Dynamic RAM Controller ............. B-129

8205 High Speed lOut of 8 Binary Decoder .. B-130

8251A Programmable Communication

Interface. . . . . . . . . . . . . . . . . . . . . . . . . . .. B-131

8253/8253-5 Programmable Interval Timer. .. B-132

8255A/8255A-5 Programmable Peripheral

Interface. . . . . . . . . . . . . . . . . . . . . . . . . . .. B-133

8271/8271-6/8271-8 Programmable Floppy

Disk Controller ...................... B-134

8273 Programmable HDLC/SDLC Protocol

Controller. . . . . . . . . . . . . . . . . . . . . . . . •.. B-135

8275 Programmable CRT Controller ........ B-136

8279/8279-5 Programmable Keyboard/Display

Interface .............. ' .............. B-137

8291 GPIB Talker/Listener .........•....... B-138

8292 GPIB Controller .............•....... B-139

8293 GPIB Transceiver. . . . . . . . . . . . . . . . . . .. B-140

8294 Data Encryption Unit ................ B-141

8295 Dot Matrix Printer Controller ......... B-142

RAM Memories

2114A 1024 x 4 Bit Static RAM. . . . . . . . . • . .. B-143

21421024 x 4 Bit Static RAM. . . . . . . . . . . . . .. 8-144

EPROM Memories

271616K (2K x 8) UV Erasable PROM ....... B-146

2732 32K (4K x 8) UV Erasable PROM ....... B-147

2758 8K (l K x 8) UV Erasable Low

Power PROM ....................... B-148

Development Tools

Model 230 Intellec® Series II

Microcomputer Development System .... B-149

8086/8088 Software

Development Package ....... . . . . . . . .. B-153

8089 Assembler Support Package. . . . . . . . . .. B-163

ICE-86™ 8086 In-Circuit Emulator; ........ B-165

iSBC 86/ 12A TM Single Board Computer .... , B-I71

iSBC 957™ Intellec®-iSBC 86/12ATM Interface

and Execution Package ................ B-179

iSBC 300/340™ iSBC 300™ 32K-Byte RAM

Expansion Module iSBC 340™ 16K-Byte

EPROM/ROM Expansion Module ..... B-184

SDK-86 MCS-86™ Sys.tem Design Kit ....... B-188

SDK-C86 MCS-86™ System Design Kit.: ... 8-194

'vi

�

Chapter 1

Introduction

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc