ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

AR0130 Registers, Rev. D

For more information, please visit www.aptina.com

AR0130 Register Reference

AR0130 Registers Rev. D Pub. 11/14 EN

1

©Semiconductor Components Industries, LLC,2011

�

ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

Table of Contents

Table of Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Register Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Register Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Register Aliases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Bit Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Byte Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Address Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Bit Representation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Data Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Register Behavior. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Double-Buffered Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Bad Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Register Summary Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Manufacturer-Specific Register List and Default Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Manufacturer-Specific Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

AR0130 Registers Rev. D Pub. 11/14 EN

2

©Semiconductor Components Industries, LLC,2011.

�

ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

List of Tables

List of Tables

Table 1:

Table 2:

Table 3:

Table 4:

Address Space Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Manufacturer-Specific Register List and Default Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Manufacturer-Specific Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

AR0130 Registers Rev. D Pub. 11/14 EN

3

©Semiconductor Components Industries, LLC,2011.

�

ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

Introduction

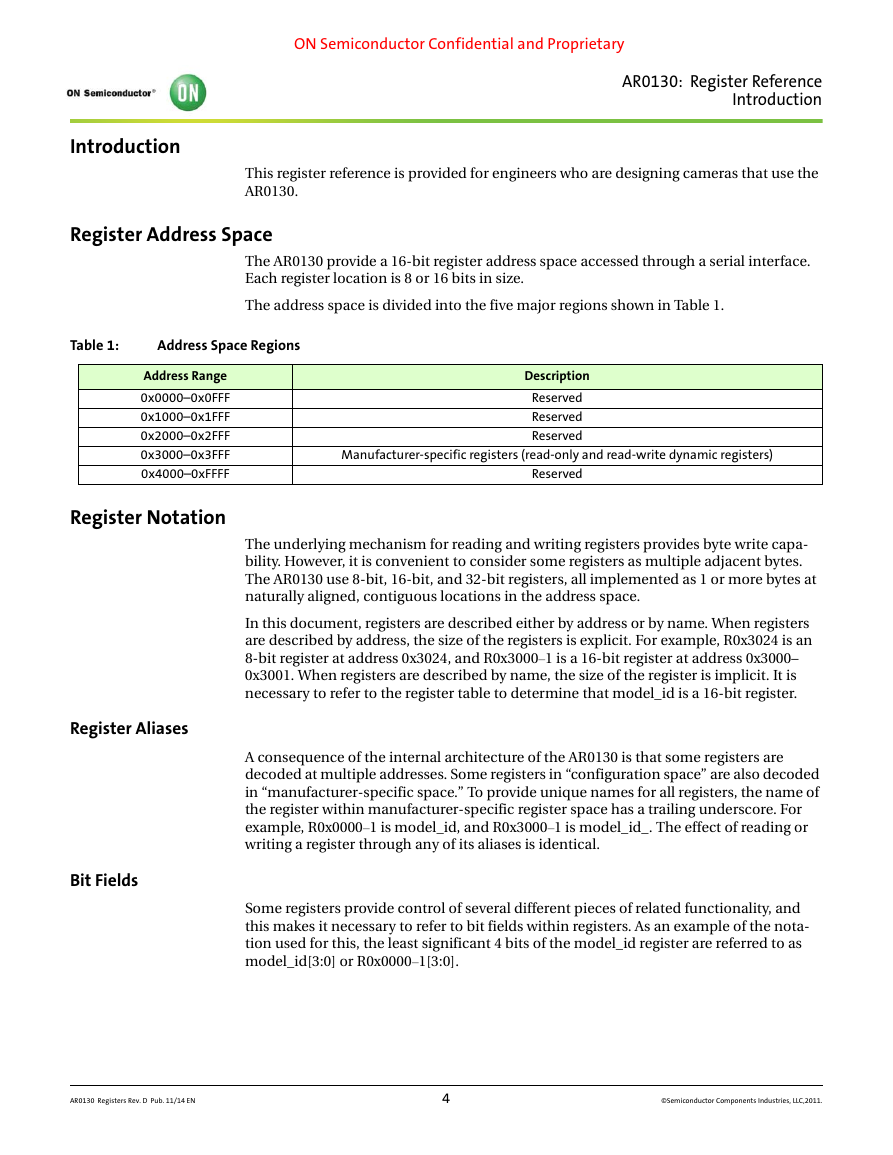

Introduction

This register reference is provided for engineers who are designing cameras that use the

AR0130.

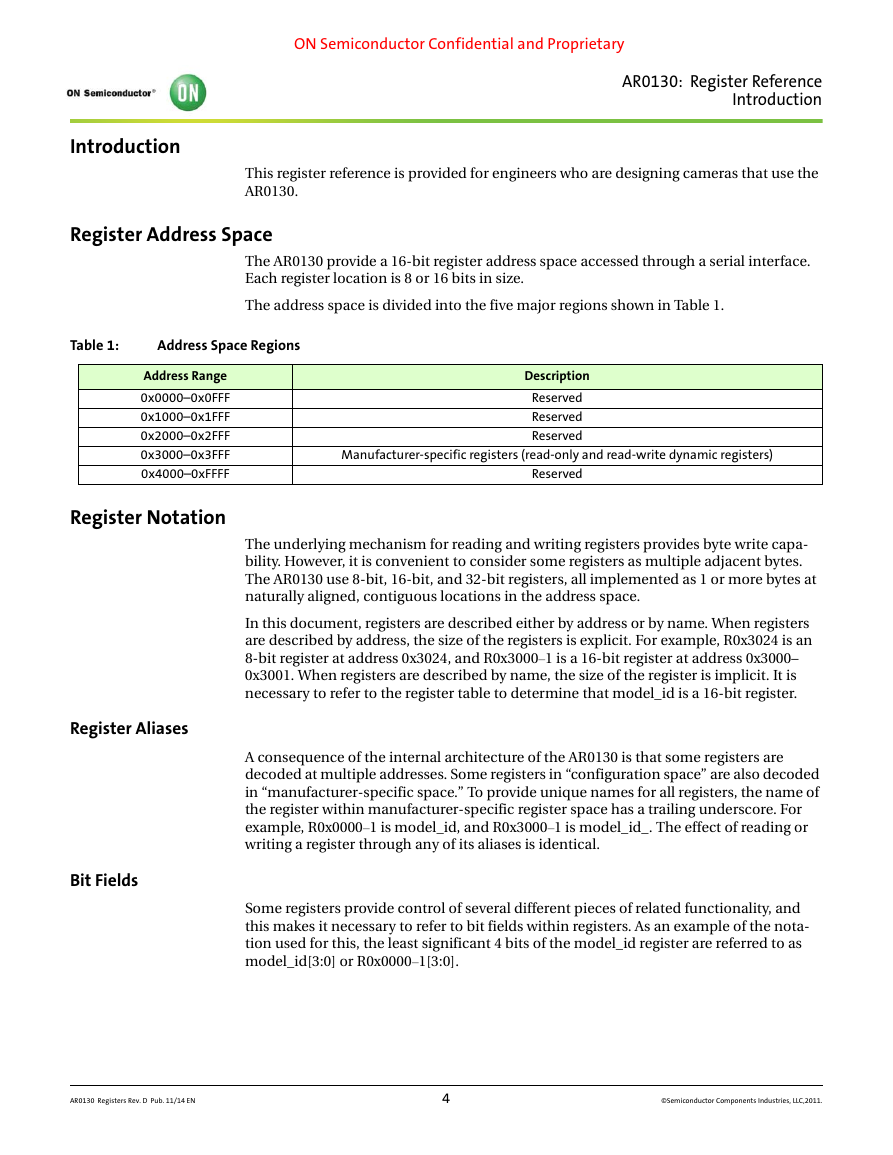

Register Address Space

The AR0130 provide a 16-bit register address space accessed through a serial interface.

Each register location is 8 or 16 bits in size.

The address space is divided into the five major regions shown in Table 1.

Table 1:

Address Space Regions

Address Range

0x0000–0x0FFF

0x1000–0x1FFF

0x2000–0x2FFF

0x3000–0x3FFF

0x4000–0xFFFF

Register Notation

Description

Reserved

Reserved

Reserved

Manufacturer-specific registers (read-only and read-write dynamic registers)

Reserved

The underlying mechanism for reading and writing registers provides byte write capa-

bility. However, it is convenient to consider some registers as multiple adjacent bytes.

The AR0130 use 8-bit, 16-bit, and 32-bit registers, all implemented as 1 or more bytes at

naturally aligned, contiguous locations in the address space.

In this document, registers are described either by address or by name. When registers

are described by address, the size of the registers is explicit. For example, R0x3024 is an

8-bit register at address 0x3024, and R0x3000–1 is a 16-bit register at address 0x3000–

0x3001. When registers are described by name, the size of the register is implicit. It is

necessary to refer to the register table to determine that model_id is a 16-bit register.

A consequence of the internal architecture of the AR0130 is that some registers are

decoded at multiple addresses. Some registers in “configuration space” are also decoded

in “manufacturer-specific space.” To provide unique names for all registers, the name of

the register within manufacturer-specific register space has a trailing underscore. For

example, R0x0000–1 is model_id, and R0x3000–1 is model_id_. The effect of reading or

writing a register through any of its aliases is identical.

Some registers provide control of several different pieces of related functionality, and

this makes it necessary to refer to bit fields within registers. As an example of the nota-

tion used for this, the least significant 4 bits of the model_id register are referred to as

model_id[3:0] or R0x0000–1[3:0].

Register Aliases

Bit Fields

AR0130 Registers Rev. D Pub. 11/14 EN

4

©Semiconductor Components Industries, LLC,2011.

�

ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

Register Notation

Registers that occupy more than 1 byte of address space are shown with the lowest

address in the highest-order byte lane to match the byte-ordering on the bus. For

example, the model_id register is R0x0000–1. In the register table the default value is

shown as 0x2402. This means that a READ from address 0x0000 would return 0x26, and a

READ from address 0x0001 would return 0x00. When reading this register as two 8-bit

transfers on the serial interface, the 0x26 will appear on the serial interface first, followed

by the 0x00.

All register addresses are aligned naturally. Registers that occupy two bytes of address

space are aligned to even 16-bit addresses, and registers that occupy four bytes of

address space are aligned to 16-bit addresses that are an integer multiple of 4.

For clarity, 32-bit hex numbers are shown with an underscore between the upper and

lower 16 bits. For example: 0x3000_01AB.

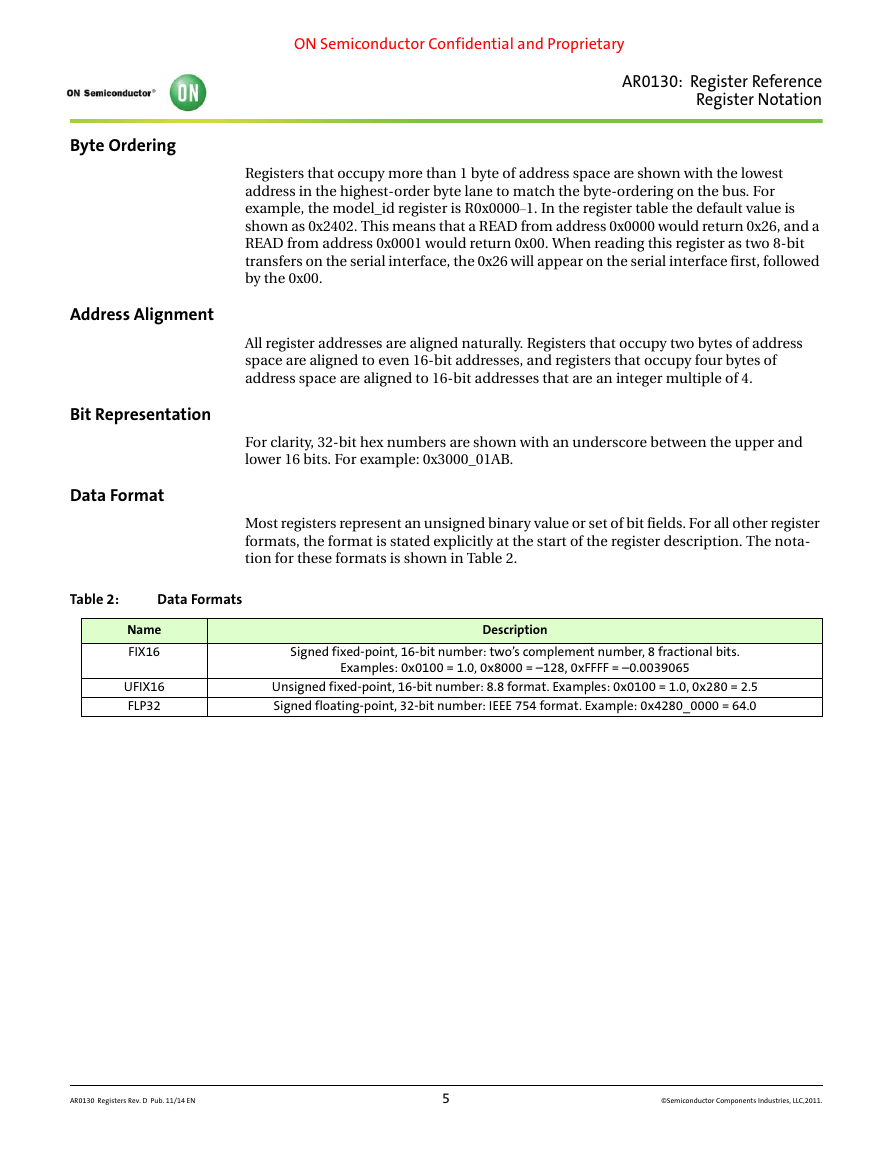

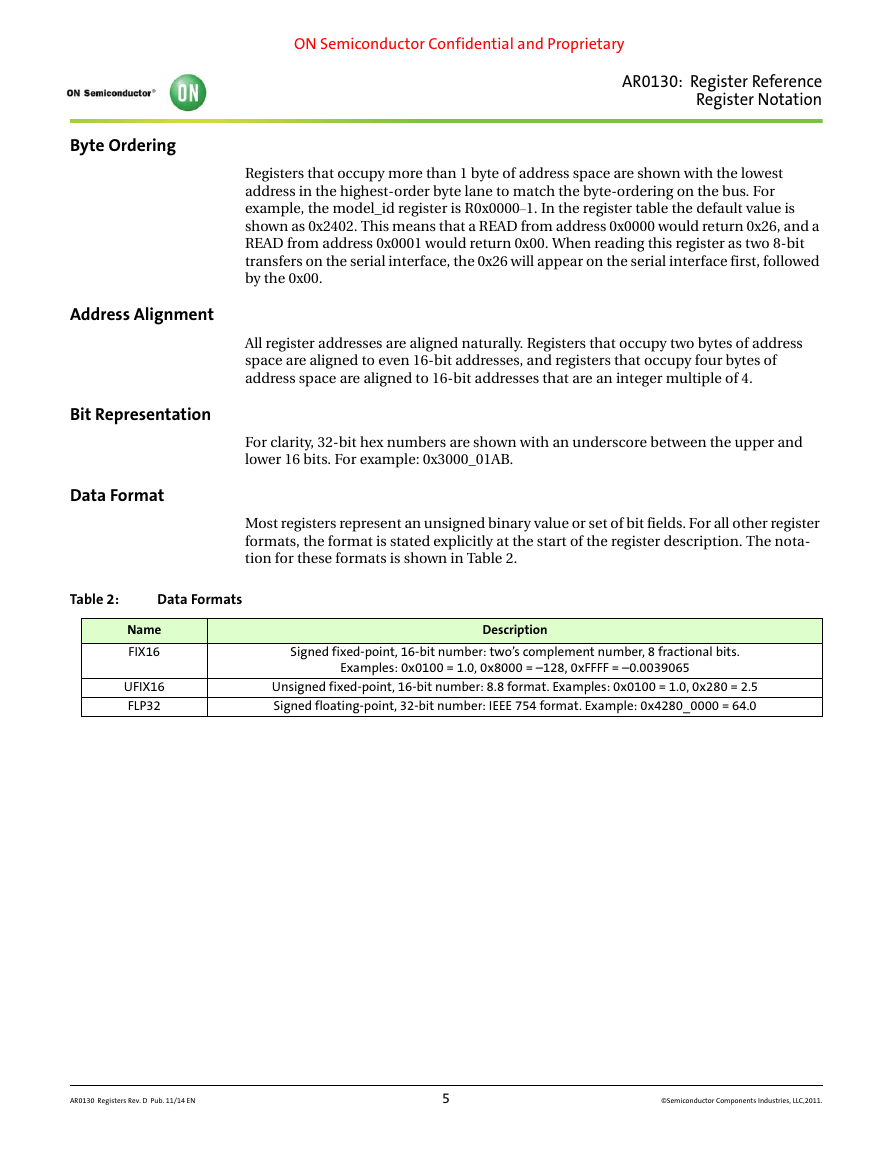

Most registers represent an unsigned binary value or set of bit fields. For all other register

formats, the format is stated explicitly at the start of the register description. The nota-

tion for these formats is shown in Table 2.

Byte Ordering

Address Alignment

Bit Representation

Data Format

Table 2:

Data Formats

Name

FIX16

UFIX16

FLP32

Description

Signed fixed-point, 16-bit number: two’s complement number, 8 fractional bits.

Examples: 0x0100 = 1.0, 0x8000 = –128, 0xFFFF = –0.0039065

Unsigned fixed-point, 16-bit number: 8.8 format. Examples: 0x0100 = 1.0, 0x280 = 2.5

Signed floating-point, 32-bit number: IEEE 754 format. Example: 0x4280_0000 = 64.0

AR0130 Registers Rev. D Pub. 11/14 EN

5

©Semiconductor Components Industries, LLC,2011.

�

ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

Register Behavior

Register Behavior

Registers vary from “read-only,” “read/write,” and “read, write-1-to-clear.”

Double-Buffered Registers

Bad Frames

Some sensor settings cannot be changed during frame readout. For example, changing

x_addr_start partway through frame readout would result in inconsistent row lengths

within a frame. To avoid this, the AR0130 double-buffer many registers by implementing

a “pending” and a “live” version. READs and WRITEs access the pending register; the live

register controls the sensor operation.

The value in the pending register is transferred to a live register at a fixed point in the

frame timing, called frame start. Frame start is defined as the point at which the first

dark row is read out internally to the sensor. In the register tables the “Sync’d” column

shows which registers or register fields are double-buffered in this way.

A bad frame is a frame where all rows do not have the same integration time or where

offsets to the pixel values have changed during the frame.

Many changes to the sensor register settings can cause a bad frame. For example, when

line_length_pck is changed, the new register value does not affect sensor behavior until

the next frame start. However, the frame that would be read out at that frame start will

have been integrated using the old row width, so reading it out using the new row width

would result in a frame with an incorrect integration time.

By default, bad frames are not masked. If the masked bad frame option is enabled, both

LV and FV are inhibited for these frames so that the vertical blanking time between

frames is extended by the frame time.

In the register tables, the “Bad Frame” column shows where changing a register or

register field will cause a bad frame. This notation is used:

N—No. Changing the register value will not produce a bad frame.

Y—Yes. Changing the register value might produce a bad frame.

YM—Yes; but the bad frame will be masked out when mask_corrupted_frames

(R0x0105) is set to “1.”

AR0130 Registers Rev. D Pub. 11/14 EN

6

©Semiconductor Components Industries, LLC,2011.

�

ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

Register Summary Table

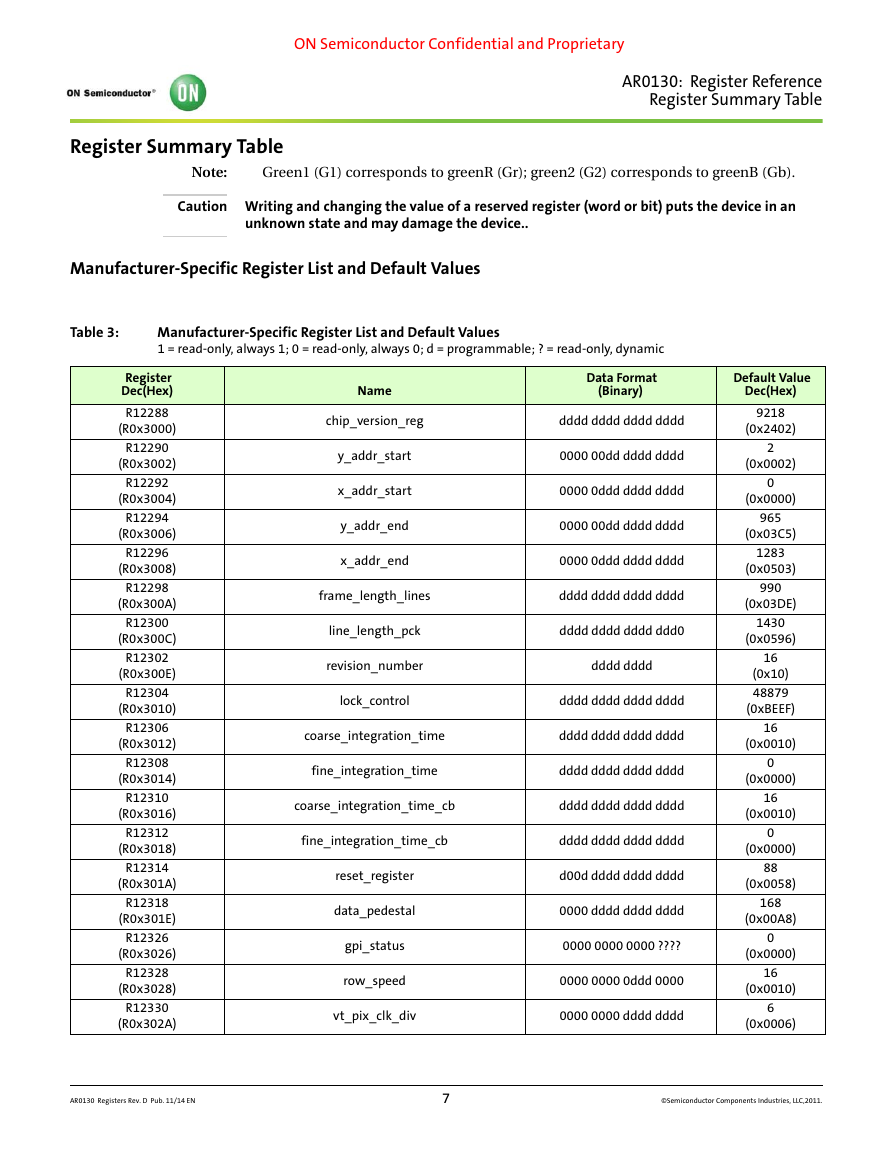

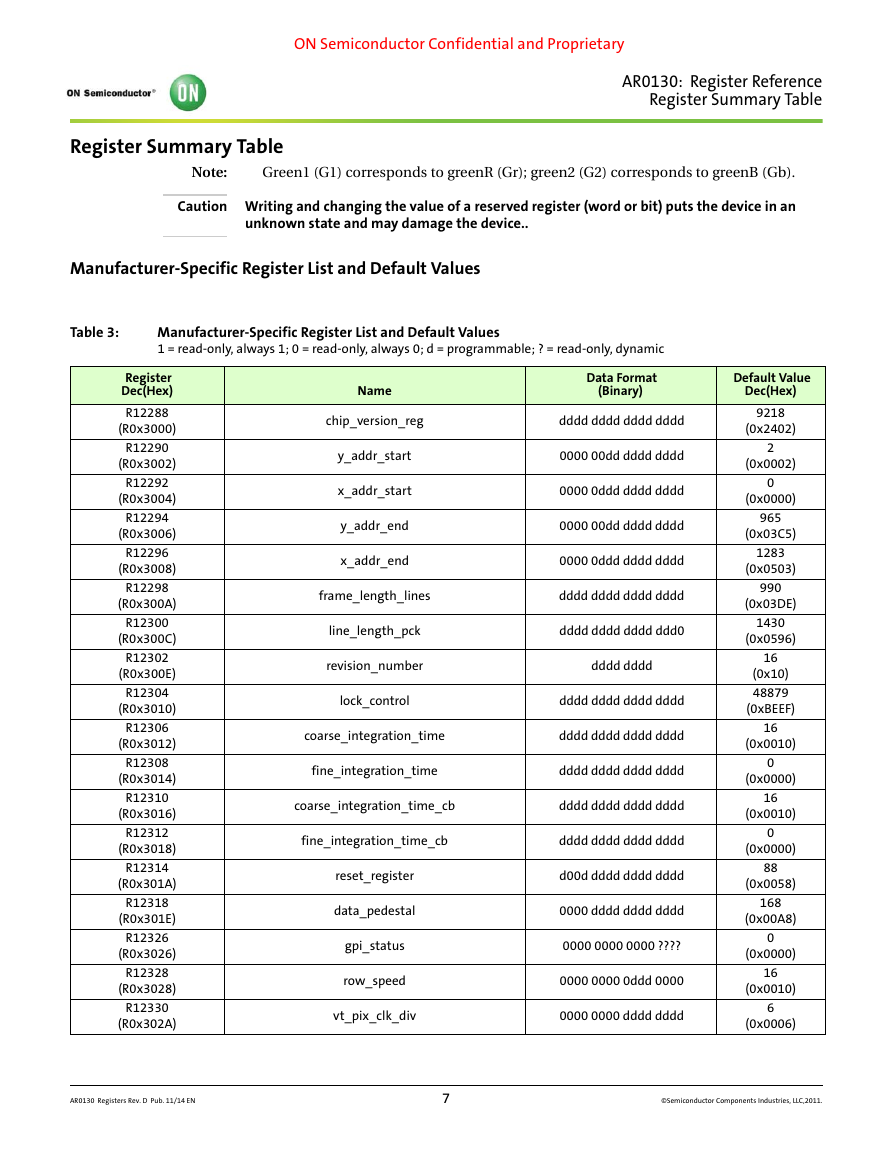

Register Summary Table

Note:

Green1 (G1) corresponds to greenR (Gr); green2 (G2) corresponds to greenB (Gb).

Caution Writing and changing the value of a reserved register (word or bit) puts the device in an

unknown state and may damage the device..

Manufacturer-Specific Register List and Default Values

Table 3:

Manufacturer-Specific Register List and Default Values

1 = read-only, always 1; 0 = read-only, always 0; d = programmable; ? = read-only, dynamic

Register

Dec(Hex)

R12288

(R0x3000)

R12290

(R0x3002)

R12292

(R0x3004)

R12294

(R0x3006)

R12296

(R0x3008)

R12298

(R0x300A)

R12300

(R0x300C)

R12302

(R0x300E)

R12304

(R0x3010)

R12306

(R0x3012)

R12308

(R0x3014)

R12310

(R0x3016)

R12312

(R0x3018)

R12314

(R0x301A)

R12318

(R0x301E)

R12326

(R0x3026)

R12328

(R0x3028)

R12330

(R0x302A)

Name

Data Format

(Binary)

Default Value

Dec(Hex)

chip_version_reg

dddd dddd dddd dddd

y_addr_start

x_addr_start

y_addr_end

x_addr_end

0000 00dd dddd dddd

0000 0ddd dddd dddd

0000 00dd dddd dddd

0000 0ddd dddd dddd

frame_length_lines

dddd dddd dddd dddd

line_length_pck

dddd dddd dddd ddd0

revision_number

dddd dddd

lock_control

dddd dddd dddd dddd

coarse_integration_time

dddd dddd dddd dddd

fine_integration_time

dddd dddd dddd dddd

coarse_integration_time_cb

dddd dddd dddd dddd

fine_integration_time_cb

dddd dddd dddd dddd

reset_register

data_pedestal

gpi_status

row_speed

d00d dddd dddd dddd

0000 dddd dddd dddd

0000 0000 0000 ????

0000 0000 0ddd 0000

vt_pix_clk_div

0000 0000 dddd dddd

9218

(0x2402)

2

(0x0002)

0

(0x0000)

965

(0x03C5)

1283

(0x0503)

990

(0x03DE)

1430

(0x0596)

16

(0x10)

48879

(0xBEEF)

16

(0x0010)

0

(0x0000)

16

(0x0010)

0

(0x0000)

88

(0x0058)

168

(0x00A8)

0

(0x0000)

16

(0x0010)

6

(0x0006)

AR0130 Registers Rev. D Pub. 11/14 EN

7

©Semiconductor Components Industries, LLC,2011.

�

ON Semiconductor Confidential and Proprietary

AR0130: Register Reference

Register Summary Table

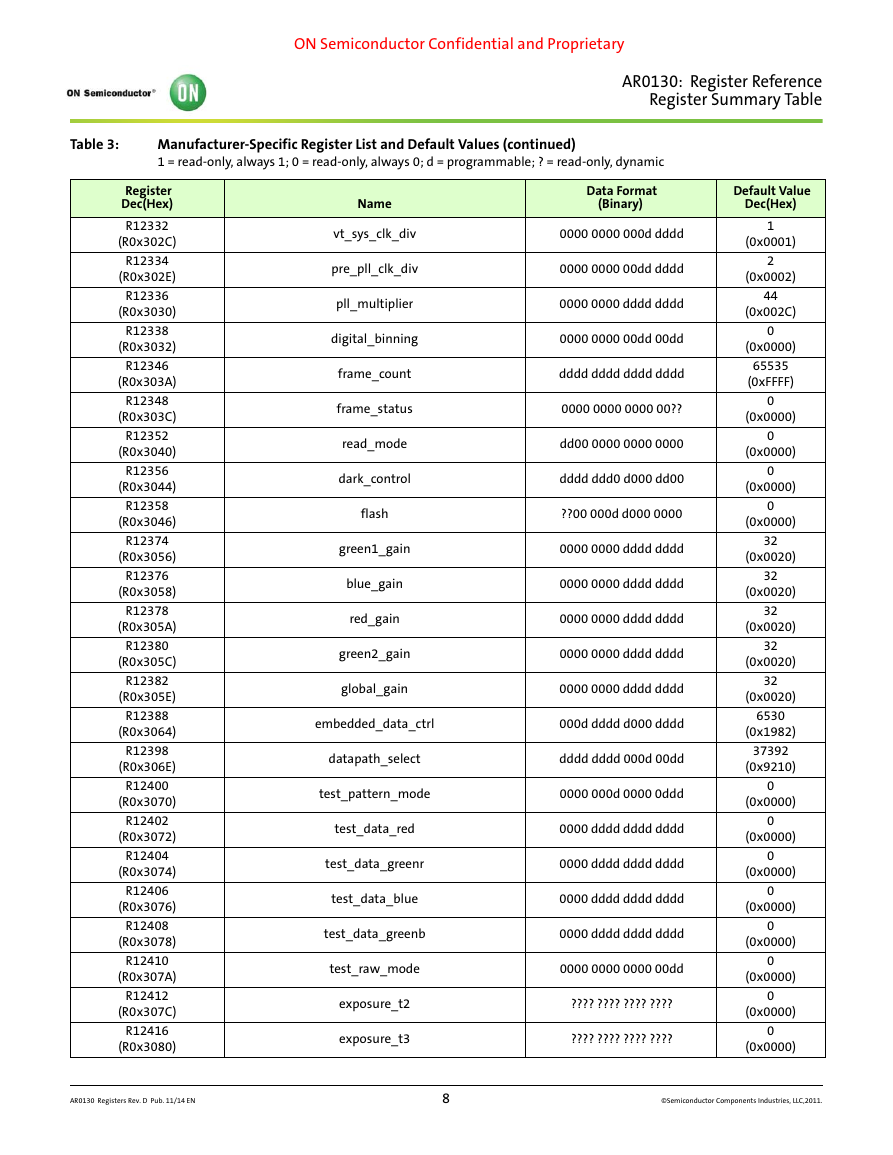

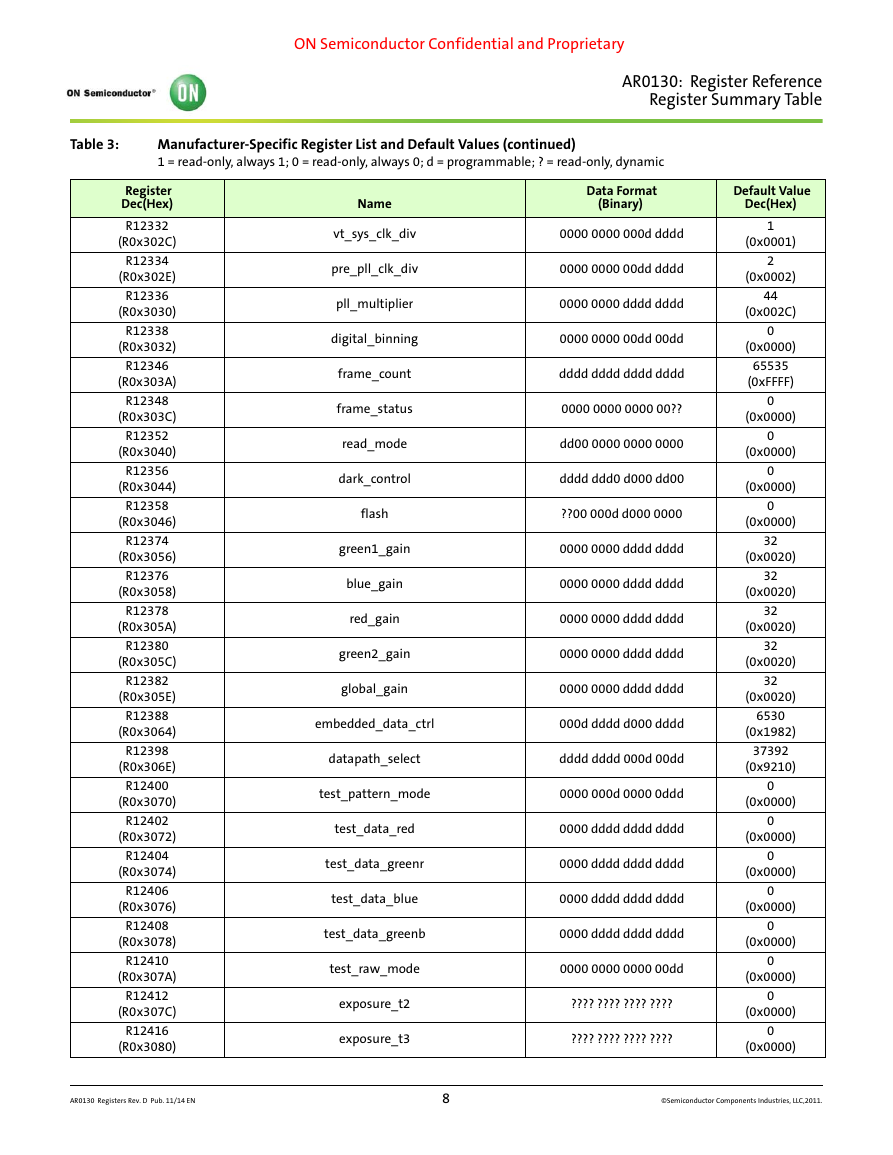

Table 3:

Manufacturer-Specific Register List and Default Values (continued)

1 = read-only, always 1; 0 = read-only, always 0; d = programmable; ? = read-only, dynamic

Data Format

(Binary)

Default Value

Dec(Hex)

Name

vt_sys_clk_div

pre_pll_clk_div

pll_multiplier

digital_binning

frame_count

frame_status

read_mode

dark_control

flash

green1_gain

blue_gain

red_gain

green2_gain

global_gain

0000 0000 000d dddd

0000 0000 00dd dddd

0000 0000 dddd dddd

0000 0000 00dd 00dd

dddd dddd dddd dddd

0000 0000 0000 00??

dd00 0000 0000 0000

dddd ddd0 d000 dd00

??00 000d d000 0000

0000 0000 dddd dddd

0000 0000 dddd dddd

0000 0000 dddd dddd

0000 0000 dddd dddd

0000 0000 dddd dddd

1

(0x0001)

2

(0x0002)

44

(0x002C)

0

(0x0000)

65535

(0xFFFF)

0

(0x0000)

0

(0x0000)

0

(0x0000)

0

(0x0000)

32

(0x0020)

32

(0x0020)

32

(0x0020)

32

(0x0020)

32

(0x0020)

6530

(0x1982)

37392

(0x9210)

0

(0x0000)

0

(0x0000)

0

(0x0000)

0

(0x0000)

0

(0x0000)

0

(0x0000)

0

(0x0000)

0

(0x0000)

Register

Dec(Hex)

R12332

(R0x302C)

R12334

(R0x302E)

R12336

(R0x3030)

R12338

(R0x3032)

R12346

(R0x303A)

R12348

(R0x303C)

R12352

(R0x3040)

R12356

(R0x3044)

R12358

(R0x3046)

R12374

(R0x3056)

R12376

(R0x3058)

R12378

(R0x305A)

R12380

(R0x305C)

R12382

(R0x305E)

R12388

(R0x3064)

R12398

(R0x306E)

R12400

(R0x3070)

R12402

(R0x3072)

R12404

(R0x3074)

R12406

(R0x3076)

R12408

(R0x3078)

R12410

(R0x307A)

R12412

(R0x307C)

R12416

(R0x3080)

embedded_data_ctrl

000d dddd d000 dddd

datapath_select

dddd dddd 000d 00dd

test_pattern_mode

0000 000d 0000 0ddd

test_data_red

0000 dddd dddd dddd

test_data_greenr

0000 dddd dddd dddd

test_data_blue

0000 dddd dddd dddd

test_data_greenb

0000 dddd dddd dddd

test_raw_mode

0000 0000 0000 00dd

exposure_t2

exposure_t3

???? ???? ???? ????

???? ???? ???? ????

AR0130 Registers Rev. D Pub. 11/14 EN

8

©Semiconductor Components Industries, LLC,2011.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc