数字电路知识点汇总(东南大学)

第 1 章 数字逻辑概论

一、进位计数制

1.十进制与二进制数的转换

2.二进制数与十进制数的转换

3.二进制数与 16 进制数的转换

二、基本逻辑门电路

第 2 章 逻辑代数

表示逻辑函数的方法,归纳起来有:真值表,函数表达式,卡诺

图,逻辑图及波形图等几种。

一、逻辑代数的基本公式和常用公式

1)常量与变量的关系A+0=A与A 1 A

A+1=1 与

00 A

AA =1 与 AA =0

2)与普通代数相运算规律

a.交换律:A+B=B+A

ABBA

b.结合律:(A+B)+C=A+(B+C)

(

c.分配律:

CBACBA

)

(

)

( CBA

)

= BA

CA

CBA

(

CABA

)()

)

)

3)逻辑函数的特殊规律

a.同一律:A+A+A

1

�

b.摩根定律:

BABA

,

BABA

b.关于否定的性质A= A

二、逻辑函数的基本规则

代入规则

在任何一个逻辑等式中,如果将等式两边同时出现某一变量A的地

方,都用一个函数L表示,则等式仍然成立,这个规则称为代入规则

例如:

CBACBA

可令L= CB

则上式变成

LALA

=

CBALA

三、逻辑函数的:——公式化简法

公式化简法就是利用逻辑函数的基本公式和常用公式化简逻辑

函数,通常,我们将逻辑函数化简为最简的与—或表达式

1)合并项法:

利用A+

AA

1

或

ABABA

,将二项合并为一项,合并时可消去

一个变量

例如:L=

CCBACBACBA

(

)

BA

2)吸收法

利用公式

ABAA

,消去多余的积项,根据代入规则 BA 可以是

任何一个复杂的逻辑式

例如 化简函数L=

AB

EBDA

解:先用摩根定理展开: AB = BA

再用吸收法

L=

AB

EBDA

2

�

=

EBDABA

=

(

DAA

)

(

EBB

)

BDA

)

=

1(

A

= BA

3)消去法

利用

BABAA

1(

EB

)

消去多余的因子

例如,化简函数L=

EBABABA

ABC

解: L=

EBABABA

ABC

=

(

EBABA

)

(

BA

ABC

)

=

(

EBBA

)

(

BA

BC

)

=

(

BBCBA

)(

)

(

CBBBA

)(

)

=

=

=

4)配项法

(

CBA

)

(

CBA

)

BACABA

AC

CBABA

利用公式

CABA

BC

CABA

将某一项乘以( AA ),即乘以 1,

然后将其折成几项,再与其它项合并。

例如:化简函数L=

BACBCBBA

解:L=

BACBCBBA

=

CBBA

(

)

CCBACBAA

(

)

=

BCACBACBACBBA

CBA

=

(

CBABA

)

(

CBACB

)

(

BCACBA

)

3

�

=

BA

1(

C

)

CB

1(

)

A

CACBBA

=

2.应用举例

BBCA

(

)

将下列函数化简成最简的与-或表达式

1)L=

BA

BD

DCE

AD

2) L=

CBBA

AC

3) L=

AB

CBCA

ABCD

解:1)L=

BA

BD

DCE

AD

=

)

ABDBA

(

DCE

=

=

ABDBA

DCE

BADBA

DCE

=

(

BADBA

)(

AB

)

DCE

=

=

DBA

DCE

DBA

2) L=

CBBA

AC

=

=

=

=

)

CCBA

(

CB

AC

CBCBACBA

AC

AC

1(

B

)

CB

1(

)

A

AC

CB

3) L=

AB

CBCA

ABCD

=

=

AB

)

AACBCA

(

ABCD

AB

CA

CBACAB

ABCD

4

�

=

(

AB

CAB

ABCD

)

(

CBACA

)

=

AB

1(

C

CD

)

CA

1(

B

)

=

AB

CA

四、逻辑函数的化简—卡诺图化简法:

卡诺图是由真值表转换而来的,在变量卡诺图中,变量的取值顺

序是按循环码进行排列的,在与—或表达式的基础上,画卡诺图的步

骤是:

1.画出给定逻辑函数的卡诺图,若给定函数有 n 个变量,表示卡

诺图矩形小方块有 n2 个。

2.在图中标出给定逻辑函数所包含的全部最小项,并在最小项内

填 1,剩余小方块填 0.

用卡诺图化简逻辑函数的基本步骤:

1.画出给定逻辑函数的卡诺图

2.合并逻辑函数的最小项

3.选择乘积项,写出最简与—或表达式

选择乘积项的原则:

①它们在卡诺图的位置必须包括函数的所有最小项

②选择的乘积项总数应该最少

③每个乘积项所包含的因子也应该是最少的

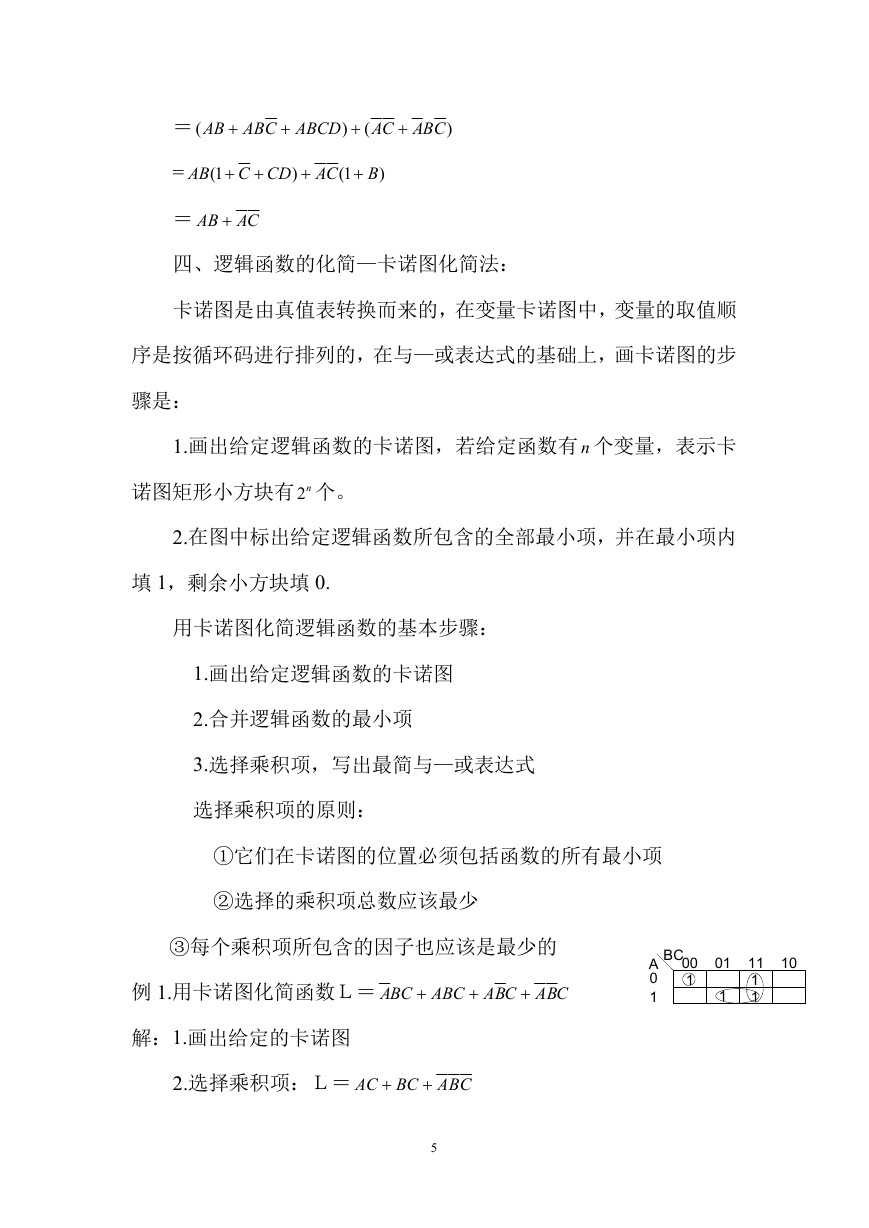

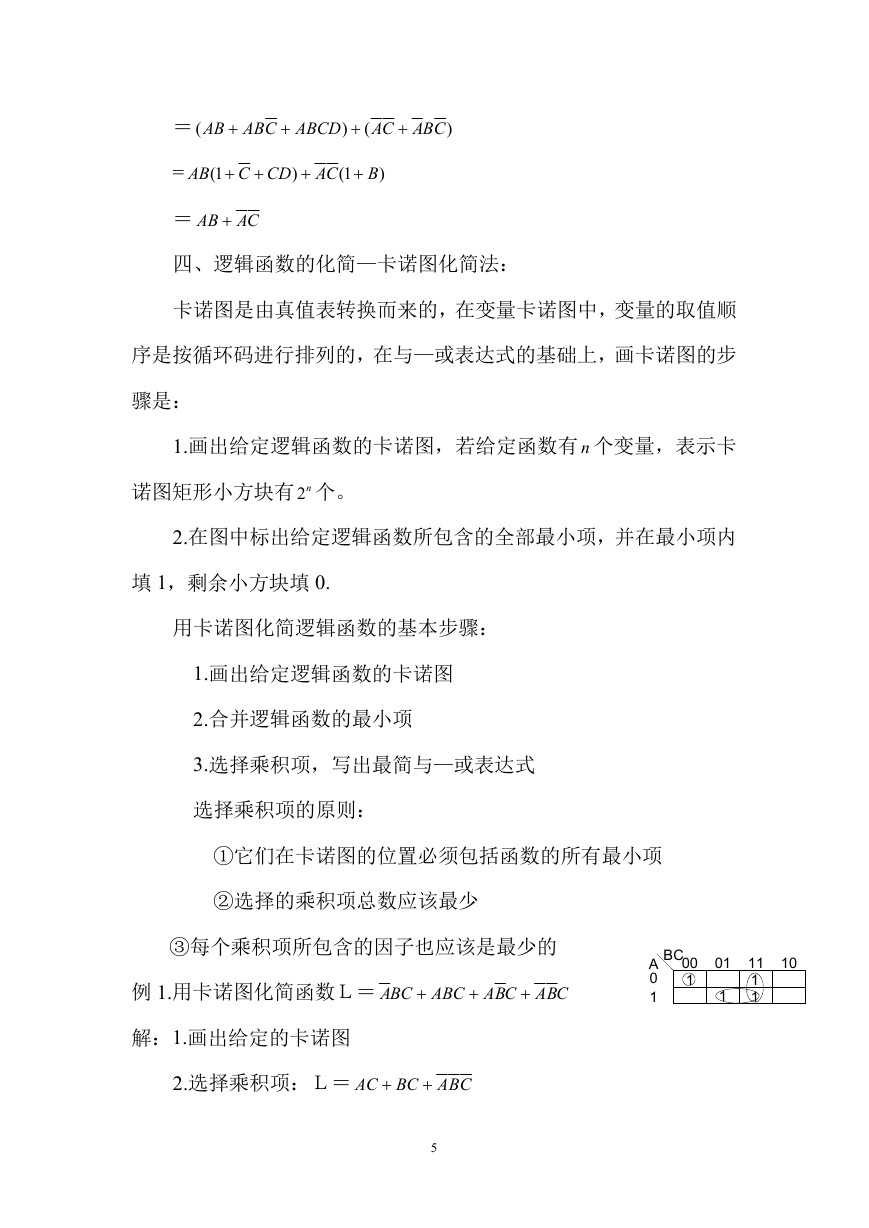

例 1.用卡诺图化简函数L=

BCA

ABC

CBACBA

A BC

0

1

00

1

01

1

11

1

1

10

解:1.画出给定的卡诺图

2.选择乘积项:L=

AC

BC

CBA

5

�

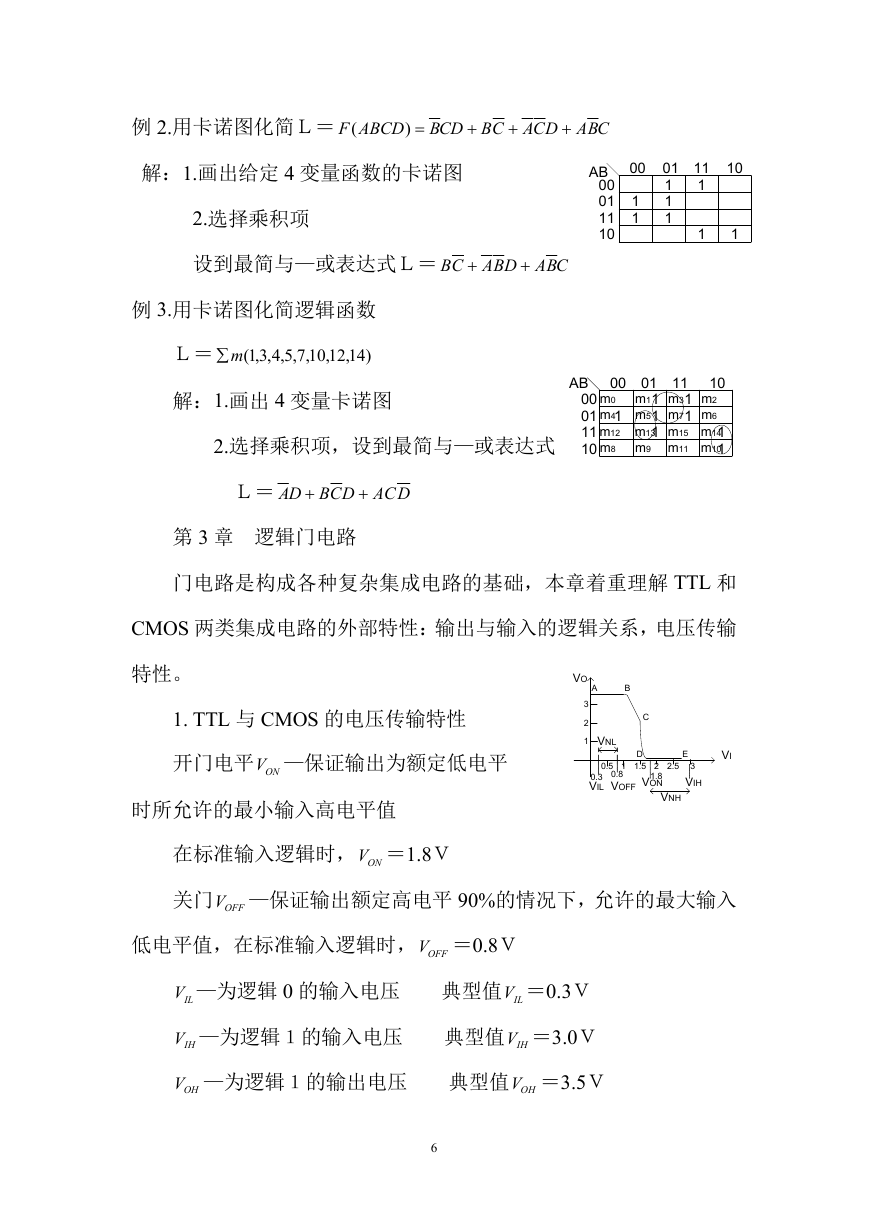

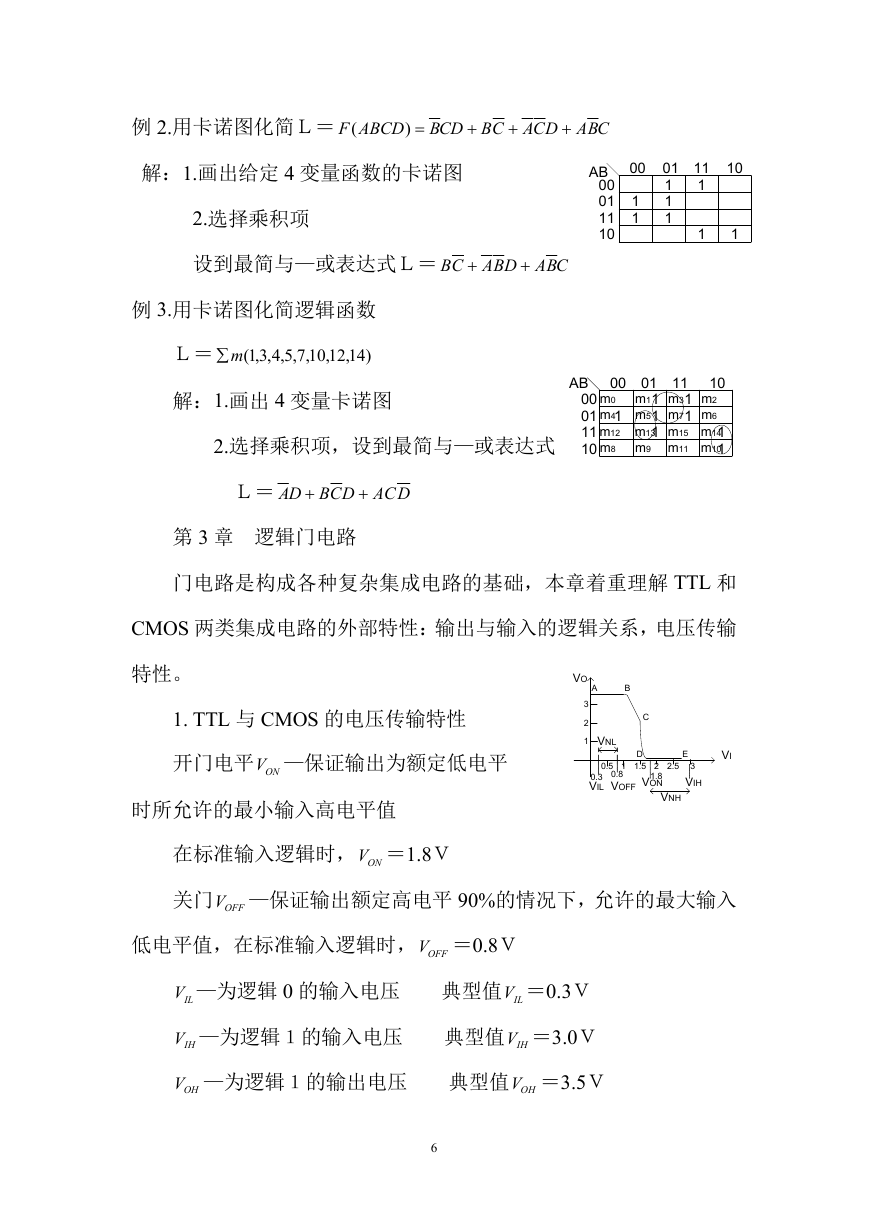

例 2.用卡诺图化简L=

F

(

ABCD

)

CDB

解:1.画出给定 4 变量函数的卡诺图

CBADCACB

2.选择乘积项

设到最简与—或表达式L=

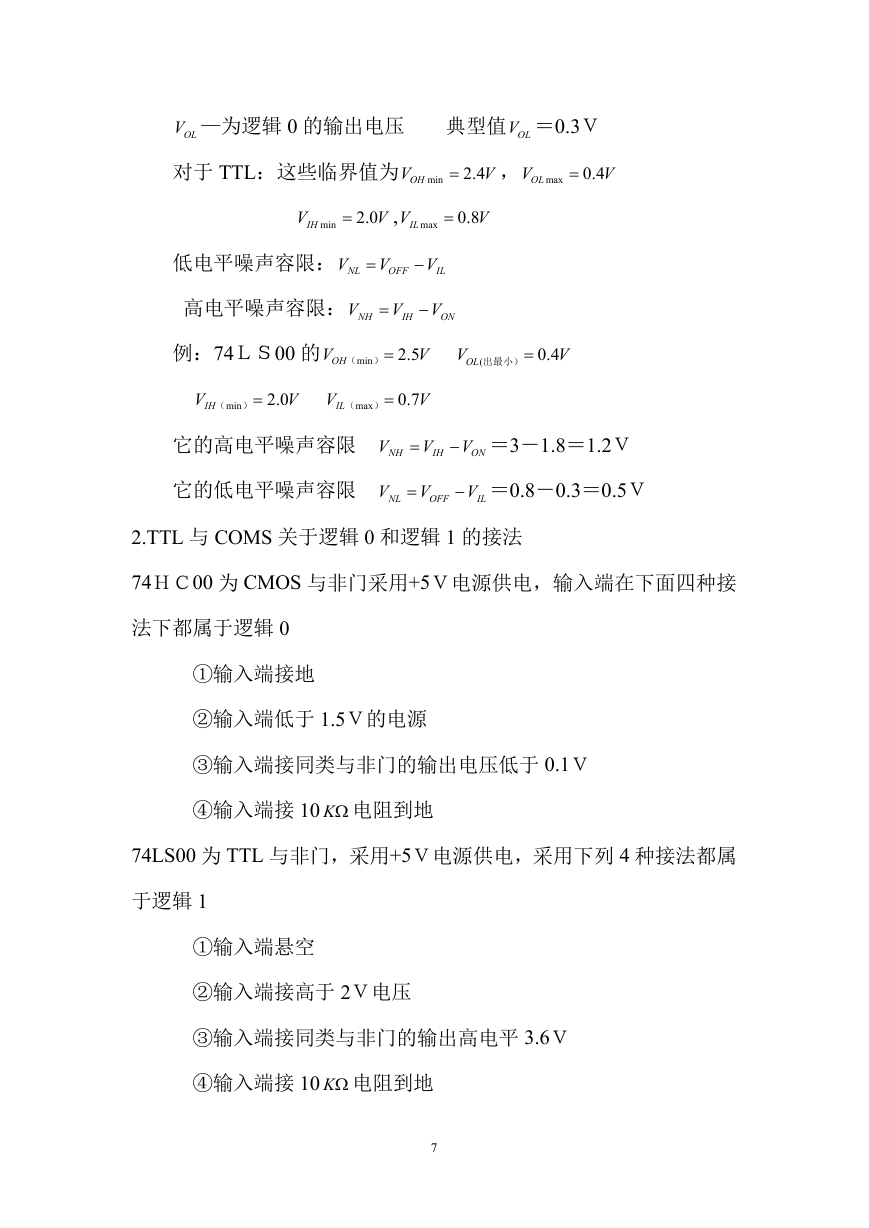

例 3.用卡诺图化简逻辑函数

L=

)14,12,10,7,5,4,3,1(m

解:1.画出 4 变量卡诺图

CBADBACB

2.选择乘积项,设到最简与—或表达式

L=

DCBDA

DAC

第 3 章 逻辑门电路

AB

00

01

11

10

00

1

1

01

1

1

1

10

11

1

1

1

AB

00

01

11

10

00

01

1

m1

m0

1

1

m4 m5

1

m12 m13

m8 m9

11

1

m3

1

m7

m15

m11

10

m2

m6

1

m14

1

m10

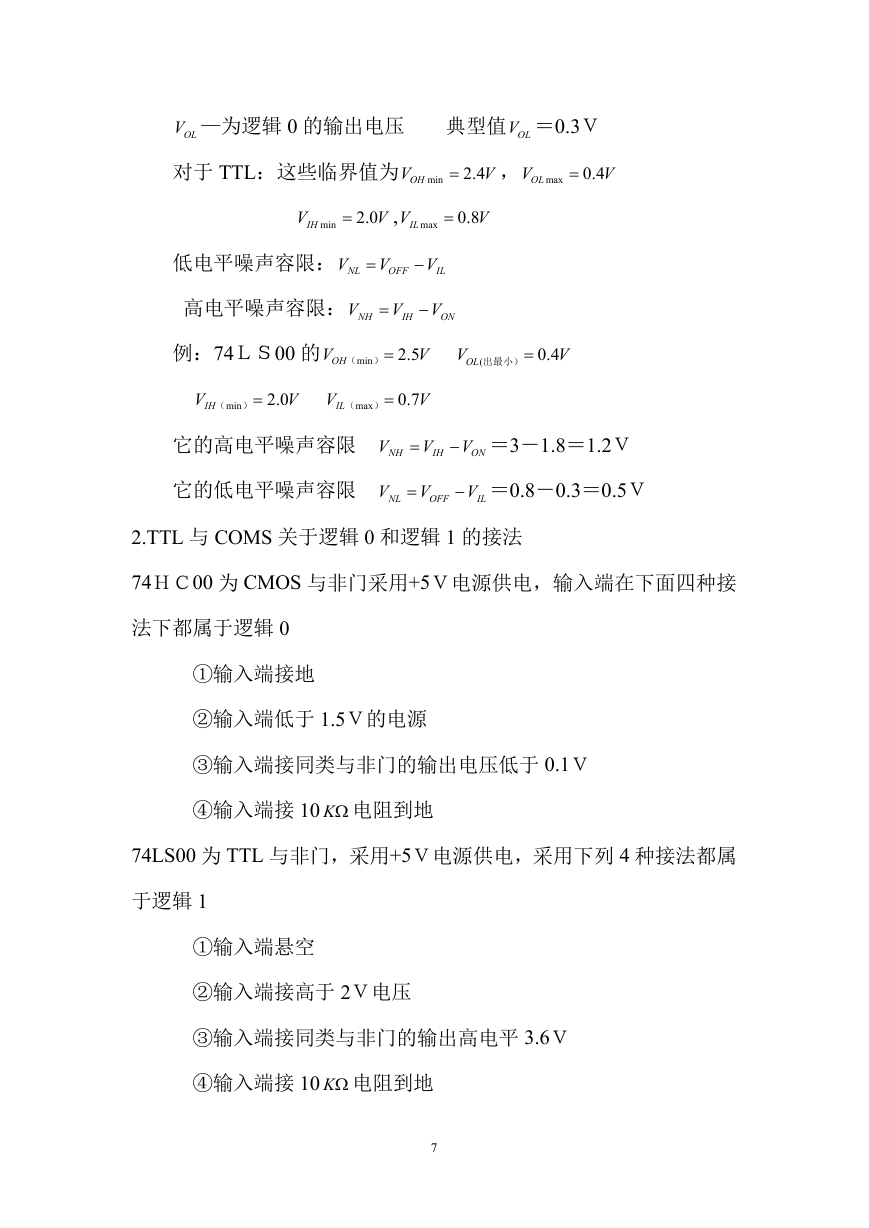

门电路是构成各种复杂集成电路的基础,本章着重理解 TTL 和

CMOS 两类集成电路的外部特性:输出与输入的逻辑关系,电压传输

特性。

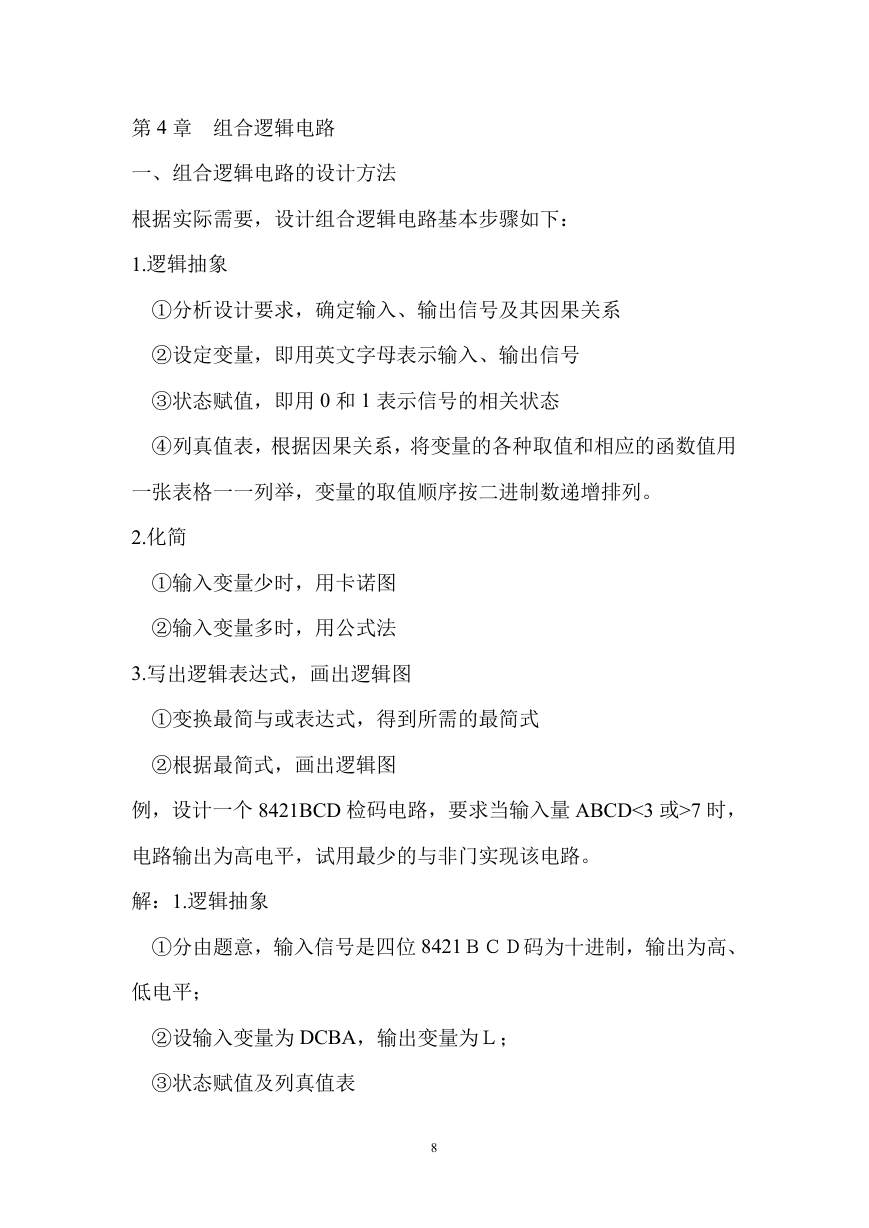

1. TTL 与 CMOS 的电压传输特性

开门电平 ONV —保证输出为额定低电平

时所允许的最小输入高电平值

在标准输入逻辑时, ONV =1.8V

VO

A

B

3

2

1

VNL

C

D

0.5 1 1.5 2 2.5

1.8

VOFF VON

0.3 0.8

VIL

VNH

VI

E

3

VIH

关门 OFFV —保证输出额定高电平 90%的情况下,允许的最大输入

低电平值,在标准输入逻辑时, OFFV =0.8V

ILV —为逻辑 0 的输入电压 典型值 ILV =0.3V

IHV —为逻辑1的输入电压 典型值 IHV =3.0V

OHV —为逻辑1的输出电压 典型值 OHV =3.5V

6

�

OLV —为逻辑 0 的输出电压 典型值 OLV =0.3V

对于 TTL:这些临界值为

VOH

min ,

4.2

V

VOL

max

4.0

V

VIH

min

0.2

V

,

VIL

max

8.0

V

低电平噪声容限:

V

NL

V

OFF

V

IL

高电平噪声容限:

V

NH

V

IH

V

ON

例:74LS00 的

VOH

min )(

5.2

V

VOL

(

出最小)

4.0

V

VIH

min )(

0.2

V

VIL

max )(

7.0

V

它的高电平噪声容限

V

NH

V

IH

V

ON

=3-1.8=1.2V

它的低电平噪声容限

V

NL

V

OFF

V

IL

=0.8-0.3=0.5V

2.TTL 与 COMS 关于逻辑 0 和逻辑 1 的接法

74HC00 为 CMOS 与非门采用+5V电源供电,输入端在下面四种接

法下都属于逻辑 0

①输入端接地

②输入端低于 1.5V的电源

③输入端接同类与非门的输出电压低于 0.1V

④输入端接 10 K 电阻到地

74LS00 为 TTL 与非门,采用+5V电源供电,采用下列 4 种接法都属

于逻辑 1

①输入端悬空

②输入端接高于 2V电压

③输入端接同类与非门的输出高电平 3.6V

④输入端接 10 K 电阻到地

7

�

第 4 章 组合逻辑电路

一、组合逻辑电路的设计方法

根据实际需要,设计组合逻辑电路基本步骤如下:

1.逻辑抽象

①分析设计要求,确定输入、输出信号及其因果关系

②设定变量,即用英文字母表示输入、输出信号

③状态赋值,即用 0 和 1 表示信号的相关状态

④列真值表,根据因果关系,将变量的各种取值和相应的函数值用

一张表格一一列举,变量的取值顺序按二进制数递增排列。

2.化简

①输入变量少时,用卡诺图

②输入变量多时,用公式法

3.写出逻辑表达式,画出逻辑图

①变换最简与或表达式,得到所需的最简式

②根据最简式,画出逻辑图

例,设计一个 8421BCD 检码电路,要求当输入量 ABCD<3 或>7 时,

电路输出为高电平,试用最少的与非门实现该电路。

解:1.逻辑抽象

①分由题意,输入信号是四位 8421BCD码为十进制,输出为高、

低电平;

②设输入变量为 DCBA,输出变量为L;

③状态赋值及列真值表

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc