特性

射频输出频率范围:54 MHz 至 13,600 MHz

小数 N 分频频率合成器与整数 N 分频频率合

成器

高分辨率 38 位模数

相位频率检测器(PFD)工作至 125 MHz

参考频率达 600 MHz

-40°C 至+85°C 范围内维持锁频

低相位噪声的 VCO

可编程 1, 2, 4, 8, 16, 32 或 64 分频输出

模拟和数字电源:3.3V

电荷泵和 VCO 电源:5V,典型

1.8V 逻辑兼容性

可编程双模预分频器:4/5 或 8/9

可编程的输出功率

射频输出静音功能

模拟和数字锁定检测

ADIsimPLL 设计工具软件支持

应用

无线基础设施(W-CDMA,TD-SCDMA,WiMAX,

GSM,PCS,DCS,DECT)

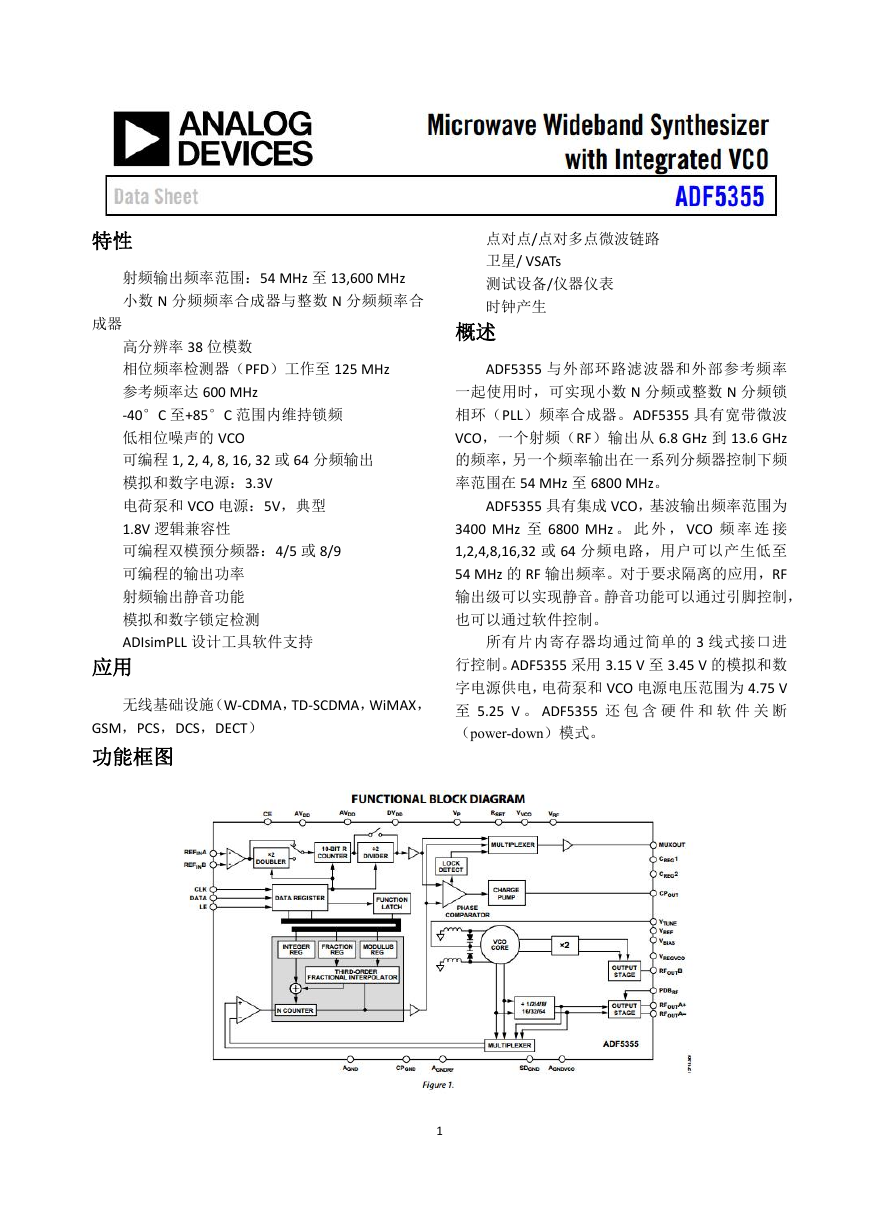

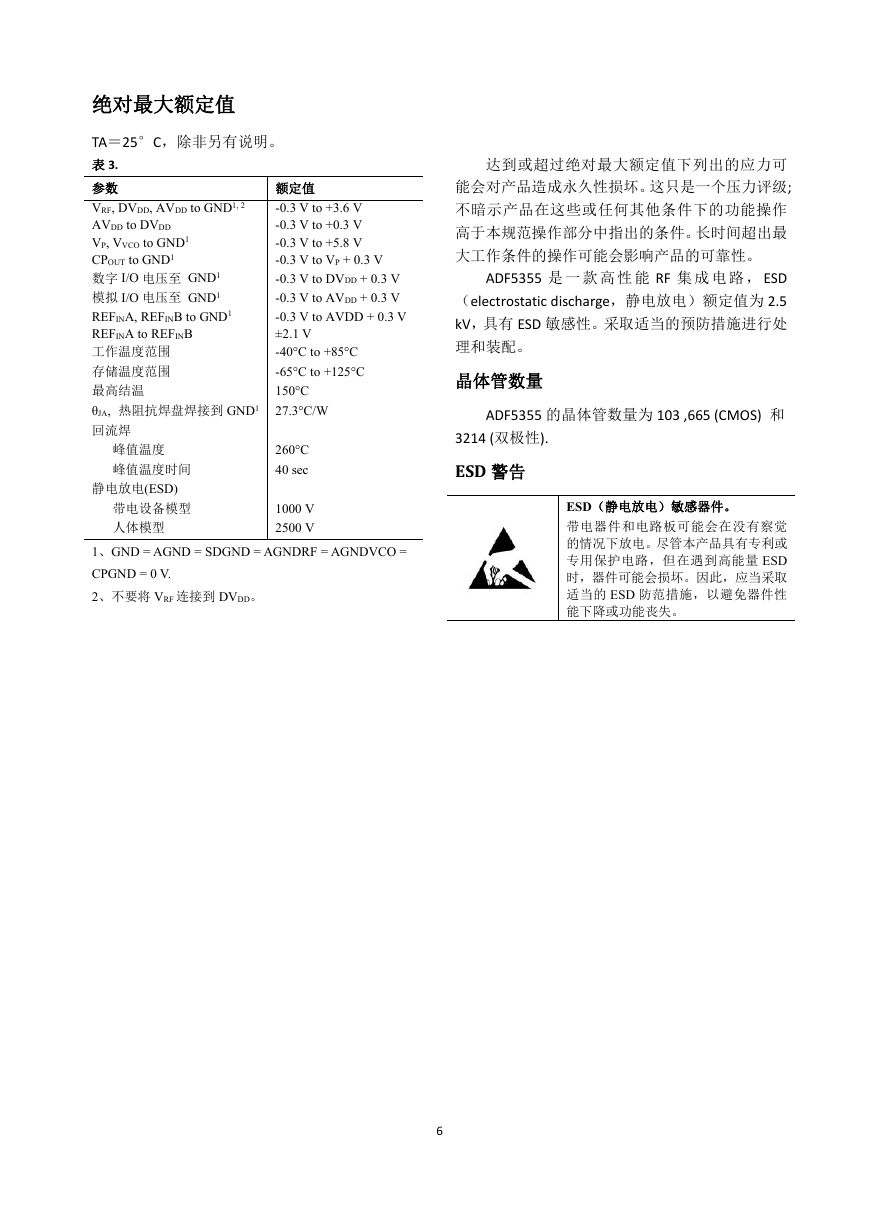

功能框图

点对点/点对多点微波链路

卫星/ VSATs

测试设备/仪器仪表

时钟产生

概述

ADF5355 与外部环路滤波器和外部参考频率

一起使用时,可实现小数 N 分频或整数 N 分频锁

相环(PLL)频率合成器。ADF5355 具有宽带微波

VCO,一个射频(RF)输出从 6.8 GHz 到 13.6 GHz

的频率,另一个频率输出在一系列分频器控制下频

率范围在 54 MHz 至 6800 MHz。

ADF5355 具有集成 VCO,基波输出频率范围为

3400 MHz 至 6800 MHz 。 此 外 , VCO 频 率 连 接

1,2,4,8,16,32 或 64 分频电路,用户可以产生低至

54 MHz 的 RF 输出频率。对于要求隔离的应用,RF

输出级可以实现静音。静音功能可以通过引脚控制,

也可以通过软件控制。

所有片内寄存器均通过简单的 3 线式接口进

行控制。ADF5355 采用 3.15 V 至 3.45 V 的模拟和数

字电源供电,电荷泵和 VCO 电源电压范围为 4.75 V

至 5.25 V 。 ADF5355 还 包 含 硬 件 和 软 件 关 断

(power-down)模式。

1

�

目录

特性........................................................................1

应用........................................................................1

概述........................................................................1

功能框图................................................................1

目录........................................................................2

详细说明................................................................3

时序特性............................................................5

绝对最大额定值....................................................6

晶体管数量........................................................6

ESD 警告............................................................ 6

引脚配置和功能描述............................................7

典型性能特点........................................................9

REGISTER 7....................................................... 25

REGISTER 8....................................................... 26

REGISTER 9....................................................... 26

REGISTER 10..................................................... 27

REGISTER 11..................................................... 28

REGISTER 12..................................................... 28

寄存器初始化顺序..........................................28

频率更新顺序..................................................29

RF 合成器 - 一个工作示例........................... 29

参考倍频器和参考分频器..............................30

杂散优化和快速锁定......................................30

优化抖动..........................................................30

杂散机制..........................................................30

锁定时间..........................................................30

电路描述..............................................................14

应用信息..............................................................32

参考输入..........................................................14

RF N 分频........................................................ 14

鉴频鉴相器(PFD)和电荷泵....................... 15

供电电源..........................................................32

芯片封装的 PCB 设计指导原则..................... 32

输出匹配..........................................................32

MUXOUT 和锁定检测..................................... 15

外形尺寸..............................................................33

订购指南..........................................................33

输入移位寄存器..............................................15

编程模式..........................................................16

VCO...................................................................16

输出级..............................................................16

寄存器映射..........................................................18

REGISTER 0....................................................... 18

REGISTER 1....................................................... 19

REGISTER 2....................................................... 19

REGISTER 3....................................................... 20

REGISTER 4....................................................... 21

REGISTER 5....................................................... 22

REGISTER 6....................................................... 23

2

�

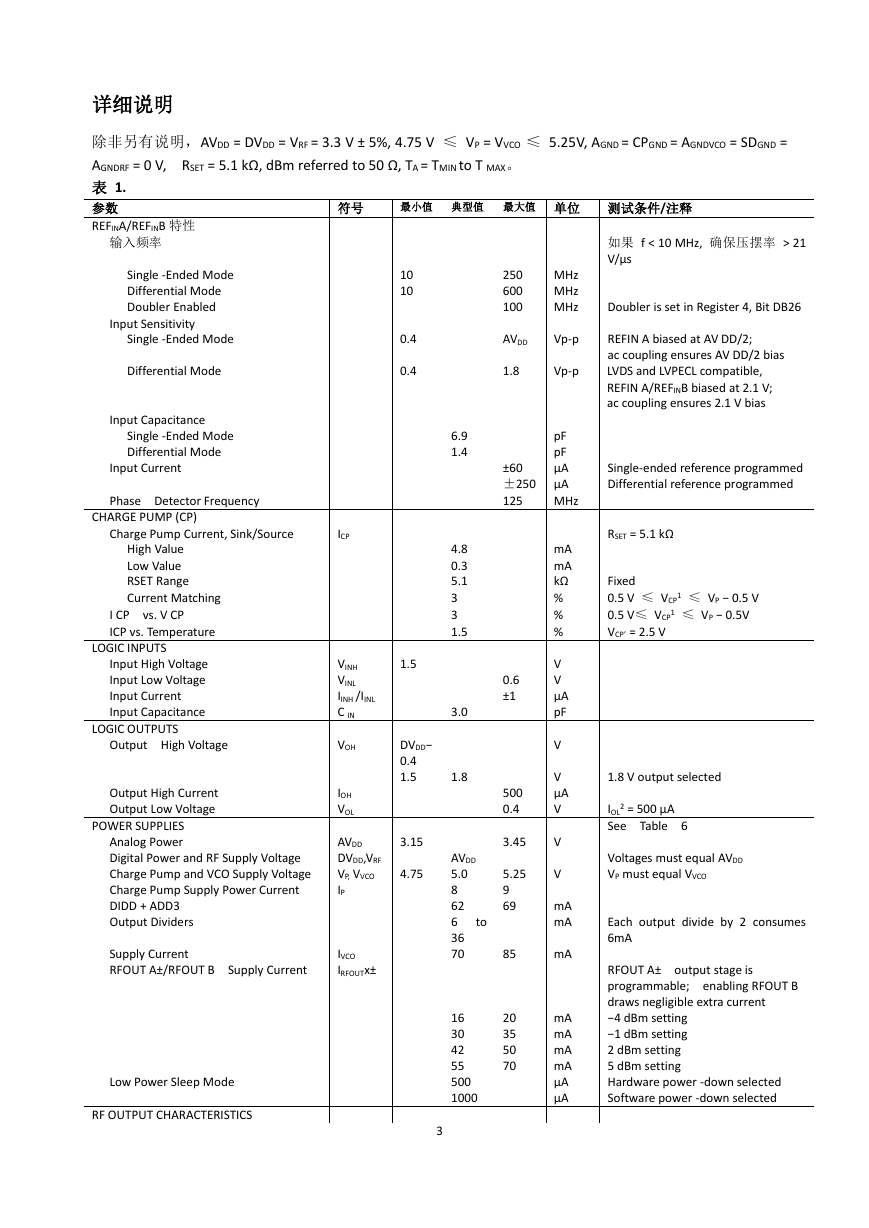

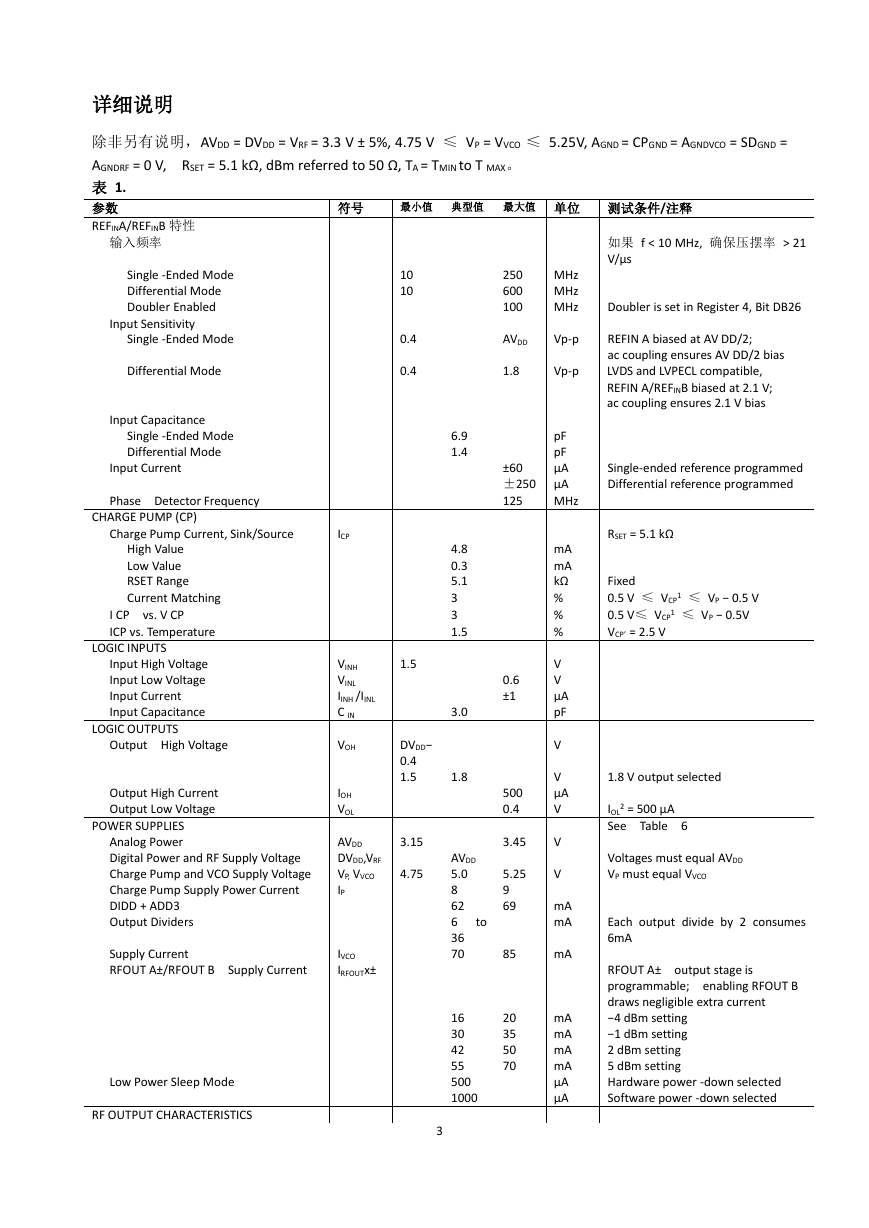

详细说明

除非另有说明,AVDD = DVDD = VRF = 3.3 V ± 5%, 4.75 V ≤ VP = VVCO ≤ 5.25V, AGND = CPGND = AGNDVCO = SDGND =

AGNDRF = 0 V, RSET = 5.1 kΩ, dBm referred to 50 Ω, TA = TMIN to T MAX。

表 1.

参数

REFINA/REFINB 特性

最小值 典型值 最大值 单位

测试条件/注释

符号

250

600

100

AVDD

1.8

±60

±250

125

MHz

MHz

MHz

Vp-p

Vp-p

pF

pF

µA

µA

MHz

mA

mA

kΩ

%

%

%

V

V

µA

pF

V

V

µA

V

V

V

mA

mA

mA

mA

mA

mA

mA

µA

µA

0.6

±1

500

0.4

3.45

5.25

9

69

85

20

35

50

70

如果 f < 10 MHz, 确保压摆率 > 21

V/µs

Doubler is set in Register 4, Bit DB26

REFIN A biased at AV DD/2;

ac coupling ensures AV DD/2 bias

LVDS and LVPECL compatible,

REFIN A/REFINB biased at 2.1 V;

ac coupling ensures 2.1 V bias

Single-ended reference programmed

Differential reference programmed

RSET = 5.1 kΩ

Fixed

0.5 V ≤ VCP1 ≤ VP − 0.5 V

0.5 V≤ VCP1 ≤ VP − 0.5V

VCP’ = 2.5 V

1.8 V output selected

IOL2 = 500 µA

See

Table 6

Voltages must equal AVDD

VP must equal VVCO

Each output divide by 2 consumes

6mA

enabling RFOUT B

RFOUT A± output stage is

programmable;

draws negligible extra current

−4 dBm setting

−1 dBm setting

2 dBm setting

5 dBm setting

Hardware power -down selected

Software power -down selected

输入频率

Single -Ended Mode

Differential Mode

Doubler Enabled

Input Sensitivity

Single -Ended Mode

Differential Mode

Input Capacitance

Single -Ended Mode

Differential Mode

Input Current

Phase Detector Frequency

CHARGE PUMP (CP)

Charge Pump Current, Sink/Source

High Value

Low Value

RSET Range

Current Matching

I CP vs. V CP

ICP vs. Temperature

LOGIC INPUTS

Input High Voltage

Input Low Voltage

Input Current

Input Capacitance

LOGIC OUTPUTS

Output High Voltage

Output High Current

Output Low Voltage

POWER SUPPLIES

Analog Power

Digital Power and RF Supply Voltage

Charge Pump and VCO Supply Voltage

Charge Pump Supply Power Current

DIDD + ADD3

Output Dividers

10

10

0.4

0.4

1.5

DVDD−

0.4

1.5

6.9

1.4

4.8

0.3

5.1

3

3

1.5

3.0

1.8

ICP

VINH

VINL

IINH /IINL

C IN

VOH

IOH

VOL

AVDD

DVDD,VRF

VP, VVCO

IP

3.15

4.75

Supply Current

RFOUT A±/RFOUT B Supply Current

IVCO

IRFOUTx±

Low Power Sleep Mode

RF OUTPUT CHARACTERISTICS

AVDD

5.0

8

62

6

36

70

to

16

30

42

55

500

1000

3

�

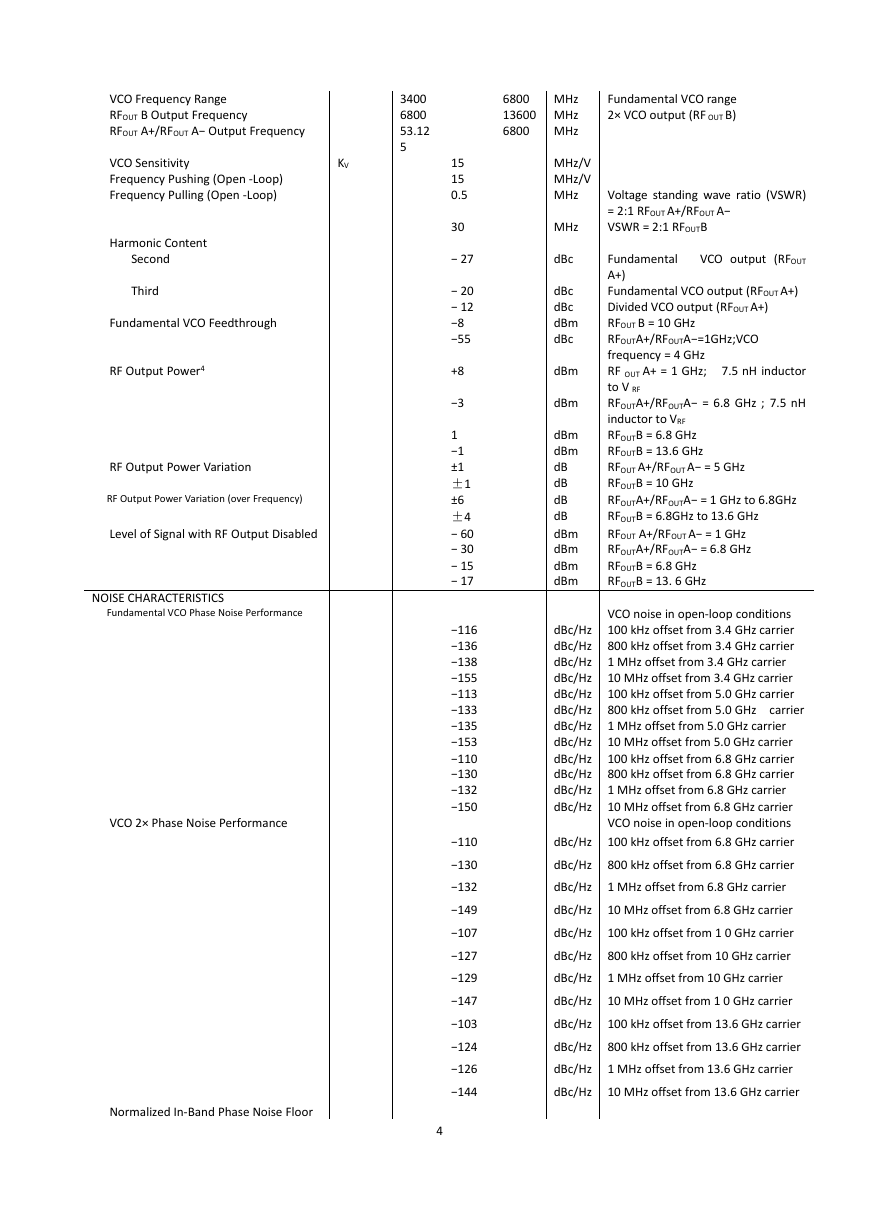

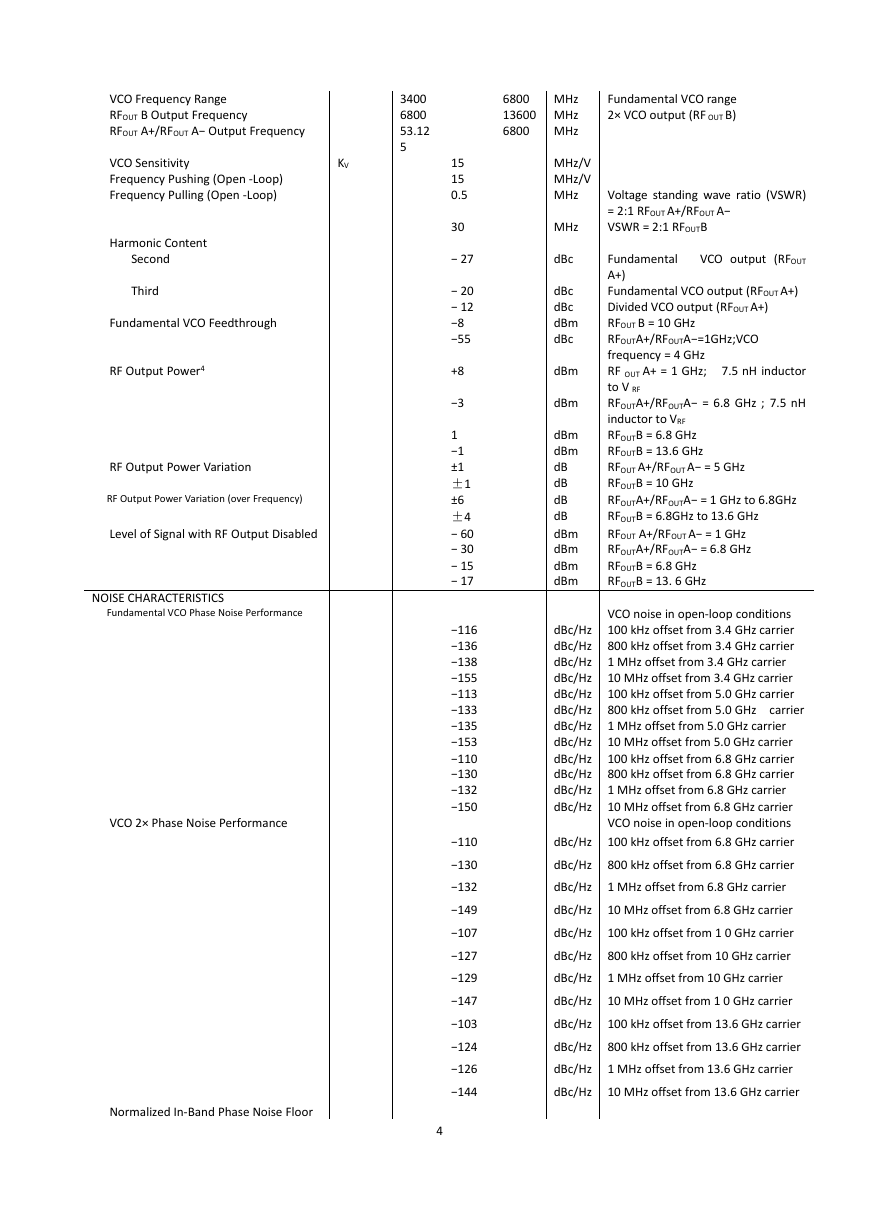

VCO Frequency Range

RFOUT B Output Frequency

RFOUT A+/RFOUT A− Output Frequency

VCO Sensitivity

Frequency Pushing (Open -Loop)

Frequency Pulling (Open -Loop)

KV

3400

6800

53.12

5

Harmonic Content

Second

Third

Fundamental VCO Feedthrough

RF Output Power4

RF Output Power Variation

RF Output Power Variation (over Frequency)

Level of Signal with RF Output Disabled

NOISE CHARACTERISTICS

Fundamental VCO Phase Noise Performance

VCO 2× Phase Noise Performance

Normalized In-Band Phase Noise Floor

4

6800

MHz

13600 MHz

MHz

6800

Fundamental VCO range

2× VCO output (RF OUT B)

15

15

0.5

30

− 27

− 20

− 12

−8

−55

+8

−3

1

−1

±1

±1

±6

±4

− 60

− 30

− 15

− 17

−116

−136

−138

−155

−113

−133

−135

−153

−110

−130

−132

−150

−110

−130

−132

−149

−107

−127

−129

−147

−103

−124

−126

−144

MHz/V

MHz/V

MHz

MHz

dBc

dBc

dBc

dBm

dBc

dBm

dBm

dBm

dBm

dB

dB

dB

dB

dBm

dBm

dBm

dBm

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Voltage standing wave ratio (VSWR)

= 2:1 RFOUT A+/RFOUT A−

VSWR = 2:1 RFOUTB

7.5 nH inductor

VCO output (RFOUT

Fundamental

A+)

Fundamental VCO output (RFOUT A+)

Divided VCO output (RFOUT A+)

RFOUT B = 10 GHz

RFOUTA+/RFOUTA−=1GHz;VCO

frequency = 4 GHz

RF OUT A+ = 1 GHz;

to V RF

RFOUTA+/RFOUTA− = 6.8 GHz ; 7.5 nH

inductor to VRF

RFOUTB = 6.8 GHz

RFOUTB = 13.6 GHz

RFOUT A+/RFOUT A− = 5 GHz

RFOUTB = 10 GHz

RFOUTA+/RFOUTA− = 1 GHz to 6.8GHz

RFOUTB = 6.8GHz to 13.6 GHz

RFOUT A+/RFOUT A− = 1 GHz

RFOUTA+/RFOUTA− = 6.8 GHz

RFOUTB = 6.8 GHz

RFOUTB = 13. 6 GHz

carrier

VCO noise in open-loop conditions

100 kHz offset from 3.4 GHz carrier

800 kHz offset from 3.4 GHz carrier

1 MHz offset from 3.4 GHz carrier

10 MHz offset from 3.4 GHz carrier

100 kHz offset from 5.0 GHz carrier

800 kHz offset from 5.0 GHz

1 MHz offset from 5.0 GHz carrier

10 MHz offset from 5.0 GHz carrier

100 kHz offset from 6.8 GHz carrier

800 kHz offset from 6.8 GHz carrier

1 MHz offset from 6.8 GHz carrier

10 MHz offset from 6.8 GHz carrier

VCO noise in open-loop conditions

100 kHz offset from 6.8 GHz carrier

800 kHz offset from 6.8 GHz carrier

1 MHz offset from 6.8 GHz carrier

10 MHz offset from 6.8 GHz carrier

100 kHz offset from 1 0 GHz carrier

800 kHz offset from 10 GHz carrier

1 MHz offset from 10 GHz carrier

10 MHz offset from 1 0 GHz carrier

100 kHz offset from 13.6 GHz carrier

800 kHz offset from 13.6 GHz carrier

1 MHz offset from 13.6 GHz carrier

10 MHz offset from 13.6 GHz carrier

�

Fractional Channel5

Integer Channel6

Normalized 1/f Noise, PN1_f7

Integrated RMS Jitter

Spurious Signals due to PFD Frequency

−221

−223

−116

150

−80

dBc/Hz

dBc/Hz

dBc/Hz

fs

dBc

10 kHz offset; normalized to 1 GHz

1、VCP is the voltage at the CPOUT pin.

2、IOL is the output low current.

3、TA = 25°C; AVDD = DVDD = VRF = 3.3 V; VVCO = VP = 5.0 V; 预分频器= 4/5; fREFIN = 122.88 MHz; fPFD = 61.44 MHz; and fRF = 1650 MHz.

For the nominal DIDD + AIDD (62 mA): DIDD = 15 mA (typical), AIDD (Pin 5) = 24 mA (typical), AIDD (Pin 16) = 23 mA (typical) .

4、使用 EV-ADF5355SD1Z 评估板将射频输出功率接到频谱分析仪中测量,将电路板和电缆损耗扣除。未使用的 RF 输出引

脚以 50Ω端接。

5、使用此值计算任何应用的相位噪声。要计算 VCO 输出端的带内相位噪声性能,请使用以下公式:-221 + 10log(fPFD)+ 20logN。

给出的值是针对小数通道的最低噪声模式。

6、使用此值计算任何应用的相位噪声。要计算 VCO 输出端的带内相位噪声性能,请使用以下公式:-223 + 10log(fPFD)+ 20logN。

给出的值是针对整数通道的最低噪声模式。

7、PLL 相位噪声由 1/f(闪烁)噪声加上归一化的 PLL 本底噪声组成。用 PN=P1_f+10log(10kHz/f)+20log(fRF/1GHz)给出了在

RF 频率(fRF)和频率偏移(f)下 1/f 噪声贡献的计算公式。归一化相位本底噪声和闪烁噪声均在 ADIsimPLL 设计工具中建模。

时序特性

除非另有说明,AVDD = DVDD =V RF = 3.3 V ± 5%, 4.75 V ≤ VP = VVCO ≤ 5.25 V, AGND = CPGND = AGNDVCO = SDGND

= AGNDRF = 0 V, RSET = 5.1 kΩ, dBm referred to 50 Ω, TA = TMIN to TMAX。.

表 2. 写时序

参数

fCLK

t1

t2

t3

t4

t5

t6

t7

写时序图

限值

50

10

5

5

10

10

5

20 (或 2/fPFD ,以更长的时间为准)

单位

MHz max

ns min

ns min

ns min

ns min

ns min

ns min

ns min

描述

串行外设接口 CLK 频率

LE 设置时间

DATA 到 CLK 设置时间

DATA 到 CLK 保持时间

CLK 高电平持续时间

CLK 低电平持续时间

CLK 到 LE 设置时间

LE 脉冲宽度

5

�

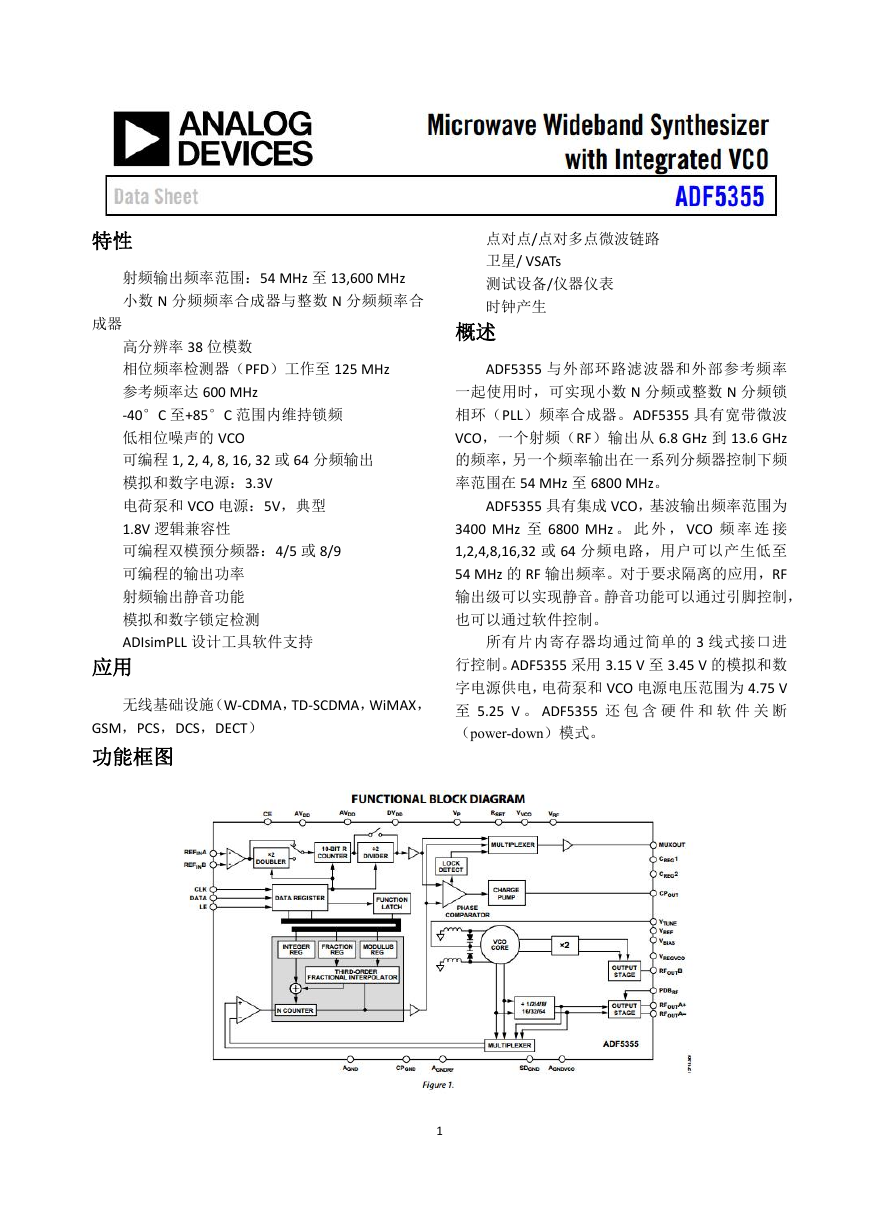

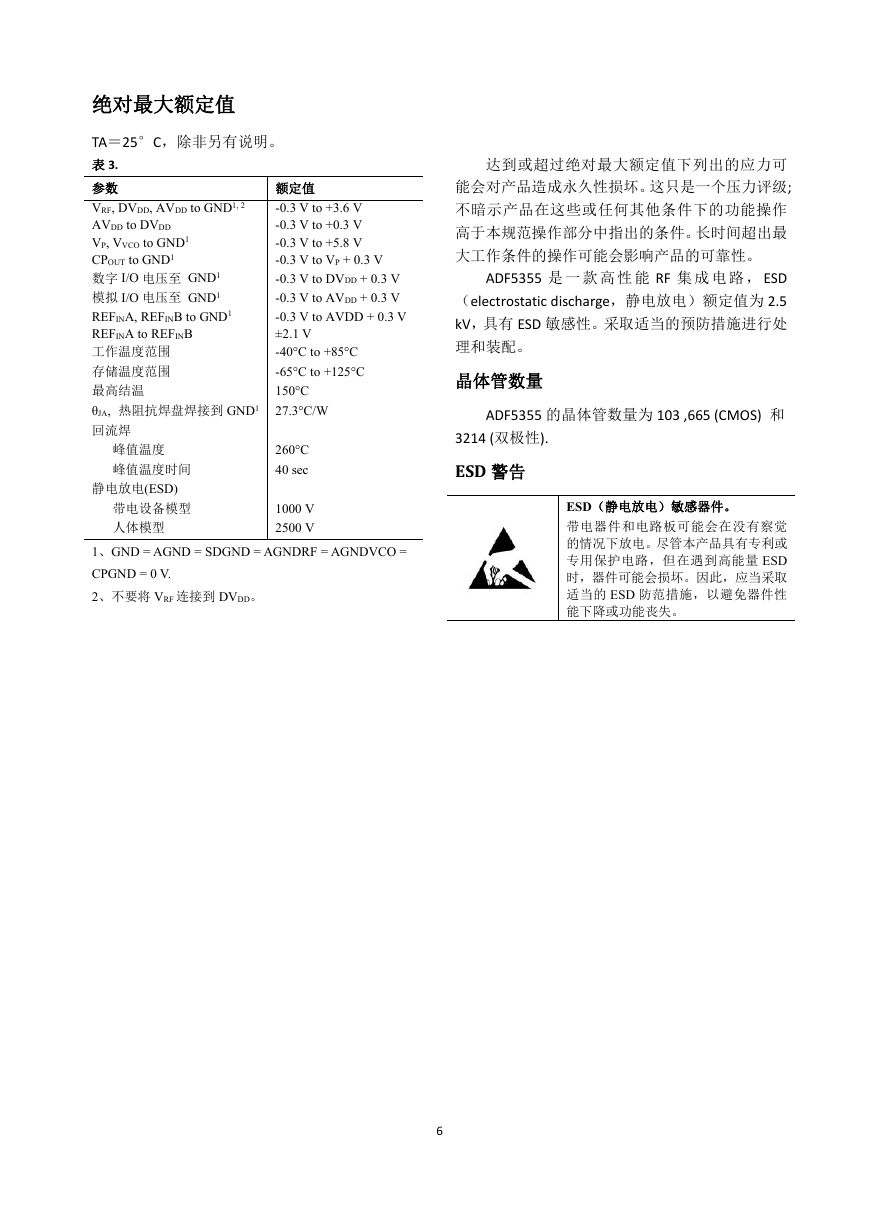

绝对最大额定值

TA=25°C,除非另有说明。

表 3.

参数

VRF, DVDD, AVDD to GND1, 2

AVDD to DVDD

VP, VVCO to GND1

CPOUT to GND1

数字 I/O 电压至 GND1

模拟 I/O 电压至 GND1

REFINA, REFINB to GND1

REFINA to REFINB

工作温度范围

存储温度范围

最高结温

θJA, 热阻抗焊盘焊接到 GND1

回流焊

额定值

-0.3 V to +3.6 V

-0.3 V to +0.3 V

-0.3 V to +5.8 V

-0.3 V to VP + 0.3 V

-0.3 V to DVDD + 0.3 V

-0.3 V to AVDD + 0.3 V

-0.3 V to AVDD + 0.3 V

±2.1 V

-40°C to +85°C

-65°C to +125°C

150°C

27.3°C/W

峰值温度

峰值温度时间

静电放电(ESD)

带电设备模型

人体模型

260°C

40 sec

1000 V

2500 V

1、GND = AGND = SDGND = AGNDRF = AGNDVCO =

CPGND = 0 V.

2、不要将 VRF 连接到 DVDD。

达到或超过绝对最大额定值下列出的应力可

能会对产品造成永久性损坏。这只是一个压力评级;

不暗示产品在这些或任何其他条件下的功能操作

高于本规范操作部分中指出的条件。长时间超出最

大工作条件的操作可能会影响产品的可靠性。

ADF5355 是 一 款 高 性 能 RF 集 成 电 路 , ESD

(electrostatic discharge,静电放电)额定值为 2.5

kV,具有 ESD 敏感性。采取适当的预防措施进行处

理和装配。

晶体管数量

ADF5355 的晶体管数量为 103 ,665 (CMOS) 和

3214 (双极性).

ESD 警告

ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉

的情况下放电。尽管本产品具有专利或

专用保护电路,但在遇到高能量 ESD

时,器件可能会损坏。因此,应当采取

适当的 ESD 防范措施,以避免器件性

能下降或功能丧失。

6

�

引脚配置和功能描述

表 4. 引脚功能描述

引脚编号 引脚名称 描述

1

2

CLK

DATA

3

4

LE

CE

5,16

AVDD

6

7

8

9

10

11

12

13,15

14

17

18,21

19

VP

CPOUT

CPGND

AGND

VRF

RFOUTA+

RFOUTA-

AGNDRF

RFOUTB

VVCO

AGNDVCO

VREGVCO

串行时钟输入。数据在 CLK 上升沿逐个输入 32 位移位寄存器。此输入为高阻抗 CMOS 输入。

串行数据输入。串行数据首先加载最高有效位(MSB),其中四位最低位(LSB)作为控制位。

此输入为高阻抗 CMOS 输入。

加载使能,CMOS 输入。当 LE 变为高电平时,存储在移位寄存器中的数据被加载到由四位

LSB 选择的寄存器中。

芯片使能。此引脚上的逻辑低电平将关断器件,并使电荷泵进入三态模式。此引脚上的逻辑

高电平(电平等于 DVDD)将使器件上电,具体取决于掉电位(power-down bit)的状态。除

非移除电源电压,否则将保留寄存器中内容。

模拟电源。该引脚的电压范围为 3.15 V 至 3.45 V。连接到模拟地层的去耦电容应尽可能靠近

此引脚。AVDD 必须与 DVDD 具有相同的值。

电荷泵电源。VP 必须与 VVCO 具有相同的值。连接到接地层的去耦电容应尽可能靠近此引脚。

电荷泵输出。使能时,此输出将为外部环路滤波器提供±ICP。环路滤波器的输出连接到 VTUNE

以驱动内部 VCO。

电荷泵接地。这是 CPOUT 的接地回路引脚。

模拟地。这是 AVDD 的接地回路引脚。

射频输出电源。连接到模拟地层的去耦电容应尽可能靠近此引脚。VRF 必须与 AVDD 具有相同

的值。不要将 VRF 连接到 DVDD。

VCO 输出。输出电平是可编程的。可以使用 VCO 基波输出或分频后输出。如果寄存器 6 中设

置为 RFOUTA 禁用,或通过 PDBRF 引脚禁用,则该引脚可以悬空。

互补 VCO 输出。输出电平是可编程的。可以使用 VCO 基波输出或分频后输出。如果寄存器 6

中禁止 RFOUTA 或通过 PDBRF 引脚禁用,则该引脚可以悬空。

射频输出级接地。RF 输出级的接地返回引脚。

辅助 VCO 输出。该引脚提供 2×VCO 输出。

VCO 的电源。此引脚上的电压范围为 4.75 V 至 5.25 V。至在模拟地层的去耦电容应尽可能靠

近此引脚。为获得最佳性能,此电源必须干净且噪音低。

VCO 地。VCO 的接地回路引脚。

VCO 补偿节点。将去耦电容放置在接地层上,尽可能靠近此引脚。将此引脚直接连接到 VVCO。

7

�

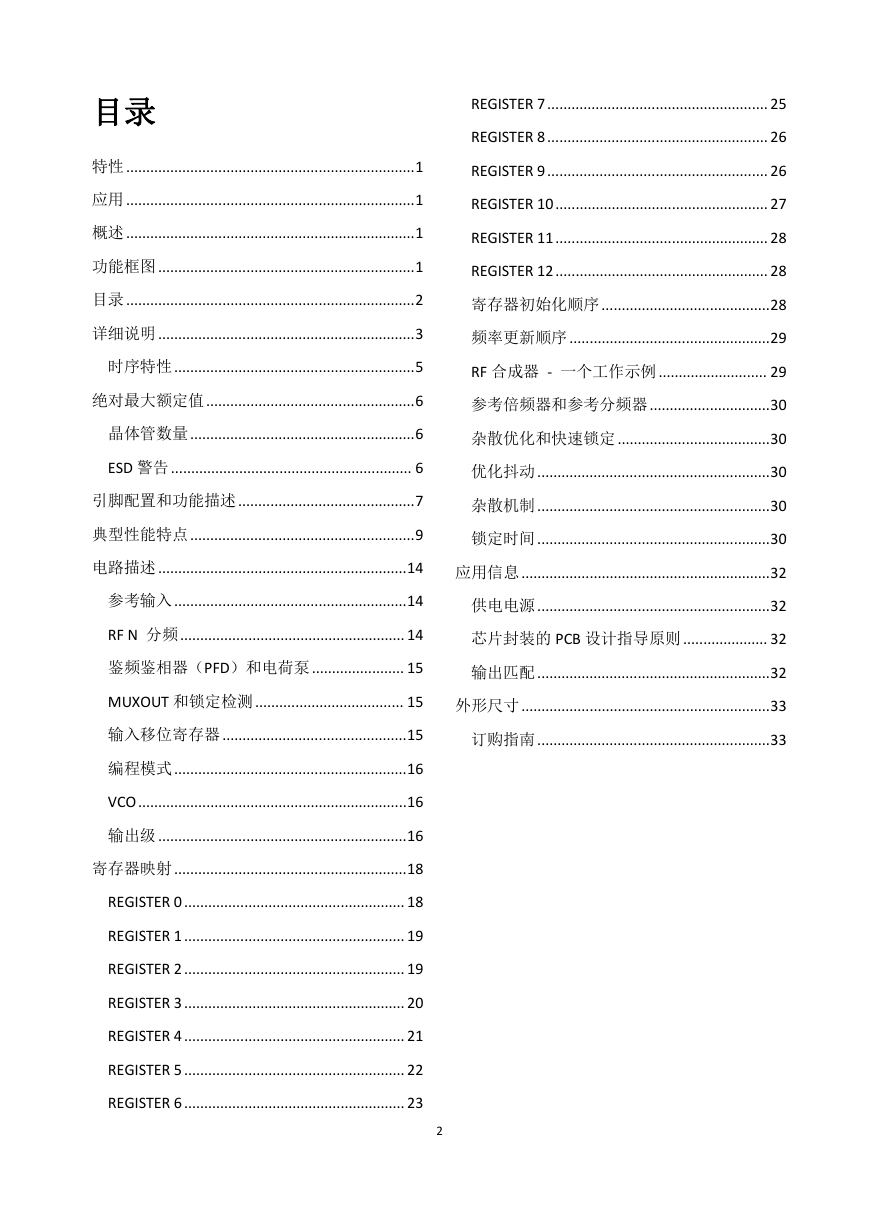

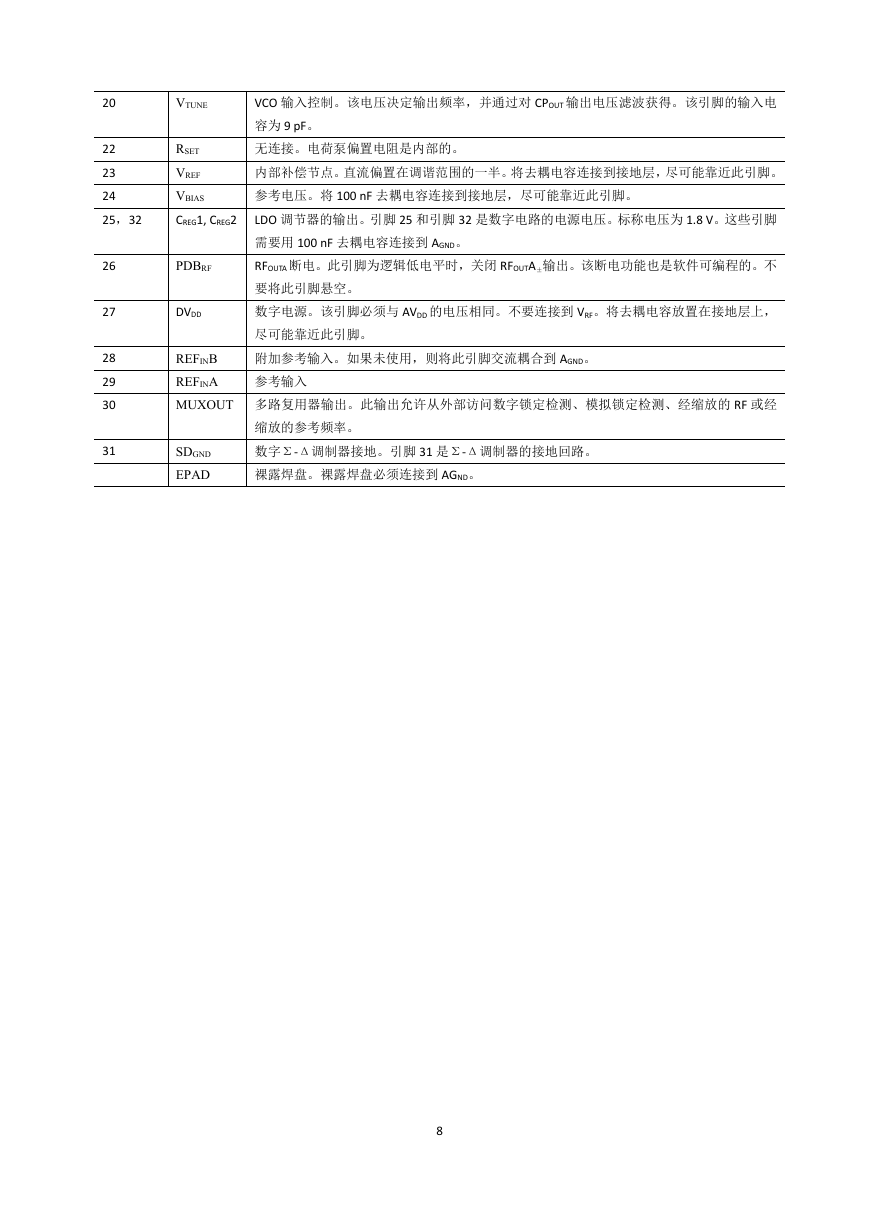

20

VTUNE

22

23

24

25,32

RSET

VREF

VBIAS

CREG1, CREG2

PDBRF

DVDD

26

27

28

29

30

31

VCO 输入控制。该电压决定输出频率,并通过对 CPOUT 输出电压滤波获得。该引脚的输入电

容为 9 pF。

无连接。电荷泵偏置电阻是内部的。

内部补偿节点。直流偏置在调谐范围的一半。将去耦电容连接到接地层,尽可能靠近此引脚。

参考电压。将 100 nF 去耦电容连接到接地层,尽可能靠近此引脚。

LDO 调节器的输出。引脚 25 和引脚 32 是数字电路的电源电压。标称电压为 1.8 V。这些引脚

需要用 100 nF 去耦电容连接到 AGND。

RFOUTA 断电。此引脚为逻辑低电平时,关闭 RFOUTA±输出。该断电功能也是软件可编程的。不

要将此引脚悬空。

数字电源。该引脚必须与 AVDD 的电压相同。不要连接到 VRF。将去耦电容放置在接地层上,

尽可能靠近此引脚。

附加参考输入。如果未使用,则将此引脚交流耦合到 AGND。

参考输入

REFINB

REFINA

MUXOUT 多路复用器输出。此输出允许从外部访问数字锁定检测、模拟锁定检测、经缩放的 RF 或经

SDGND

EPAD

缩放的参考频率。

数字Σ-Δ调制器接地。引脚 31 是Σ-Δ调制器的接地回路。

裸露焊盘。裸露焊盘必须连接到 AGND。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc