Virtex-5 Libraries Guide for

Schematic Designs

ISE 8.2.2

R

�

R

R

Xilinx is disclosing this Document and Intellectual Property (hereinafter “the Design”) to you for use in the development of designs to operate

on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design be copied, reproduced, distributed, republished,

downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical,

photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design violate copyright laws,

trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents,

copyrights, or any rights of others. You are responsible for obtaining any rights you require for your use or implementation of the Design.

Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no

obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the

accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED “AS IS” WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS

WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR

ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER

EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES,

INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU

HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION

WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE

AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF

ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE

THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-

safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or

weapons systems (“High-Risk Applications”). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk

Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

Copyright © 1995-2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks

of Xilinx, Inc. PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners.

2

www.xilinx.com

Virtex-5 Libraries Guide for Schematic Designs

ISE 8.2.2

�

R

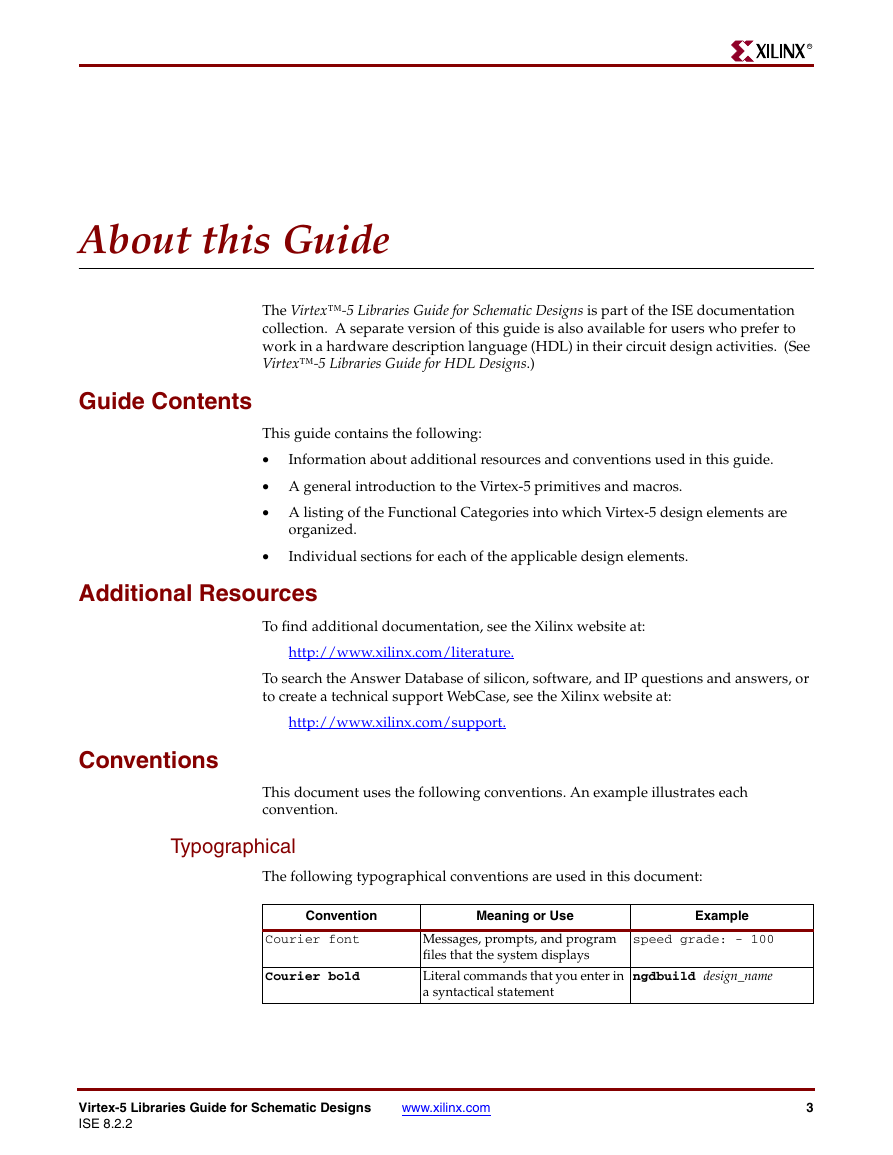

About this Guide

The Virtex™-5 Libraries Guide for Schematic Designs is part of the ISE documentation

collection. A separate version of this guide is also available for users who prefer to

work in a hardware description language (HDL) in their circuit design activities. (See

Virtex™-5 Libraries Guide for HDL Designs.)

Guide Contents

Information about additional resources and conventions used in this guide.

This guide contains the following:

•

• A general introduction to the Virtex-5 primitives and macros.

• A listing of the Functional Categories into which Virtex-5 design elements are

organized.

Individual sections for each of the applicable design elements.

•

Additional Resources

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or

to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

Conventions

This document uses the following conventions. An example illustrates each

convention.

Typographical

The following typographical conventions are used in this document:

Convention

Meaning or Use

Example

Courier font

Courier bold

Messages, prompts, and program

files that the system displays

Literal commands that you enter in

a syntactical statement

speed grade: - 100

ngdbuild design_name

Virtex-5 Libraries Guide for Schematic Designs

ISE 8.2.2

www.xilinx.com

3

�

R

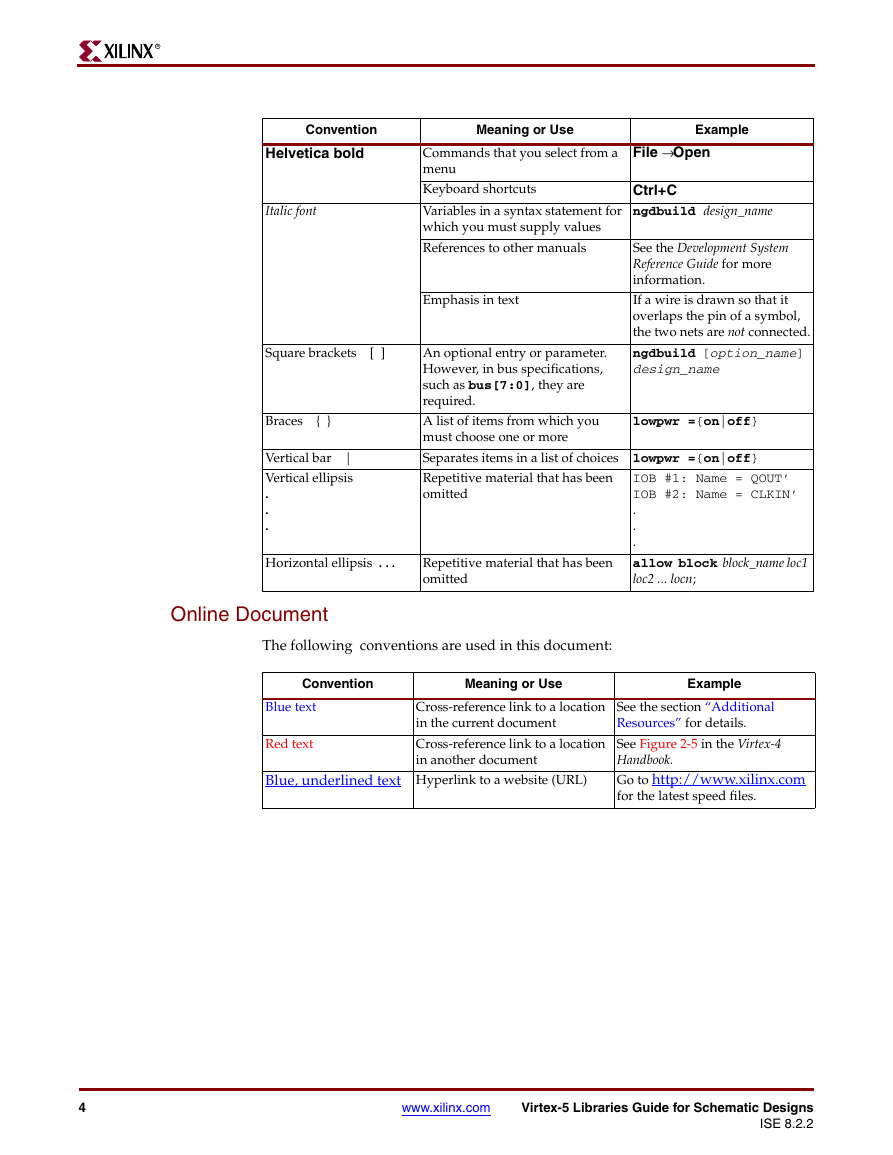

Convention

Meaning or Use

Example

Helvetica bold

Italic font

Square brackets [ ]

Braces { }

Vertical bar |

Vertical ellipsis

.

.

.

Commands that you select from a

menu

Keyboard shortcuts

Variables in a syntax statement for

which you must supply values

References to other manuals

Emphasis in text

File → Open

Ctrl+C

ngdbuild design_name

See the Development System

Reference Guide for more

information.

If a wire is drawn so that it

overlaps the pin of a symbol,

the two nets are not connected.

ngdbuild [option_name]

design_name

An optional entry or parameter.

However, in bus specifications,

such as bus[7:0], they are

required.

A list of items from which you

must choose one or more

Separates items in a list of choices lowpwr ={on|off}

Repetitive material that has been

omitted

lowpwr ={on|off}

IOB #1: Name = QOUT’

IOB #2: Name = CLKIN’

.

.

.

allow block block_name loc1

loc2 ... locn;

Horizontal ellipsis . . .

Repetitive material that has been

omitted

Online Document

The following conventions are used in this document:

Convention

Meaning or Use

Example

Blue text

Red text

Cross-reference link to a location

in the current document

Cross-reference link to a location

in another document

Blue, underlined text Hyperlink to a website (URL)

See the section “Additional

Resources” for details.

See Figure 2-5 in the Virtex-4

Handbook.

Go to http://www.xilinx.com

for the latest speed files.

4

www.xilinx.com

Virtex-5 Libraries Guide for Schematic Designs

ISE 8.2.2

�

Introduction

R

Xilinx maintains software libraries containing hundreds of functional design elements

(primitives and macros) for various device architectures. New functional elements are

assembled with each release of development system software. The catalog of design

elements is known as the Xilinx Unified Libraries. Elements in these libraries are

common to multiple Xilinx device architectures. This “unified” approach means that

you can use your circuit design created with “unified” library elements across many

Xilinx device architectures that recognize the element you are using.

Elements that exist in multiple architectures look and function the same, but their

implementations might differ to make them more efficient for a particular

architecture. A separate library still exists for each architecture and several hundred

design elements (primitives and macros) are available across multiple device

architectures, providing a common base for programmable logic designs.

Starting in 2004, libraries guides began to be published only for the latest available

architectures. This architecture-specific approach is also published in a two-volume

set: one for designers who prefer to use hardware description language (HDL), and

one for those who prefer to use schematics.

The Virtex-5 Libraries Guide describes the primitive and macro logic elements

supported under the Virtex-5 architecture. Common logic functions can be

implemented with these elements and more complex functions can be built by

combining macros and primitives.

Functional Categories

The functional categories list the available design elements in each category, along

with a brief description of each element supported under each Xilinx architecture.

Attributes and Constraints

The terms attribute and constraint have been used interchangeably by some in the

engineering community, while others ascribe different meanings to these terms. In

addition, language constructs use the terms attribute and directive in similar yet

different senses. For the purpose of clarification, the following distinction can be

drawn between these terms.

An attribute is a property associated with a device architecture primitive that affects

an instantiated primitive’s functionality or implementation. Attributes are typically

conveyed as follows:

•

•

In VHDL, by means of generic maps.

In Verilog, by means of defparams or inline parameter passing during the

instantiation process.

Constraints impose user-defined parameters on the operation of ISE tools. There are

two types of constraints:

•

Synthesis Constraints direct the synthesis tool optimization technique for a

particular design or piece of HDL code. They are either embedded within the

VHDL or Verilog code, or within a separate synthesis constraints file.

Implementation Constraints are instructions given to the FPGA implementation

tools to direct the mapping, placement, timing, or other guidelines for the

•

Virtex-5 Libraries Guide for Schematic Designs

ISE 8.2.2

www.xilinx.com

5

�

R

implementation tools to follow while processing an FPGA design.

Implementation constraints are generally placed in the UCF file, but can exist in

the HDL code, or in a synthesis constraints file.

Attributes are identified with the components to which they apply in the libraries

guide for those components. Constraints are documented in the Xilinx Constraints

Guide. Both resources are available from the Xilinx Software Manuals collection.

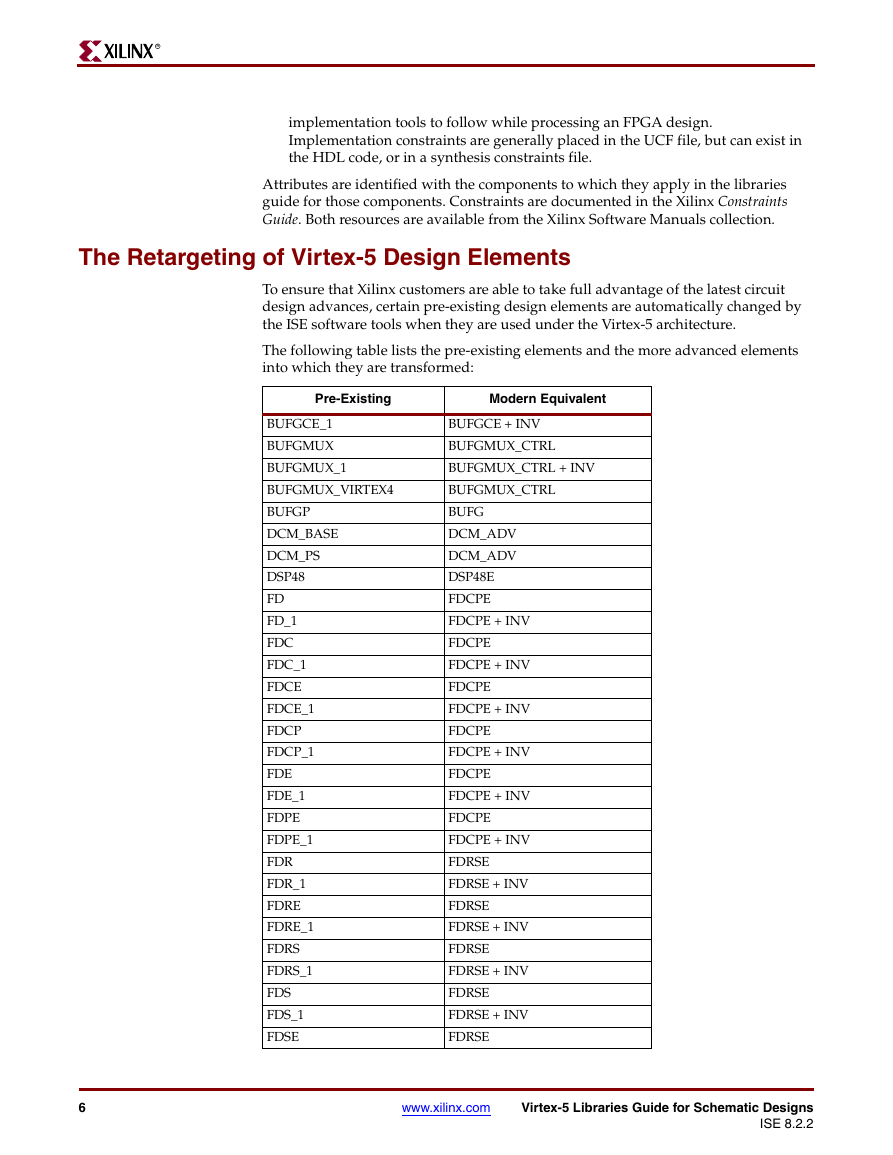

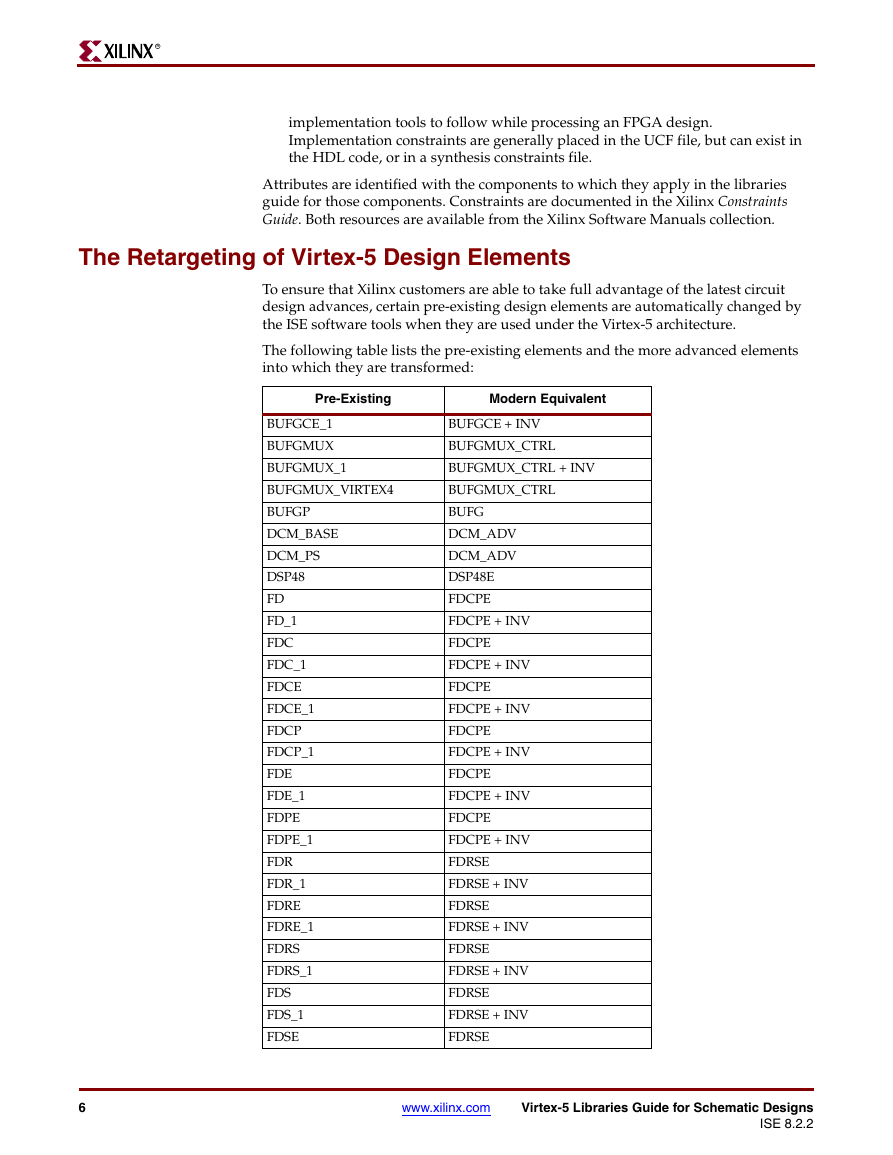

The Retargeting of Virtex-5 Design Elements

To ensure that Xilinx customers are able to take full advantage of the latest circuit

design advances, certain pre-existing design elements are automatically changed by

the ISE software tools when they are used under the Virtex-5 architecture.

The following table lists the pre-existing elements and the more advanced elements

into which they are transformed:

Pre-Existing

Modern Equivalent

BUFGCE_1

BUFGMUX

BUFGMUX_1

BUFGMUX_VIRTEX4

BUFGP

DCM_BASE

DCM_PS

DSP48

FD

FD_1

FDC

FDC_1

FDCE

FDCE_1

FDCP

FDCP_1

FDE

FDE_1

FDPE

FDPE_1

FDR

FDR_1

FDRE

FDRE_1

FDRS

FDRS_1

FDS

FDS_1

FDSE

BUFGCE + INV

BUFGMUX_CTRL

BUFGMUX_CTRL + INV

BUFGMUX_CTRL

BUFG

DCM_ADV

DCM_ADV

DSP48E

FDCPE

FDCPE + INV

FDCPE

FDCPE + INV

FDCPE

FDCPE + INV

FDCPE

FDCPE + INV

FDCPE

FDCPE + INV

FDCPE

FDCPE + INV

FDRSE

FDRSE + INV

FDRSE

FDRSE + INV

FDRSE

FDRSE + INV

FDRSE

FDRSE + INV

FDRSE

6

www.xilinx.com

Virtex-5 Libraries Guide for Schematic Designs

ISE 8.2.2

�

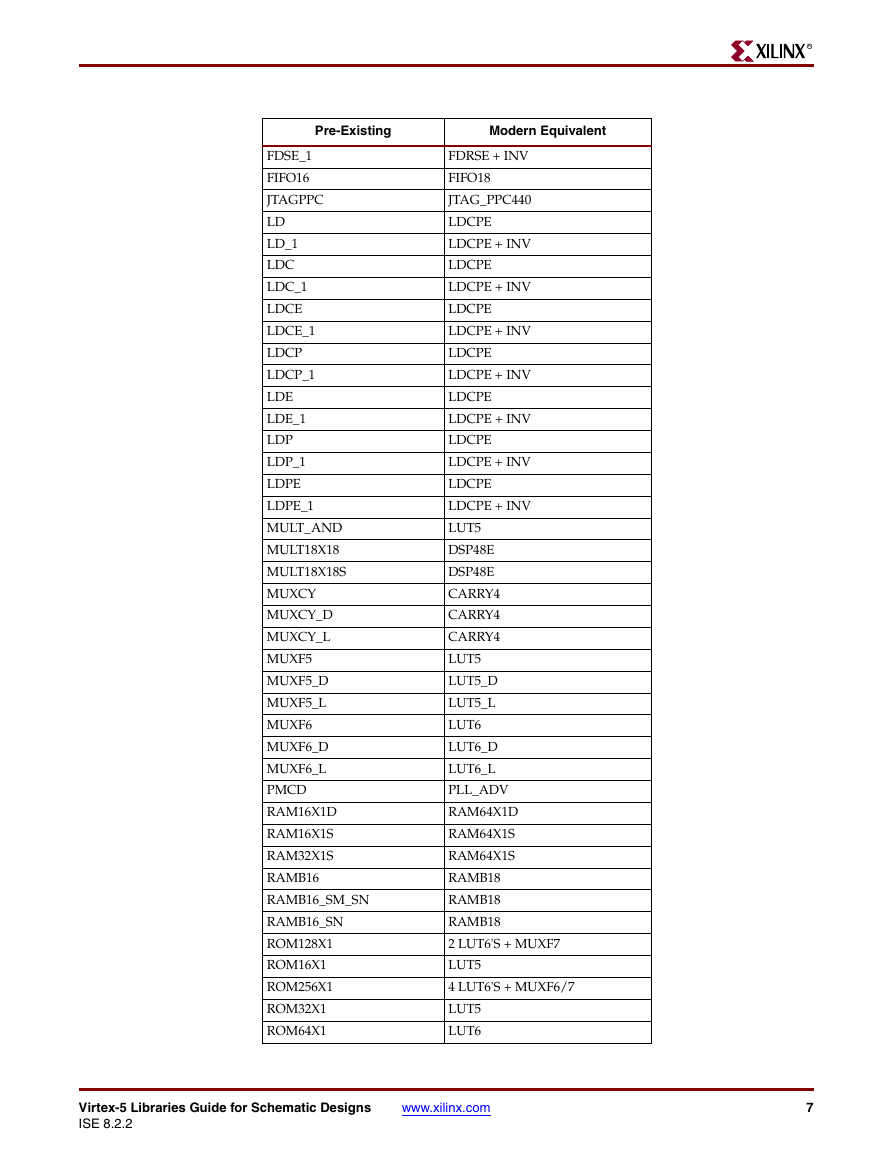

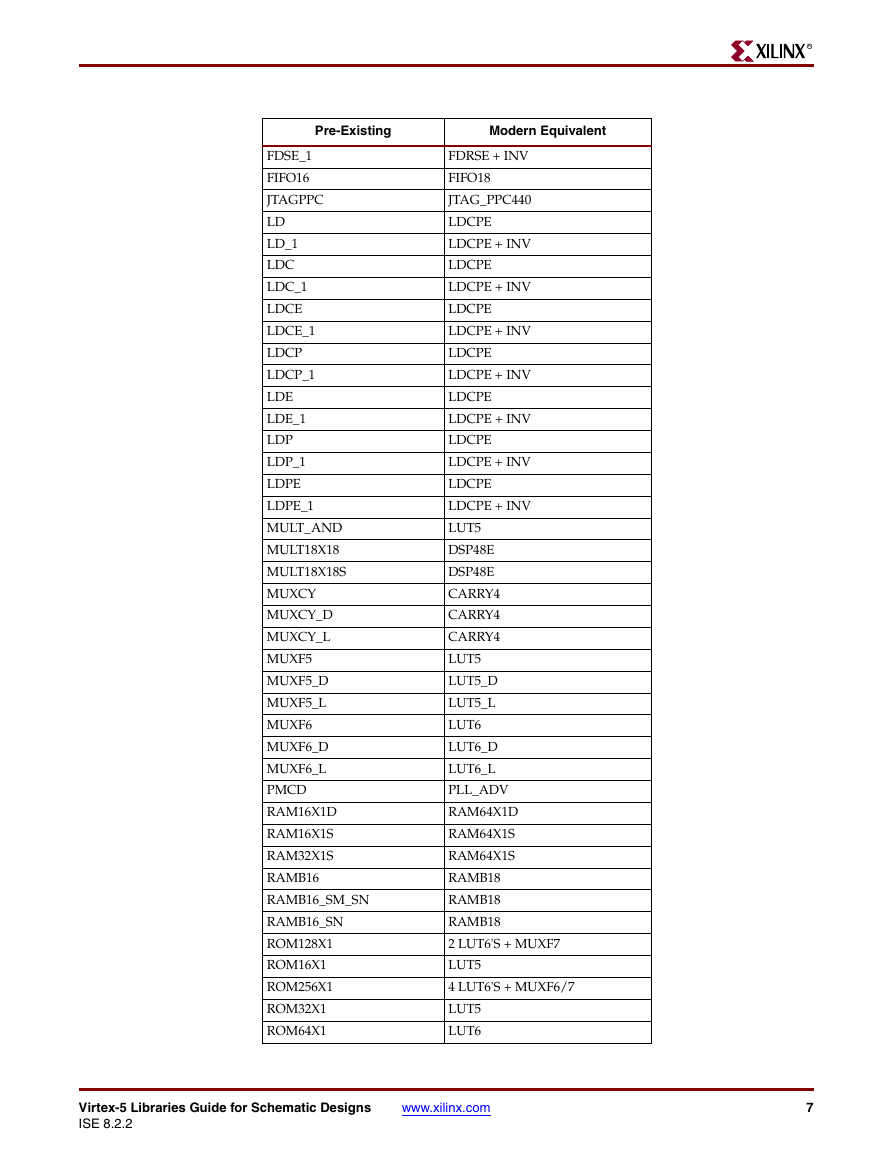

Pre-Existing

Modern Equivalent

FDSE_1

FIFO16

JTAGPPC

LD

LD_1

LDC

LDC_1

LDCE

LDCE_1

LDCP

LDCP_1

LDE

LDE_1

LDP

LDP_1

LDPE

LDPE_1

MULT_AND

MULT18X18

MULT18X18S

MUXCY

MUXCY_D

MUXCY_L

MUXF5

MUXF5_D

MUXF5_L

MUXF6

MUXF6_D

MUXF6_L

PMCD

RAM16X1D

RAM16X1S

RAM32X1S

RAMB16

RAMB16_SM_SN

RAMB16_SN

ROM128X1

ROM16X1

ROM256X1

ROM32X1

ROM64X1

FDRSE + INV

FIFO18

JTAG_PPC440

LDCPE

LDCPE + INV

LDCPE

LDCPE + INV

LDCPE

LDCPE + INV

LDCPE

LDCPE + INV

LDCPE

LDCPE + INV

LDCPE

LDCPE + INV

LDCPE

LDCPE + INV

LUT5

DSP48E

DSP48E

CARRY4

CARRY4

CARRY4

LUT5

LUT5_D

LUT5_L

LUT6

LUT6_D

LUT6_L

PLL_ADV

RAM64X1D

RAM64X1S

RAM64X1S

RAMB18

RAMB18

RAMB18

2 LUT6'S + MUXF7

LUT5

4 LUT6'S + MUXF6/7

LUT5

LUT6

Virtex-5 Libraries Guide for Schematic Designs

ISE 8.2.2

www.xilinx.com

R

7

�

R

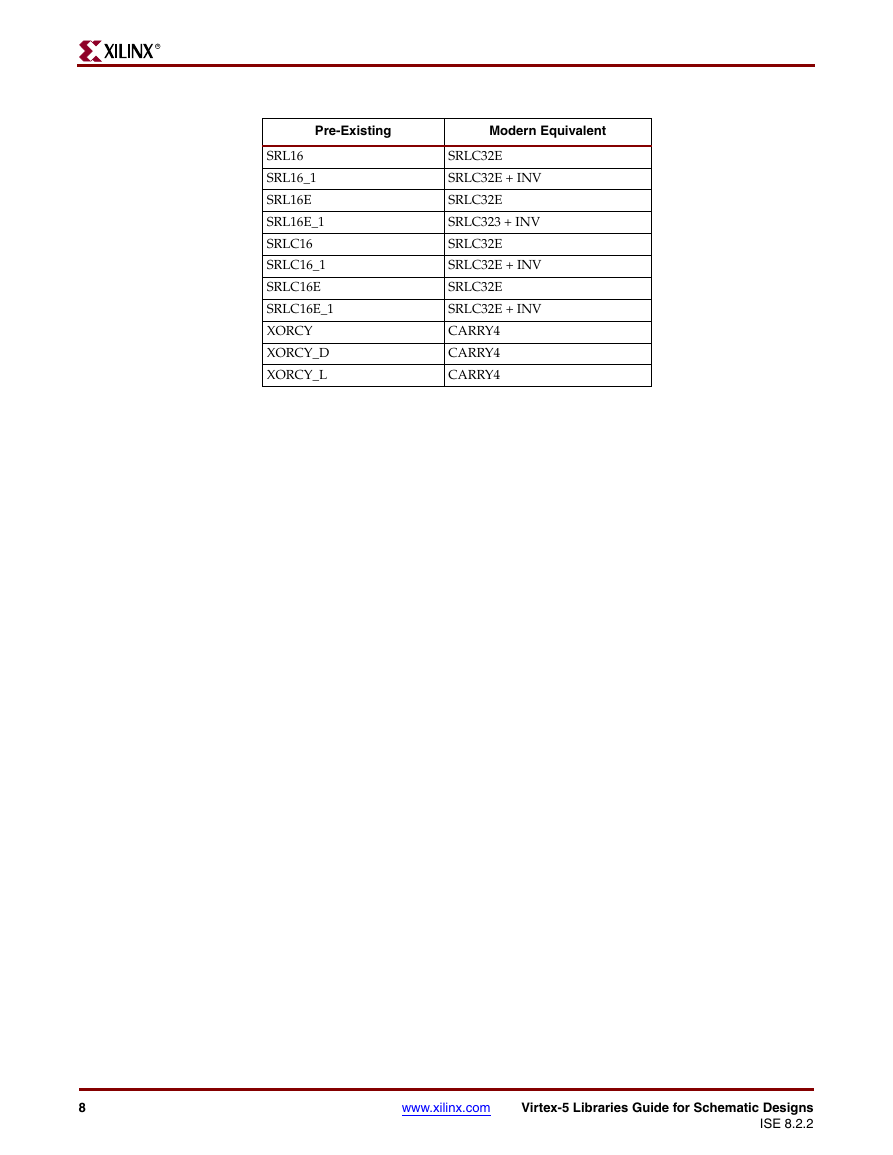

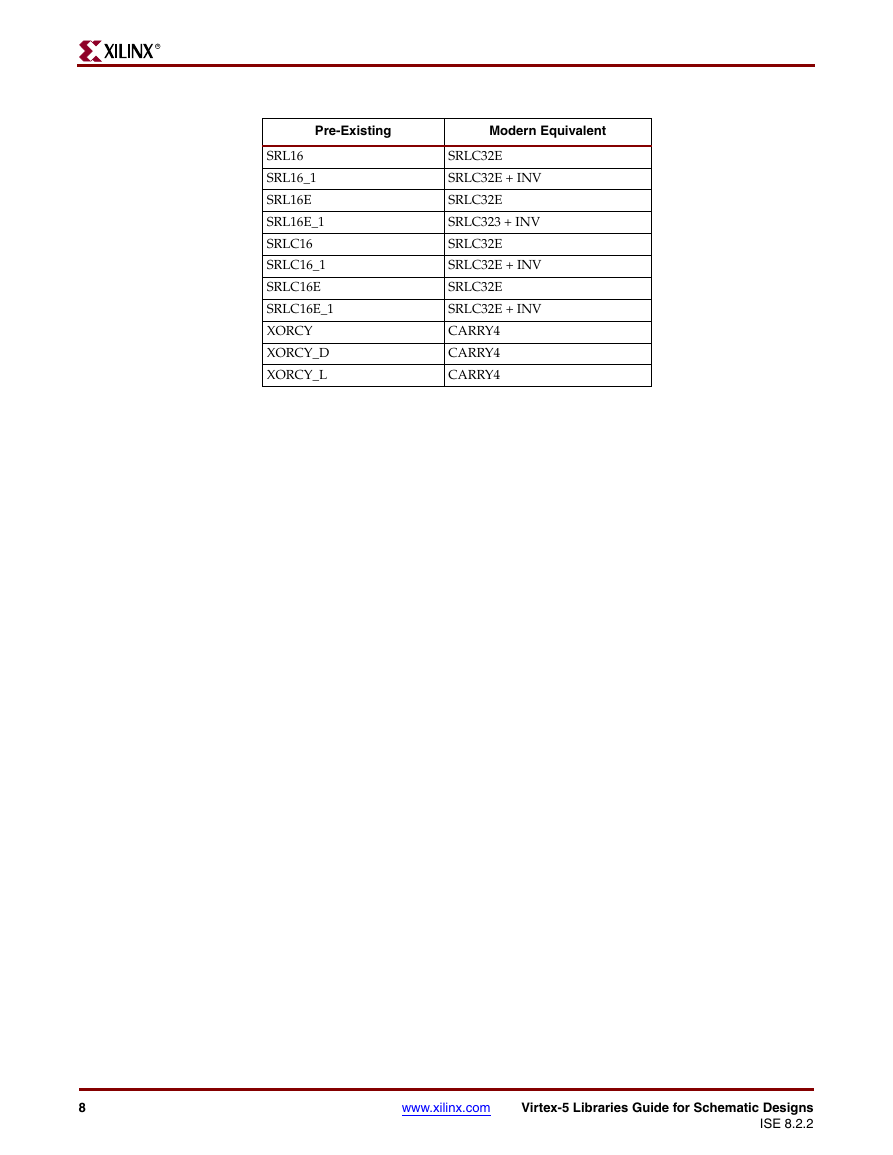

Pre-Existing

Modern Equivalent

SRL16

SRL16_1

SRL16E

SRL16E_1

SRLC16

SRLC16_1

SRLC16E

SRLC16E_1

XORCY

XORCY_D

XORCY_L

SRLC32E

SRLC32E + INV

SRLC32E

SRLC323 + INV

SRLC32E

SRLC32E + INV

SRLC32E

SRLC32E + INV

CARRY4

CARRY4

CARRY4

8

www.xilinx.com

Virtex-5 Libraries Guide for Schematic Designs

ISE 8.2.2

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc