题目名称:数字钟的设计与制作

姓

班

学

日

名: 王忻澄

级: 电气 062

号: 200633495229

期: 2009-1-16

嘉兴学院电气工程系

�

数字钟的设计与制作

一.指标要求:

1.显示时、分、秒。.采用 24 小时制。

2.具有校时功能,可以对小时和分单独校时,对分校时的时候,停止分向小时进位。校

时时钟源可以手动输入或借用电路中的时钟。

3.为了保证计时准确、稳定,由晶体振荡器提供标准时间的基准信号。

二.设计计算:

总体方案设计:

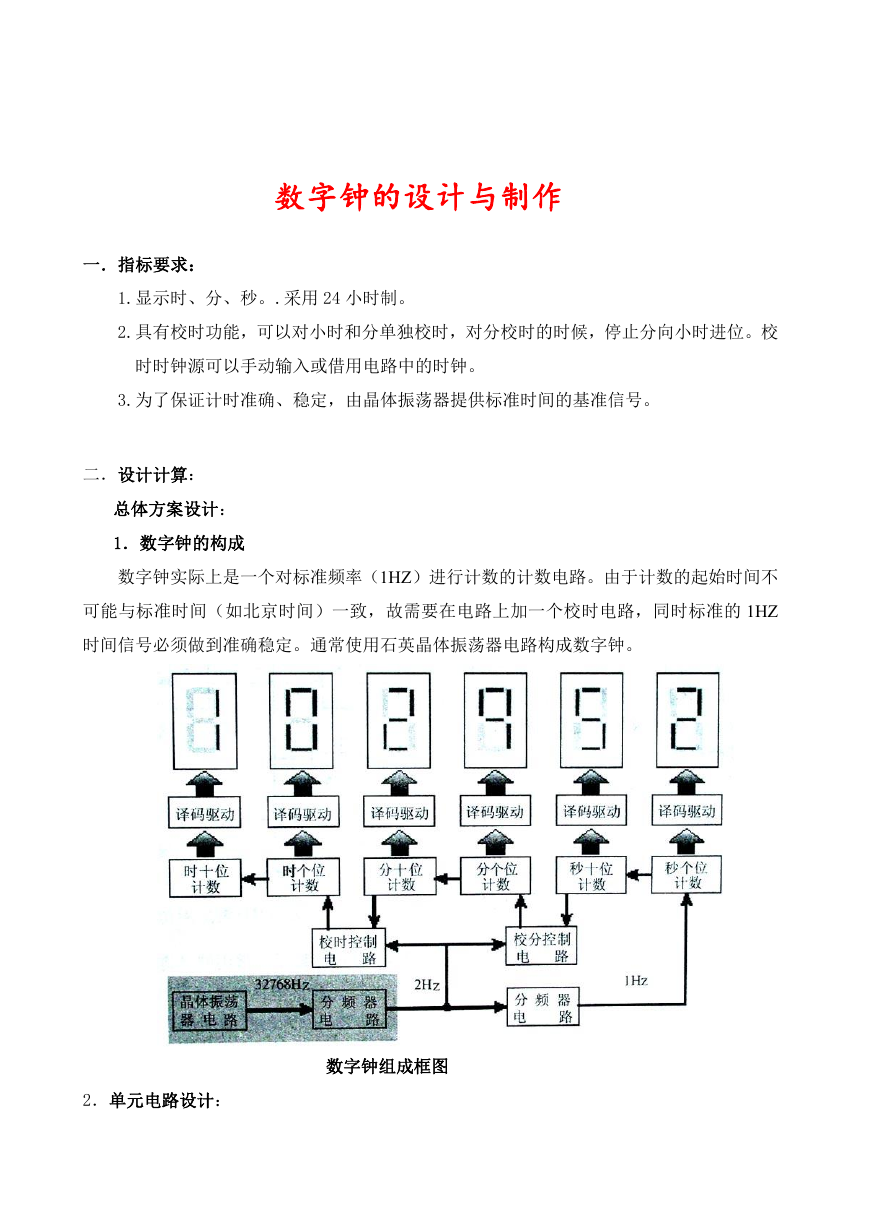

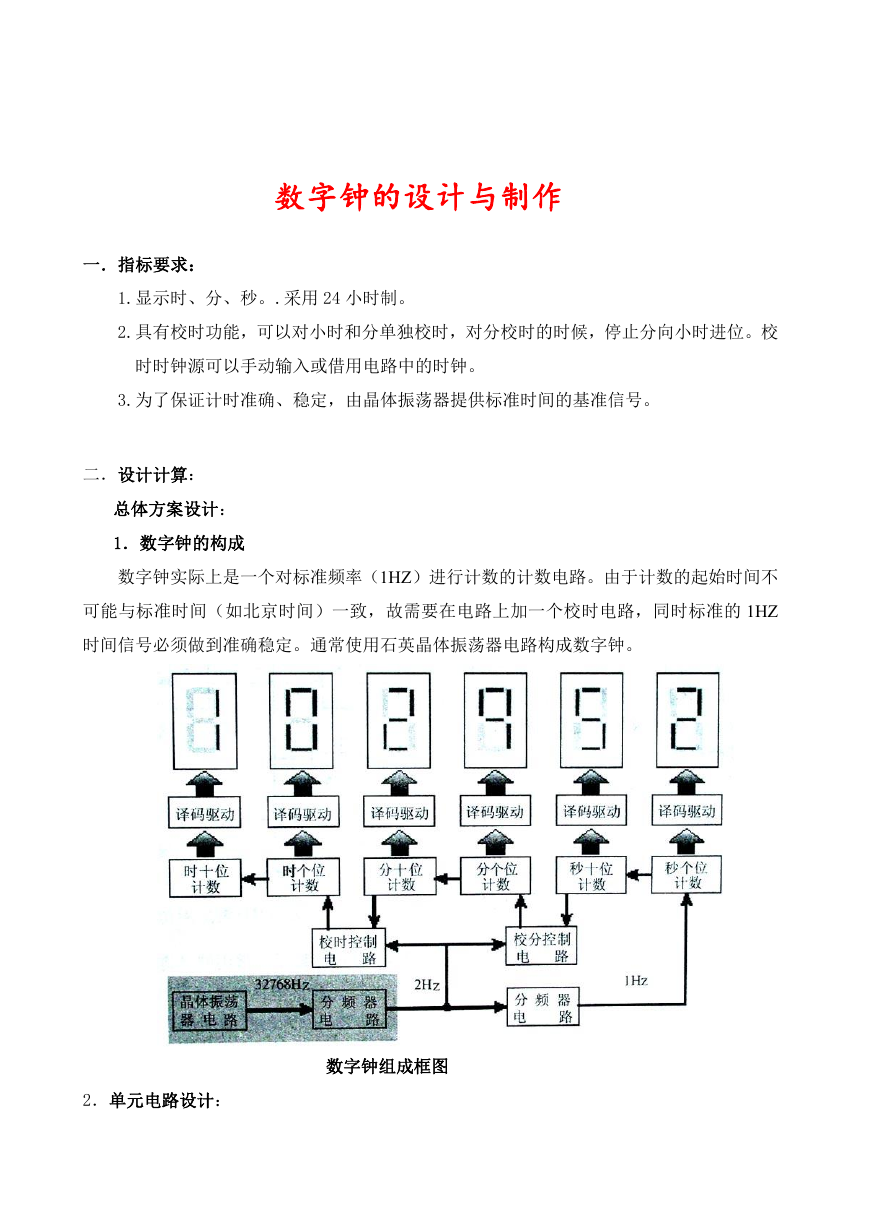

1.数字钟的构成

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不

可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的 1HZ

时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。

2.单元电路设计:

数字钟组成框图

�

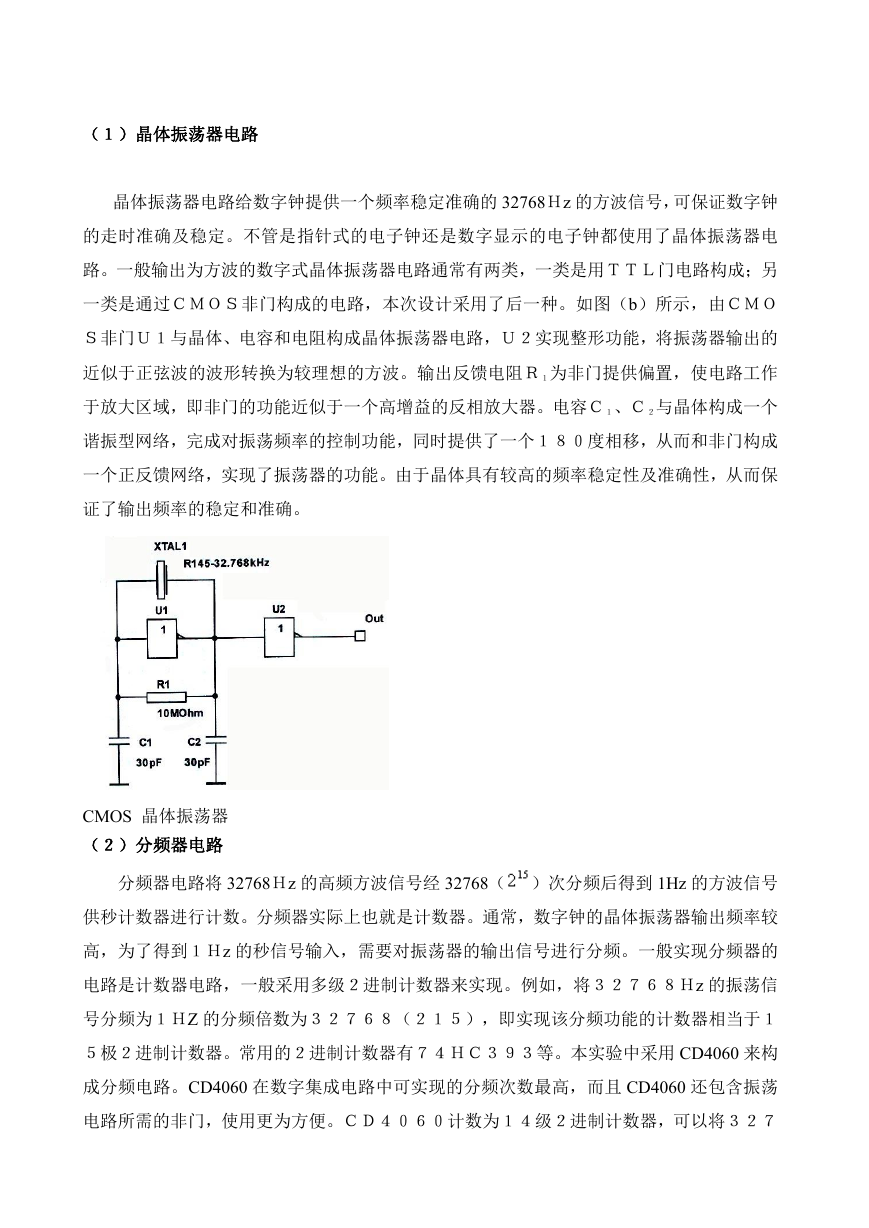

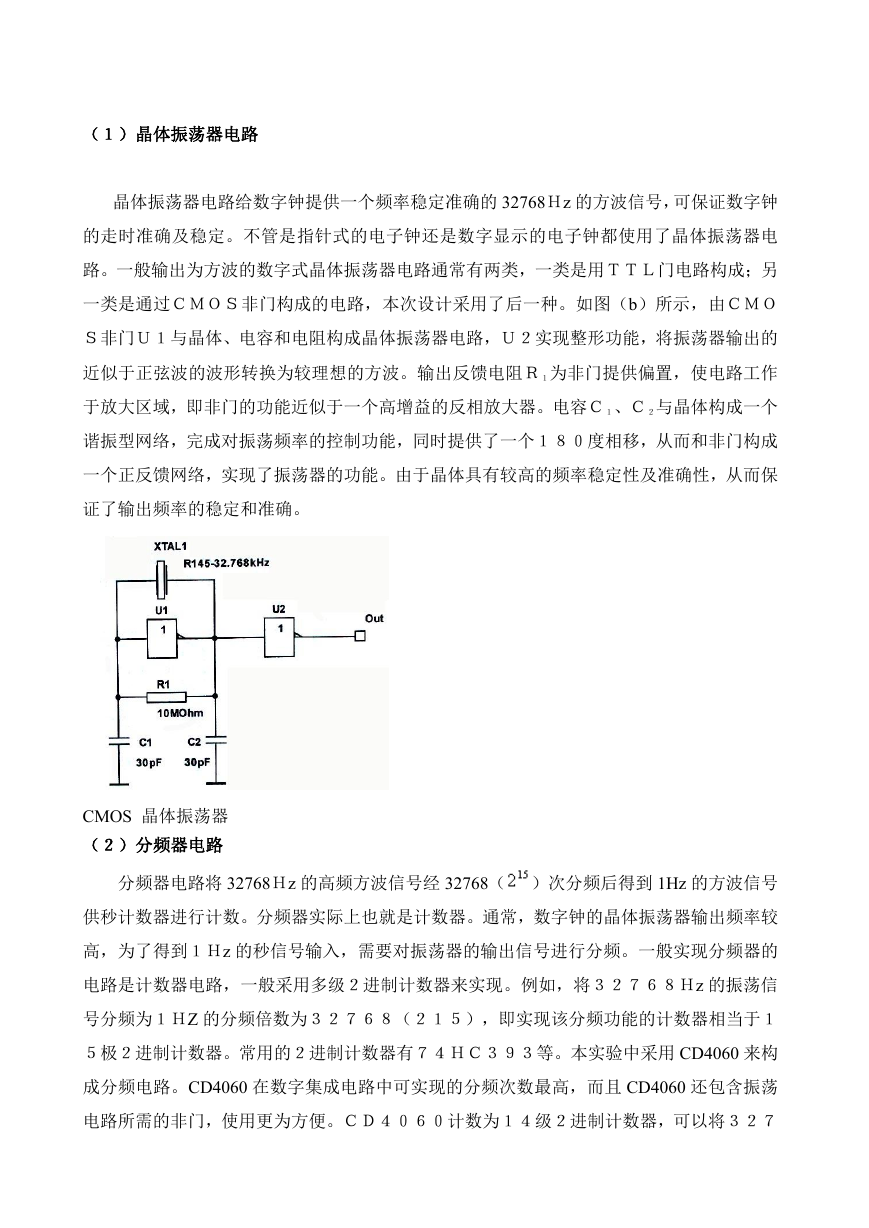

(1)晶体振荡器电路

晶体振荡器电路给数字钟提供一个频率稳定准确的 32768Hz 的方波信号,可保证数字钟

的走时准确及稳定。不管是指针式的电子钟还是数字显示的电子钟都使用了晶体振荡器电

路。一般输出为方波的数字式晶体振荡器电路通常有两类,一类是用TTL门电路构成;另

一类是通过CMOS非门构成的电路,本次设计采用了后一种。如图(b)所示,由CMO

S非门U1与晶体、电容和电阻构成晶体振荡器电路,U2实现整形功能,将振荡器输出的

近似于正弦波的波形转换为较理想的方波。输出反馈电阻R1为非门提供偏置,使电路工作

于放大区域,即非门的功能近似于一个高增益的反相放大器。电容C1、C2与晶体构成一个

谐振型网络,完成对振荡频率的控制功能,同时提供了一个180度相移,从而和非门构成

一个正反馈网络,实现了振荡器的功能。由于晶体具有较高的频率稳定性及准确性,从而保

证了输出频率的稳定和准确。

CMOS 晶体振荡器

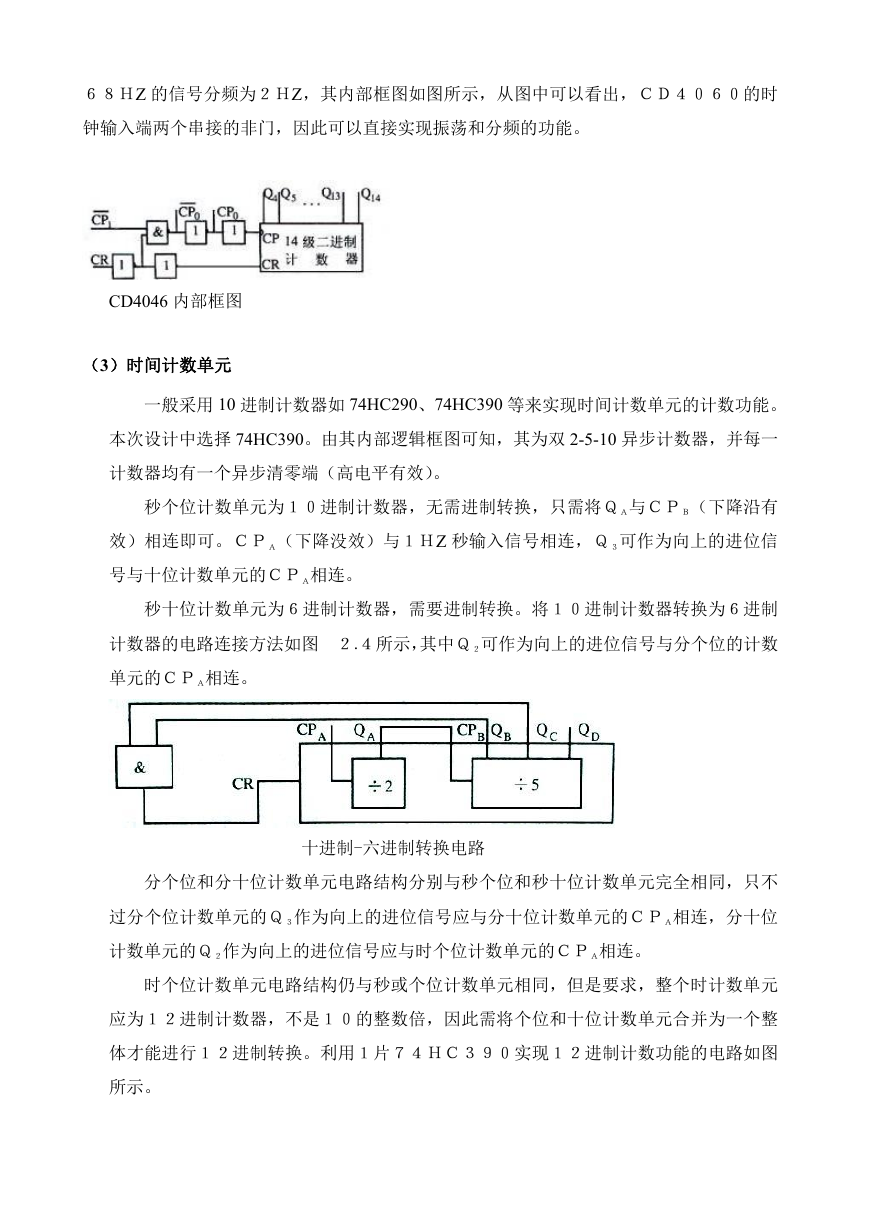

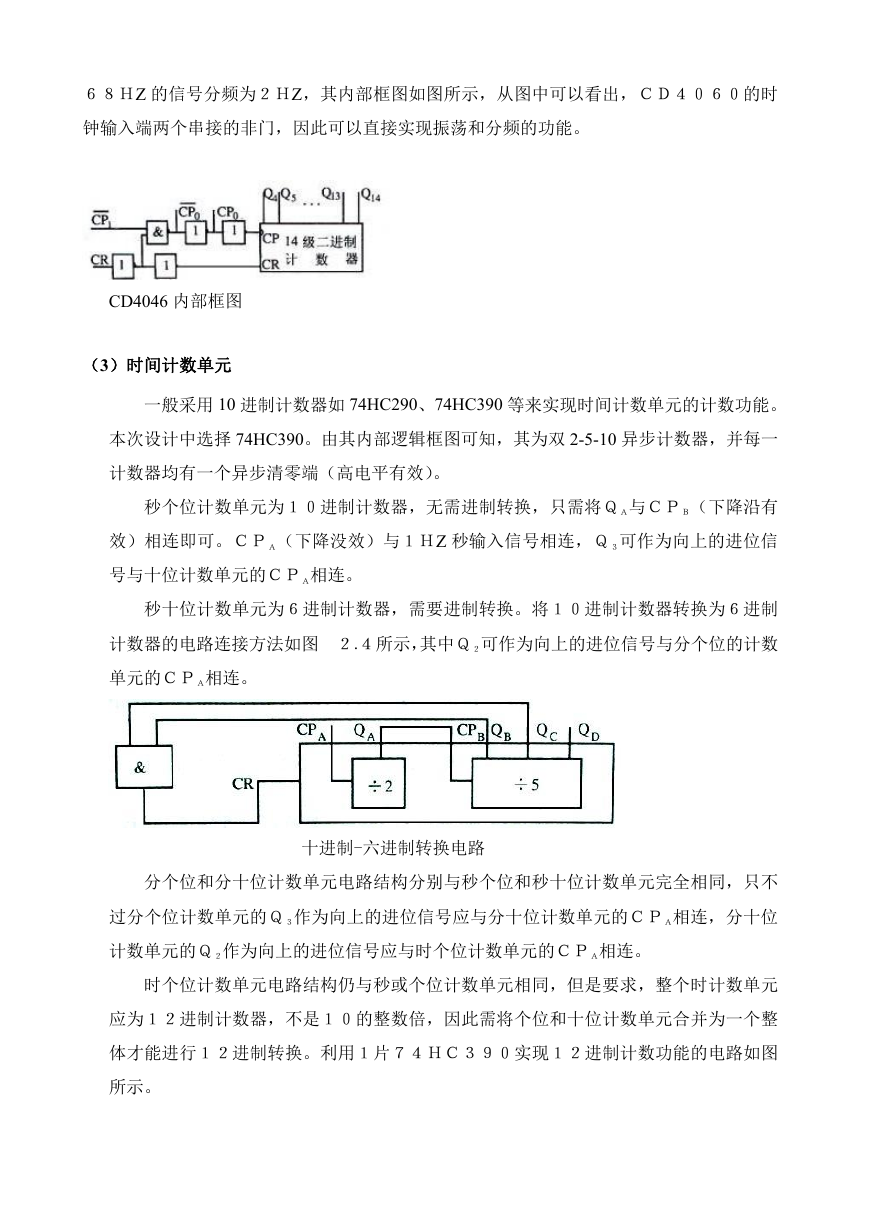

(2)分频器电路

分频器电路将 32768Hz 的高频方波信号经 32768( )次分频后得到 1Hz 的方波信号

供秒计数器进行计数。分频器实际上也就是计数器。通常,数字钟的晶体振荡器输出频率较

高,为了得到1Hz 的秒信号输入,需要对振荡器的输出信号进行分频。一般实现分频器的

电路是计数器电路,一般采用多级2进制计数器来实现。例如,将32768Hz 的振荡信

号分频为1HZ 的分频倍数为32768(215),即实现该分频功能的计数器相当于1

5极2进制计数器。常用的2进制计数器有74HC393等。本实验中采用 CD4060 来构

成分频电路。CD4060 在数字集成电路中可实现的分频次数最高,而且 CD4060 还包含振荡

电路所需的非门,使用更为方便。CD4060计数为14级2进制计数器,可以将327

�

68HZ 的信号分频为2HZ,其内部框图如图所示,从图中可以看出,CD4060的时

钟输入端两个串接的非门,因此可以直接实现振荡和分频的功能。

CD4046 内部框图

(3)时间计数单元

一般采用 10 进制计数器如 74HC290、74HC390 等来实现时间计数单元的计数功能。

本次设计中选择 74HC390。由其内部逻辑框图可知,其为双 2-5-10 异步计数器,并每一

计数器均有一个异步清零端(高电平有效)。

秒个位计数单元为10进制计数器,无需进制转换,只需将QA与CPB(下降沿有

效)相连即可。CPA(下降没效)与1HZ 秒输入信号相连,Q3可作为向上的进位信

号与十位计数单元的CPA相连。

秒十位计数单元为6进制计数器,需要进制转换。将10进制计数器转换为6进制

计数器的电路连接方法如图 2.4所示,其中Q2可作为向上的进位信号与分个位的计数

单元的CPA相连。

十进制-六进制转换电路

分个位和分十位计数单元电路结构分别与秒个位和秒十位计数单元完全相同,只不

过分个位计数单元的Q3作为向上的进位信号应与分十位计数单元的CPA相连,分十位

计数单元的Q2作为向上的进位信号应与时个位计数单元的CPA相连。

时个位计数单元电路结构仍与秒或个位计数单元相同,但是要求,整个时计数单元

应为12进制计数器,不是10的整数倍,因此需将个位和十位计数单元合并为一个整

体才能进行12进制转换。利用1片74HC390实现12进制计数功能的电路如图

所示。

�

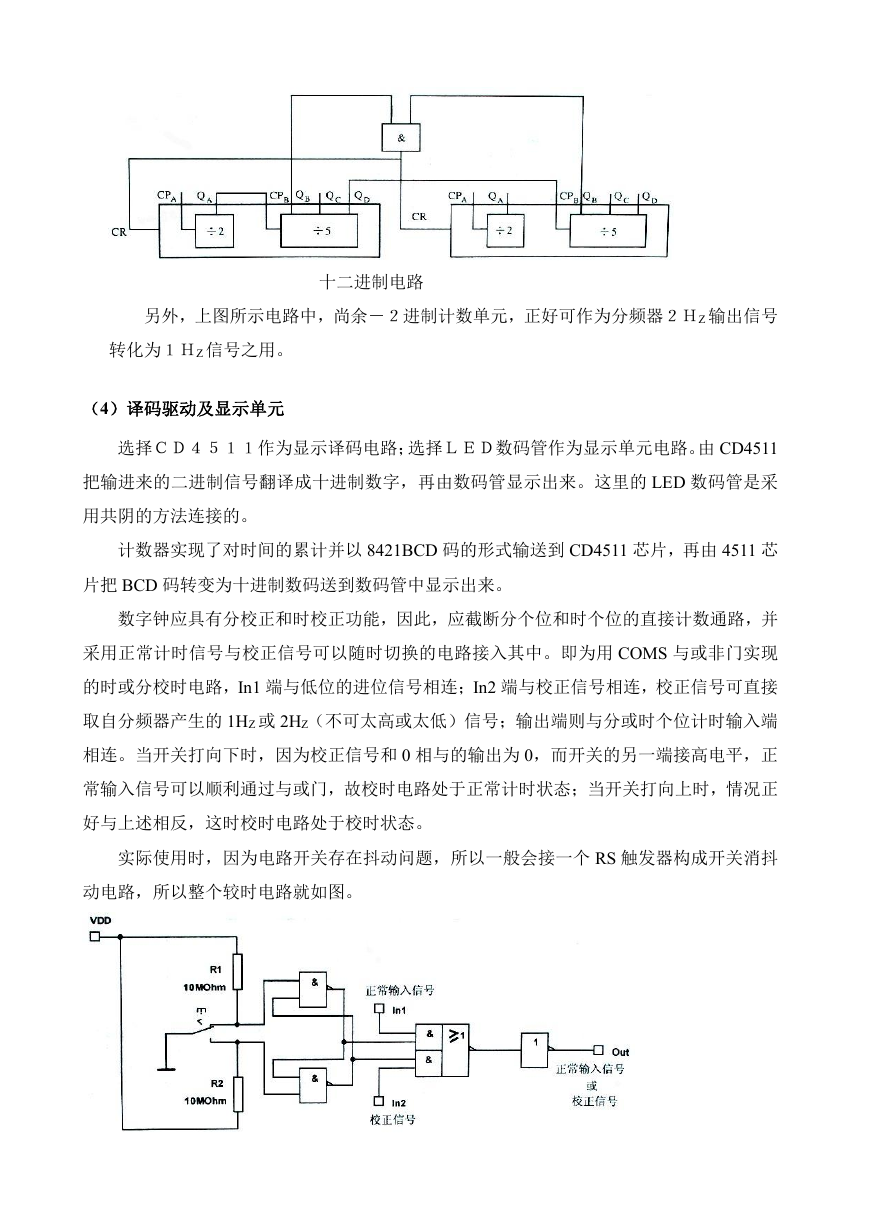

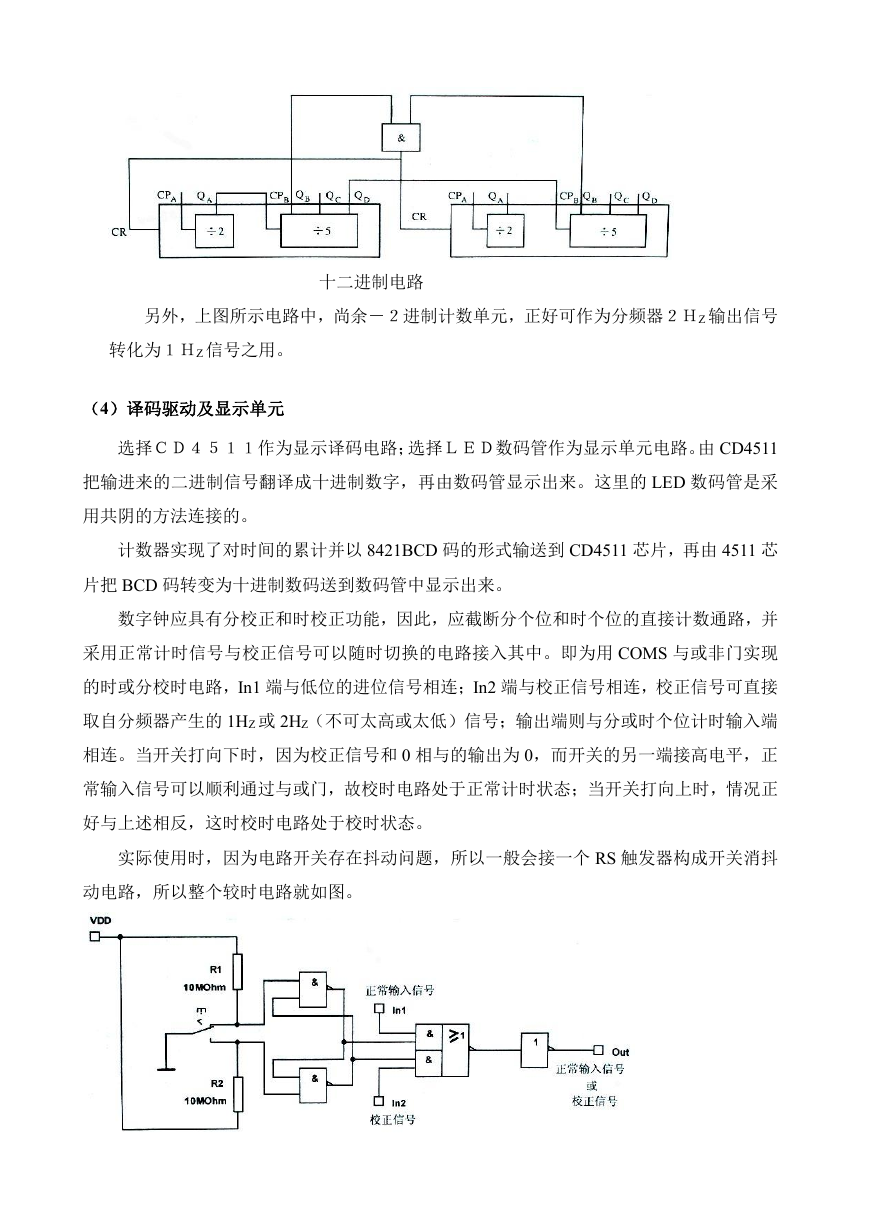

十二进制电路

另外,上图所示电路中,尚余-2进制计数单元,正好可作为分频器2HZ 输出信号

转化为1HZ 信号之用。

(4)译码驱动及显示单元

选择CD4511作为显示译码电路;选择LED数码管作为显示单元电路。由 CD4511

把输进来的二进制信号翻译成十进制数字,再由数码管显示出来。这里的 LED 数码管是采

用共阴的方法连接的。

计数器实现了对时间的累计并以 8421BCD 码的形式输送到 CD4511 芯片,再由 4511 芯

片把 BCD 码转变为十进制数码送到数码管中显示出来。

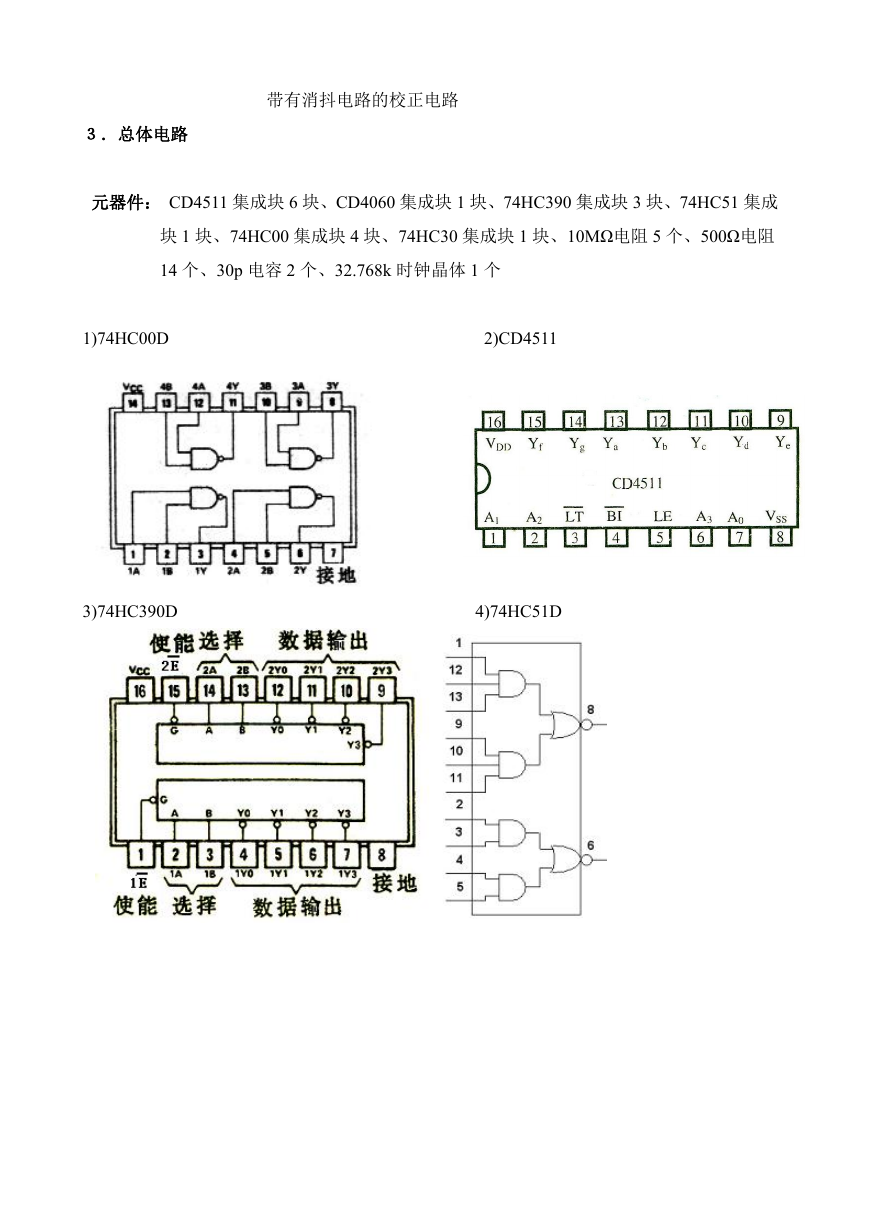

数字钟应具有分校正和时校正功能,因此,应截断分个位和时个位的直接计数通路,并

采用正常计时信号与校正信号可以随时切换的电路接入其中。即为用 COMS 与或非门实现

的时或分校时电路,In1 端与低位的进位信号相连;In2 端与校正信号相连,校正信号可直接

取自分频器产生的 1HZ 或 2HZ(不可太高或太低)信号;输出端则与分或时个位计时输入端

相连。当开关打向下时,因为校正信号和 0 相与的输出为 0,而开关的另一端接高电平,正

常输入信号可以顺利通过与或门,故校时电路处于正常计时状态;当开关打向上时,情况正

好与上述相反,这时校时电路处于校时状态。

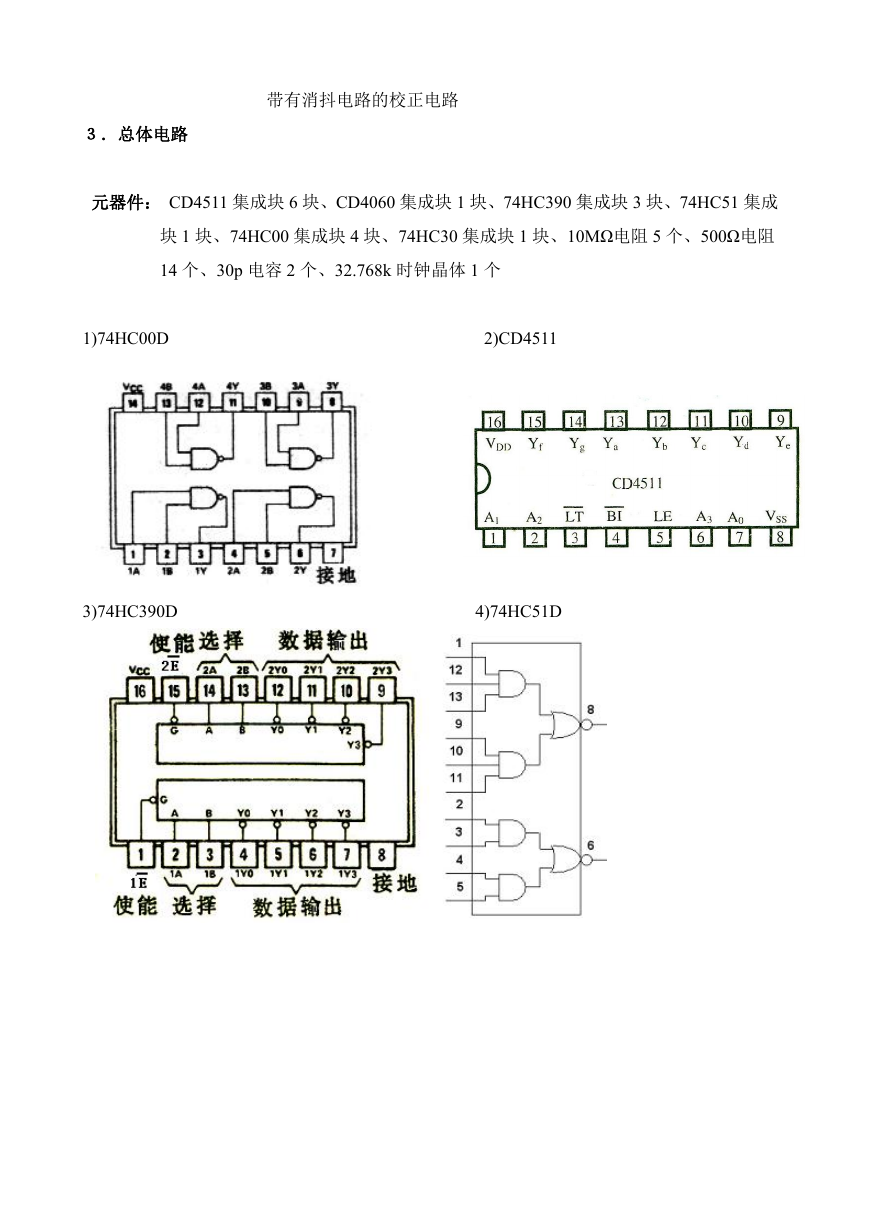

实际使用时,因为电路开关存在抖动问题,所以一般会接一个 RS 触发器构成开关消抖

动电路,所以整个较时电路就如图。

�

带有消抖电路的校正电路

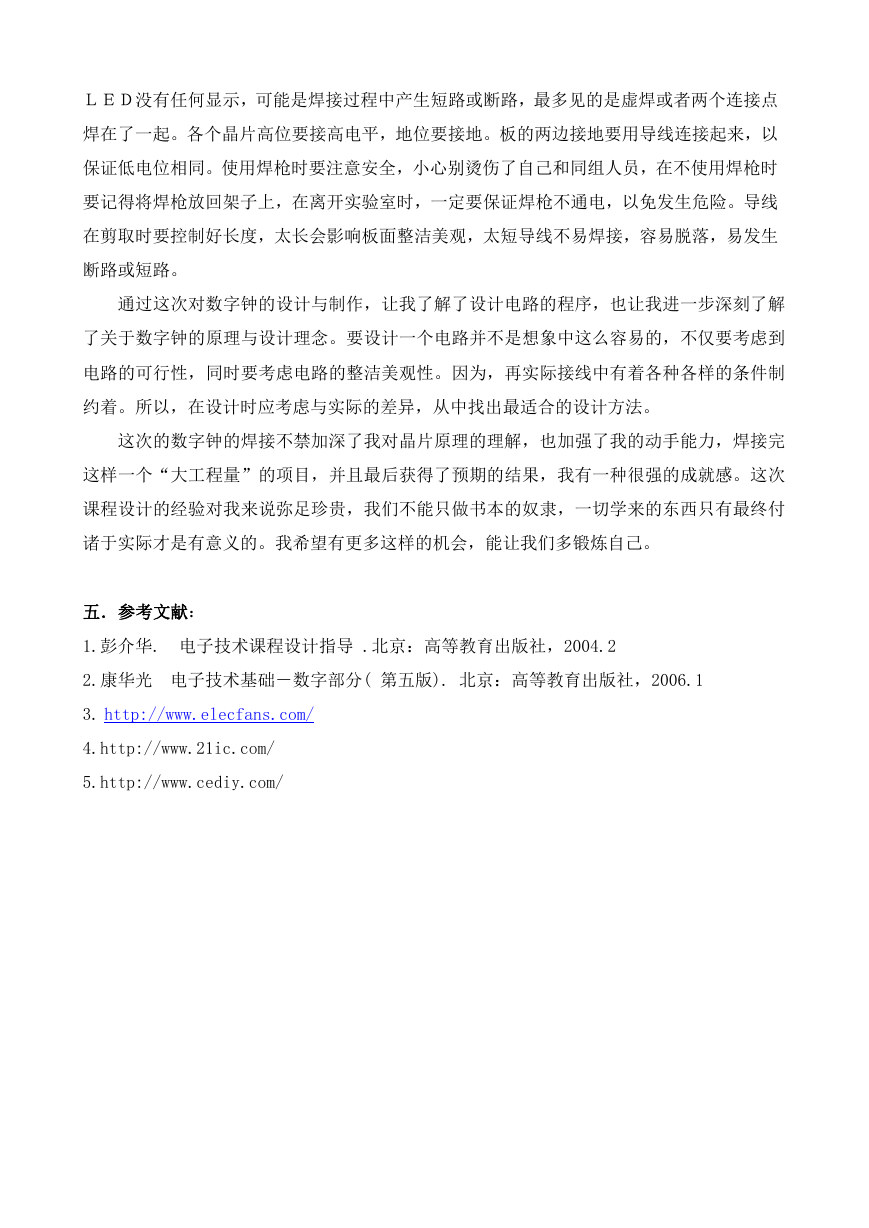

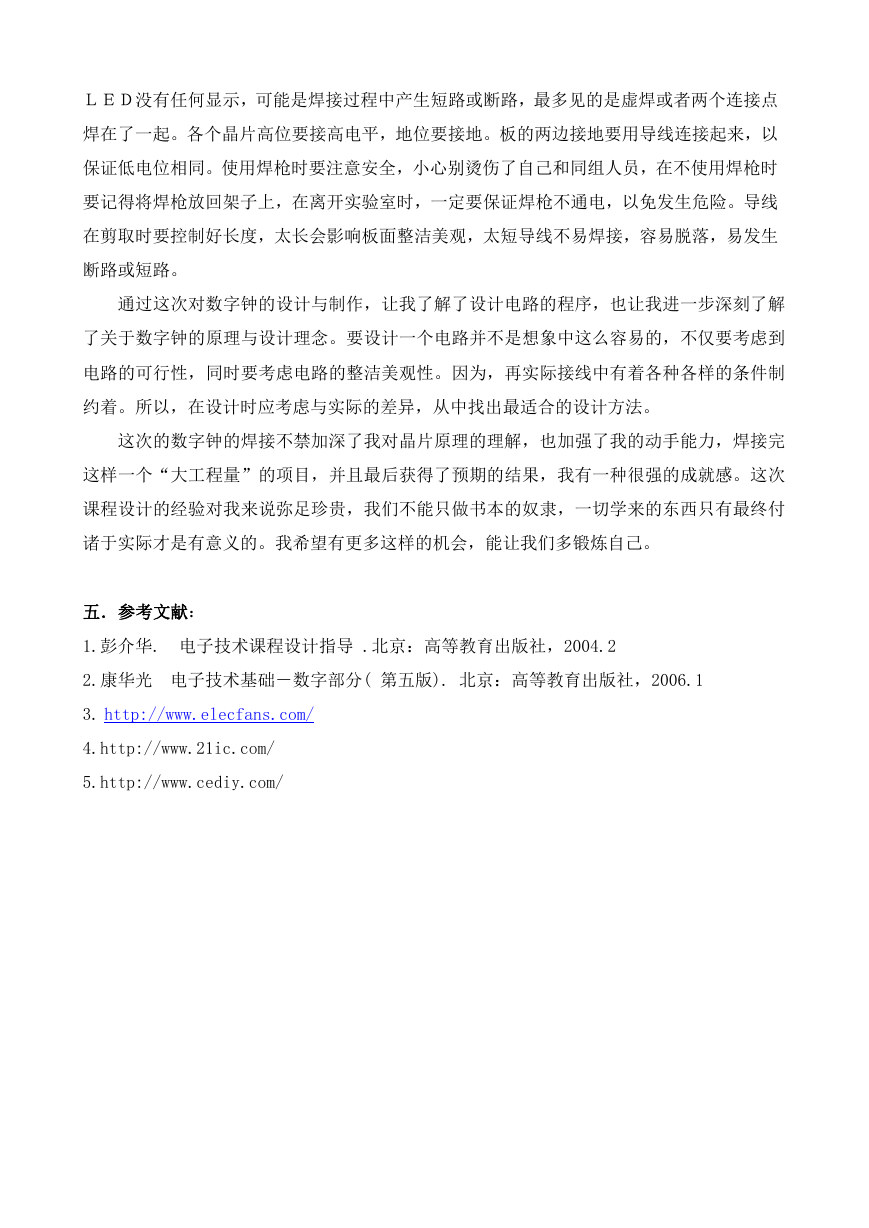

3.总体电路

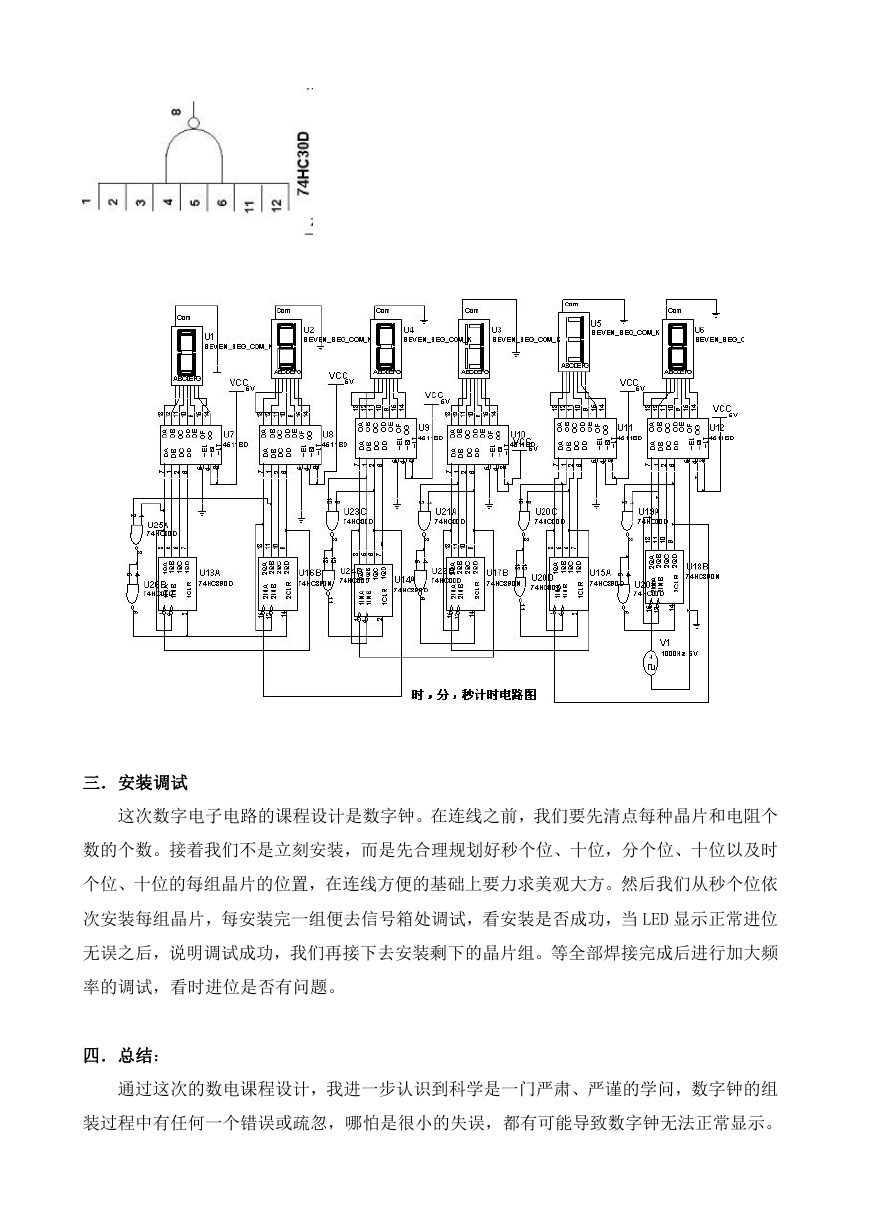

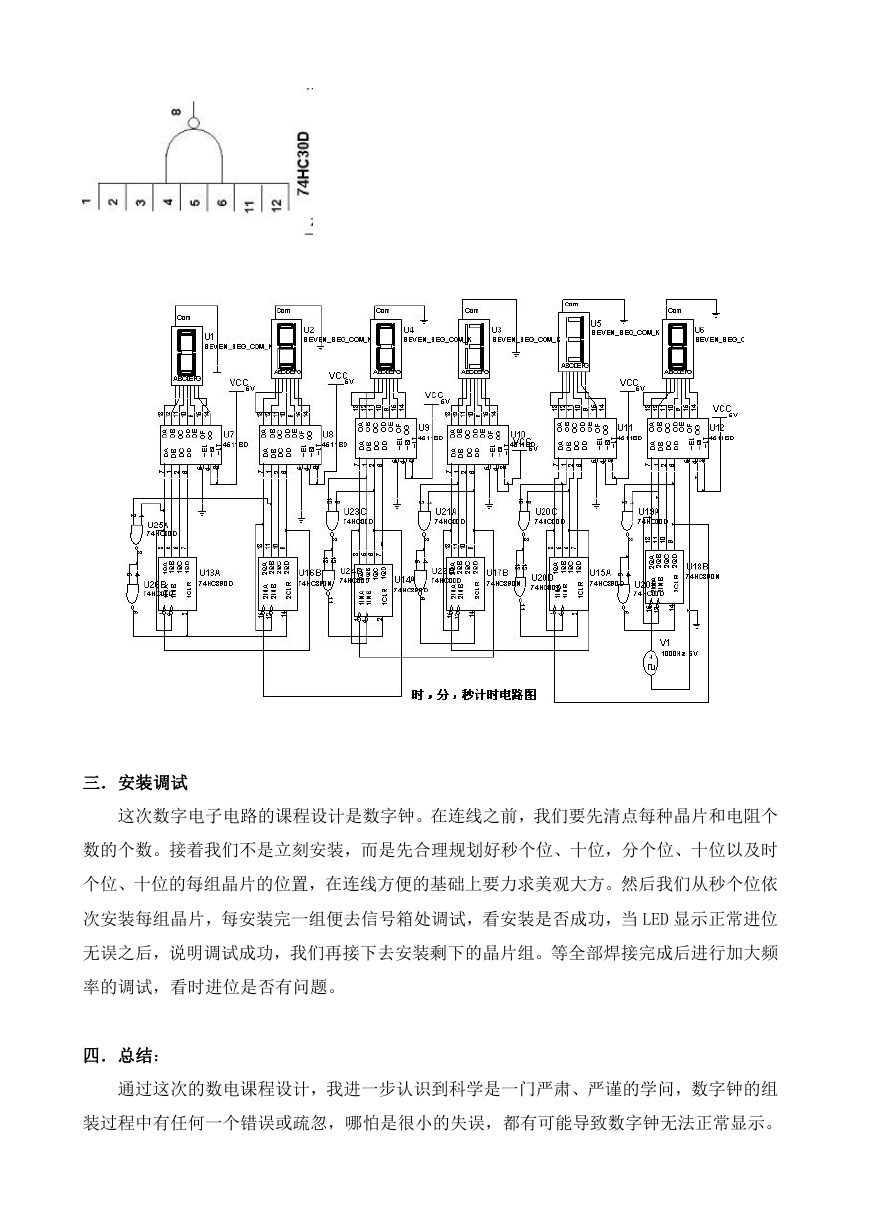

元器件: CD4511 集成块 6 块、CD4060 集成块 1 块、74HC390 集成块 3 块、74HC51 集成

块 1 块、74HC00 集成块 4 块、74HC30 集成块 1 块、10MΩ电阻 5 个、500Ω电阻

14 个、30p 电容 2 个、32.768k 时钟晶体 1 个

1)74HC00D

2)CD4511

3)74HC390D

4)74HC51D

�

三.安装调试

这次数字电子电路的课程设计是数字钟。在连线之前,我们要先清点每种晶片和电阻个

数的个数。接着我们不是立刻安装,而是先合理规划好秒个位、十位,分个位、十位以及时

个位、十位的每组晶片的位置,在连线方便的基础上要力求美观大方。然后我们从秒个位依

次安装每组晶片,每安装完一组便去信号箱处调试,看安装是否成功,当 LED 显示正常进位

无误之后,说明调试成功,我们再接下去安装剩下的晶片组。等全部焊接完成后进行加大频

率的调试,看时进位是否有问题。

四.总结:

通过这次的数电课程设计,我进一步认识到科学是一门严肃、严谨的学问,数字钟的组

装过程中有任何一个错误或疏忽,哪怕是很小的失误,都有可能导致数字钟无法正常显示。

�

LED没有任何显示,可能是焊接过程中产生短路或断路,最多见的是虚焊或者两个连接点

焊在了一起。各个晶片高位要接高电平,地位要接地。板的两边接地要用导线连接起来,以

保证低电位相同。使用焊枪时要注意安全,小心别烫伤了自己和同组人员,在不使用焊枪时

要记得将焊枪放回架子上,在离开实验室时,一定要保证焊枪不通电,以免发生危险。导线

在剪取时要控制好长度,太长会影响板面整洁美观,太短导线不易焊接,容易脱落,易发生

断路或短路。

通过这次对数字钟的设计与制作,让我了解了设计电路的程序,也让我进一步深刻了解

了关于数字钟的原理与设计理念。要设计一个电路并不是想象中这么容易的,不仅要考虑到

电路的可行性,同时要考虑电路的整洁美观性。因为,再实际接线中有着各种各样的条件制

约着。所以,在设计时应考虑与实际的差异,从中找出最适合的设计方法。

这次的数字钟的焊接不禁加深了我对晶片原理的理解,也加强了我的动手能力,焊接完

这样一个“大工程量”的项目,并且最后获得了预期的结果,我有一种很强的成就感。这次

课程设计的经验对我来说弥足珍贵,我们不能只做书本的奴隶,一切学来的东西只有最终付

诸于实际才是有意义的。我希望有更多这样的机会,能让我们多锻炼自己。

五.参考文献:

1.彭介华. 电子技术课程设计指导 .北京:高等教育出版社,2004.2

2.康华光 电子技术基础-数字部分( 第五版). 北京:高等教育出版社,2006.1

3. http://www.elecfans.com/

4.http://www.21ic.com/

5.http://www.cediy.com/

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc